用于MEMS器件的CMOS封盖

文献发布时间:2023-06-19 11:47:31

相关申请的交叉引用

本申请是部分继续申请,其要求共同待决的2019年7月21日提交的美国专利申请号16/517,653的优先权,第16/517,653号是继续申请,其要求2017年7月12日提交的美国专利申请号15/647,284的优先权,第15/647,284号标题为可扩展的基于热电的红外探测器,现为美国专利10,403,674。本申请交叉引用2018年12月18日提交的美国专利申请号16/224,782,第16/224,782号是2017年7月19日提交的美国专利申请号15/653,558的分案申请,第15/653,558号标题为具有高CMOS集成度的基于热电的红外探测器,现为美国专利10,199,424,其公开内容出于所有目的通过引用整体并入本文。

技术领域

本申请涉及用于MEMS器件的CMOS封盖及其形成方法。

背景技术

由于众多应用的需求增加,对非制冷红外(IR)探测器的需求持续增长。这些应用仅举几例,包括空调系统,手机,自动驾驶汽车,物联网(IoT),消防和交通安全。此外,预计在不久的将来会有更多的应用。

常规的非制冷红外探测器已经利用微测辐射热计实现了。但是,微测辐射热计需要用于校准的机械部件。例如,微测辐射热计需要机械快门来进行偏移校正。微测辐射热计所需的机械组件会增加制造复杂性。这种复杂性增加了成本。另外,对于微测辐射热计的机械部件的需求使得难以生产小型或紧凑的装置。

本公开针对成本效益高且紧凑的IR探测器。

发明内容

本公开的实施例总体上涉及器件及其形成方法。

在一个实施例中,一种器件包括:衬底,所述衬底制备有具有CMOS器件的互补金属氧化物半导体(CMOS)区和具有微机电系统(MEMS)区的传感器区,所述微机电系统区具有MEMS组件。所述器件还包括CMOS兼容封盖,所述CMOS兼容封盖设置在CMOS区和MEMS区上方的衬底上。所述CMOS兼容封盖包括CMOS层,并且CMOS兼容封盖在MEMS区上方升高,以在封盖与MEMS区之间提供盖腔。

在另一实施例中,一种用于形成器件的方法包括:提供衬底,所述衬底制备有具有CMOS器件的互补金属氧化物半导体(CMOS)区,和具有微机电系统(MEMS)区的传感器区,所述微机电系统(MEMS)区具有MEMS组件。所述方法还包括在CMOS区和MEMS区上方的衬底上形成CMOS兼容封盖。所述CMOS兼容封盖包括CMOS层,所述CMOS兼容封盖在MEMS区上方升高,以在封盖与MEMS区之间提供盖腔。

通过参考以下描述和附图,本文公开的实施例的这些和其他优点和特征将变得显而易见。此外,应当理解,本文所述的各种实施例的特征不是互相排斥的,并可以各种组合和排列存在。

附图说明

附图示出了本公开的优选实施例,其结合在说明书中并形成说明书的一部分,其中相似的附图标记指代相似的部分,并且其与说明书一起用于解释本公开的各种实施例的原理。

图1示出了半导体晶片的俯视图;

图2a-b示出了器件的实施例的简化截面图;

图3a-b示出了位于传感器区不同数量的CMOS原位封盖的内支承壁的替代实施例的简化截面图;

图4a-b示出了用于密封传感器区的CMOS原位封盖的封盖的替代实施例的简化截面图;

图5a-d示出了传感器区的CMOS原位封盖的替代实施例的简化截面图;

图6a-d示出了用于吸气剂层,释放开口和支承壁的布局或设计的各种实施例的俯视图;

图7a-d示出了热电堆结构的各种示例性实施例的俯视图和截面图;

图7e示出了2x3传感器阵列的示例性布局;

图8a-r示出了用于形成器件的示例性工艺的简化截面图;

图8s-t示出了用于形成器件的另一工艺的简化截面图;

图8u-v示出了用于形成器件的另一工艺的简化截面图;

图9a示出了封盖的一实施例的IR透射图;和

图9b示出了封盖的一实施例的机械强度。

具体实施方式

实施例总体上涉及器件,例如,具有基于热电的红外(IR)探测器的半导体器件或集成电路(IC)。所述IC,例如是互补金属氧化物半导体(CMOS)器件。关于IR探测器或传感器,其例如是微机电系统(MEMS)。所述MEMS探测器嵌入在IC中。此外,MEMS探测器与CMOS工艺兼容。所述器件可以并入产品中,例如热成像仪。例如,器件可以包括多个MEMS传感器,其可配置为形成用于热成像仪的传感器阵列。所述传感器可用于其他类型的应用,例如单像素或线阵列温度或运动传感器。作为前道工序(FEOL)工艺的一部分,器件的制造可涉及在构成电路组件的衬底上形成特征,例如晶体管,电阻器,电容器和MEMS传感器。作为后道工序(BEOL)工艺的一部分,形成互连件以互连所述组件,使器件能够执行期望的功能。所述BEOL工艺还包括形成CMOS兼容的原位红外透明封盖,所述封盖气密密封所述MEMS传感器。

为了形成诸如CMOS电路组件,传感器,互连件和封盖之类的特征,层被重复沉积在衬底上,并根据期望使用光刻技术被图案化。例如,使用包含期望图案的掩模版通过曝光源对光刻胶层曝光对晶片进行图案化。曝光之后,光刻胶层被显影,将掩模版的图案转移到光刻胶层上。这形成光刻胶刻蚀掩模。使用刻蚀掩模执行刻蚀以复制下方晶片上的图案,可以包括一层或多层,具体取决于工艺阶段。在器件形成的过程中,大量掩模版可用于不同的图案化工艺。此外,多个器件可以在晶片上平行形成。通过使用与CMOS标准工艺流程兼容的CMOS IR透明封盖对传感器进行气密密封,制造成本被大幅较低,使得能够批量生产集成传感器器件。

图1示出了半导体晶片101的实施例的简化平面图。半导体晶片例如可以是硅晶片。所述晶片可以是轻掺杂的p型晶片。其他类型的晶片,例如绝缘体上硅(SOI)或硅锗晶片,以及掺杂有其他类型的掺杂剂或掺杂剂浓度的晶片,也可以。

晶片包括在其上形成器件115的有源表面111。多个器件可以在晶片上平行形成。所述器件,例如沿着第一(x)方向成行,并且沿着第二(y)方向成列。分离所述器件是切割通道的过程。在完成加工和封装之后,晶片被沿着切割通道划片,以将器件分离成单独的芯片。

图2a-b示出了器件115的实施例的简化截面图。所述器件例如是具有嵌入式MEMS结构或组件的CMOS器件。在一个实施例中,所述器件是嵌入有基于热电的IR传感器或探测器的CMOS器件。在一些实施例中,器件的MEMS结构包括多个基于热电的IR传感器。多个传感器可配置为形成传感器或探测器阵列。例如,所述器件可以是IR成像仪,其中每个传感器可以是红外图像的一个像素。其他类型的MEMS结构或应用也是可以的。所述器件例如可以与其他器件平行形成在晶片上并随后被分离。

如图2a-b所示,所述器件包括衬底201。所述衬底例如可以是所述晶片的一部分,在所述晶片上形成器件并分离成单个裸片,如图1所示。共同元件可能不描述或详细描述。衬底可以是半导体衬底,例如硅衬底,其是晶片的一部分。衬底可以是轻掺杂的p型硅衬底。其他类型的衬底或晶片也可以。

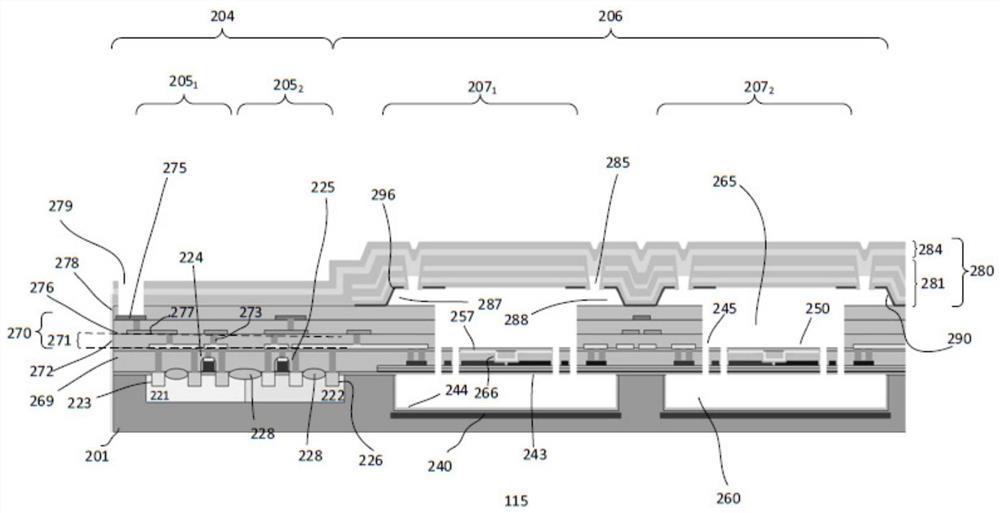

在一个实施例中,所述衬底包括第一和第二器件区域204和206。第一区域是CMOS区,而第二区域是MEMS区。所述CMOS区包括CMOS组件,而所述MEMS区包括MEMS结构或组件。如图所示,所述CMOS区包括用于第一和第二CMOS组件或器件的第一和第二CMOS器件区205

所述第一晶体管包括第二极性类型的第一阱221。所述第一晶体管包括位于第一极性类型的源极/漏极(S/D)区之间的阱表面上的栅极。第一阱还可以包括用于偏置第一阱的第二极性类型的第一抽头223。在第一晶体管为n型的情况下,阱和抽头为p型,而S/D区为n型。第二晶体管包括第一极性类型的第二阱222。第二晶体管包括在第二极性类型的S/D区之间的阱表面上的栅极。第二阱可以包括用于偏置第二阱的第一极性类型的第二抽头226。在第二晶体管是p型的情况下,阱和抽头是n型,而S/D区是p型。

栅极可包括在栅极电介质上方的栅电极。栅电极可以是多晶硅,栅极电介质可以是热氧化硅。其他类型的材料或栅极的配置也可以。所述S/D区可以包括轻掺杂的延伸区。轻掺杂的延伸区轻度掺杂有与重掺杂的S/D区相同极性类型的掺杂剂。栅极的侧壁可以包括电介质间隔物。间隔物有助于对准S/D和轻掺杂的延伸区。

尽管仅示出了两个晶体管,但是应当理解,CMOS区可以包括许多晶体管以及其他CMOS组件。晶体管可配置为以不同的电压工作。例如,CMOS区可包括用于LV晶体管的低压(LV)区,用于MV晶体管的中压(MV)区和用于HV晶体管的高压(HV)区。也可以包括其他类型的器件区。例如,可以包括其中设置有存储器阵列的存储器区。

如前所述,所述器件可以包括位于MEMS区的传感器阵列,其具有布置成具有传感器行和列的矩阵的多个传感器。每个传感器可以对应于像素阵列中的一个像素。在这种情况下,CMOS组件可以包括选择开关,行和列解码器以及读出电路。也可以包括其他CMOS组件。CMOS组件配置为读出阵列的每个像素。一旦读出传感器的全部阵列,就可以重建图像。所述图像例如是与阵列的传感器相对应的一帧。

提供隔离区228以隔离组件区域。例如,提供隔离区以隔离第一和第二晶体管区域以及CMOS和MEMS组件。另外,可以提供隔离区以将器件阱接触与S/D区隔离。隔离区可以是场氧化物(FOX)隔离区。其他类型的隔离区,例如浅沟槽隔离(STI)区,也可以。

MEMS区206包括用于MEMS结构或传感器的至少一个MEMS器件区。在一个实施例中,MEMS区包括多个MEMS器件区,每个具有一个MEMS传感器。传感器被配置并互连以形成传感器阵列。如图所示,MEMS区包括第一和第二MEMS器件区207

MEMS器件区包括下部器件或传感器腔260。在一个实施例中,下部器件腔设置在衬底中,形成衬底腔。例如,下部器件腔可以是由刻蚀衬底形成的沟槽。衬底腔包括由衬底限定的腔侧壁和底部。在衬底表面上方提供下部器件腔也可以。下部器件腔可以具有正方形或矩形的覆盖区或形状。用于下部器件腔的其他形状也可以。至于下部器件腔的顶部,它由介电层243限定。介电层覆盖下部器件腔。在MEMS区包括多个MEMS器件区的情况下,每个均具有下部器件腔,介电层覆盖传感器阵列的所有腔。介电层可以是氧化硅层。其他类型的介电层,例如氮化硅也可以。例如,介电层可以是具有多个介电层的电介质堆叠。介电层用作用于MEMS器件区的MEMS结构250的膜。

反射体240设置在下部器件腔的底部。在一个实施例中,第一反射体设置在第一下部器件腔中,第二反射体设置在第二下部器件腔中。反射体配置为反射红外(IR)辐射。反射体可由导电材料形成。在一个实施例中,反射体是导电金属硅化物反射体。金属硅化物反射体可以是硅化钛(TiSi

可以提供保护衬垫244。所述保护衬垫,在一个实施例中,衬在下部器件腔的侧壁和底部,覆盖反射体。保护衬垫用于保护反射体和下部器件腔的侧壁免受后续工艺的影响。例如,保护衬垫用于保护反射体免受刻蚀剂(例如XeF

MEMS结构250设置在介电层上的传感器区中,所述介电层限定了第一下部器件腔和第二下部器件腔的顶部。例如,MEMS结构可以设置在衬于第一和第二下部器件腔的顶部的介电层的衬垫上。MEMS结构可以是传感器。在一个实施例中,MEMS结构是用作热电IR传感器或探测器的热电堆线结构。所述热电堆结构可以类似于在例如USSN 16/517,653,USSN10,403,674,USSN 16/224,782和USSN 10,199,424中描述的那些,出于所有目的已经将它们全部引入本文作为参考。包括非IR传感器的其他类型的MEMS结构或传感器也可以设置在传感器区中。

热电堆线结构,在一个实施例中,包括掺杂的热电材料。在一个实施例中,热电堆线结构包括掺杂的多晶硅。在高温下稳定的其他类型的热电材料也可以用作热电堆线结构。例如,其他热电材料可以包括硅锗(SiGe),氮化镓(GaN)或2D材料,例如石墨烯,黑磷或硫化钼。所述热电材料可以是掺杂的热电材料。所述线结构的图案可以是蛇形或曲折的线图案。

在一个实施例中,热电堆线结构包括N个线单元,其中N≥1。例如,热电堆线结构可以包括1个(N=1)或更多(N>1)个线单元。线单元包括掺杂有第一和第二热电堆掺杂剂的第一和第二线段。第一热电堆掺杂剂是第一极性型掺杂剂,第二热电堆掺杂剂是第二极性型掺杂剂。第一和第二极性类型的掺杂剂是相反极性类型的掺杂剂。例如,第一极性类型是p型,第二极性类型是n型。第一和第二段优选地具有大约对称的长度。例如,第一和第二段的长度大约相同。这在段之间产生大致对称的散热。在某些情况下,段的长度可以为彼此的±20%。这在段之间产生可接受的散热差异。线段的掺杂可以例如被集成到p型和n型晶体管的S/D掺杂工艺中。或者,可以采用单独的掺杂工艺以形成掺杂线段。

在线结构包括单个线单元的情况下,线单元的段设置在线层上。例如,线单元的第一和第二线段设置在介电层上方的相同线层上。

在一个实施例中,金属接触件266连接第一和第二线段。金属接触件可以设置在第一和第二线段的交界处。在一个实施例中,金属接触件应该是高温接触件。例如,接触件可以维持后续工艺温度。高温金属接触件例如可以是钛(Ti)或铝(Al)合金接触件。其他类型的高温金属也可用于形成接触件。第一热电堆端子设置在线结构的第一端,第二热电堆端子设置在线结构的第二端。端子可以是线结构的一部分。

在线结构包括多线单元线结构(N>1)的情况下,多线单元结构的线单元是堆叠式线单元。多线单元线结构的线单元串联耦合。提供多个线单元以形成传感器可在不增加表面积的情况下提高传感器性能。在一个实施例中,多线结构包括第一和第二堆叠式线单元(N=2)。为线结构提供其他数量的线单元也是可以的。例如,线结构可以具有1-4(N=1-4)个线单元。优选地,线结构具有2N个线单元,其中N=0–2。其他数量的线单元也可以。

在一个实施例中,第一堆叠式线单元和第二堆叠式线单元在位于传感器区的介电层上彼此相邻地设置。堆叠式线单元包括设置在第一线层中的第一段和设置在第二线层中的第二段。第一和第二线层可由介电层分开。例如,线单元的第二线段覆盖在线单元的第一线段上方,并由线层间介电层隔开。接触件将第一线层中的第一线段连接至第二线层中的第二线段。

如前所述,第一和第二线单元串联耦合。例如,第一线单元的第二端子可以耦合至第二线单元的第一端子,而第一线单元的第一端子用作多线单元线结构的第一端子,且第二线单元的第二端子用作多线单元线结构的第二端子。例如,具有2个线单元的线结构可以串联连接以形成n-p-n-p线结构。

多线单元线结构的线单元优选具有相似的设计。例如,线结构具有相似的图案,具有相似的线段长度,其允许以相同切口通过介电层至牺牲层以便于更容易的释放工艺。线单元的其他配置也可以。

在多晶硅线结构的情况下,其可由用于形成栅电极的多晶硅层之一形成。例如,CMOS工艺可以包括用于栅电极的栅电极层,并且还可以被用作多晶硅线结构。在CMOS工艺包括多于一个多晶硅栅电极层的情况下,可以优选较薄的多晶硅栅电极层以用作多晶硅线结构。在另一个实施例中,可以采用单独的层作为线结构。当堆叠多个线结构时,不同的堆叠式结构优选具有相同的材料和厚度。提供具有不同厚度的线结构也可以。例如,可以通过改变厚度来调节电阻,并且更薄的多晶硅线结构由于灵敏度的提高可改善热隔离。在该工艺中可以包括附加的线结构层以用作所述堆叠式线结构。

可以在线结构上方设置吸收层257。吸收层例如配置为吸收入射的IR辐射。在一个实施例中,吸收层设置在线结构的中央部分上。吸收层热耦合至线结构的中心。吸收层可以是氮化钛(TiN)层。其他类型的吸收层也可以。例如,吸收层可以是镍铬(NiCr)层或掺杂的硅层。在一个实施例中,吸收体配置成吸收大部分入射的IR辐射。例如,吸收体可以配置为吸收大于85%的波长为8–14μm的入射IR辐射。提供任何其他配置也可以。在其他实施例中,吸收体配置为吸收波长为2–5μm的入射辐射。例如,使用干涉式吸收体的另一谐波。在一个实施例中,吸收体配置成吸收>50%的波长为2-5μm的入射辐射。

传感器保护层,在一个实施例中,设置在吸收层上方。传感器保护层用于保护传感器免受后续刻蚀工艺的影响。例如,保护层用于保护线结构和吸收层免受用于形成下部器件腔的刻蚀剂(例如XeF

释放开口245设置在膜和上方的其他层中,例如位于传感器,吸收层和保护层之间的介电层,以使得能够在释放工艺中去除下部器件腔中的下部器件腔牺牲材料。在一个实施例中,下部器件腔具有一定深度,该深度被选择用于通过反射体最佳地反射IR辐射的期望波长。在一个实施例中,腔的深度足以确保吸收体与反射体之间的1/4波长光学距离。例如,用于检测波长为8–12μm的IR辐射的光学距离大约为2–3μm。其他距离也可以,具体取决于要检测的波长。例如,通过减小或增加光学距离,可以分别检测具有更小或更大波长的IR辐射。光学距离被定义为IR辐射波具有穿过多层光路的距离。

层间介电(ILD)层269设置在CMOS和MEMS区中的衬底上,覆盖CMOS和MEMS组件。ILD层例如是氧化硅层。其他类型的ILD层或介电层的组合也是可以的。

金属接触件266设置在ILD层中,以接触MEMS区中的MEMS传感器的段。可以通过刻蚀介电层中的沟槽开口并用金属层衬它们以形成接触件。金属层被图案化以形成接触件。电介质衬垫,诸如氧化硅,可以设置在MEMS区中的金属接触件上方。电介质衬垫填充接触件上方的沟槽开口,并衬在CMOS和MEMS区上方的ILD层上。

导电接触插塞,例如钨插塞,设置在ILD层中,并耦合至衬底和MOS组件上的接触区。例如,接触插塞耦合到CMOS组件的S/D区和栅极,以及耦合到用于偏置阱和衬底的阱抽头。接触插塞还例如通过线结构的第一和第二热电堆端子耦合至位于MEMS区的MEMS部件的接触区。为其他类型的接触区提供接触插塞也是可以的。接触插塞例如通过镶嵌工艺形成。电介质衬垫用于保护金属接触件,同时在CMOS区中形成接触插塞。所述电介质衬垫,例如,可视为ILD层的一部分。例如,所述ILD层可以是ILD层的下部,而衬垫可以是ILD层的上部。

后道工序(BEOL)电介质270设置在在ILD层上方的衬底上。例如,BEOL电介质覆盖CMOS和MEMS区。BEOL电介质包括由BEOL介电层形成的多个金属间介电(IMD)层271。IMD层包括通孔介电层272和金属介电层276。IMD层的通孔介电层和金属介电层可以由一个或多个介电层形成,取决于设计和工艺方法。通孔介电层272可以设置在金属介电层276的下方。金属介电层包括金属线277,通孔介电层包括通孔接触件273。在通孔介电层以下设置金属介电层也是可以的。如图所示,第一金属层电介质设置在ILD层上方。BEOL介电层的其他配置也是可以的。

金属线和通孔接触件可以使用镶嵌技术形成,例如单或双镶嵌工艺。在单镶嵌工艺的情况下,接触件和金属线在单独的工艺中形成。在双镶嵌工艺的情况下,金属线和接触件在同一工艺中形成。在一些实施例中,可以通过镶嵌和反应离子刻蚀(RIE)工艺的组合来形成IMD层。例如,金属线可以通过RIE工艺形成,而接触件通过单镶嵌工艺形成。在RIE工艺的情况下,使用刻蚀掩模通过RIE形成金属层并对其进行图案化以形成金属线。应该理解,BEOL电介质的不同IMD层可以使用不同的技术,或技术或工艺的组合来形成。例如,第一IMD层可以使用镶嵌工艺形成接触件,使用RIE工艺形成金属线,中间IMD层可以使用双镶嵌工艺形成,而焊盘层通过用金属过度填充镶嵌开口来形成接触件和焊盘,并对多余的金属进行图案化以形成焊盘。或者,可以通过镶嵌和RIE工艺的组合来形成IMD层。形成IMD层的其他配置也可以。

至于BEOL电介质的顶部金属层,它可以用作具有焊盘金属线的焊盘层。焊盘线可以通过镶嵌或RIE工艺形成。在焊盘线上方形成钝化层。焊盘开口在钝化层中形成至焊盘线的焊盘。用于形成焊盘层的其他方法也可以。

ILD和IMD层可以被平坦化以在CMOS区和MEMS区上方形成平坦的顶表面。例如,在衬底上执行CMP。提供任何其他平坦化技术,例如旋涂玻璃(SOG),以填充间隙或平坦化衬底表面也可以。所述结构上方ILD和IMD层的总厚度可以在100–400nm之间。为所述结构上方的IMD层提供任何其他厚度以限定用于后续标准CMOS工艺的通孔深度也可以。

钝化层278设置在顶部金属层上方。钝化层可以是氮化硅层。可以使用其他类型的钝化层。例如,钝化层可以是具有多个钝化层的钝化堆叠,例如氧化硅层和氮化硅层的组合。顶部IMD层的顶部金属层用作焊盘层。键合开口279设置在盖的外围,以暴露下方的键合焊盘275。键合焊盘提供外部通道访问器件的内部组件。例如,可以经由键合焊盘来提供输入,输出和功率信号。键合焊盘设置在器件的外围。如图所示,键合焊盘设置在器件的一侧,该侧是传感器区的相对侧。键合焊盘也可设置在器件的一个或多个其他侧。

如图所示,BEOL层包括金属层M1,M2和M3。金属层M1是底部金属层,金属层M3是顶部金属层。提供其他数量的金属层也可以。金属层的数量可取决于所采用的CMOS工艺。通常,使用单镶嵌工艺形成ILD层的接触件。例如,形成接触件以耦合至组件的各种端子。接触件可以接触晶体管的S/D区,阱接触和传感器的端子。可以使用单镶嵌或RIE工艺来形成第一IMD层的第一金属层。至于下一通孔层的接触件和下一金属层的金属线,可以通过双镶嵌工艺形成。顶部接触层可以通过单镶嵌工艺形成,且顶部金属层可以通过RIE工艺形成。在某些情况下,可以通过过度填充通孔开口形成顶部金属并图案化多余的金属以形成顶部金属线和键合焊盘。用于形成IMD层的各种接触件和金属线的其他工艺配置也可用。

如图所示,MEMS区中的BEOL电介质材料被去除,从而形成开口265以暴露传感器。所述开口,例如形成BEOL腔。BEOL腔用作位于MEMS器件区的上部器件腔的下部。在提供多个MEMS器件区的情况下,形成多个BEOL腔。MEMS器件区之间的BEOL电介质将BEOL腔隔开。BEOL腔可以是矩形腔。

如图所示,BEOL腔包括垂直侧壁。提供具有非垂直侧壁的BEOL腔也可以。例如,BEOL腔包括锥形阶梯形状,如USSN 16/517,653和USSN10,403,674中所描述的,出于所有目的已将其并入本文作为参考。锥形阶梯形状从顶部向内到底部呈锥状,导致BEOL腔的顶部大于BEOL开口的底部。可以通过使用具有图案化金属线的各个金属层来限定阶梯状腔的形状,所述金属线用作刻蚀掩模以限定BEOL腔的形状。另外,金属层之一也可以用作刻蚀工艺的刻蚀硬掩模,以从膜上图案化线结构。用作线结构刻蚀硬掩模的金属层可以是M1。其他金属层也可以。例如,在使用M1形成线结构的金属接触件的情况下,可以使用M2作为刻蚀硬掩模。在刻蚀工艺之后,去除用作刻蚀硬掩模的金属层部分。

封盖280设置在衬底上,封装MEMS区206。在一个实施例中,所述封盖是CMOS兼容封盖。例如,使用与CMOS工艺兼容的层形成封盖。所述封盖,在一个实施例中,包括IR透明层。IR透明层可配置为用于特定应用。例如,用于热成像的IR透明层可配置为对大约8-12um波长范围内的IR透明。根据应用,提供对其他波长范围的IR或光透明的IR透明层也可以。在一个实施例中,所述封盖包括密封盖,其封装MEMS区并覆盖CMOS区。在一个实施例中,所述封盖气密地密封MEMS器件区,从而在其中提供真空。

在一个实施例中,封盖的MEMS器件区被升高,产生上部器件腔的上部。例如,在MEMS区中的封盖包括围绕MEMS区的外支承壁287。在MEMS区包括多个MEMS器件区的情况下,提供内支承壁288以隔开相邻的器件区。所述外支承壁设置在围绕MEMS区的BEOL电介质上,而所述内支承壁设置在相邻MEMS器件区之间的BEOL电介质上。在一个实施例中,所述封盖配置为单独地气密密封每个MEMS器件区。例如,MEMS器件区由封盖气密密封以形成微型壳体,其包括诸如IR传感器的MEMS器件250,位于将下部和上部器件腔260和265隔开的膜243上。

如图2a所示,位于MEMS器件区上方的封盖的底表面是平坦的。平坦的底表面是由于牺牲层的平坦化,例如通过化学机械抛光(CMP),其填充了上部器件腔。例如,平坦化的牺牲层为上部器件腔265形成平坦顶部。或者,如图2b所示,MEMS器件区上方的封盖的底表面可以是非平坦的。例如,封盖包括凹陷286,在MEMS器件区上方的封盖的底表面中形成形貌。非平坦的底表面是由于在填充上部器件腔的非平坦的牺牲层上形成封盖而引起的。

在一个实施例中,吸气剂层296设置在封盖结构的第一层的内底表面上。吸气剂在封装的器件内吸收水分和脱气。吸气剂层,例如可以是钛(Ti),铁(Fe),镍(Ni),钒(V),钴(Co),铝(Al),钡(Ba),锆(Zr),镁(Mg)。或者,可以为吸气剂层提供诸如Ti/Ni的2层金属膜堆叠。也可以使用其他类型的吸气剂材料,例如稀土元素,包括铈(Ce),镧(La),钍(Th)或铀(U)。吸气剂层有助于维持腔体中真空的完整性,从而提高可靠性。吸气剂层,例如是非红外透明的。这样,吸气剂层被图案化以允许IR穿透封盖至IR传感器。例如,吸气剂层可以被图案化为仅覆盖MEMS器件区外围的封盖的底部,而不会阻挡IR穿过至IR传感器250。如图所示,吸气剂层可以设置在支承壁(内部和外部)的侧面以及封盖的凹陷上(如图2b所示)。

在一个实施例中,在红外感测应用中,MEMS区可包括一个或多个盲像素以及一个或多个有源像素。盲像素,例如用于校准目的。所述盲像素,例如,可以通过使吸气剂层保持未图案化来形成,从而防止IR传输到传感器。为进一步确保没有红外传输到传感器,可以在盲像素器件区上方的封盖上方提供诸如Al的反射金属层。在一个实施例中,所述盲像素可设置在有源像素或像素阵列的边界处。例如,MEMS区可在有源器件区的边界处包括具有非盲像素的有源器件区和具有盲像素的非有源器件区。非有源器件区可以包括单个盲像素或盲像素的线阵列。

如前所述,所述封盖是IR透明盖。例如,在热成像器件中,所述封盖配置为透射大约8-12μm的波长内的IR辐射。所述封盖是与CMOS工艺兼容的封盖。在一个实施例中,封盖包括各种IR透明CMOS兼容层。取决于器件或应用的类型,所述封盖层可配置为对具有其他波长或波长范围的光透明。红外透明层可以包括,例如,硅(Si),诸如非晶硅(αSi)和氧化硅(SiO

在一个实施例中,所述封盖包括下部封盖或底盖281和上部封盖或密封盖284。底盖和密封盖均可以包括一个或多个IR透明层。或者,密封盖可设置有非IR透明层或IR透明层和非IR透明层的组合。在密封盖包括非IR透明层的情况下,对其进行图案化,以免阻止红外光传输到传感器。对于不同的封盖,IR透明层可以不同或相同。可以采用封盖的各种构造。封盖配置为提供足够的机械强度以维持器件的气密密封。例如,封盖可以承受外部或内部的应力,以维持器件的气密性。

在一个实施例中,所述封盖配置为底盖包括至少一个IR透明层,且密封盖包括至少一个IR透明层。底盖和密封盖均可设置一个以上的IR透明层。或者,密封盖还可设置为包括非IR透明层,或非IR透明层和一个或多个IR透明层的组合。底盖和密封盖的其他构造也可以。底盖包括释放开口285,使得释放刻蚀剂能够通过以去除下部和上部器件腔的牺牲层。在释放刻蚀工艺之后,密封盖密封释放开口。在一个实施例中,释放开口足够小以防止密封材料在沉积过程中落在BEOL叠层的顶部。

在一个实施例中,封盖包括七层,五层用于底盖,两层用于密封盖。封盖的其他构造也是可以的。在一个实施例中,底盖的IR层是交替层,密封盖的IR层是交替的IR层。在一个实施例中,底盖的顶层和密封盖的底层是不同的。底盖和密封盖的层的其他构造也可以。

对于底盖的五个交替的IR层,底层和顶层配置为对用于去除下部和上部器件腔牺牲层的刻蚀剂具有抗刻蚀性。在腔的牺牲层为αSi的情况下,底层和顶层可以是SiO

在一个实施例中,除了顶部底盖层284之外,底盖的层是局部MEMS区层,而顶部盖层是整体器件层。底盖层和密封盖层的其他构造也可以。提供除了顶部底盖层之外的局部MEMS区的底盖层,减小了MEMS区外部的封盖的总厚度,有助于更快地形成键合开口,同时保持盖的整体机械稳定性。另外,整体的第五层衬在底盖其他层中释放开口的侧壁,在刻蚀工艺期间用作防止释放刻蚀剂的保护层。例如,顶部底盖层对用于去除腔的牺牲层的刻蚀剂具有抗刻蚀性。

至于密封盖,在一个实施例中,其包括两个密封盖IR透明层。例如,底部密封盖层是αSi,而顶部密封盖层是SiO

如前所述,选择封盖的各个层的厚度以提供IR透明度和机械稳定性。在一个实施例中,盖堆叠包括以下顺序的层和厚度:

第一层:SiO

第二层:α-Si 200nm

第三层:SiO

第四层:α-Si 900nm

第五层:SiO

第六层:α-Si:200nm

第七层:SiO

盖堆叠的其他设置也可以。例如,盖堆叠可以包括其他数量的层,厚度以及IR透明层的类型。

形成盖结构的层,在一个实施例中,可具有均匀或不同的厚度。在一个实施例中,盖结构包括七层交替的非晶硅和电介质材料,并且该材料从底部第一层开始按照以下顺序沉积:400nm氧化硅/200nmα-Si/500nm氧化硅/900nmα-Si/500nm氧化硅/200nmα-Si/400nm氧化硅。这提供总厚度为3.10μm的盖结构,从而允许最大膜应力为25.4MPa的承受力。盖结构的高度可实现约3.35nm的最大向下偏转,从而实现8–12μm之间90%以上的红外波长透射。

BEOL电介质有助于限定形成MEMS器件区的腔体的微型壳体。另外,通过避免高长宽比的刻蚀,BEOL电介质为IR透明盖提供额外的机械强度。此外,由于封盖和BEOL电介质而导致的扩展的上部腔体增强MEMS器件或像素区的长期真空稳定性。

键合开口279设置在盖结构的外围,以暴露下方的键合焊盘275。键合焊盘提供外部通道访问器件的内部组件。例如,可经由键合焊盘提供输入,输出和功率信号。焊盘位于器件的外围。如图所示,键合开口和键合焊盘设置在器件的一侧,该侧是传感器区的相对侧,但是它们也可以设置在器件的一个或多个其他侧,例如,围绕MEMS区的CMOS区。其他设置也可以。例如,键合焊盘可以设置在器件的一侧,2侧或3侧。

图3a-b示出了器件的其他实施例的一部分的简化截面图。参照图3a,示出了器件315a的一部分。该部分示出了器件的MEMS区206。器件的该部分包括如图2a-b中所描述的那些共同元件。共同元件可能不描述或不详细描述。

MEMS区,例如包括MEMS器件区206

第一层:SiO

第二层:α-Si 200nm

第三层:SiO

第四层:α-Si 900nm

第五层:SiO

第六层:α-Si 200nm

第七层:SiO

盖堆叠的其他设置,其他数量的层,厚度以及IR透明层的可选类型也可以。

如图所示,底盖包括第一和第二释放开口285和397。第一释放开口285构造成使得密封盖的层不穿过进入上部腔体中,而第二释放开口构造成与BEOL对准将MEMS器件区隔开。此外,第二释放开口的尺寸构造成允许密封盖层穿过并放置在BEOL电介质上,用作内支承壁388a。例如,第一释放开口的尺寸比第二释放开口的尺寸窄。如图所示,通过一个扩大的第二释放开口形成将两个相邻器件区隔开的内支承壁。

参考图3b,示出了器件315b的另一实施例的一部分。该部分示出了器件的MEMS区206。器件的该部分包括如图2a-b和图3a中所描述的那些共同元件。共同元件可能不描述或不详细描述。

所述MEMS区,例如包括MEMS器件区206

类似于图3a,底盖包括第一和第二释放开口285和397。第一释放开口285构造成使得密封盖的各层不会穿过并进入上部腔,而第二释放开口被构造成与将MEMS器件区隔开的BEOL对准。此外,第二释放开口的尺寸构造成允许密封盖层穿过并放置在BEOL电介质上,用作内支承壁。例如,第一释放开口的尺寸比第二释放开口的尺寸窄。

在一个实施例中,提供多个第二释放开口以在两个相邻的器件区之间形成多个支承壁。例如,提供第一和第二开口397

图4a-b示出了器件的其他实施例的一部分的简化截面图。参照图4a,示出了器件415a的一部分。该部分示出了器件的MEMS区206。器件的该部分包括如图2a-b和3a-b中所描述的那些共同元件。共同元件可能不描述或不详细描述。

MEMS区,例如,包括MEMS器件区206

至于密封盖,其包括图案化的非透明密封盖层492a。所述图案化的非透明密封盖层,例如包括图案化的金属层,该图案化的金属层形成金属柱以密封释放开口。金属层,例如可以是Al。其他类型的金属层也可以。由于金属层的沉积过程(例如溅射或蒸发)是在极高的真空度下进行的,因此形成了真空微型壳体。

参照图4b,示出了器件415b的另一实施例的一部分。该部分示出了器件的MEMS区206。器件的该部分包括如图2a-b,图3a-b和图4a中所描述的那些共同元件。共同元件可能不描述或不详细描述。

所述MEMS区,例如包括MEMS器件区206

底盖包括至少一个IR层。在一个实施例中,底盖包括交替的IR透明层,例如SiO

至于密封盖,其包括下部密封盖和上部密封盖。下部密封盖,在一个实施例中,包括图案化的非透明下部密封盖层492b。图案化的非透明密封盖层,例如包括图案化的金属层,该图案化的金属层形成金属柱以密封释放开口。金属层,例如可以是Al。其他类型的金属层,例如金(Au)或铂(Pt),也可用。

上部密封盖设置在底盖和下部密封盖的图案化金属层上方。所述上部密封盖,在一个实施例中,包括αSi/SiO

图5a-d示出了具有用于具有不同盖构造的器件的其他实施例的一部分的简化截面图。参照图5a,示出了器件515a的一部分。该部分示出了器件的MEMS区206。器件的该部分包括如图2a-b,图3a-3b以及图4a-b中所描述的那些共同元件。共同元件可能不描述或不详细描述。

MEMS区,例如包括MEMS器件区206

至于密封盖,其包括一层IR透明层。在一个实施例中,密封盖层不同于顶部底盖层。在一个实施例中,密封盖层是αSi层。例如,密封盖的αSi层设置在SiO

图5b示出了器件515b的另一实施例的一部分。该部分示出了器件的MEMS区206。器件的该部分包括如图2a-b,图3a-b,图4a-b和图5a中所描述的那些共同的元件。共同元件可能不描述或不详细描述。

MEMS区,例如包括MEMS器件区206

至于密封盖,其包括一层IR透明层。在一个实施例中,密封盖层与底盖层相同。密封盖层可以是ZnS,BaF

对于图5c,其示出了器件515c的另一实施例的一部分。该部分示出了器件的MEMS区206。器件的该部分包括如图2a-b,图3a-b,图4a-b和图5a-b中所描述的那些共同元件。共同元件可能不描述或不详细描述。

MEMS区,例如包括MEMS器件区206

至于密封盖,其包括上部和下部密封盖。在个一实施例中,下部密封盖包括一IR透明层。在一个实施例中,下部密封盖层与底盖层相同。密封盖层可以是ZnS,BaF

关于图5d,其示出了器件515d的另一实施例的一部分。该部分示出了器件的MEMS区206。器件的该部分包括如图2a-b,图3a-b,图4a-b和图5a-c中所描述的那些共同元件。共同元件可能不描述或不详细描述。

MEMS区,例如包括MEMS器件区206

至于密封盖,其包括一个IR透明的ARC堆叠。例如,可以使用ARC堆叠来最小化来自封盖的IR反射。例如,在形成焊盘开口之后,ARC堆叠可以保留在封盖上方。

如图3a-b所示,为所述封盖提供不同构造的内支承壁。例如,内支承壁可以通过密封盖设置。使用密封盖提供内支承壁可以应用于本文描述的各种实施例,例如图2a-b,图4a-b以及图5a-d中的那些。

如图4a-b所示,所述密封盖包括由图案化的金属层形成的金属插塞,以密封释放开口。提供金属插塞作为密封盖可以应用于本文所述的各种实施例,例如图2a-b,图3a-3b以及图5a-d中的那些。

如图5a-d所示,封盖包括不同的构造,例如具有不同数量的层。例如,底盖可以是单层或多层底盖,密封盖可以是单层或多层密封盖。图5a-d的各种盖结构可应用于本文所述的各种实施例,例如图2a-b,图3ab以及图4a-b中的那些。

图6a-d示出了MEMS区的支承壁,吸气剂和释放开口图案600的示例性简化俯视图。MEMS区类似于先前描述的那些。共同元件可能不描述或不详细描述。

参照图6a,示出了MEMS区206。MEMS区包括以2×2矩阵布置的四个MEMS器件区207。例如,矩阵包括在y方向上的2行MEMS器件区和在x方向上的2列MEMS器件区。MEMS区用CMOS兼容封盖封装,气密密封以形成真空。封盖包括围绕MEMS区的外支承壁287和在x和y方向上的内支承壁288,以将MEMS器件区的行和列隔开。在一个实施例中,内支承壁和外支承壁完全隔离MEMS器件区,从而为每个像素形成单独的真空微型壳体。在其他实施例中,在微型壳体之间的内部支承壁中设置开口,从而为整个阵列上的像素产生均匀的真空度。

底盖包括释放开口285。所述开口设置在MEMS IR传感器所在的器件区的外围。这样可以避免干扰传感器。在一个实施例中,释放开口构造成沿着列或y方向位于器件区相对侧的细长槽。释放开口的其他构造也可以。例如,释放开口可以是沿着行或x方向的细长槽。可替代地,释放开口可以沿着相反的x和y方向设置。其他构造可以包括将释放开口布置在器件区的两个相邻侧面或器件区的三个侧面。如图所示,释放开口被设置为连续的细长槽。提供包括多个不连续狭槽的释放开口或包括连续的细长槽和不连续狭槽的组合的释放开口也可以。

封盖的下方是吸气剂290。所述吸气剂被配置为避免像释放开口一样干扰传感器的IR接收。这样,吸气剂配置为围绕传感器区650。在一个实施例中,吸气剂围绕传感器区的所有四个侧面。例如,除释放开口之外,吸气剂可以设置在封盖的底或内表面上,包括外和内支承壁的侧面和底部。

支承壁的图案可以由器件腔上方BEOL的上方牺牲层的图案定义。例如,牺牲层的图案决定外支承壁和内支承壁的构造。支承壁可以由围绕MEMS区(外支承壁)的牺牲层的凹陷图案限定,且在牺牲层图案中围绕MEMS器件区(内支承壁)的MEMS区内。围绕MEMS区和MEMS器件区的凹陷图案可以是连续的,以形成单独的微型壳体。在一个实施例中,围绕MEMS区的凹陷图案是连续的,而限定单个MEMS器件区的凹陷图案可以是不连续的。

图6b示出了MEMS区206的另一实施例。MEMS区类似于图6a中所描述的。共同元件可能不描述或不详细描述。MEMS区包括以2×2矩阵布置的四个MEMS器件区207。MEMS区用CMOS兼容封盖封装。所述封盖包括围绕MEMS区的外支承壁287和在x和y方向上的内支承壁388a,以隔开MEMS器件区的行和列。在一个实施例中,内支承壁和外支承壁完全隔开MEMS器件区,从而为每个像素形成单独的真空微型壳体。例如,相邻像素共用相同的内支承壁。

在一个实施例中,使用密封盖通过第二释放开口397形成内支承壁。例如,第二释放开口构造成具有比第一释放开口更大的尺寸,从而允许密封盖穿过并放置在像素之间的BEOL电介质上,以形成内支承壁。如图所示,第二释放开口是连续的细长开口,其在MEMS器件区或像素区之间沿x和y方向完全延伸至外支承壁的相对侧。第二释放开口彼此交叉。这形成内支承壁,其完全隔开MEMS器件区,从而为每个像素形成单独的真空微型壳体。

在某些情况下,可以使用混合内支承壁。例如,混合内支承壁既包括底盖又包括密封盖作为支承壁。其可通过为牺牲层定义适当的图案而很容易地构造。例如,可以在底盖用作内支承壁的位置设置凹陷,而在密封盖用作内支承壁的位置不设置凹陷。在混合内支承壁的情况下,第二开口可以是不连续的开口。

封盖的下方是吸气剂290。吸气剂配置成避免像释放开口一样干扰传感器对IR的接收。这样,吸气剂配置为围绕传感器区650。在一个实施例中,吸气剂围绕传感器区的所有四个侧面。例如,吸气剂可以设置在封盖的底或内表面上,包括外和内支轴承壁的侧面和底部,除释放开口之外。

在图6c中,示出了MEMS区206的另一实施例的简化俯视图600。MEMS区类似于图6a-b中所述。共同元件可能不描述或不详细描述。MEMS区包括以2×2矩阵布置的四个MEMS器件区207。MEMS区用CMOS兼容封盖封装。封盖包括围绕MEMS区的外支承壁287和在x方向和y方向上的内支承壁288,以将MEMS器件区的行和列分开。在一个实施例中,内支承壁构造为在MEMS器件区之间提供通道,从而为MEMS区产生均匀的真空度。

在一个实施例中,使用密封盖通过第二释放开口397形成内支承壁388a。例如,第二释放开口构造成具有比第一释放开口更大的尺寸,从而允许密封盖穿过并放置在像素间的BEOL电介质上,以形成内支承壁。如图所示,第二释放开口是不连续的细长开口。例如,第二释放开口彼此不交叉。第二释放开口由外支承壁朝向MEMS器件区的相对侧延伸,而不彼此交叉。这形成了在MEMS器件区之间具有通道的内支承壁,从而为整个MEMS区的MEMS器件区产生均匀的真空度。

内支承壁的其他构造或设计也是可用的。例如,如图所示,内支承壁是连续的内支承壁,该内支承壁由沿x或y方向的两个相邻的MEMS器件区共用,而不穿过或延伸到其他器件区。然而,内支承壁可以是沿着x或y方向的两个相邻的MEMS器件区之间的不连续的内支承壁。提供不完全密封MEMS器件区的混合内支承壁也可以。

封盖的下方是吸气剂290。吸气剂配置为避免像释放开口一样干扰传感器接收IR。这样,吸气剂配置为围绕传感器区650。在一个实施例中,吸气剂围绕传感器区的所有四个侧面。例如,除释放开口之外,吸气剂可以设置在封盖的底或内表面上,包括外和内支承壁的侧面和底部。

图6d示出了MEMS区206的另一实施例的简化俯视图600。MEMS区类似于图6a-c中所描述。共同元件可能不描述或不详细描述。MEMS区包括以2×2矩阵布置的四个MEMS器件区207。MEMS区用CMOS兼容封盖封装。该封盖包括围绕MEMS区的外轴承壁287和在x方向和y方向上的内轴承壁,以分隔MEMS器件区的行和列。在一个实施例中,内支承壁配置为在MEMS器件区之间提供通道,从而为MEMS区产生均匀的真空度。

使用密封盖通过第二释放开口形成内支承壁。例如,第二释放开口构造成具有比第一释放开口更大的尺寸,从而允许密封盖穿过其中并且放置在像素之间的BEOL电介质上以形成内支承壁。在一个实施例中,MEMS器件区的沿y方向的内支承壁包括通过第二释放开口397

封盖的下方是吸气剂290。吸气剂配置为避免像释放开口一样干扰传感器接收IR。这样,吸气剂配置为围绕传感器区650。在一个实施例中,吸气剂围绕传感器区的所有四个侧面。例如,除释放开口之外,吸气剂可以设置在封盖的底或内表面上,包括外和内支承壁的侧面和底部。

图7a示出了MEMS传感器或结构750的实施例的简化俯视图,并且图7b示出了沿A-A’,B-B’和C-C’的MEMS结构的各种截面图。俯视图不包括保护层。MEMS结构是线结构。线结构是用作热电IR传感器或探测器的热电堆。线结构设置在限定下部器件腔顶部的膜或介电层上。线结构,在一个实施例中,包括具有弯曲形状并占据膜表面的单个线单元(N=1)。

在一个实施例中,线单元包括多晶硅。其他类型的线单元也可以。例如,可以采用在高温下稳定的热电材料来形成线结构。这样的材料可以,例如包括SiGe,GaN和2D材料,诸如石墨烯,黑磷或硫化钼。

线单元包括第一和第二线段720和740。第一端751是第一线段的一部分,而第二端752是第二线段的一部分。在一个实施例中,第一端和第二端可以用作热电堆的冷结。第一线结构端子754设置在第一端,第二线结构端子756设置在第二端。所述端子,例如是线结构的线单元的一部分。所述端子用作MEMS结构或传感器的端子。

在一个实施例中,第一线段掺杂有第一极性类型的掺杂剂,第二线段掺杂有第二极性类型的掺杂剂。例如,第一线段重掺杂有第一极性类型的掺杂剂,第二线段重掺杂有第二极性类型的掺杂剂。第一极性类型可以是p型,第二极性类型可以是n型。提供n型的第一极性类型和p型的第二极性类型也可用。掺杂可以集成到形成S/D区和阱接触的注入中。与形成S/D区和阱接触的注入分开掺杂线段也可以。

可以使用掩模和刻蚀技术来图案化线结构。例如,将光刻胶设置在线结构层上。光刻胶可以由曝光源通过包含期望的线结构图案的掩模版曝光。显影后,掩模版的图案转移到光刻胶上以形成刻蚀掩模。使用刻蚀掩模利用刻蚀来图案化线结构层以形成线结构。刻蚀掩模,例如可以是光刻胶掩模。所述刻蚀,例如是各向异性刻蚀,例如反应离子刻蚀(RIE)。其他刻蚀工艺也可以。在一个实施例中,刻蚀形成具有第一和第二线段的线结构。或者,所述线结构可以是具有例如第一和第二段的非连续线结构。所述第一段和第二段可以通过金属接触件电连接。如果将线结构集成到栅电极层中,则可以将用于图案化栅极的掩模用于图案化线结构。可选地,可以使用分开的掩模和刻蚀工艺来图案化栅极和线结构。

如图所示,所述线段是彼此的镜像。这产生大约相同长度的线段。通过为线段提供弯曲设计,可以有效地使用传感器区,同时产生具有期望电阻的线结构。例如,线结构的电阻约为5–50kΩ。其他电阻也可用。

为了掺杂第一和第二线段,可以使用分开注入。例如,使用第一注入掩模的第一注入用于掺杂第一线段,使用第二注入掩模的第二注入用于掺杂第二线段。在线段的掺杂集成到S/D注入中的情况下,注入掩模可以是用于p型和n型S/D注入的掩模。

线介电层758覆盖线结构,填充间隙。线介电层为热电堆膜提供机械支撑。线介电层可以是自平坦化介电层,例如旋涂玻璃(SOG)。其他类型的自平坦化电介质材料也可用。介电层的顶表面可能比线结构的顶部高100-400nm。在线结构的顶部上方提供具有其他厚度的介电层也可以。

提供接触件766以电耦合第一段和第二段。所述接触件,例如是金属接触件,例如钛(Ti)或铝(Al)。其他类型的接触件也可以。为了形成接触件,在介电层中形成接触开口,以在第一段和第二段的接合点附近暴露线结构。在衬底上形成金属层并对其进行图案化,保留耦合第一段和第二段的接触件。所述金属层,例如可以是通过溅射或电镀形成的钛(Ti)或铝(Al)。其他类型的金属层或形成技术也可用。在其他实施例中,接触件可以通过镶嵌技术形成。例如,在介电层中形成通孔开口。形成导电层,填充通孔开口并覆盖介电层。执行诸如CMP的平坦化工艺以在通孔开口中形成金属接触件,从而连接线结构的第一和第二段。

在所述衬底上形成吸收层757,覆盖介电层。可以使用刻蚀和掩模工艺来图案化吸收层。图案化的吸收层用作线结构上方的吸收体。在一个实施例中,吸收层被图案化,覆盖线结构的中央部分和接触件,而使中央部分外部的支腿部分暴露。吸收层,例如吸收IR辐射。吸收层可以是TiN或NiCr层。吸收层,例如可以通过溅射形成。其他类型的吸收层也是可用的。在一个实施例中,吸收体配置成吸收大部分IR辐射。例如,吸收体可以配置为吸收超过85%的波长8-14μm的IR辐射。吸收其他波长也可以。如图所示,吸收层设置在接触件上方。吸收体用作热电堆的热结。第一线结构的第一端751和第二线结构的第二端752用作热电堆的冷结。吸收体未覆盖的线结构的支腿部分在热结和冷结之间提供热隔离。

可以提供保护层759。保护层,例如覆盖MEMS结构。保护层保护MEMS结构不受后续工艺的影响。该保护层,例如是通过CVD形成的氧化硅层。其他类型的保护层也可用。保护层可以是金属层和金属接触件之间的介电层。例如,保护层可以是M1(接触件)和M2之间的介电层。金属层和保护层的其他构造也可以。

在一个实施例中,保护层形成设置在BEOL介电层下方的ILD层的第一接触层的上部。对形成腔顶部的保护层,线介电层和膜进行图案化以形成开口755,从而将支腿与线结构的中央部分隔开。开口提供通向腔体的通道。这使得能够去除腔体中的牺牲填充物,从而释放线结构。在一个实施例中,可以对BEOL电介质中的金属层之一进行图案化以用作线结构刻蚀硬掩模,以对各个层进行图案化形成开口755释放线结构。例如,金属层可以是M1或M2。其他金属层也可以用作释放刻蚀工艺的刻蚀掩模。

图7c示出了MEMS结构750的另一实施例的俯视图,图7d示出了基于图7c的MEMS结构俯视图的MEMS结构的横截面图。横截面图沿A-A',B-B'和C-C'表示。MEMS结构是形成用作热电IR传感器的热电堆的线结构。俯视图不包括保护线结构的保护层。线结构与图7a-7b中描述的相似。共同元件可能不描述或不详细描述。线结构设置在构成腔体的膜上。

与图7a-7b相比,线结构具有更多的曲折或弯曲,以增加占据膜表面的段的长度。这增加了线结构的电阻。以增加或调整段的长度以实现期望的电阻的用于线段的其他设计也可用。

在一个实施例中,MEMS结构是具有N个线单元的多线单元线结构,所述N个线单元串联耦合以形成热电IR传感器。如图所示,MEMS结构包括第一和第二线路单元750

如前所述,所示的线结构包括第一和第二线单元。在一个实施例中,多线单元线结构的线单元是堆叠式线单元。第一堆叠式线单元和第二堆叠式线单元可以在传感器区内的介电层上彼此相邻地布置。如图所示,传感器区的中心用作第一和第二线单元750

堆叠式线单元包括设置在第一线层771中的第一段(720

接触件(766

在一个实施例中,线单元的第一线段掺杂有第一极性类型的掺杂剂,线单元的第二线段掺杂有第二极性类型的掺杂剂。例如,第一层中的线单元的第一段掺杂有第一极性类型的掺杂剂,而第二层中的线单元的第二段掺杂有第二极性类型的掺杂剂。第一极性类型可以是n型,第二极性类型可以是p型。掺杂线段的其他设置也可用。

如图所示,第一线单元具有第一端和第二端751

第一吸收层7571和第二吸收层7572设置在第二线介电层7582上方的衬底上。如图所示,这些层覆盖传感器区的中央部分,包括第一和第二接触件的接触区。例如,第一吸收体覆盖传感器区的中央部分和第一线单元的第一接触区,第二吸收体覆盖传感器区的中央部分和第二接触区。由于第一和第二吸收层是导电的,因此它们是不同的吸收层。

吸收层,例如吸收IR辐射。吸收层可以是TiN或NiCr层。其他类型的吸收层也是可用的。在一个实施例中,吸收体配置成吸收大部分IR辐射。例如,吸收体可以配置为吸收超过85%的波长8-14μm的IR辐射。吸收其他波长也可用。如图所示,吸收层设置在接触件上方。吸收体用作热电堆的热结。线单元的第一线段的第一端751

形成堆叠式线结构的工艺可以包括,例如在衬底上形成第一线段层,包括在传感器膜介电层上方和腔体上方的传感器区中。在一个实施例中,通过CVD在衬底上形成多晶硅层。图案化第一线段层以形成第一和第二线单元的不同的第一线段720

通过CVD在第一层间线介电层上形成第二线段层,例如多晶硅,并使用掩模和刻蚀技术对其进行图案化以形成第一和第二线单元的不同的第二线段740

在衬底上形成第二层间线电介质衬垫758

在衬底上形成吸收层,覆盖第二层间线介电层和接触件。吸收层,例如是通过溅射形成的导电层。使用掩模和刻蚀技术,图案化吸收层,以在传感器区的中央部分形成不同的第一吸收层757

可以提供保护层759。保护层例如覆盖MEMS结构。保护层保护MEMS结构不受后续工艺的影响。所述保护层,例如是通过CVD形成的氧化硅层。其他类型的保护层也可用。

对形成腔顶部的保护层,线介电层和膜进行图案化以形成开口755,从而将支腿与线结构的中央部分隔开。例如,执行图案化工艺以形成线结构的线单元。所述开口提供通向腔体的通道。这使得能够去除空腔中的牺牲填充物,从而释放线结构。图案化工艺的掩模,在一个实施例中,可以由BEOL电介质的金属层提供。例如,该掩模可以由BEOL电介质的M1或M2提供。在其他实施例中,掩模可以是图案化的抗蚀剂掩模。

如前所述,第一和第二线单元750

如前所述,线单元的线段设置在相同线层并且掺杂有相同的掺杂剂类型。这允许使用单个注入工艺(例如,使用单个注入掩模的相同注入工艺)来掺杂线单元的线段。在替代实施例中,相同线层中的线单元的线段可以掺杂有相反极性类型的掺杂剂。在这种情况下,通过分开的注入工艺(例如,使用不同的注入掩模的不同注入工艺)来掺杂线段。这样,在相同的线层提供具有相同掺杂类型的线单元的线段减少了使用额外的注入掩模的需要。用于线单元的线段的其他配置也可用。

如前所述,MEMS结构包括堆叠并串联耦合的2个线单元。堆叠其他数量的串联耦合的线单元也可以。优选地,堆叠线单元的线结构具有类似的设计。但是,可以理解,这不是必需的。另外,线单元或结构可以具有除图7a-7d中所描述的之外的布局。

图7e示出了传感器阵列704。传感器阵列包括多个传感器单元710。传感器单元包括耦合至MEMS结构的开关,所述MEMS结构例如是图7a-7d中所描述的线结构。共同元件可能不描述或不详细描述。

所述传感器单元构造成形成具有Y行和Z列的阵列。传感器单元对应于传感器阵列的像素。传感器单元通过行线(RLm)在行方向上耦合,并且通过列线(CLn)在列方向上耦合。传感器单元可以对应于像素。此外,公共线(Coms)也用于耦合每列中的传感器单元。例如,传感器的每一列耦合到各自的Com(例如,Com

传感器阵列的像素可以包括以矩阵布置在衬底上的多个传感器。例如,每个像素可以包括传感器区和CMOS开关或连接区。传感器区设置在,例如,衬底的传感器阵列区中。例如,传感器阵列区包括对应于传感器像素的多个传感器区。

在一个实施例中,传感器单元的MEMS结构的第一端子耦合至开关795,而第二端子耦合至公共线(Com)。如图所示,传感器单元的每一列耦合到各自的Com(例如,Com

在一个实施例中,传感器阵列配置为读出一行传感器单元或像素。例如,一次读出一行阵列的像素。在一个实施例中,选择阵列的RL。这样选择一行像素。然后选择CL,从而使得所选择的RL的像素被读出。在一个实施例中,阵列配置为从第一行到最后一次读出一行像素。读出的信息存储在存储器中。读取所有像素或扫描完所有行后,将生成图像或成像仪的帧。例如,可以重建存储在从像素读出的存储中的信息以形成图像。

在图7e中的2×3阵列的情况下,扫描像素以形成图像可以包括选择RL

图8a-r示出了用于形成器件800的工艺的实施例的简化横截面图。该器件,例如类似于图2a中所描述的。共同元件可能不描述或不详细描述。

参照图8a,提供了衬底801。所述衬底,例如可以是半导体衬底,例如硅衬底。其他类型的衬底或晶片也可用。例如,衬底可以是硅锗,锗,砷化镓,或诸如绝缘体上硅(SOI)的绝缘体上晶体(COI)衬底。衬底可以是掺杂的衬底。例如,衬底可以轻掺杂有p型掺杂剂。为衬底提供其他类型的掺杂剂或掺杂剂浓度,以及未掺杂的衬底也可以。

所述衬底,如图所示,制备有第一和第二器件区域804和806。第一区域是CMOS区,而第二区域是MEMS区。CMOS区设置为包括CMOS组件,而MEMS区设置为包括一个或多个MEMS组件。如图所示,CMOS区包括第一和第二CMOS器件区805

对于MEMS区,如图所示,其包括第一和第二MEMS器件区807

加工衬底以形成用于MEMS器件区的下部器件腔860。例如,在每个MEMS器件区的衬底中形成下部器件腔。可以通过使用掩模和刻蚀工艺刻蚀衬底来形成器件腔。掩模和刻蚀工艺可以使用具有对应于下部器件腔的开口的图案化掩模来刻蚀衬底。掩模可以是硬掩模,例如氧化硅掩模;或软掩模,例如光刻胶掩模。刻蚀,例如是各向异性刻蚀,例如反应离子刻蚀(RIE),其刻蚀衬底以形成下部器件腔。

如图8b所示,IR反射体841形成在下部器件腔的底部。例如,IR反射体形成在所述下部器件腔的底部上。在一个实施例中,反射体是形成在下部器件腔底部的金属硅化物层。金属硅化物反射体可以是硅化钛(TiSi

为了形成金属硅化物反射体,在衬底上形成导电金属层。导电金属层可以衬在衬底的表面和下部器件腔的底部。在一个实施例中,保留用于形成衬底的掩模。这样,导电金属层覆盖衬底表面上的掩模。在光刻胶掩模的情况下,在沉积导电金属层之后将其去除。这样去除了掩模上的导电金属层,留下覆盖第一和第二下部器件腔底部的导电金属层的一部分。进行退火,从而使导电金属与腔底部的硅衬底之间发生反应,以形成金属硅化物层。在硬掩模的情况下,不去除衬底上的金属层。硬掩模可防止与衬底发生反应。退火后,去除未反应的金属和硬掩模。可以使用第一湿法刻蚀来去除未反应的金属和硬掩模。

可替代类型的反射体也可以形成在下部器件腔的底部。在另一个实施例中,反射体是腔体底部处的掺杂区。例如,可以使用形成下部器件腔的掩模来进行注入。该注入掺杂下部器件腔的底部以形成反射体。反射体掺杂剂可以是n型或p型。为以期望的反射度反射IR辐射而相应地选择反射体的掺杂剂浓度。例如,掺杂的反射层的掺杂剂浓度可以为约10

在其他实施例中,反射体可以是非导电反射体,例如光子晶体反射体。例如,通过刻蚀下部器件腔的表面来形成光子晶体层。光子晶体层可以包括设置以反射入射的IR辐射的光栅图案。例如,可以从光子晶体层的表面刻蚀出深度不同的不同光栅图案,以调节反射的IR辐射的波长和特性。光子晶体层可以包括设置以反射入射辐射的光栅图案。形成其他类型的反射体也可以。

参照图8c,形成反射体之后,在衬底上形成反射体保护衬垫844。例如,保护衬垫用于保护反射体免受在释放工艺中用于形成下部器件腔的刻蚀剂(例如XeF

在衬底上形成牺牲层861。牺牲层覆盖衬底并填充下部器件腔。可以选择性地去除牺牲层而不损坏保护衬垫。在一个实施例中,牺牲层是非晶硅层。其他类型的牺牲材料也可以用作牺牲层。牺牲层可以通过CVD形成。去除衬底上多余的牺牲材料。例如,采用诸如化学机械抛光(CMP)之类的平坦化工艺来去除多余的牺牲材料。在一个实施例中,CMP去除多余的牺牲材料以及覆盖衬底表面的保护衬垫。CMP在衬底和腔体中的牺牲层上形成平坦的顶表面。其他类型的平坦化工艺也可用。例如,使用一个或多个掩模的回蚀工艺也可以。

在衬底上形成介电层842。电介质可以是氧化硅层。也可以形成其他类型的介电层。对介电层进行图案化,使其保留在MEMS区上方。例如,介电层覆盖下部器件腔,在处理CMOS区时保护MEMS区。介电层还限定下部器件腔的顶部,并且用作MEMS传感器的膜或膜的至少一部分。介电层可以通过CVD形成并且可以使用掩模和刻蚀工艺来图案化。

参照图8d,加工CMOS区。例如,在衬底上执行前道(FEOL)工序工艺。加工衬底的CMOS区以在第一CMOS器件区805

在一个实施例中,在第一和第二晶体管区形成第一和第二晶体管阱。对于n型MOS晶体管,第一晶体管阱可以是p型阱,对于p型MOS晶体管,第二晶体管阱可以是n型阱。所述阱,例如,可以通过使用注入掩模的离子注入形成。注入掩模可以是光刻胶注入掩模,其被图案化以提供用于注入区的开口。采用单独的注入工艺形成p型和n型阱。

可以在衬底上形成隔离区以隔离衬底的不同区域。隔离区,例如,也可以被提供用于阱接触区。隔离区例如是场氧化物(FOX)隔离区。FOX区可以通过使用氮化物掩模对衬底进行选择性热氧化形成。其他类型的隔离区也可用。例如,隔离区可以是浅沟槽隔离(STI)区。STI区是在衬底中形成的沟槽,并填充有电介质材料,例如氧化硅。STI区可以与通过CMP生成的衬底具有共面的顶表面。在一个实施例中,在掺杂剂注入之前形成STI区,以防止硅的掺杂影响其生长。

在衬底上形成栅极层。在一个实施例中,栅极层包括栅极介电层和栅电极层。栅极介电层可以是热氧化物层,而栅电极层可以是多晶硅层。可以通过CVD形成栅电极层。栅电极层,例如覆盖CMOS和MEMS区中的衬底。图案化栅电极层以在晶体管区形成栅极。可以使用掩模和刻蚀技术来图案化栅电极层。例如,使用图案化的抗蚀剂掩模通过RIE来图案化栅电极层。栅极包括在栅极电介质上方的栅电极。

在一个实施例中,对栅电极层进行图案化以在晶体管区中形成栅极,并在MEMS器件区中形成MEMS结构。MEMS结构可以配置为在传感器阵列中形成多个IR传感器。MEMS结构可以是用作热电传感器的热电堆结构,如图7a-e所示。其他类型的MEMS结构也可用。

在形成MEMS结构的工艺中,可以在MEMS区上方形成一个或多个介电层或843,并对其进行图案化以用作膜。一个或多个附加层可以是该工艺的一部分或有意添加。如图所示,所述膜是用于MEMS器件区的连续膜。膜的其他构造也可用。例如,介电层可以被图案化以形成用于每个MEMS器件区的单独的膜。

在替代实施例中,以单独的工艺形成MEMS结构。例如,可以在形成栅极之前或之后形成MEMS结构。在这种情况下,在衬底上形成MEMS结构层并对其进行图案化以形成线结构。MEMS结构层可以是多晶硅。其他类型的MEMS结构层也可用。例如,MEMS结构层可以是硅锗(SiGe),氮化镓(GaN)或2D材料,诸如石墨烯,黑磷或硫化钼。

在使用单独的工艺形成MEMS结构的情况下,CMOS区可以由硬掩模层保护。硬掩模层,例如可以是介电层,诸如氧化硅或氮化硅层。可以对硬掩模层进行图案化以暴露MEMS区,而使CMOS区受到保护。硬掩模层可以用作刻蚀停止层。其他类型的硬掩模层也可用。硬掩模层使得能够在MEMS区中对MEMS结构层进行图案化,同时保护CMOS区。在形成MEMS结构之后,可以去除硬掩模层。

晶体管的源极/漏极(S/D)区与栅极相邻地形成。S/D区是重掺杂区。例如,第一晶体管包括重掺杂的n型S/D区,而第二晶体管包括重掺杂的p型S/D区。当形成S/D区时,也可以形成阱抽头。可以为S/D区提供轻掺杂的延伸区。电介质侧壁间隔物可以形成在栅极的侧壁上,以有助于轻掺杂延伸区的形成。

在一个实施例中,轻掺杂的延伸区与栅极相邻地形成。p型轻掺杂延伸区与p型晶体管的栅极相邻地形成,n型轻掺杂延伸区与n型晶体管的栅极相邻地形成。可使用诸如光刻胶掩模的注入掩模来利用单独的注入形成不同类型的轻掺杂延伸区。

在形成延伸区之后,在衬底上形成间隔物介电层。间隔物介电层可以是氧化硅层。其他类型的间隔物介电层也可用。进行各向异性刻蚀,去除间隔物介电层的水平部分,保留栅极侧壁上的间隔物。P型S/D区与P型晶体管的栅极相邻地形成,N型S/D区与N型晶体管的栅极相邻地形成。可使用诸如光刻胶掩模的注入掩模来利用单独的注入以形成不同类型的S/D区。

在一个实施例中,用以形成S/D区的注入也用于形成线结构的掺杂段。例如,用于形成p型S/D区的p型注入也形成线结构的p型段,而用于形成n型S/D区的n型注入也形成线结构地n型段。使用与用于形成S/D区的注入分开的注入来形成线结构的掺杂段也可用。

在其他实施例中,如前所述,可以在MEMS区中形成堆叠式线单元。形成堆叠式线单元可以与用以形成CMOS组件的工艺(CMOS工艺)分开。部分或完全地结合用于形成堆叠式线单元的CMOS工艺也可以。例如,这可能取决于所采用的CMOS工艺。形成CMOS组件和MEMS结构的其他设置也可用。

可以在衬底上形成金属硅化物接触件。例如,可以在S/D区,栅极和阱接触上形成金属硅化物接触件。金属层,诸如Ti,W或Al,可沉积在衬底上并进行退火,以引起金属和硅之间的反应形成金属硅化物接触件。未反应的金属通过例如湿法刻蚀去除,从而保留金属硅化物接触件。

在图8e中,在衬底上方形成ILD层。ILD层包括将第一介电层858设置在衬底上方。在一个实施例中,介电层覆盖CMOS和MEMS区。例如,介电层覆盖晶体管和MEMS结构。介电层用作第一通孔的一部分或ILD层的接触层。介电层可以是通过CVD形成的氧化硅。其他类型的介电层也可以。进行诸如CMP的抛光工艺以产生介电层的平坦顶表面。该平坦顶表面在传感器和晶体管上方。提供任何其他平坦化技术,例如旋涂玻璃(SOG)以填充间隙或平坦化衬底表面也可用。

参照图8f,形成热电偶接触件866。接触件构造为耦接线结构的第一和第二段。例如,接触件形成热电偶,其耦合布置在下部器件腔上方的膜843上的线结构850的线段。形成接触件可以包括在介电层中形成通孔开口。通孔开口暴露线结构的第一和第二线段。在衬底上沉积金属接触层。金属接触层,例如可以是钛(Ti)或铝(Al)。图案化金属层以形成接触件。如图所示,接触件衬在通孔开口处并覆盖与通孔开口相邻的介电层的顶表面的一部分。

在图8g中,ILD的形成继续进行,在衬底上沉积吸收层。吸收层覆盖介电层和热电偶。在一个实施例中,吸收层是TiN或NiCr吸收层。其他类型的吸收层也是可用的。吸收层可以通过例如溅射形成。吸收层可以使用其他技术形成。在一个实施例中,例如,调节吸收体的厚度以形成具有约377Ohm/sq的薄层电阻的层。为吸收体提供任何其他厚度和薄层电阻也可以。图案化吸收层以在MEMS区中的热电堆结构上方形成吸收体857。可以通过掩模和刻蚀技术来图案化吸收体。

第二介电层859形成为ILD层的一部分。第二介电层859形成在衬底上方,介电层覆盖吸收体和第一介电层858。第二介电层还填充吸收层上方的开口。第二介电层,例如是通过CVD形成的氧化硅。第二介电层用作ILD层的第一通孔层的上部。可以沉积介电层,填充由衬在通孔开口的接触件形成的开口。可以执行诸如CMP的平坦化工艺以在吸收体的顶部与第二介电层之间提供平坦的顶表面。

如前所述,形成单线结构的阵列。该工艺可以用来形成多个线结构,其堆叠且串联地耦合以形成堆叠式线结构,例如先前所述。例如,可以执行使用掺杂的附加线结构层,介电层和掺杂剂注入。另外,如图7e所示,可以形成堆叠式线结构以提供传感器阵列。形成其他类型的MEMS结构也可以。第一和第二介电层,例如用作ILD层的第一接触件或通孔介电层872。

如图8h所示,该工艺包括在第一通孔介电层872中形成接触件873。接触件耦合到CMOS和MEMS区中的各个端子。例如,接触件耦合到S/D区,栅极和阱接触。另外,提供接触件873用于MEMS结构或传感器端子。接触件可以是钨接触件。其他类型的接触件也可以。接触件例如通过单镶嵌技术形成。单镶嵌技术包括形成通孔,用接触层填充通孔以及抛光(例如CMP)以去除多余的接触材料。使用其他技术形成接触件也可以。

在图8i中,BEOL工艺开始。在一个实施例中,形成具有金属层的BEOL电介质870和IMD层871。例如,具有金属线877的第一金属层876形成在IDL层上方。随后在第一金属层上方形成第一IMD层以及其他IMD层。如前所述,通孔介电层包括通孔接触件873,而金属介电层包括金属线877。金属线和通孔形成器件的互连件。如图所示,BEOL电介质包括2个IMD层。可以为BEOL电介质提供其他数量的IMD层。最上层的金属层包括键合焊盘,并用作焊盘层。钝化层878形成在最上层的金属或焊盘层上方。钝化层,例如是氮化硅。在一些实施例中,钝化层可以是具有多个钝化层的钝化堆叠。例如,钝化堆叠可以包括氧化硅和氮化硅层。其他类型的钝化层也可用。钝化层可以通过CVD形成。

参照图8j,对BEOL电介质图案化以在MEMS器件区中形成BEOL腔864,以通过例如第一通孔层电介质和膜暴露传感器850和下部器件腔释放开口845。可以采用两步工艺。例如,第一工艺形成下部器件腔释放开口,而第二工艺形成BEOL腔。使用掩模和刻蚀技术来执行工艺。形成下部器件腔释放开口和BEOL腔的其他设置也可用。

在一个实施例中,对诸如光刻胶的刻蚀掩模进行处理以在BEOL电介质中限定开口以用于下部器件腔释放开口。RIE刻蚀穿过BEOL,并在第一接触层电介质和膜中限定下部器件腔开口。在限定了下部器件腔释放开口之后,去除刻蚀掩模。在衬底上形成另一刻蚀掩模。处理第二刻蚀掩模,以限定用于BEOL腔的开口。执行RIE以形成BEOL腔。

BEOL腔用作上部器件腔的下部。在一个实施例中,在BEOL电介质上方形成刻蚀掩模869,例如光刻胶层。图案化光刻胶层以提供对应于BEOL腔的开口。执行RIE以刻蚀BEOL介电层,形成BEOL腔。如图所示,去除MEMS器件区中的BEOL电介质材料以暴露传感器。BEOL腔被BEOL隔开,从而为MEMS器件区形成单独的BEOL腔。腔体可以具有矩形的开口。在一个实施例中,BEOL腔具有由掩模限定的垂直侧壁。应当理解,由于刻蚀工艺条件,腔体侧壁可能不完全垂直。此外,可以调整刻蚀工艺以形成倾斜的侧壁。例如,随着刻蚀的进行,可以调整刻蚀以在侧壁上从抗蚀剂沉积聚合物,从而形成倾斜的侧壁。

在替代实施例中,BEOL腔开口可具有通过IMD层中的金属图案促进的侧壁轮廓。腔的侧壁轮廓可以是阶梯形轮廓。其他类型的轮廓也可以。该轮廓,例如可以由BEOL电介质的各个层中的金属环限定。金属环,例如是矩形的金属环,并且可以构造为从上到下连续变小,从而形成阶梯状轮廓。其他轮廓也可以。金属环可以在金属层,环层或它们的组合中形成。例如,使用刻蚀掩模形成BEOL腔,IMD层中的金属图案限定BEOL腔轮廓。

如图8k所示,为简单起见,示出了MEMS区806的横截面图。在形成BEOL腔之后,去除刻蚀掩模。在一个实施例中,在介电层上方形成第一BEOL牺牲层892,并填充BEOL腔且覆盖BEOL介电层。所述牺牲层可以与填充下部器件腔的牺牲层相同。例如,牺牲层可以是非晶硅(α-Si)层。也可以将其他类型的牺牲材料用于牺牲层,该牺牲层可以选择性地去除至BEOL电介质。牺牲层可以通过CVD形成。衬底上多余的牺牲材料被去除。例如,采用诸如化学机械抛光(CMP)的平坦化工艺来去除多余的牺牲材料。采用其他平坦化技术也可以。平坦化工艺在牺牲层和BEOL电介质之间形成平坦表面。

在图8l中,在衬底上方形成第二或附加的BEOL牺牲层893。第二BEOL牺牲层可以被图案化以成形上部器件腔的上部。如图所示,对附加的BEOL牺牲层进行图案化,以形成用于MEMS器件区的单独的微型壳体,如前所述。对附加的BEOL牺牲层进行图案化以在微型壳体中形成开口,从而为器件区产生均匀的真空度,如前所述,也可用。

在一个实施例中,图8k的牺牲层可以充分过填充并且平坦化,以保留用作附加牺牲层的附加牺牲材料。这避免了形成附加牺牲层的附加沉积工艺。在另一个实施例中,牺牲层没有进行平坦化,从而产生如图2b所示的腔体轮廓。

参照图8m,在衬底上沉积吸气剂层890,覆盖BEOL电介质和牺牲层。吸气剂,例如可以是锆(Zr)合金,钛(Ti),镍(Ni),铝(Al),钡(Ba)或镁(Mg)。也可以使用其他类型的吸气剂材料,例如稀土元素,包括铈(Ce),镧(La),钍(Th)或铀(U)。吸气剂在封装的器件内吸收水分和脱气,从而有助于保持腔体中真空的完整性,从而提高可靠性。吸气剂层,例如是非红外透明的。这样,吸气剂层被图案化以允许IR穿过封盖穿透到IR传感器。例如,吸气剂层可以被图案化以覆盖MEMS器件区的外围,包括支承壁的侧面和底部,同时使传感器和释放开口暴露。如前所述,吸气剂的其他各种图案也可用。

在一个实施例中,MEMS区包括一个或多个盲像素以及用于感测IR辐射的一个或多个有源像素。盲像素,例如,出于校准目的用作参考像素。这样可以最大程度地减少校准误差。所述盲像素,例如,可以通过使吸气剂层保持未图案化来形成,从而防止IR传输到传感器。为了进一步确保IR到传感器的零传输,可以沉积反射金属层(例如Al)并对其进行图案化,以保留在盲像素器件区上。在一个实施例中,盲像素可设置在有源像素或像素阵列的边界处。例如,MEMS区可以包括在有源器件区的边界处具有非盲像素的有源器件区和具有盲像素的非有源器件区。非有源器件区可以包括单个盲像素或盲像素的线阵列。

在图8n中,开始形成CMOS兼容的IR透明封盖的工艺。CMOS透明封盖构造为透射波长范围8-14μm内的IR辐射。CMOS封盖覆盖器件800。例如,CMOS封盖覆盖CMOS区并封装MEMS区806。该工艺,如图所示,形成了底盖的下部882。该下部,在一个实施例中,包括多个IR透明层。提供其他数量的IR透明层(包括1个)也可用。红外透明层可以包括,例如SiO

在一个实施例中,底盖的下部包括交替的IR透明层。优选地,与BEOL电介质接触的底部IR透明层对例如释放刻蚀剂,例如XeF

如图所示,所述牺牲层构造为形成封盖,其中底盖分别形成外和内支承壁887和888,从而为每个MEMS器件区形成微型壳体。牺牲层可构造为形成封盖,其中,底盖仅形成外支承壁,而密封盖通过释放开口形成内支承壁,如图3a-b所示。这样可以构造成为每个MEMS器件区形成微型壳体,或者包括相邻像素之间的通道,其在整个MEMS器件区的阵列上产生均匀的真空度,如图6a-d所示。

在形成底盖的下部之后,将其图案化。在一个实施例中,对底盖进行图案化以形成释放开口885。在一个实施例中,所述图案化还从CMOS区去除底盖的下部。例如,底盖的下部位于MEMS区的局部。可以使用掩模和刻蚀技术来图案化底盖的下部。例如,光刻胶掩模通过掩模版用曝光源曝光。掩模版的图案被转移到抗蚀剂层,从而形成刻蚀掩模。RIE刻蚀封盖的下部,去除由抗蚀剂掩模暴露的部分。

在图8o中,在衬底上形成介电层893,覆盖CMOS区和MEMS区中的底盖的下部,包括内衬释放开口。介电层形成底盖的第五层。例如,介电层形成底盖的上部,完成底盖881。在一个实施例中,介电层是SiO

对底盖进行图案化以去除衬在释放开口底部的介电层。图案化介电层可以采用掩模和刻蚀工艺。打开释放窗口暴露上部器件腔中的牺牲层。

如前所述,底盖可构造成具有各种数量的层。例如,底盖可以构造为具有3层,例如SiO

在图8p中,打开释放开口之后,对衬底进行释放工艺处理。释放工艺通过膜中的释放开口845去除上部和下部器件腔中的牺牲填充物。这样暴露了膜上的MEMS结构以及下部器件腔底部的反射体。在一个实施例中,释放工艺包括干法刻蚀以去除牺牲填充物。与BEOL电介质以及反射体上方的保护层相比,刻蚀剂以高刻蚀率刻蚀牺牲层。例如,刻蚀剂对金属和氧化硅具有高度选择性。在一个实施例中,二氟化氙(XeF

参照图8q,在底盖上方形成密封盖884。所述密封盖,例如可以包括多个IR透明层。提供具有单层的密封盖也可用。在一个实施例中,密封盖包括αSi/SiO

在图8r中,该工艺形成焊盘开口878以暴露焊盘层中的焊盘。例如,在CMOS区通过焊盘和钝化层形成焊盘开口。可以通过掩模和刻蚀工艺形成焊盘开口。例如,在抗反射涂层(ARC)上形成抗蚀剂层。所述ARC,例如,可以用于最小化来自封盖的IR反射。所述ARC,例如可以是具有多个设置以最小化来自封盖的IR反射的电介质层的ARC堆叠。抗蚀剂通过掩模版用曝光源曝光。显影后,掩模版上的图案转移到抗蚀剂上,形成刻蚀掩模。使用刻蚀掩模执行RIE以形成焊盘开口。尽管示出了一个焊盘开口,但是应当理解,可以存在多个焊盘开口。此外,焊盘开口可以分布在MEMS区之外的器件上。

如前所述,底盖和密封盖可以有不同的构造。底盖可以具有多层或单层。类似于底盖,密封盖可以具有多层或单层。密封盖可具有与顶部底盖层相同或不同的层。例如,在单个底盖层和单个密封盖层的情况下,封盖可以是IR透明层。IR透明层可以是任何对刻蚀剂具有抗蚀性的IR透明层。在某些情况下,ARC可以用作密封盖或保留在密封盖上方并成为密封盖的一部分。

图8s-t示出了用于形成器件的替代工艺800。参照图8s,它处于类似于图8p中所述的加工阶段。共同元件可能不描述或不详细描述。如图所示,在器件上方形成底盖881,该底盖包括覆盖CMOS和MEMS区的顶部底盖层893。在一个实施例中,底盖包括具有释放开口885的SiO

在一个实施例中,形成金属柱894以密封释放开口。为了形成金属柱,在衬底上形成诸如铝的金属层。其他类型的金属层也可以。可以通过在高真空度下溅射或蒸发来形成金属层。这样也密封具有高真空度的微型壳体。可替代地,使用金属柱可以密封部分微型壳体,以在整个阵列上提供均匀的真空度。通过掩模和刻蚀工艺来图案化金属层。金属层的图案可以类似于吸气剂层的图案。例如,金属层的图案密封释放开口,而在传感器区中提供开口以使传感器的感测能够穿过封盖。金属柱可形成密封盖的下部884。

参照图8t,在衬底上形成密封盖的上部886。密封盖的上部,例如包括αSi/SiO

图8u-v示出了用于形成器件的替代工艺800。参照图8u,它处于类似于图8p中所述的加工阶段。共同元件可能不描述或不详细描述。如图所示,在器件上方形成底盖881,该底盖包括覆盖CMOS和MEMS区的3个最上层。在一个实施例中,底盖包括具有释放开口885的SiO2/αSi/SiO2/αSi/SiO2/αSi/SiO2底盖堆叠。进一步处理该器件以去除上部和下部器件腔中的牺牲层,从而暴露传感器850。

参照图8v,形成密封盖884。在一个实施例中,密封盖包括金属柱894。金属柱894密封释放开口。为了形成金属柱,在衬底上形成诸如铝的金属层。其他类型的金属层也可用。可以通过在高真空度下溅射或蒸发来形成金属层。这样也密封具有高真空度的微型壳体。或者,使用金属柱可以密封部分微型壳体,以在整个阵列上提供均匀的真空度。通过掩模和刻蚀工艺来图案化金属层。金属层的图案可以类似于吸气剂层的图案。例如,金属层的图案密封释放开口,而在传感器区中提供开口,以使传感器的感测能够穿过封盖。该工艺如图8r所示继续进行。

图9a示出了绘制CMOS封盖的实施例的IR透射率的曲线图900。CMOS封盖包括以下顺序的层和厚度:

第一层-SiO

第二层-α-Si-200nm

第三层-SiO

第四层-α-Si-900nm

第五层-SiO

第六层-α-Si-200nm

第七层-SiO

图9b示出了在大气压力下CMOS封盖的实施例的机械强度的仿真结果901。CMOS封盖包括以下顺序的层和厚度:

第一层-SiO

第二层-α-Si-200nm

第三层-SiO

第四层-α-Si-900nm

第五层-SiO

第六层-α-Si-200nm

第七层-SiO

仿真表明,封盖的最大膜应力为25.4MPa,远低于α-Si和SiO

在不脱离本发明的精神或必要特征的情况下,本公开可以以其他特定形式来体现。因此,前述实施例在所有方面都应被认为是说明性的,而不是限制本文所述的发明。因此,本发明的范围由所附权利要求书而不是前面的描述指示,并且落入权利要求书的等同含义和范围内的所有改变都应包含在其中。

- 用于MEMS器件的CMOS封盖

- 一种通用CMOS MEMS器件电化学腐蚀绝缘保护方法