堆叠存储器及ASIC装置

文献发布时间:2023-06-19 09:26:02

技术领域

本发明是有关一种集成电路存储器装置。

背景技术

在高密度存储器装置的制造中,集成电路上每单位面积的数据的量可为关键因素。因此,由于存储器装置的临界尺寸接近技术限制,已提出用于堆叠存储器单元的多层式的(multiple levels)技术以便达成每一位更大储存密度及更低成本。此外,正部署新存储器技术,包括相变存储器、铁磁性存储器、金属氧化物类存储器等等。

正部署的存储器技术可能需要与执行支持周边电路(诸如用于地址译码器、状态机及命令译码器的逻辑)不同的制造步骤顺序。作为支持存储器阵列及周边电路两者的制造步骤的需求的结果,实施存储器装置所需的生产线可能更昂贵,或在实施于周边电路中的电路类型中进行折衷。这会对使用更先进技术制得的集成电路造成更高的成本。

在以引用的方式并入本文中的陈(Chen)的美国专利第9,240,405号中,描述具有芯片外周边电路的存储器装置。所述装置适用于低成本制造。装置的存储器电路及周边电路在堆叠结构的不同层中实施。存储器电路层及周边电路层包括互补的内连线表面,所述互补内连线表面配对在一起之后在存储器电路与周边电路之间建立电气互连。存储器电路层及周边电路层可在不同制造线上的不同基板上使用不同工艺分别地形成。分开的电路可接着堆叠且封装在一起。

所述概念提供多个益处。首先,通常位于存储器芯片的周边区域中的电路,诸如感测放大器、列及行译码器以及控制器,可移动至周边电路层,从而在存储器电路芯片上不留下存储器阵列自身。因此,最小晶粒大小可在存储器电路芯片上实现,从而改良产率。其次,两个芯片中的每一个可使用对于其特定需要而言最佳的工艺制造。举例而言,存储器电路芯片可在3D存储器阵列的多个层中制造而周边电路芯片可通过针对先进CMOS技术优化的工艺制造,因此改良两者的结果。第三,存储器阵列节点与周边电路芯片(其可为ASIC芯片)的直接接合可实施用于优化Von Neumann架构的最近推动的“存储器内运算(in-memorycomputation)”或“存储器内处理器(processor in memory)”技术。此类直接接合允许较少数据移动、较短延迟以及较少功率消耗。

然而,出现问题,这是因为自一个芯片至另一芯片可能需要潜在地大数量的连接。这些可包括用于存储器电路的每一位线的至少一个连接及用于每一字线的至少一个连接。在三维存储器阵列以及一些其他存储器阵列结构中,额外连接是此类导体所需的,例如共同源极线、串选择线、接地选择线以及电力线。这些合起来可能需要数千个内连线。由于内连线通常包括比将电气信号携带至存储器电路或自其携带存储器电路中的电气信号的导体大得多的接合垫,其通常无法设置于非常靠近其所连接至的存储器电路导体。在一些情况下,存储器电路信号必须侧向行进较大距离以便达至其经分配的内连线衬垫。因此,存储器带宽可能受限,且侧向延伸导体在位线或字线设置操作期间可产生额外寄生RC延迟及更高功率消耗。

发明内容

附图

本发明涉及一种包括存储器芯片的装置,所述存储器芯片具有存储器阵列、与存储器阵列的数据携带节点通信的位线以及与存储器阵列的某些栅极控制节点通信的字线。存储器芯片具有在各自存储器芯片内连线位置处形成于内连线表面上的接合垫。存储器阵列的每个位线及每个字线包括芯片的导电层中的各自着陆垫,且这些着陆垫经由重布线导体连接至一组存储器芯片接合垫中的每一个。用于位线的重布线导体具有正平均侧向信号行进距离(positive average lateral signal travel distance),其小于用于字线的重布线导体的正平均侧向信号行进距离。

提供以上发明内容以便提供对本发明的一些方案的基本理解。此发明内容不想要识别本发明的关键或决定性要素或描绘本发明的范畴。其唯一目的在于以简化形式呈现本发明的一些概念以作为随后提出的更详细描述的序言。本发明的特定方案描述于申请专利范围、说明书及附图中。

附图说明

将关于本发明的特定实施例描述本发明,且将对附图进行参考,其中:

图1为并入有本发明的方案的存储器芯片及ASIC晶圆的象征图。

图2为来自图1的ASIC晶圆的ASIC芯片及来自图1的存储器晶圆的存储器芯片的横截面图中的象征图。

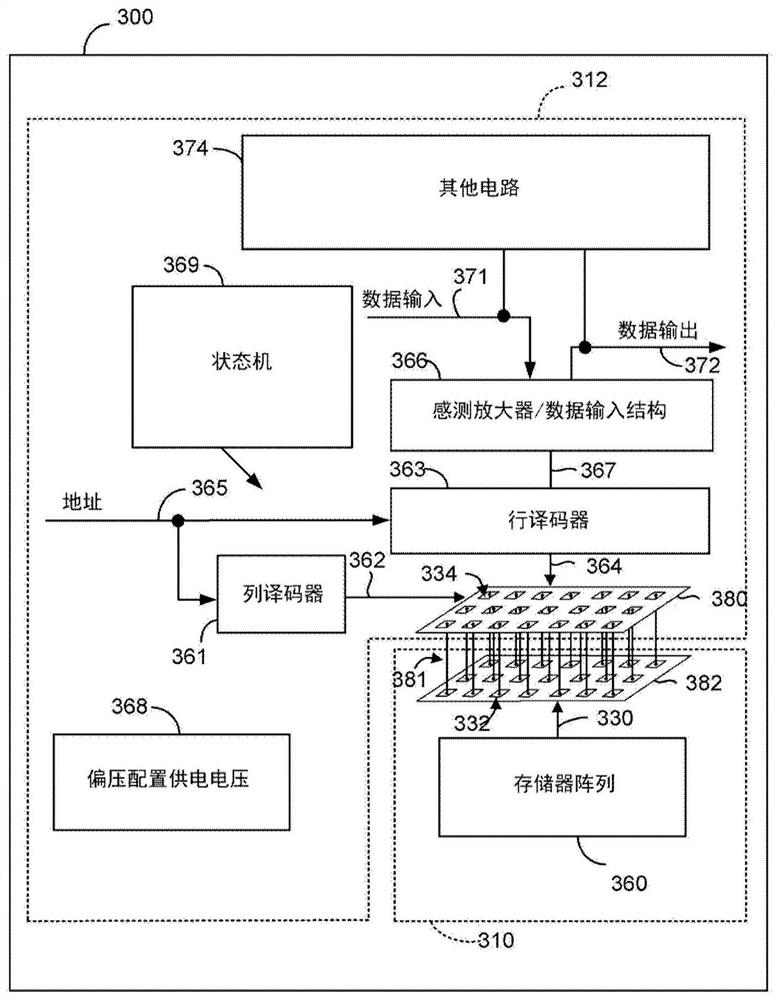

图3为包括存储器电路及周边电路的堆叠集成电路装置的简化方块图。

图4为可用于本发明的方案的3D U形存储器结构的透视图。

图5为用于图4的存储器结构的部分的简化电路图。

图6、图7、图8、图9、图10及图11为根据本发明的方案的存储器芯片的不同导电层的布局(平面)图。

图12为根据本发明的实施例的存储器电路芯片的若干上部层的象征性透视图。

图13为说明用于制造并入有本发明的特征的装置的方法的流程图。

图14为可用于执行并入有本发明的方案的某些方法步骤的实例计算机系统的方块图。

【符号说明】

110:存储器晶圆

112:ASIC晶圆

210:存储器芯片

212:ASIC芯片

300:堆叠集成电路装置

310:存储器电路

312:周边电路

330、362、364、732、VA2、VA3、VA4:导体

332:内连线衬垫

334:内连线位置

360:存储器阵列

361:列译码器

363:行译码器

365:总线

366:感测放大器/数据输入结构

367:数据总线

368:区块

369:状态机

371:数据输入线

372:数据输出线

374:电路

380、382:内连线表面

381:内连线界面

440、444:源参考导线

460:位线

469:电路路径

471:部分

510、511:字符串

514、515:串选择栅极

518、519:存储器单元

520、521:下部选择栅极

522:位线导体

528:共同选择线

610:局部共同源极线导体

612、613、1112:区段

630:层间导体

720:ML2 GBL着陆垫

734:层间导体

810:金属全局字线

812、ML3:CSL

820:GWL着陆垫

840:GBL着陆垫

912、914、1012、1212:接合垫

920:箭头

922:区域

1010、1210:GWL

1020:着陆垫

1030:北侧

1032:南侧

1060、1260:GBL

1061:间隙

1211:CSL导体

1242:重布线导体

1310、1312、1314、1316、1318、1320、1322:步骤

1410:计算机系统

1412:总线子系统

1414:处理器子系统

1416:网络界面子系统

1418:通信网络

1420:用户界面输出装置

1422:使用者界面输入设备

1424:储存子系统

1426:存储器子系统

1428:档案储存子系统

1430:主要随机存取存储器

1432:只读存储器

ML1、ML2、ML3、ML4、ML5:金属层

Px_BL、Px_PAD、Py_PAD:间距

X、Y:方向

具体实施方式

以下描述经呈现以使得所属领域的技术人员能够制成及使用本发明,且提供于特定应用及其要求的上下文中。对所揭露的实施例的各种修改对于所属领域的技术人员而言将显而易见,且本文中定义的通用原理可在不脱离本发明的精神及范畴的情况下应用于其他实施例及应用。因此,本发明并不限于所示实施例,而是应符合与本文中所揭露的原理及特征一致的最广范畴。

图1为存储器晶圆110及ASIC晶圆112的象征图,数个存储器电路已制造于所述存储器晶圆110上,感测放大器及其他偏压发生器以及用于存储器电路的支持电路已制造于所述ASIC晶圆112上。ASIC晶圆112还可包括其他先进CMOS装置,诸如处理器、中央处理单元、通用处理器、逻辑控制器、状态机、算术逻辑单元、阵列处理单元、图形处理单元、内存管理单元、高速缓存、SRAM以及输入/输出控制器。如图中所示,存储器晶圆110及ASIC晶圆112彼此面对面连接。在翻转之后,存储器晶圆的背侧将最接近印刷电路板或其他支撑结构。在一个实施例中,两个晶圆首先接合且稍后切割,而在另一实施例中,两个晶圆先切割且稍后接合。

图2为来自ASIC晶圆112的ASIC芯片212及来自存储器晶圆110的存储器芯片210的横截面视角的象征图。ASIC芯片212示出为具有制造于其上的多个晶体管,所述晶体管具有延伸至芯片的内连线层的源、漏极与门极接点。示出三个接合垫(bonding pads),其中其顶部表面暴露于上述面向下的存储器芯片210。如同图1,两个芯片经示出与其最终配置相比是上下颠倒的,其中存储器芯片210的背侧抵靠PC板。存储器芯片210象征性地显示包括制造于其上的3D存储器阵列,其中导电插塞自多个阵列节点向上(在附图中向下)延伸至重布层(redistribution layer),且接着延伸至其顶部表面(在附图中面向下)暴露于ASIC芯片212下方的三个接合垫。芯片212可为任何周边芯片,不仅仅为ASIC芯片。如本文中所使用,“周边芯片”包括感测放大器,但也可包括任何其他逻辑,包括CPU、状态机、ALU等。用语“周边芯片”在本文中经预期包括所有此类变化。

尽管存储器电路芯片210及周边电路芯片212各自无关产品本身而构成,但在其经由内连线界面381(图3)接合在一起时获得其他益处。如本文中所使用的用语“接合(joined/joining)”指代其中存储器电路芯片210附接、贴附或以其他方式实体地连接至周边电路芯片212的组态。所述用语涵盖其中存储器电路芯片210直接贴附至周边电路芯片212(诸如经由接合)的组态。所述用语进一步涵盖由此存储器电路芯片210经由使用中间“插入件(interposer)”构件或元件间接地连接至周边电路芯片212的组态。另外,尽管芯片210上的接合垫在图2中呈现为匹配具有芯片212上的接合垫的位置,但应了解,在特定实施例中,其不一定必须匹配方位,或恰好匹配位置,尤其在使用插入件时。任一芯片上的每一垫也不必在另一芯片上具有对应的垫。

图3为包括存储器电路310及周边电路312的堆叠集成电路装置300的简化方块图。存储器电路310及周边电路312实体地分离至装置300的不同层上,且经由内连线界面381接合。存储器电路310包括存储器阵列360。字线(未图示)沿存储器阵列360中的列配置。位线(未图标)沿存储器阵列360中的行配置,以用于读取及编程存储器阵列360中的存储器单元(未图标)。如本文中所使用,用语“存取线”大体是指位线、源极线及/或字线。存储器电路310也可包括其他电路,诸如高电压晶体管或驱动器,所述其他电路在包括于与存储器阵列360相同的芯片上时可提供更佳效能。

存储器电路310包括具有一组内连线衬垫(也被称作接合垫)332的内连线表面382。内连线衬垫332配置于内连线位置处,其形成定义存储器电路310的垂直电气内连线界面的图案。图3绘示可包括数千个接合垫332的内连线表面382的小部分。接合垫332经由导体330耦接至存储器阵列360中的对应存取线,由此如下文所描述实现对存储器阵列360的特定列或行的选择。

存储器阵列360可实施多种不同的2D或3D存储器架构。存储器阵列360也可使用诸如浮置栅极、电荷陷入、可编程电阻、相位变换等储存技术实现多种不同种类的存储器单元,包括各种各样的随机存取存储器、只读存储器以及其他非挥发性存储器。在一些实施例中,存储器阵列360使用堆叠薄膜晶体管结构实施,诸如美国专利第7,473,589号及美国专利第7,709,334号中所描述的那些堆叠薄膜晶体管结构,所述美国专利的揭露内容以引用的方式并入本文中。

周边电路312也包括在一组内连线位置334处具有接合垫的内连线表面380。内连线位置334以定义周边电路312的垂直电气内连线界面的图案配置。

内连线表面382与内连线表面380之间的内连线界面381用于将特定周边装置接合垫334电连接至对应存储器装置接合垫332。内连线界面381也用于使剩余接合垫332、334彼此电隔离。在此情况下,内连线界面381将周边电路312垂直地连接至个别存取线或存储器阵列360中的其他存储器阵列节点。

周边电路312为存储器电路310的操作提供控制信号,诸如偏压信号、定时信号、开关控制信号等等。如本文中所使用,用语“信号(signal)”出于所有目的包括电通信,包括信息携带信号(诸如数据及控制信号)以及功率。周边电路312包括经由互补接合垫382、互补接合垫380以及接合垫381耦接至存储器阵列360中的字线的导体362。导体362延伸至列译码器361。导体364经由接合垫382、接合垫380、内连线界面381以及导体330将行译码器363耦接至存储器阵列360中的位线。地址在总线365上供应至列译码器361及行译码器363。感测放大器及数据输入(data-in)结构366在此实例中经由数据总线367耦接至行译码器363。行译码器363及区块366中的感测放大器可配置于允许广泛、并行读取及写入操作的页缓冲器结构中。数据经由数据输入线371自集成电路存储器装置300上的输入/输出端口供应至区块366中的数据输入结构。在所示出的实施例中,其他电路374包括于周边电路312中,诸如通用处理器或专用应用程序电路,或提供由存储器阵列360支持的系统单芯片功能性的模块的组合。数据经由数据输出(data-out)线372自区块366中的感测放大器供应至周边电路312上的输入/输出端口,或供应至在集成电路312内部或外部的其他目的地。

在此实例中实施的控制器使用偏压配置状态机369来控制经由区块368中的电压源产生或提供的偏压配置供电电压(诸如读取及编程电压)的施加。这些偏压配置供电电压以及其他控制信号随后经由接合垫382、接合垫380以及内连线界面381提供至存储器电路310。如此项技术中已知的,可使用专用逻辑电路来实施控制器。在替代性实施例中,控制器包括通用处理器,所述通用处理器可在周边电路312中实施,其执行计算机程序以控制装置300的操作。在另外其他的实施例中,可利用专用逻辑电路与通用处理器的组合来实施控制器。

多种不同技术可用于堆叠周边电路312及存储器电路310以经由内连线界面381建立电气内连线。举例而言,经图案化导电材料可应用于内连线表面382、内连线表面380中的一者或两者。材料可例如为导电接合黏着剂或焊接材料。周边电路312及存储器电路310接着可堆叠以使得内连线表面382、内连线表面380直接配对在一起,由此配对来自两个芯片的接合垫中的对应者。

在一些实施例中,内连线界面381包括插入于内连线表面382与内连线表面380之间的插入件。插入件可包括金属层的半导体基板,所述金属层具有经配置以在内连线表面之间传导信号,且包括如用于耦合插入件的一侧与另一侧上的接点的TSV技术的结构。插入件包括具有各自内连线位置的相对侧。在内连线位置之间延伸的导电构件在相对侧之间形成导电路径。在一些实施例中,插入件可包括额外电路,诸如放大器中继器、电感器、电容器以及二极管,以支持信号的传达及分层存储器与周边电路之间的阻抗匹配。如本文中所使用,描述为彼此“通信(in communication with)”的两个节点不必彼此持续通信。所述用语也包括在其之间包含可暂时阻止信息或电流通过的串联连接开关的配置。

存储器电路310及周边电路312的实体分离使得能够使用非依赖性制造工艺技术,一者用于存储器电路310且另一者用于支持周边电路312(且又一者用于可任选的插入件)。举例而言,存储器电路310及周边电路312可在不同制造线中的不同基板上使用不同工艺分开地形成。因此,周边电路312可使用仅逻辑工艺(logic only processes)形成,诸如用于形成静态随机存取存储器(SRAM)的那些工艺,而非用于习知存储器的更复杂组合逻辑/存储器工艺。此导致以低成本设计高效能周边电路312的能力。类似地,存储器电路310可使用存储器工艺技术制造,而无需考虑周边电路312的制造工艺技术。

即使有接合工艺的成本,存储器电路310及周边电路312的分开形成仍可显著降低每一存储器单元的净成本。举例而言,假定存储器电路310及周边电路312占据相同晶粒面积且其各自工艺技术不包括共同工艺步骤。也假定存储器电路310及周边电路312各自需要以每层$50的成本形成20个材料层。根据这些假定,形成存储器电路310以及周边电路312将产生约(20*$50+20*$50)/1000或$2的晶粒成本。相比之下,形成存储器电路310及周边电路312分开地产生约(20*$50/2000)+(20*$50/2000)+堆叠及接合成本或$1加接合工艺成本的晶粒成本。因此,若接合电路的成本小于$1,则分离存储器及周边电路将比在单个晶圆上实施这些工艺的成本更低。

存储器电路310及周边电路312的实体分离也实现各自的模块化。此模块化可针对相同存储器装置300上的不同存储器单元提供不同操作模式,诸如不同读取或写入操作。这些不同操作模式使得不同存储器单元能够提供不同存储器特性。

尽管存储器电路310可为多种不同类型的存储器中的任一者,但本说明书出于说明的目的使用3D NAND垂直通道阵列作为实例。此结构的实例描述于胜又(Katsumata)等人的“具有16个堆叠层的管形BiCS闪存及超高密度储存装置的多位准单元操作(Pipe-shapedBiCS Flash Memorywith 16 Stacked Layers and Multi-Level-Cell Operation forUltra High Density Storage Devices)”中,技术论文摘要-2009 VLSI技术研讨会(2009Symposium on VLSI Technology Digest of Technical Papers),2009年,其以引用的方式并入本文中。胜又等人中所描述的结构包括垂直NAND栅,使用硅-氧化物-氮化物-氧化物-硅SONOS电荷陷入技术来在每一栅极/垂直通道界面处产生储存器位点。存储器结构是基于经配置为用于NAND栅的垂直通道的半导体材料的行,具有邻接基板的下部选择栅极及在顶部上的上部选择栅极。多个水平字线使用与所述行相交的平面字线层形成,从而在各层处形成所谓的环绕式栅极单元。

图4为3D U形存储器结构的透视图,其中每一串单元沿间隙的一侧向下延伸,在底部跨越间隙,且在间隙的另一侧上返回。如图4中所示的电路路径469绘示用于连接于位线460中的源参考导线444之间的U形NAND串的电流。结构显示出在导电带的对应偶数堆叠与奇数堆叠之间的多个主动柱。主动柱包括具有外表面及内表面的半导体膜。外表面安置在形成存储器单元的3D阵列的对应偶数与奇数堆叠的侧壁上的数据储存器结构上。存储器单元经连接以形成自偶数垂直通道膜的上端至下端及自奇数垂直通道膜的下端至上端的电流路径。

在图4的存储器装置中,导电带的堆叠由沟渠分隔开。参考第一及第二堆叠中的导电带,可描述用于互连至U形NAND串的组态。导电带的第一及第二堆叠具有在分离堆叠的沟槽的第一侧及第二侧上的侧壁。数据储存器结构形成于沟渠中的条带的侧壁上。垂直通道结构安置于第一堆叠与第二堆叠之间的沟渠中。每一垂直通道结构包括垂直地安置成接触沟槽的相对侧上的数据储存器结构的第一半导体膜及第二半导体膜,所述半导体膜在沟槽的底部电连接。第一堆叠中的上部条带经组态为在第一半导体膜中具有通道的第一开关(例如,SSL(串选择线)开关)的栅极,且第二堆叠的上部条带经组态为在第二半导体膜中具有通道的第二开关(例如,GSL(接地选择线,也被称作共同选择线)开关)的栅极。第一及第二堆叠中的中间层条带经组态为字线。第一及第二堆叠中的底部条带经组态为辅助栅极(AG)。一或多个经图案化导体层上覆于堆叠。第一层间连接器将第一导体(例如位线460)连接至主动柱中的第一半导体膜的顶部表面。第二层间连接器将第二导体(例如源参考导线440)连接至垂直通道结构中的第二半导体膜的顶部表面。此外,安置于相同第一堆叠与第二堆叠之间的额外垂直通道结构经组态,使得沟槽的第二侧上的第二半导体膜全部电连接,且可共享至相同源参考线的连接。此外,相同第一堆叠与第二堆叠之间的额外垂直通道结构经组态使得沟槽的第一侧上的第一半导体膜电性地分离,且可使用个别层间连接器(例如第三层间连接器)个别地连接至分开的位线。

如本文中所使用,被称为“高于”或“低于”其他层的层在各种实施例中可通过一或多个介入层与此类其他层分离。若无介入层经预期,则用语“在...正上方”或“在...正下方”在本文中使用。相同解释意欲用于描述为“叠加于(superposing)”、“下伏于(underlying)”或“在...上方(over)”或“上覆于(overlying)”另一层的层。另外,若第一层更接近于装置的主动表面,所述主动表面在本文中也被称作装置的“顶侧”,则第一层称为“上覆于”第二层。类似地,若第二层更接近于装置的后部表面,所述后部表面在本文中也被称作装置的“背侧”,则第二层称为“下伏于”第一层。若芯片倒置,其并不改变哪一表面是顶侧及哪一者是背侧。

第三堆叠与第二堆叠之间的垂直通道结构包括沿在第三堆叠与第二堆叠之间的第二堆叠的侧壁上的沟渠的第一侧的第一半导体膜,及沿第三堆叠与第二堆叠之间的沟渠的第二侧的第二半导体膜。第三堆叠与第二堆叠之间的垂直通道结构的第一半导体膜可电连接(通过部分471)至第一堆叠与第二堆叠之间的垂直通道结构的第二半导体膜。关于图4的结构的更多细节以及其制造方法可见于以引用的方式并入本文中的卢(Lue)美国专利第10,211,218号。

在图4的结构中,位线460在Y方向上延伸,且字线条带(在附图中标记为WL)在X方向上延伸。SSL、GSL及AG条带也在X方向上延伸。

图5为示出图4的实例存储器阵列的U形串中之两者中的存储器单元及存取晶体管的简化电路图,在图5中编号为510、511。每一字符串含有数目“i”个串联连接的存储器单元。字符串510中的存储器单元标记为518(0)...518(i-1)(代表性地518),而字符串511中的存储器单元标记为519(0)...519(i-1)(代表性地519)。存储器单元518及存储器单元519中的每一者包括源极端子、漏极端子以及控制栅极。归因于多个晶体管中的源极及漏极的电学可互换性,这两个端子本文中有时被统称为「电流路径端子」。字符串中的晶体管的串联连接为字符串中的晶体管的电流路径端子的串联连接。

字符串510也包括串联连接在字符串的存储器单元518的相对侧上的串选择栅极及下部选择栅极(更准确地被称作用于U形存储器阵列的接地选择栅极)。更特定言之,每一串选择栅极514及下部选择栅极520包括控制闸电极及两个电流路径端子,且电流路径端子与字符串的存储器单元518的电流路径端子串联连接。类似地,字符串511也包括串联连接在字符串的存储器单元519的相对侧上的串选择栅极515及下部选择栅极521。两个字符串510、字符串511共享连接至两个串选择栅极的漏极端子的单个位线导体522。两个串选择栅极的控制栅极连接至分开的串选择线(字符串510中的串选择栅极514及字符串511中的串选择栅极515),由此准许位线522与各自存储器单元字符串510及存储器单元字符串511之间的可选通信。两个字符串也共享连接至两个下部选择栅极的源极端子的单个共同选择线528及连接至两个下部选择栅极的控制栅极的共同下部选择线520。

存储器也包括i个分开的局部字线(local word line)导体WL(0)...WL(i-1)(代表性地WL),各自形成于如图4的存储器阵列中所示的分开的字线条带中。字线条带形成于图4的存储器阵列的多个平面中,且一者对应于字符串510中的存储器单元518中的每一者。字符串511中的对应存储器单元519如同字符串510中的那些存储器单元位于对应平面。每个局部字线导体WL中的每一者连接至字符串510中的对应存储器单元518的控制栅电极,且许多者也连接至字符串511中的对应存储器单元519中的控制栅电极。因此可见,字符串中的每一者与局部字线导体相交,且字符串的存储器单元位于局部字线导体与字符串之间的交点处。

为了编程存储器中的单元,控制电路526首先抹除单元的整个区块,而排出陷入层上的任何电荷。控制电路(图5中未示出)随后通过将适当电压施加至所选及未选SSL、位线以及局部字线来编程单元的一个列(在图5中)一次。在电压经配置以使得自控制栅电极至通道跨越介电质电荷陷入结构中的陷入层的电场足够高,以允许电子自通道至陷入层上的Fowler-Nordheim穿隧(Fowler Nordheim tunneling)时编程单元。编程的抑制是通过配置电压以使得电场过小而不能产生此类穿隧。

图6为上覆于包括如上所述的U形NAND字符串的存储器阵列的四个3D区块的第一金属层的布局图。四个区块在Y方向上分离且标记为Block_J、Block_J+1、Block_J+2以及Block_J+3。每一区块在X方向上分段;尽管示出仅两个区段612及区段613,但其通常为多个区段长。每一区段例示性地示出为含有在X方向上延伸的九个局部共同源极线(CSL)导体610。这些局部CSL 610形成于半导体堆叠上方的金属层中,例如ML1。可形成于ML1中的其他全局导体(未图示)包括全局GSL线及全局SSL线。参考区块J,区段612,ML1中的所有局部CSL在一个末端或另一末端处连接在一起且连接至层间导体630以用于进一步连接至更高金属层。

图7为其中下一更高的金属层ML2中的相关导体中的一些添加至如图6中所示的ML1中的那些导体的布局图。ML2中的导体包括在Y方向上延伸的全局位线(GBL)460。金属层中的每一者与在介电层(未图示)上方及下方的金属层分离。如图4所示,GBL 460经连接在每一「U」的一个末端处连接至下伏存储器单元字符串。此类连接穿过GBL 460下方的介电层中的层间导体。GBL 460中的每一者在一个末端处或另一末端处与通孔着陆垫720端接以用于层间连接至上方的RDL层,如下文中所描述。如本文中所使用,「着陆垫(landing pad)」为芯片的一个层上的促进经由层间导体(有时在本文中也被称作通孔)与相同芯片的另一层上的导体的电气互连的导电材料区域。其不同于“接合垫”,原因在于接合垫用于芯片外互连。

在底层字线条带在多晶硅中制造的实施例中,字线条带较佳地连接至上覆层中的一组金属全局字线(GWL)810。这些示出于图8中,其示出GWL 810以及添加至图7中的那种下一金属层ML3中的一些其他相关导体。字线层间导体(未图示)将GWL 810连接至个别底层字线条带(现被称作局部字线LWL),其可以如图2中象征性地绘示的阶梯状方式端接。为了说明清楚起见,来自图6的局部CSL610不再示出于图7中,来自图7的ML2 CSL导体732也如此。但层间导体734将ML2 CSL导体连接至其他ML3共同源极线812。GWL及ML3 CSL在X方向上延伸。

如上所述,GWL 810经由层间导体连接至下方局部字线,其以阶梯状方式端接,以允许视需要通过特定存储器阵列架构分离用于每一LWL或一组LWL的垂直层间导体。额外用于下方LWL的GWL适用于诸如图4的阵列架构的阵列架构,这是因为LWL通常形成于多晶硅中,其具有较大RC寄生效应。沿字线的长度周期性地连接至金属GWL有助于减少可接受层的RC寄生效应。GWL 810中的每一者在一个末端处或另一末端处与着陆垫820端接以用于层间连接至上方的RDL层,如下文中所描述。在图8的实施例中,着陆垫820存在于交替末端处及距着陆垫614不同的纵向距离处。此提供用于更宽着陆垫820的空间,其有助于放宽对较高层的对齐准确度要求。GBL着陆垫840也示出于图8中,其形成于图7中的ML2 GBL着陆垫720正上方,且经由层间导体连接至ML2 GBL着陆垫720。

应注意,并非所有可用于本发明的方案的存储器阵列必然具有全局字线及局部字线两者;一些具有仅一种字线,且其他者具有多于两种字线。如本文中所使用,用语“字线”或WL意欲通用于所有这些种类的字线。类似地,并非所有可用于本发明的方案的存储器阵列必然具有全局位线及局部位线两者;一些具有仅一种位线,且其他者具有多于两种位线。如本文中所使用,用语“位线”或BL意欲通用于所有这些种类的位线。

图8中的ML3 CSL 812也在X方向上延伸且形成于与GWL 810相同的金属层中。CSL812经由层间导体(未图示)连接至U形存储器字符串的末端,所述末端与GBL 460所连接至的末端相反。应注意,在不同实施例中,本文中所示出及描述的多个导电内连线层可以与如本文所阐述的次序不同的次序存在。

因此,待连接至接合垫以用于连接至周边芯片212的存储器阵列节点包括CSL812、GWL 810、GBL 460、SSL、GSL,以及在一些实施例中,存取栅极线(AGL)。然而,为了最大化可跨越内连线界面381传输的信号的数目,内连线位置332通常以具有最小间距的规则栅格图案(regular grid pattern)布置,可依赖所述最小间距以利用周边芯片212上的对应内连线位置334恰当地对齐,给定对齐设备的置放准确度。因此通常不可能提供在着陆垫正上方的内连线位置332,每一信号在底层中将连接至所述着陆垫。要求信号节点的某一重布线,涉及一些额外侧向信号传输。此重布线增大信号行进的长度且因此增强RC寄生效应。但代替尝试最小化侧向重布线信号行进的总侧向长度,在本发明的方案中,本文实施例优先化将首先布线至最接近内连线位置334的所述类型的信号,从而允许每一后续布线信号类型在比先前信号类型更长的距离内布线。特定言之,在本发明的方案中,尤其对于NAND技术,CSL线812首先经由最小路径布线,这是因为CSL加载归因于IR压降是至关重要的。在多个实施例中,CSL收集所有字符串电流,且会引起可影响单元特性的高I*R值。位线(诸如GBL460)布线在附近的衬垫旁,这是因为其也携带大部分电流(尽管小于CSL)。最终,MOS晶体管的信号控制栅极最后布线至剩余衬垫,这是因为其携带最小电流。这些包括GWL810,随后SSL及GSL。

图9为顶部上叠加有接合垫912的栅格的存储器电路芯片210的布局图。也示出一组箭头920以显示哪些GBL着陆垫840及GWL着陆垫820连接至哪些接合垫912。通过箭头920指示的连接存在于其中形成有着陆垫的金属层上方的重布线(RDL)金属层中,且在暴露接合垫912的芯片内连线表面382下方。举例而言,若GWL 810及CSL 812形成于金属层ML3中,则RDL可能在金属层ML4中且接合垫912可形成于金属层ML5中。应注意,虽然示出于图9中的箭头920包括对角线,但在另一实施例中,在RDL层中仅使用直角“曼哈顿(Manhattan)“布线。

在图9中可见,CSL 812已优先提供其接合垫的短路线。特定言之,用于CSL 812的接合垫914是直接位在用于CSL 812的着陆垫正上方。已给定GBL 460针对至其接合垫的较短路线的第二偏好,且已给定GWL 810第三偏好。特定的说,较佳的是GBL着陆垫840与其经分配接合垫(assigned bonding pad)912之间的平均侧向信号行进距离为正(也即存在一定侧向行进),但小于GWL着陆垫820与其经分配接合垫912之间的平均侧向信号行进距离。

如本文中所使用,“侧向信号行进距离”是指信号实际上沿其行进以达至其目的地衬垫的导体长度的总和。举例而言,在曼哈顿布线(Manhattan-routed)RDL层中,侧向信号行进距离为RDL导体在X方向上的总绝对RDL长度加在Y方向上的总绝对RDL长度。举例而言,在直接布线RDL层中,用语是指两个衬垫之间的欧几里得(Euclidean)距离。另外,如本文中所使用,“侧向”距离或“侧向”关系是指在投影至X-Y平面上时的位移。其包括在X方向上的位移,在Y方向上的位移以及在X方向及Y方向两者上的位移。垂直位移(在Z方向上),若存在,在考虑“侧向”位移时忽略。也即,路线在量测X及Y位移之前投影至侧向平面上。

另外,在图9中可见,接合垫912的栅格在X方向及Y方向上都比存储器阵列更大。出于本发明论述的目的,接合垫912的“行”定义为在Y方向上形成直线式接合垫,而接合垫912的“列”定义为在X方向上形成直线式接合垫。利用此定义,也较佳的是用于GBL 460的在X方向上上覆于阵列的单个区段的所有GBL着陆垫840为上覆于阵列的相同区段的「行」中的经分配接合垫912。换言之,较佳的是用于GBL 460的侧向定位在一对CSL接合垫914之间的所有GBL着陆垫840为也侧向定位在相同的一对CSL接合垫914之间的“行”中的经分配接合垫912。可见,对于图9中的GBL着陆垫840的接合垫分配而言以上描述皆为真,且同时侧向定位于阵列的单个区块上方的用于GWL 810的所有GWL着陆垫820为也定位于阵列的相同区块上方的栅格的“列”中的经分配接合垫912不为真。

图9也通过虚线指示分配给GBL着陆垫840的接合垫的区域922。可见,在阵列的每一侧向区段内,这些区域922包括在GBL 460的两个末端处的衬垫,但不包括上覆于GBL 460但分配给GWL着陆垫820的衬垫924的区域。每一区域922中的接合垫配置于邻接列及邻接行中,如区域924中的接合垫。在阵列的每一侧向区段内,区域924在Y方向上居中、在彼区段中的两个区域922之间侧向地定位。较佳地,连接至位线着陆垫的所有接合垫包含在接合垫的第一组邻接列及第三组邻接列中,且无一者包含在横向位于第一组及第三组列之间的接合垫的第二组邻接列中。此外,第二组邻接列中的接合垫中的一些(至少一个)连接至字线着陆垫。如本文中所使用,若两个对象并未由相同类型的另一对象分隔开,则两个对象彼此“邻接”。举例而言,若两条线之间不存在介入线,则两条线视为彼此“邻接”,即使两条线并不彼此接触。除非明确地要求,否则用语“邻接”不要求紧密相邻。

如在图9的实例中,也较佳的是所有GBL着陆垫840为上覆于或侧向邻接于各自GBL着陆垫840的“行”中的经分配接合垫912。所有GWL着陆垫820为上覆于或侧向邻接于各自GWL着陆垫820的栅格的「列」中的经分配接合垫912在图9中不为真。

图10为全局字线GWL 1010及全局位线GBL 1060的另一配置的布局图,其中针对GBL 1060显示出着陆垫1020。尽管未示出,所有所绘示的GBL 1060侧向安置在底层阵列的单个区段1112内,但所绘示的GWL 1010跨越由所述GBL 1060覆盖的所有区块安置。GBL1060在间隙1061处断裂以终止传导。在图10的实例中,存在32个GBL 1060,其中的16个在本文中将称作阵列的“北”侧1030的着陆垫1020处终止,且其中的16个在本文中将称作阵列的“南”侧1032的着陆垫1020处终止。(阵列的“北”侧面经示出在附图中的GWL 1010的侧向上方,且阵列的「南」侧经示出在附图中的GWL 1010的侧向下方。)因此,来自栅格的16个接合垫1012为分配至阵列的北侧上的着陆垫1020所需的,且16个接合垫为分配至阵列的南侧上的着陆垫1020所需的。16个接合垫1012的子栅格1022中的一者绘示于附图中。

图11为图10的配置的布局图,其中示出32个接合垫1012,且箭头1024指示接合垫1012至GBL着陆垫1020的分配。可见,所有GBL着陆垫1020经分配给接合垫1012的最接近行中的接合垫1012。对于直接下伏于接合垫1012的行的GBL着陆垫1020,着陆垫1020经分配给其所下伏于的接合垫1012的行中的接合垫1012。对于侧向存在于接合垫1012的两个行之间的GBL着陆垫1020,着陆垫1020经分配给接合垫1012的侧向最接近行中的接合垫1012。如本文中所使用,若GBL着陆垫1020定位在接合垫1012的两个行之间的中间位置,则两个行视为“最接近”行。

较佳地,接合垫1012的栅格相对于GBL着陆垫1020对齐,使得侧向在阵列的北侧1030上的子栅格的中心线(在Y方向上)与横跨阵列的相同区段1112的阵列的北侧上的GBL着陆垫1020的中心线(在Y方向上)对准。类似地,较佳地,接合垫1012的栅格相对于GBL着陆垫1020对齐,使得侧向在阵列的南侧1032上的子栅格的中心线(在Y方向上)与在横跨阵列的相同区段1112的阵列的南侧上的GBL着陆垫1020的中心线(在Y方向上)对准。如本文中所使用,一组着陆垫在特定方向上的中心线为正交于特定方向的线,所述中心线满足以下准则:与中心线正交的距中心线的一侧上的着陆垫中的每一者的距离的总和等于与中心线正交的距中心线的另一侧上的着陆垫中的每一者的距离的总和。

较佳地,接合垫1012的栅格相对于GBL着陆垫1020对齐,使得侧向在阵列的北侧1030上的子栅格的中心线(在在X方向上)与横跨阵列的相同区段1112的阵列的北侧上的GBL着陆垫1020的中心线(在X方向上)对准。类似地,较佳地,接合垫1012的栅格相对于GBL着陆垫1020对齐,使得侧向在阵列的南侧1032上的子栅格的中心线(在X方向上)与在横跨阵列的相同区段1112的阵列的南侧上的GBL着陆垫1020的中心线(在X方向上)对准。

较佳为,接合垫1012通过以下分配给GBL着陆垫1020:首先判定接合垫1012(Nx_PAD)的行如何在X方向上配合在一个阵列区段内,给定接合垫1012(Px_PAD)在X方向上的最小间距;将区段内的GBL 1060的数目的一半除以数目Nx_PAD,以判定在接合垫1012的两个子栅格中的每一者中在Y方向上要求的接合垫1012(Ny_PAD)的数目;在X方向及Y方向两者上使每一子栅格的中心点与存储器阵列的相同侧面1030或侧面1032上的GBL着陆垫1020的阵列的中心点对准;以及将GBL着陆垫1020中的每一者分配给子栅格的侧向最接近接合垫1012。

较佳地,在诸如图11的配置中,接合垫1012的栅格相对于GBL着陆垫1020对齐,使得GBL RDL长度L

L

其中Py_PAD为接合垫1012在Y方向上的间距,

Px_PAD为接合垫1012在X方向上的间距,以及

Px_BL为GBL 1060在X方向上的间距。

间距Py_PAD、间距Px_PAD以及间距Px_BL如图10所示的定义。

图12为根据本发明的实施例的存储器电路芯片210的若干上部层的象征性透视图。GBL 1260绘示为形成于金属层ML2中,且GWL 1210绘示为形成于下一更高的金属层ML3中。CSL导体1211也共享金属层ML3。重布线导体1242形成于ML3上方的RDL层ML4中,且接合垫1212形成于ML4上方的金属层ML5中。也示出层间导体。这些包括:将GBL 1260连接至ML3中的着陆垫的层间导体VA2;将ML3中的组件连接至ML4中的RDL导体1242的导体VA3;以及将ML4中的组件连接至ML5中的接合垫1212的导体VA4。可见,CSL导体1211连接至在CSL导体1211正上方的接合垫1212;GBL 1260经由相对较短RDL导体1242布线至侧向邻近接合垫1212;以及GWL 1210经由相对较长RDL导体1242布线至其他接合垫1212。用于GWL的RDL导体的绝对侧向长度具有比用于GBL的RDL导体的绝对侧向长度更宽的方差,其随后具有比用于CSL的RDL导体的绝对侧向长度更宽的方差。如本文中所使用,导体的群体的长度中的“方差(variance)”是导体中的每一者的长度之间的差的平方及导体的长度的平均数的总和。

在图7至图11的实施例中,可见GBL成对组织。在附图中自左至右,前两个GBL指向南,随后两个GBL指向北,后续两个GBL指向南等。此仅为实例配置,且将理解其他组织是可能的。举例而言,在另一实施例中,GBL可个别地而非成对地交替方向。在此实施例中,接合垫1012的栅格相对于GBL着陆垫1020对齐,使得GBL RDL长度L

LBL_RDL<1/2*Py_PAD*(Px_PAD/Px_BL)

再次参考图2,可见存储器电路芯片210及周边芯片212面对面接合。以此方式,周边芯片212可经由数千个接合垫直接控制存储器电路芯片210上的存储器单元,从而在与周边电路一起在芯片上时一样地操作存储器阵列。但对于多个应用,所得堆叠芯片仍必须接收功率以操作,且仍必须可由外部电路存取以用于控制信号及数据输入及输出。为了解决此问题,硅穿孔(TSV)较佳用于经由存储器电路芯片210将周边芯片212上的电路节点连接至其背侧,至用于连接至诸如印刷电路板的底层结构上的导电迹线的金属凸块。如同图9中的情况,若并非所有存储器电路芯片210上的接合垫913均分配给存储器阵列节点,则此类TSV可容纳于堆叠装置中。如图9中可见,接合垫913中的一些保持为空(未分配)且不连接至存储器阵列节点中的任一者。这些未分配接合垫913因此可用于形成TSV。

在一个用于实现此的工艺中,在制造两个芯片210及芯片212之后,存储器电路芯片210与周边芯片212面对面接合。存储器电路芯片210随后通过背侧研磨及抛光变薄,直至其足够薄为止。举例而言,存储器电路芯片210可薄化至大约50微米的厚度。接着,通过背侧光刻,在每一所需未分配接合垫913的侧向位置处于硅中蚀刻出孔,一直贯穿至接合垫913的内表面。这些孔可例如具有大约1微米的直径为及50的深宽比(aspect ratio),且以小至5微米的间距定位。孔随后经由如钨、铜或多晶硅的导电材料填充,且接着于经暴露导电填充物上涂覆背侧金属凸块。经接合堆叠装置随后凸块侧向下置放在诸如印刷电路板的底层结构上,其可接着向周边芯片212供应电力且与所述周边芯片交换输入/输出信号。这些穿过TSV、穿过存储器电路芯片210的主动表面上的接合垫913,跨越界面381传达至周边芯片212上的配对接合垫334,并进入周边芯片212的电路中。在一个示例性实施例中,存储器电路芯片可具有连接至全局位线的大约4000个接合垫,连接至全局字线的大约4000个接合垫,且仍具有可用于通过TSV连接至外部电路的大约几十至几千个接合垫。

图13为说明用于制造并入有本发明的特征的装置的方法的流程图。在步骤1310中,布置存储器字符串及存储器阵列结构的其他部分(诸如图4中所绘示的部分)。在步骤1312中,最接近的存储器芯片接合垫经分配给阵列的共同源极线。在步骤1314中,位线经分配给剩余存储器芯片接合垫中的最接近者。在步骤1316中,字线及其他栅极控制线经分配给仍剩余的存储器芯片接合垫中的最接近者。在步骤1318中,存储器芯片的RDL层根据接合垫的这些分配而布置。在步骤1320中,制造存储器芯片,且在步骤1322中,存储器芯片接合至对应周边芯片,如本文中其他处所描述。

图13中的布局及接合垫分配步骤可通过计算机系统自动地执行,所述计算机系统诸如图14的方块图中所绘示的计算机系统。请参考图14,计算机系统1410通常包括经由总线子系统1412与多个周边装置通信的处理器子系统1414。这些周边装置可包括储存子系统1424(包括存储器子系统1426及档案储存子系统1428)、用户界面输入设备1422、用户界面输出装置1420,以及网络界面子系统1416。输入及输出装置允许用户与计算机系统1410交互。网络界面子系统1416将界面提供至外部网络,包括将界面提供至通信网络1418,且经由通信网络1418耦接至其他计算机系统中的对应界面装置。通信网络1418可包括多个互连计算机系统及通信链路。这些通信链路可为有线链路、光学链路、无线链路,或用于信息传达的任何其他机制,但其通常为基于IP的通信网络。虽然在一个实施例中,通信网络1418是因特网,在其他实施例中,通信网络1418可为任何合适的计算机网络。

尽管网络界面的实体硬件组件有时被称作网络适配器(network interfacecard;NIC),但其不必呈卡形式:例如其可为直接安装至主板上的集成电路(ICs)及连接器的形式,或是在与计算机系统的其他组件一起制造于单个集成电路芯片上的巨胞(macrocells)形式。

用户界面输入设备1422可包括键盘、诸如鼠标的指针设备、轨迹球、触摸板或图形平板计算机、扫描仪、并入至显示器中的触摸屏、诸如语音识别系统的音频输入设备、麦克风,以及其他类型的输入设备。大体而言,用语“输入设备”的使用意欲包括用以将信息输入至计算机系统1410中或计算机网络1418上的所有可能类型的装置及方式。

用户界面输出装置1420可包括显示子系统、打印机、传真机或诸如音频输出装置的非视觉显示器。显示子系统可包括阴极射线管(cathode ray tube;CRT)、诸如液晶显示器(LCD)的平板装置、投影装置、或用于产生可见影像的某一其他机制。显示子系统也可诸如经由音频输出装置提供非视觉显示器。大体而言,用语“输出装置”的使用意欲包括用以将信息自计算机系统1410输出至用户或另一机器或计算机系统的所有可能类型的装置及方式。

储存子系统1424储存提供本发明的某些实施例的功能性的基本编程及数据构造。举例而言,实施本发明的某些实施例的功能性的各种模块可储存于储存子系统1424中。这些软件模块通常通过处理器子系统1414执行。作为另一实例,描述图13的部分及全部完整的布局的数据结构以及追踪图13中的存储器芯片接合垫的分配的数据结构可储存于储存子系统1424中。

存储器子系统1426通常包括多个存储器,所述存储器包括用于在程序执行期间储存指令及数据的主要随机存取存储器(RAM)1430及其中储存有固定指令的只读存储器(ROM)1432。档案储存子系统1428提供对程序及数据文件的持久储存,且可包括硬盘驱动机、软式磁盘驱动器以及相关联可拆卸式媒体、CD ROM驱动机、光驱,或可拆卸式媒体盒。实施本发明的某些实施例的功能性的数据库及模块可能已提供于诸如一或多个CD-ROM的计算机可读媒体上且可通过档案储存子系统1428储存。主机存储器1426尤其含有计算机指令,所述计算机指令在由处理器子系统1414执行时使得计算机系统操作或执行如本文中所描述的功能。如本文中所使用,据称在“主机”或“计算机”中或上运行的工艺及软件响应于主机存储器子系统1426中的计算机指令及数据在处理器子系统1414上执行,所述主机存储器子系统包括用于此类指令及数据的任何其他局部或远程储存器。

总线子系统1412提供用于使计算机系统1410的各种组件及子系统如预期的彼此通信的机制。尽管总线子系统1412经示意性地示出为单一总线,但总线子系统的替代性实施例可使用多个总线。

计算机系统1410本身可属于不同类型,包括个人计算机、携带型计算机、工作台、计算机终端、网络计算机、电视、大型计算机、服务器群,或任何其他数据处理系统或用户装置。归因于计算机及网络不断改变的本质,出于绘示本发明的较佳实施例的目的,图14中所描绘的计算机系统1410的描述仅意欲作为特定实例。计算机系统1410的多个其他组态有可能具有比图14中所描绘的计算机系统更多或更少的组件。

在实施例中,用于执行本文中所描述功能中的任一者的软件程序代码部分可储存于一个位置处,且提取及传输至将执行所述软件程序代码部分的计算机系统的位置。传输可采取将程序代码部分写入至非暂时性计算机可读媒体上且将媒体实体地递送至目标计算机系统的形式,或其可采取诸如经由因特网朝向目标计算机系统电子地传输程序代码部分的形式。如本文中所使用,“朝向”目标计算机系统的电子传输在传输离开正确寻址的源到达目标计算机系统时完整。

如本文中所使用,置于基板主体自身中或者置于基板主体的上覆层中的集成电路的物质之间没有区别。举例而言,集成电路的所有特征,包括井、扩散区、STI区域、栅极介电层、栅极导体以及顶盖层材料,在本文中均等效地描述为“在基板上”或“在基板中”,且预期两组字之间没有区别。

本申请人特此在以下限度内单独地揭露本文中所描述的每一个别特征及两个或更多个此类特征的任何组合:此类特征或组合能够鉴于所属领域的技术人员的公知常识并基于本发明作为整体进行,而不顾及此类特征或特征组合是否解决本文中所揭露的任何问题,且不限制申请专利范围的范畴。申请人指示,本发明的方案可由任何此类特征或特征组合组成。鉴于前述描述,对于所属领域的技术人员而言将显而易见的是可在本发明的范畴内进行各种修改。

已出于说明及描述的目的提供本发明的较佳实施例的前述描述。其并不意欲为详尽的或将本发明限制于所揭露的精确形式。显然,多种修改及改变对于所属领域的技术人员而言将显而易见。举例而言,尽管以上描述出于说明的目的使用3D NAND垂直通道阵列作为实例,但本发明的方案也可与其他类型的存储器阵列一起使用,诸如3D NAND垂直栅极、先进平面NAND以及NOR闪存技术。

此外,非限制性地,以引用方式并入本专利申请案中的任何文献中或本专利申请案的先前技术部分中描述、提出的任何及所有变化在本文中特定地以引用的方式并入本发明的实施例的描述中。另外,关于任一个实施例描述、提出或以引用的方式并入本文中的任何及所有变化也将被视为关于所有其他实施例的教示。选择及描述本文中所描述的实施例以便最佳地解释本发明的原理及其实际应用,由此使得所属领域的技术人员能够在具有适合于所涵盖的特定用途的各种修改的情况下理解本发明及各种实施例。希望通过以下申请专利范围及其等效物界定本发明的范畴。

- 堆叠存储器及ASIC装置

- 存储器裸片、堆叠式存储器、存储器装置及方法