在缓冲器上方形成的光电子器件

文献发布时间:2023-06-19 09:29:07

本公开要求于2018年5月29日提交的美国临时专利申请号62/677,563的优先权,其公开内容通过引用整体并入本文。

技术领域

本公开涉及光电子器件,更具体地,本公开涉及在基板上方的缓冲层上形成的光电子器件。

背景技术

使用锑基合金(Sb-based alloys)的常规红外(IR)光探测器经常粘结或使用铟凸点粘附到硅基读出集成电路(silicon-based read-out integrated circuit,ROIC)晶片上以创造焦平面阵列(focal plane array,FPA)。使用锑基合金制造这种结构以粘结常见的红外光探测器的过程需要额外的制造步骤,这可能使ROIC过程复杂化。另外,基于铟凸点的技术也可能带来热管理问题。

发明内容

在一些实施方案中,光电子器件可以包括经由缓冲层在硅基板上生长的锑基变质(metamorphic)光探测器。该器件包括分层结构。这里,形容词“变质”用于表示一个晶体结构在另一个晶体结构上的外延生长,其中两个晶体结构具有不同的晶格间距。在一些实施方案中,分层结构包括基板,在基板上方形成的缓冲层,以及在缓冲层上方形成的红外光探测器。在一些实施方案中,缓冲层包括具有子层的复合缓冲层。例如,在一些实施方案中,复合缓冲层包括在基板上方形成的锗基子层、在锗基子层上生长的III-As子层、以及在III-As子层上方形成的III-Sb子层。

附图说明

本公开根据一个或多个不同实施方案并参考附图详细描述于下文。提供附图仅用于说明的目的,并且仅描绘典型或示例实施方案。所提供这些图式是为了便于理解本文公开的概念,并且不应被视为限制这些概念的广度、范围或适用性。应该注意,为了清楚和便于说明,这些附图不一定按比例绘制。

图1示出了根据本公开的一些实施方案的在基板上方具有光电子器件的示例性分层结构的截面图。

图2示出了根据本公开的一些实施方案的在基板和复合缓冲器上方具有光电子器件的说明性分层结构的截面图;

图3示出了根据本公开的一些实施方案的示例性分层结构的作为偏压的函数的量子效率曲线图;

图4示出了根据本公开的一些实施方案的示例性分层结构的作为波长的函数的量子效率曲线图;

图5示出了根据本公开的一些实施方案的示例性分层结构的作为偏压的函数的暗电流密度曲线图;

图6示出了根据本公开的一些实施方案的示例性分层结构的X射线衍射光谱图。

图7示出了根据本公开的一些实施方案的用于制作分层结构的说明性过程的流程图;以及

图8示出了根据本公开利用具有锑基光探测器的分层结构所产生的两个图像。

具体实施方式

本文描述的结构和方法涉及了包括有缓冲层而形成的光电子器件。在一些实施方案中,光电子器件包括经由缓冲层而在硅基板上方生长的锑基变质光探测器。例如,缓冲层可以包括复合Ge/III-As/III-Sb缓冲层。在说明性示例中,红外光探测器可以形成为焦平面阵列(FPA)的一部分,其可以用于光谱观察(例如,结合望远镜系统或其他光学系统),红外线感测、成像或其组合。

诸如红外光探测器之类的光电子器件可以基于GaSb材料,其提供丰富的带隙工程设计可能性,例如II型破裂间隙对准(type-II broken-gap alignment)。这些带隙属性允许许多器件架构。例如,器件架构可以基于单极势垒设计概念,其可以被称为“nBn”或“XBn”。例如,制造基于nBn的较大格式FPA探测器需要较大直径的晶片基板以提高产量、容积和产率。在一些实施方案中,本公开提供了一种集成锑基变质光电子器件的分层结构。光电子器件可以包括基于在单个外延堆栈中的单极设计的红外光探测器,其允许了外延堆栈支持大面积FPA。红外光探测器的集成提供了硅基电子电路的高水平批量生产、高速以及III-V材料的期望光学性能的组合优点,其中III-V材料可以是外延堆栈的一部分。在一些实施方案中,硅基板包括硅晶片,其具有已经加工到晶片中的适当电路(例如,互补金属氧化物半导体(CMOS)兼容电路)。例如,可以将ROIC加工到晶片中。在另一示例中,ROIC可以设置在光探测器外延的正下方或者设置在基板的相邻部分中(例如,与缓冲层和光探测器结构相邻)。在一些实施方案中,在基板上形成ROIC改善了外延堆栈的热管理。

图1示出了根据本公开的一些实施方案的具有在基板102上方的光电子器件106的说明性分层结构100的截面图。

在一些实施方案中,基板102包括了具有预定晶体取向的硅晶片。例如,基板102可以包括晶体取向<100>的晶体硅基板。在另一示例中,基板102可以包括(100)面,其具有朝向[111]取向的错切(例如,6°或任何其他合适的取向),作为形成缓冲层104的表面。在一些实施方案中,基板102包括一个或多个预形成的电路或器件。例如,基板102可以包括ROIC或其他合适的电路(例如,CMOS兼容电路)。基板102可以包括任何合适的材料、其区域、器件、电路、包括器件的区域、包括电路的区域、或其任何组合。

在基板102上方形成缓冲层104。如图1所示,缓冲层104可以直接形成在基板102上。在一些实施方案中,通过变质外延在基板102上形成缓冲层104。在一些实施方案中,缓冲层104包括多于一个的层,每层由合适的材料形成。包括了缓冲层104以在基板102和光电子器件106之间提供过渡。该过渡可包括化学过渡、晶格常数过渡、材料性质的过渡、任何其它适当的过渡、或上述过渡的任何组合。在例如图2的情况中描述缓冲层的进一步细节。

光电子器件106形成在缓冲层104上。在一些实施方案中,光电子器件106包括III族和V族元素的一种或多种合金。在一些实施方案中,光电子器件106可以包括多于一种的V族元素以及一种III族元素。例如,光电子器件106可以包括InAs

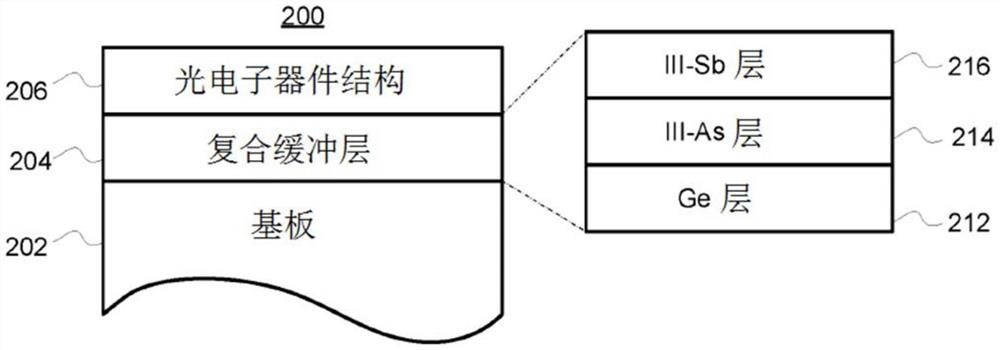

图2示出了根据本公开的一些实施方案的说明性分层结构200的截面图,该说明性分层结构200具有在基板202和复合缓冲层204上方的光电子器件206。在一些实施方案中,分层结构200是图1的分层结构100的示例,其中复合缓冲层204是缓冲层104的示例。

在一些实施方案中,基板202包括具有预定晶体取向的硅晶片。例如,基板202可以包括具有晶体取向<100>的晶体硅基板。在一些实施方案中,基板202包括一个或多个预形成的电路或器件。例如,基板202可以包括ROIC或其他合适的电路。基板202可包括任何合适的材料、其区域、器件、电路、包括器件的区域、包括电路的区域、或其任何组合。

在基板202上方形成复合缓冲层204。如图2所示,复合缓冲层204可以直接逐层地形成在基板202上。在一些实施方案中,复合缓冲层204的一个或多个层通过变质外延形成在基板202上或复合缓冲层204的先前层上。复合缓冲层204在基板202和光电子器件206之间提供过渡。所述过渡可以包括化学过渡、晶格常数过渡、材料性质的过渡、任何其它合适的过渡,或上述过渡的任何组合。如图所示,复合缓冲层204包括三个子层(例如,一组层中的层)。在基板202上方形成锗层212。例如,可以在基板202上外延形成锗层212。在另一个例子中,可以在化学气相沉积(CVD)反应腔中在基板202上方形成锗层212。在锗层212上方形成砷基层(例如,III-As层214)。在III-As层214上方形成锑基层(例如,III-Sb层216)。例如,可以通过外延法在III-As层214上方形成III-Sb层216。

光电子器件206形成在复合缓冲层204上方。例如,光电子器件206形成在III-Sb层216上方。在一些实施方案中,光电子器件206包括一种或多种III族和V族元素的合金。在一些实施方案中,光电子器件206可以包括多于一种的V族元素以及一种III族元素。例如,光电子器件206可以包括InAs

分别示出于图3~图6的曲线图300、400、500和600所呈现的数据对应于与图2的分层结构200类似的分层结构。分层结构包括硅基板,其具有复合缓冲层以及在缓冲层上方形成的锑基光探测器(例如,光二极管)。显示在图3~图6中的数据来自没有钝化的大面积台面二极管或抗反射涂层。对于图3所示的曲线图300,其器件性能是在150K下、以正面照射、且搭配3.1μm带通滤波器来测量。

图3示出了根据本发明的示例性分层结构的作为偏压的函数的量子效率的曲线图300。量子效率是衡量入射光转换为电能的百分比的量度。曲线图300示出了与图2的分层结构200类似的说明性结构的数据。例如,如曲线图300所示,可以在约-0.1V或更小的偏压下实现超过60%的量子效率。

图4示出了根据本发明的示例性分层结构的作为波长的函数的量子效率的曲线图400。所示波长对应于在类似于图2的分层结构200的说明性结构处入射的光的波长。例如,如曲线图400所示,可以在约2-4微米的光谱范围内(例如,短红外到中红外波长)实现高于50%的量子效率。

图5示出了根据本发明的示例性分层结构的作为偏压的函数的暗电流密度的曲线图500。暗电流密度(例如,没有入射辐射)可以提供光探测器的电噪声的指示。曲线图500示出了类似于图2的分层结构200的说明性结构的暗电流密度结果。例如,曲线图500示出了在-0.2V的偏压下约2×10

可以在外延层使用各种技术来评估分层结构(例如,图1的分层结构100或图2的分层结构200)。例如,X射线衍射(XRD)技术可用于识别晶格和其取向。图6显示了根据本发明的示例性分层结构的XRD光谱的曲线图600。曲线图600示出了具有三个不同峰值的说明性高分辨率XRD光谱,其源自(1)III-Sb缓冲子层和nBn光探测器结构(例如,峰值601),(2)GaAs(例如,III-As缓冲子层)和锗缓冲子层(例如,峰值602),以及(3)硅基板(例如,峰值603)。来自III-Sb和光探测器层的相对尖锐峰值表明了下层缓冲器设计的优异结构特性和有效性。

图7是根据本公开的用于制造分层结构的说明性过程700的流程图。例如,图1和图2分别示出的说明性分层结构100和200可以通过过程700来形成。

步骤701包括制备基板。步骤701可以包括生长单晶晶片、形成硅晶片、处理或以其他方式准备基板的表面、在基板上形成一个或多个电路、在基板上形成一个或多个器件、以及用来准备基板以进行进一步加工的任何其他适合的动作、或上述动作的任何组合。基板可以包括,例如,具有错切表面(例如,错切(100)表面)的晶体基板、具有CMOS电路的基板、绝缘体上硅、绝缘体上锗、锗、晶格工程设计基板上硅(silicon-on-lattice-engineered-substrate,SOLES)、具有相关晶格常数的任何其他合适的基板、或上述情况的任何组合。

步骤702包括在步骤701的基板上方形成缓冲层。在一些实施方案中,步骤702包括在基板上直接形成缓冲层。在一些实施方案中,步骤702包括使用变质外延形成缓冲层,其中缓冲层是具有与基板不同的晶格常数的外延层。例如,在一些实施方案中,步骤702至少部分地在分子束外延(MBE)反应腔中进行。在另一个实例中,在一些实施方案中,步骤702至少部分地在化学气相沉积(CVD)反应腔中进行。在一些实施方案中,步骤702包括形成多层缓冲器,其中形成多于一个的子层。例如,步骤702可以包括如图7所示的步骤712、714和716。在另一个例子中,这些子层可以依次直接地形成在基板和彼此之上。在一些实施方案中,步骤702包括使用多于一个的过程在多于一个的腔室中加工该结构。

步骤712包括在基板上方形成第一子层。第一子层可以包括在基板上方形成的锗基材料。在一些实施方案中,步骤712包括在基板上直接形成第一子层。在一些实施方案中,步骤712包括利用变质外延来形成第一子层。在说明性示例中,步骤712可以包括在基板上方形成锗层(例如,其可以是0.5~1.0微米的厚度或任何其他适当的厚度)。在另一个说明性实例中,液相化学气相沉积(CVD)工具可用于形成晶种层,然后形成主体锗层。在一些实施方案中,步骤712包括基板的表面准备。例如,在形成第一子层之前,可用氢来去除基板表面上的自然氧化物。在使用硅基板和锗第一子层的说明性示例中,步骤712得到的结构可以称为硅上锗基板。在说明性实例中,可以将硅上锗基板从CVD处理中取出,然后将其引入MBE反应腔以进行进一步的处理。

步骤714包括在第一子层上方形成第二子层。第二子层可以包括在第一层上方形成的III-As材料(即,III族元素和砷)。在一些实施方案中,步骤714包括直接在第一子层上方形成第二子层。在一些实施方案中,步骤714包括利用变质外延形成第二子层。例如,步骤714可以包括将MBE应用于第一子层的表面以形成第二子层。在说明性实例中,可以使用一个或多个带阀门的裂化器源(cracker source)来提供V族材料(例如,砷和/或锑)。在另一个说明性实例中,一个或多个SUMO单元或锥形喷射单元可用于提供III族材料(例如,铝、镓和/或铟)。为了说明,第二子层可以是GaAs子层。

步骤716包括在第二子层上方形成第三子层。第三子层可以包括在第二层上方形成的III-Sb材料(即,III族元素和锑)。在一些实施方案中,步骤716包括直接在第二子层上方形成第三子层。在一些实施方案中,步骤716包括利用变质外延形成第二子层。因为第三子层可以是锑基(Antimony-based)的,所以可以更容易地在第三子层上方外延形成锑基光探测器结构。例如,第三子层的晶格常数可以类似于在步骤704形成的光电子器件结构的晶格常数。在一些实施方案中,步骤716可以包括将分子束外延(MBE)应用于第二子层的表面以形成第三子层。在说明性示例中,可以使用一个或多个带阀门的裂化器源来提供V族材料。在另一个说明性实例中,可以一个或多个SUMO单元或锥形喷射单元(conical effusioncell)来提供III族材料(例如,铝、镓和/或铟)。在一些实施方案中,步骤714和716在相同的反应腔(例如,MBE腔)中进行。

步骤704包括在步骤702的缓冲层上方形成光电子器件。红外光探测器可以包括在缓冲层上方形成的锑基材料。在一些实施方案中,步骤704包括直接在缓冲层(例如,复合缓冲层的第三子层)上方形成光电子器件。在一些实施方案中,步骤704包括利用变质外延形成红外光探测器。例如,步骤704可以包括藉由形成大约4微米厚的吸收层(例如,InAsSb吸收层),然后在吸收层上方形成势垒层(例如,AlAsSb势垒层),然后在势垒层上方形成顶部接触层(例如,Si掺杂的InAsSb接触层)来形成红外光探测器。在另一示例中,红外光探测器可以是锑基nBn光探测器。在一些实施方案中,红外光探测器具有约4微米的截止波长。

在说明性示例中,过程700可包括在硅上利用含锗的缓冲层进行整个变质光探测器结构的全晶片外延生长。在一些实施方案中,过程700是用于形成锑基光电子器件(例如红外光探测器)的可调整、多步骤,硅到锗到III-V族、M-缓冲器的方法。

图8示出了根据本公开利用具有锑基红外光探测器的分层结构产生的图像800和850。红外光图像800和850都是利用包括在Ge-Si基板上形成的多个nBn型红外光探测器的焦平面阵列在77K下产生的。因此,可以利用本公开的变质外延形成的结构来实现高质量的光探测。图像800包括插图,其示出了利用可见光范围拍摄所拍的图像,以供参考。

贯穿本公开的内容,“单片集成的”是指形成在基板表面上的,通常通过沉积设置在表面上的层进行。

“设置在…上”是指存在于下面的材料或层之上。这种层可包括中间层,例如过渡层,这对于确保合适的表面是必需的。例如,如果材料被描述为“设置在基板上”,则这可以意味着(1)材料与基板紧密接触;或(2)该材料与位于基板上的一个或多个过渡层接触。

单晶是指基本上仅包含一种类型晶胞的晶体结构。然而,单晶层可能表现出一些晶体缺陷,例如堆栈缺陷、位错或其他常见的晶体缺陷。

单域是指晶体结构,其基本上仅包含一种晶胞结构,并且基本上仅包含一种晶胞取向。换句话说,单域晶体不表现出孪晶或反相域。

单相是指即是单晶又是单域的晶体结构。

基板是指在其上方形成沉积层的材料。示例性基板包括但不限于:主体硅晶片(bulk silicon wafer),其中晶片包括均匀厚度的单晶硅、复合晶片(例如绝缘体上硅晶片,其包括在二氧化硅层上形成的硅层,所述二氧化硅层形成在主体硅晶片上)、或者是用作基底层的任何其它合适的材料(在该基底上或基底内形成器件)。随着应用的不同,适合用作基板层和主体基板的这种其它材料的实例包括但不限于锗、IV族元素的合金(例如SiGe、SiGeSn、GeSn)、氧化铝、砷化镓、磷化铟、氧化硅、二氧化硅、硼硅酸盐玻璃、派热克斯玻璃和蓝宝石。在一些非限制性实例中,基板层可包括具有相同或不同孔隙率的多孔材料的一个或多个部分或子层。

错切基板是指这样的基板,其所包含的表面晶体结构的取向相对于与该基板的晶体结构相关的取向成一角度。例如,6°错切<100>硅晶片包括<100>硅晶片,其已经以与<100>晶体取向成一6°角切割而朝向另一个主要晶体取向(例如<111>)。通常但不一定,错切将达到约20°。除非特别指出,否则短语“错切基板”包括具有任何主要晶体取向的错切晶片。也就是说,<111>晶片朝向<011>方向错切,<100>晶片朝向<110>方向错切,而<011>晶片向<001>方向错切。

本文描述和/或描绘为在第二层“上”或“上方”的第一层可以紧邻第二层,或者一个或多个中间层可以在第一层和第二层之间。在本文中描述和/或描绘为“直接在第二层或基板上”或“直接在第二层或基板上方”的第一层紧邻第二层或基板而不存在中间层,除了可能的可以由于第一层与第二层或基板的混合而形成的中间合金层之外。另外,在本文中描述和/或描绘为在第二层或基板“上”、“上方”、“直接在上”或“直接在上方”的第一层可以覆盖整个第二层或基板,或者覆盖第二层或基板的一部分。

基板的顶表面是接收一个或多个外延层的表面(例如,“外延就绪”表面)。当形成层时,“顶部”表面或“上”表面是离基板最远的层。本文描绘和描述的任何结构可以是较大结构的一部分,在所描绘的那些之上和/或之下具有附加层。为清楚起见,本文中的附图可省略这些附加层,尽管这些附加层可以是所公开结构的一部分。另外,所描绘的结构可以单元重复,即使这些重复未在附图中示出。

前述内容仅仅是对本公开的原理的说明,并且本领域技术人员可以在不脱离本公开的范围的情况下进行各种修改。提供上述实施方案是出于说明而非限制的目的。除了在此明确描述的那些之外,本公开还可以采用许多形式。因此,要强调的是,本公开不限于明确披露的方法、系统和装置,而是旨在包括在权利要求书的精神内的变形和修改。

- 在缓冲器上方形成的光电子器件

- 用于在有机光电子器件中形成电互连的方法、用于制造有机光电子器件的方法以及有机发光器件