优化的SM4算法线性层电路

文献发布时间:2023-06-19 10:16:30

技术领域

本发明涉及SM4算法的加密实现技术,具体的涉及一种优化的SM4算法线性层电路。

背景技术

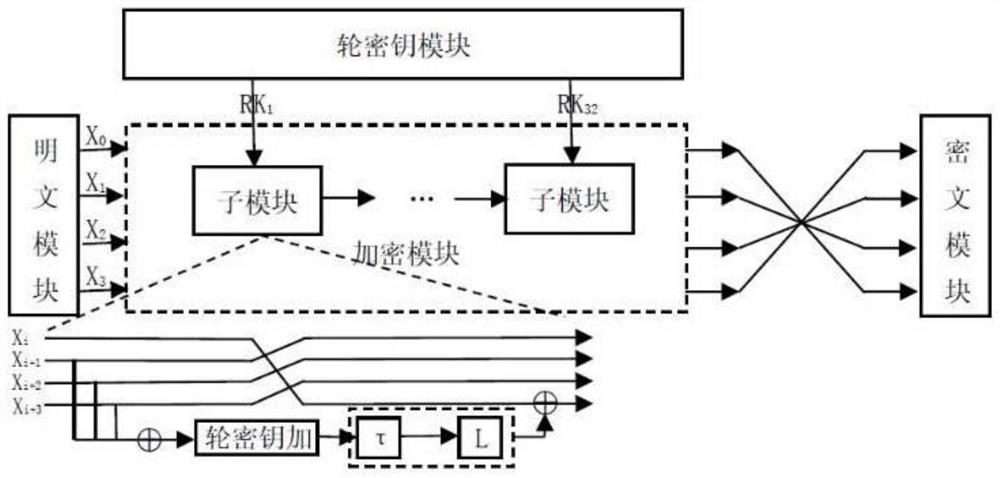

随着轻量级应用越来越普遍,为了适应资源受限平台,密码算法的优化实现越来越受到广泛关注,如图1所示,我国商用分组密码标准(SM4算法)属于常用密码算法的一种,是我国国家密码管理局发布的密码行业标准,适用于无线局域网和可信计算系统,在我国密码行业中占据着极其重要的地位。

扩散作为设计密码算法的两个基本准则之一,对于密码算法的安全性起着至关重要的作用,而密码算法的线性部件是实现扩散的主要组件。因此,在研究密码算法的硬件实现时,线性部件的硬件实现开销也不容忽视。

密码算法线性层可由矩阵表示,其实现代价也可由实现该矩阵所需异或数来评估。研究表明,求解线性矩阵的最少异或数实现(即最优实现)是一个NP-困难问题。因此,学者们提出了一系列高效的启发式算法搜索矩阵的优化实现,比如算法Paar1、RPaar1、Paar2、BP、BFI(Banik等人的方法)、RNBP、A1以及A2。值得注意的是,这些算法给出的矩阵实现与矩阵的大小以及稠密度有关,对于较大、较稠密的矩阵,上述搜索算法给出的实现仍有进一步优化的空间。

发明内容

本发明要解决的技术问题是针对以上不足,提供一种优化的SM4算法线性层电路,可减少电路所需异或门电路数量来降低密码算法线性层的实现成本以及所需硬件面积,从而达到优化整体密码算法硬件实现的目的。

为解决以上技术问题,本发明采用以下技术方案:

优化的SM4算法线性层电路,包括第一模块、第二模块、第三模块、第四模块、第五模块和第六模块,设线性层电路总输入信号为{x

x

t

t

所述第二模块的输入信号为:

x

t

t

所述第三模块的输入信号为:

x

t

t

所述第四模块的输入信号为:

t

t

所述第五模块的输入信号为t

t

所述第六模块的输入信号为t

本发明的有益效果为:本发明给出的优化的SM4算法线性层电路中异或门电路数目前已知最优(即最少)。本发明减少了SM4算法线性变换的实现代价,进而降低了整体密码算法硬件实现的成本及面积。

下面结合附图和实施例对本发明进行详细说明。

附图说明

图1为SM4算法原始实现流程图;

图2为SM4算法迭代搜索矩阵的优化实现框架图;

图3为本发明的优化的SM4算法线性层模块连接图;

图4为本发明的第一模块电路图;

图5为本发明的第二模块电路图;

图6为本发明的第三模块电路图;

图7为本发明的第四模块电路图;

图8为本发明的第五模块电路图;

图9为本发明的第六模块电路图。

具体实施方式

以下结合附图对本发明的原理和特征进行描述,所举实例只用于解释本发明,并非用于限定本发明的范围。

如图1所示为SM4密码算法流程图,本发明涉及的电路是优化整个算法中的线性层L部分对应电路。

本发明的线性层电路的得到方法为,扩充SM4算法线性部件对应的矩阵,得到该矩阵在二元域上的表示;优化矩阵的实现,减少实现该矩阵所需异或门电路数量;列出算法线性部件的门级硬件电路图。具体步骤为:

S1、扩充算法线性部件对应的矩阵,得到该矩阵在二元域上的表示

对于SM4算法,其线性变换可由矩阵

于是,矩阵L可扩充为二元域F

S2.优化矩阵的实现,减少实现该矩阵所需异或门电路数量

线性部件的输出为其输入的线性表达,相应的,在硬件实现其对应的矩阵时,任一输出信号可由输入信号线性表示。因此,目前的研究通常通过统计实现矩阵所有输出信号所消耗的异或门电路数目来评估算法线性层的实现代价。本发明沿用这种方法,设硬件实现时矩阵的输入信号为{x

本发明基于如图2所示框架,迭代搜索SM4算法线性层线性变换对应矩阵L的优化实现。

下面,我们介绍利用该框架搜索矩阵L的优化实现的步骤。

S2.1:将矩阵L作为该框架的输入,并从Paar1、RPaar1、BP、BFI、RNBP、A1以及A2中随机选择一个算法求解矩阵L的初始实现A。A由有限个(设为n)形如t

S2.2:从上述实现A中截取长度为LEN(LEN∈[2,n-1],且初始值为n-1。)的连续片段,记为片段2,并依此恢复出矩阵L’。下面我们给出根据片段2恢复出矩阵L’的一般过程:

S2.2.1:求矩阵L’的输出;

片段2也是由若干形如t

S2.2.2:求矩阵L’的输入;

由步骤S2.2.1可得矩阵L’的输出集合S

S2.2.3:根据输入集合S

S2.3:再次从Paar1、RPaar1、BP、BFI、RNBP、A1以及A2中随机选择一个算法求解矩阵L’的实现,该实现与截取片段2等价。用矩阵L’的实现替换片段2,得到矩阵L新的实现。

S2.4:使用下列有助于减少实现代价的约简规则优化替换后矩阵L的实现;

如表1所示,我们以规则2为例简要说明上述规则实现约简的原理。假设给定的实现形如{…,t

表1约简规则表

对于替换后矩阵L的实现,我们从该实现中任取2或3个寄存器(形如t

利用上述框架,我们得到如下表2所示SM4线性层线性变换对应矩阵L的优化实现。

表2 SM4算法线性变换矩阵L的优化实现

S3.列出算法线性部件的门级硬件电路图

利用目前已知基于g-xor标准求解矩阵实现的技术(Paar1,RPaar1,Paar2,BP,BFI,RNBP,A1,A2),本发明涉及的SM4算法线性层线性变换对应矩阵L的实现代价如下表所示:

表3、现有技术实现SM4算法线性层线性层异或门数量

本发明的SM4算法线性层线性变换对应矩阵实现所消耗的异或数为83,目前已知最优。

如表2所示,实现SM4算法线性变换对应矩阵所需异或门电路数为83,深度为6,因此,如图3所示,SM4算法线性变换的硬件实现可分为六个模块。所有模块均为异或门电路的集成,除初始模块(第一模块),其他各模块均受深度较浅模块的影响。各模块的输入输出分析如下:

(1)第一模块:

第一模块的输出信号受SM4算法线性变换的部分输入信号影响,该模块的输出信号又会影响第二模块、模块三以及第四模块的输出信号值。

输入:

x

输出:

t

t

(2)第二模块

第二模块的输出信号受SM4算法线性变换的部分输入信号以及第一模块的部分输出信号影响,该模块的输出信号又会影响第三模块、第四模块、第五模块以及第六模块的输出信号值。

输入:

x

输出:

t

具体包括21个异或门电路集成,分别为:

t

(3)第三模块

第三模块的输出信号受SM4算法线性变换的部分输入信号以及第一模块和第二模块的部分输出信号影响,该模块的输出信号又会影响第四模块的输出信号值。

输入:

x

输出:

t

t

(4)第四模块

第四模块的输出信号受SM4算法线性变换实现第一模块、第二模块以及第三模块的部分输出信号影响,该模块的输出信号又会影响第五模块的输出信号值。

输入:

t

输出:y

具体包括13个异或门电路,分别为:

t

(5)第五模块

第五模块的输出信号受SM4算法线性变换实现第二模块以及第四模块的部分输出信号影响,该模块的输出信号又会影响第六模块的输出信号值。

输入:t

输出:y

具体包括4个异或门电路集成,分别为:

t

(6)第六模块

第六模块的输出信号受SM4算法线性变换实现第二模块以及第五模块的部分输出信号影响。

输入:t

输出:y

具体包含两个异或门电路,输出信号为:t

图3中所有模块均为异或门电路的集成,各模块的电路实现已由图4-9具体给出。由于各模块所需异或门电路总数达到目前已知最优,图4-9给出的电路实现降低了算法线性部件的实现代价。基于上述实现,本发明可以减少对应模块的实现成本以及面积,从而达到优化整体算法硬件实现的目的。

由表3的结果可知,与现有技术给出的SM4算法线性层硬件电路相比,本发明给出的SM4算法线性层硬件电路中异或门数量最优。以上所述为本发明最佳实施方式的举例,其中未详细述及的部分均为本领域普通技术人员的公知常识。本发明的保护范围以权利要求的内容为准,任何基于本发明的技术启示而进行的等效变换,也在本发明的保护范围之内。

- 优化的SM4算法线性层电路

- 一种搜索密码算法线性层硬件实现优化的启发式算法