多核计算芯片

文献发布时间:2023-06-19 10:19:37

技术领域

本申请涉及芯片技术领域,特别是涉及一种多核计算芯片。

背景技术

芯片内部由大量的晶体管单元组成,在生产加工过程中容易不可避免的引入一些制造缺陷,导致一些单元不能正常工作,导致整个芯片无法正常工作。因此必须对芯片进行测试,识别出有瑕疵的芯片。

随着工艺节点的降低,芯片面积的增大,单芯片内部发生制造缺陷的概率也随之增加。现有的芯片测试方式一般是在芯片被集成到终端产品之前用测试机台将有瑕疵的芯片检测出来,并将有瑕疵的芯片丢弃掉。

但是,现有技术无法对多核芯片(即多个计算引擎)进行定时或实时检测;当只有个别核心(即计算引擎)有制造缺陷而采取丢弃的方式会大幅降低芯片的良率并增加芯片的成本;对于在使用过程中出现的功能性错误,只能采取更换芯片的方式修复,增加维修成本。

发明内容

基于此,本申请提供一种多核计算芯片,能够对多核芯片定时或实时检测,能够对异常核心进行处理,从而为降低芯片成本和维修成本提供技术支持。

第一方面,本申请提供一种多核计算芯片,所述多核计算芯片包括多个用于并行计算的计算引擎,所述多核计算芯片还包括:

存储部件,用于存储测试向量和所述测试向量对应的预期结果;

控制与测试部件,用于控制所述计算引擎根据所述存储部件中存储的测试向量对自身进行测试得到所述计算引擎的所述测试向量对应的测试结果,结合所述存储部件中存储的所述测试向量对应的预期结果,确定所述多个计算引擎中是否存在异常计算引擎。

第二方面,本申请提供另一种多核计算芯片,所述多核计算芯片包括多个用于并行计算的计算引擎,所述多核计算芯片还包括:

异常核心处理部件,用于在多个计算引擎中存在异常计算引擎时,在控制指令下对所述异常计算引擎进行处理;

对所述异常计算引擎进行处理包括:对所述异常计算引擎进行标记处理和/或在处于工作模式时对所述异常计算引擎进行屏蔽处理。

本申请实施例提供了一种多核计算芯片,所述多核计算芯片包括多个用于并行计算的计算引擎,还包括:存储部件,用于存储测试向量和所述测试向量对应的预期结果;控制与测试部件,用于控制所述计算引擎根据所述存储部件中存储的测试向量对自身进行测试得到所述计算引擎的所述测试向量对应的测试结果,结合所述存储部件中存储的所述测试向量对应的预期结果,确定所述多个计算引擎中是否存在异常计算引擎。由于存储测试向量和所述测试向量对应的预期结果的存储部件和控制所述计算引擎对自身进行测试的控制与测试部件和计算引擎集成在一起,属于芯片不可分割的部件,通过这种方式,能够对多核计算芯片中的多个计算引擎进行定时或实时检测。

本申请实施例还提供了另一种多核计算芯片,所述多核计算芯片包括多个用于并行计算的计算引擎,还包括:异常核心处理部件,用于在多个计算引擎中存在异常计算引擎时,在控制指令下对所述异常计算引擎进行处理;对所述异常计算引擎进行处理包括:对所述异常计算引擎进行标记处理和/或在处于工作模式时对所述异常计算引擎进行屏蔽处理。由于在存在异常计算引擎时能够对异常核心进行处理,对异常计算引擎进行标记处理和/或在处于工作模式时对异常计算引擎进行屏蔽处理,这样当异常计算引擎数量不多时,可以保留该芯片,不用丢弃掉,能够提高芯片良率、降低芯片成本;对异常计算引擎进行屏蔽处理,其他正常计算引擎可以继续使用,不用更换芯片,从而能够降低维修成本,因此,对异常核心进行处理能够为降低芯片成本和降低维修成本提供技术支持。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。

附图说明

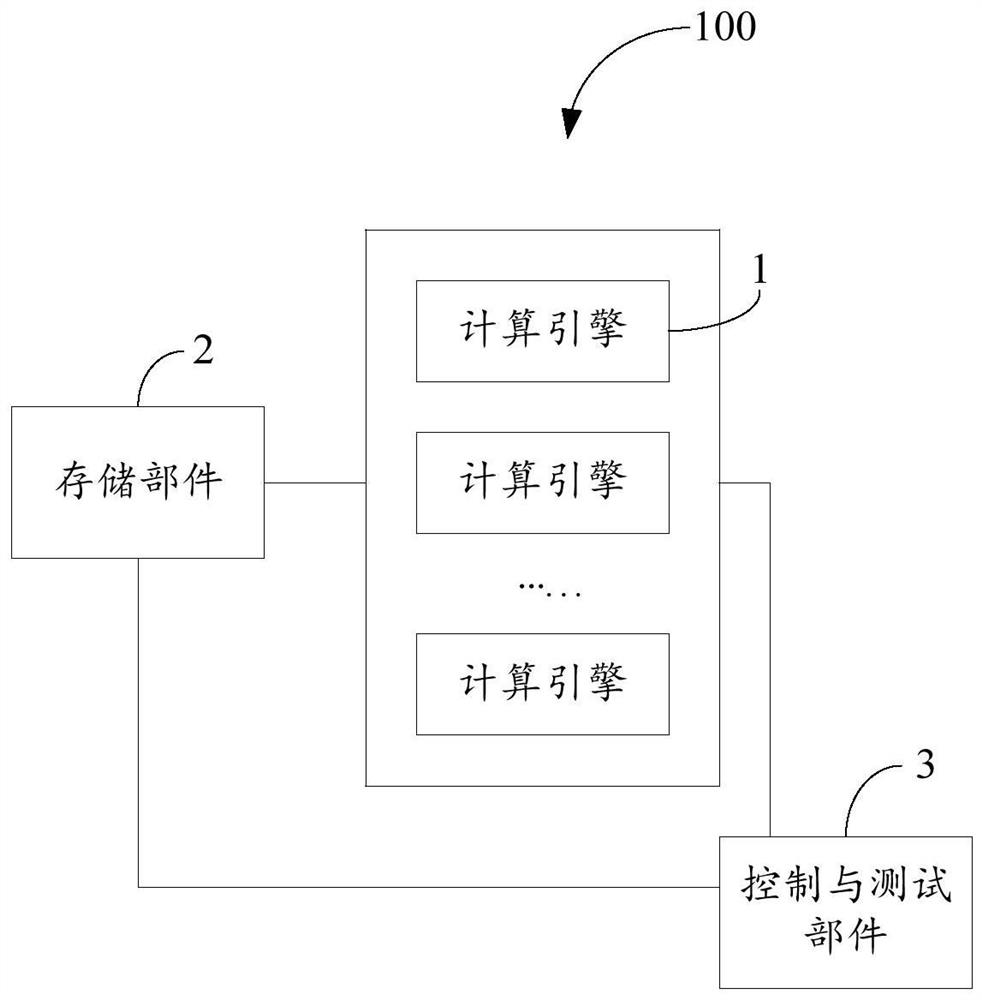

图1是本申请多核计算芯片一实施例的结构示意图;

图2是本申请多核计算芯片另一实施例的结构示意图;

图3是本申请多核计算芯片又一实施例的结构示意图;

图4是本申请多核计算芯片又一实施例的结构示意图;

图5是本申请多核计算芯片又一实施例的结构示意图;

图6是本申请多核计算芯片又一实施例的结构示意图;

图7是本申请多核计算芯片又一实施例的结构示意图;

图8是本申请多核计算芯片又一实施例的结构示意图。

主要元件及符号说明:

100、多核计算芯片;

1、计算引擎;2、存储部件;21、测试向量存储部件;22、预期结果存储部件;3、控制与测试部件;31、测试结果比对部件;32、控制部件;4、异常核心处理部件;41、异常核心标记部件;42、异常核心屏蔽部件;

200、上层系统。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

附图中所示的流程图仅是示例说明,不是必须包括所有的内容和操作/步骤,也不是必须按所描述的顺序执行。例如,有的操作/步骤还可以分解、组合或部分合并,因此实际执行的顺序有可能根据实际情况改变。

芯片在生产加工过程中容易引入制造缺陷,导致一些单元不能正常工作,导致整个芯片无法正常工作。因此必须对芯片进行测试,识别出有瑕疵的芯片。现有的芯片测试方式一般是在芯片被集成到终端产品之前用测试机台将有瑕疵的芯片检测出来,并将有瑕疵的芯片丢弃掉。但是现有技术无法对多核芯片(即多个计算引擎)进行定时或实时检测;当个别核心(即计算引擎)有制造缺陷而丢弃芯片,会降低芯片良率并增加芯片成本;对芯片在使用中出现的功能性错误,更换芯片会增加维修成本。

本申请实施例提供了一种多核计算芯片,所述多核计算芯片包括多个用于并行计算的计算引擎,还包括:存储部件,用于存储测试向量和所述测试向量对应的预期结果;控制与测试部件,用于控制所述计算引擎根据所述存储部件中存储的测试向量对自身进行测试得到所述计算引擎的所述测试向量对应的测试结果,结合所述存储部件中存储的所述测试向量对应的预期结果,确定所述多个计算引擎中是否存在异常计算引擎。由于存储测试向量和所述测试向量对应的预期结果的存储部件和控制所述计算引擎对自身进行测试的控制与测试部件和计算引擎集成在一起,属于芯片不可分割的部件,通过这种方式,能够对多核计算芯片中的多个计算引擎进行定时或实时检测。

本申请实施例还提供了另一种多核计算芯片,所述多核计算芯片包括多个用于并行计算的计算引擎,还包括:异常核心处理部件,用于在多个计算引擎中存在异常计算引擎时,在控制指令下对所述异常计算引擎进行处理;对所述异常计算引擎进行处理包括:对所述异常计算引擎进行标记处理和/或在处于工作模式时对所述异常计算引擎进行屏蔽处理。由于在存在异常计算引擎时能够对异常核心进行处理,对异常计算引擎进行标记处理和/或在处于工作模式时对异常计算引擎进行屏蔽处理,这样当异常计算引擎数量不多时,可以保留该芯片,不用丢弃掉,能够提高芯片良率、降低芯片成本;对异常计算引擎进行屏蔽处理,其他正常计算引擎可以继续使用,不用更换芯片,从而能够降低维修成本,因此,对异常核心进行处理能够为降低芯片成本和降低维修成本提供技术支持。

下面结合附图,对本申请的一些实施方式作详细说明。在不冲突的情况下,下述的实施例及实施例中的特征可以相互组合。

参见图1,图1是本申请多核计算芯片一实施例的结构示意图,本实施例中,多核可以是指多个核心,核心可以是指计算引擎(Compute Engine),计算引擎可以是指专为大规模数据处理而设计的快速通用的一个动力核心;根据不同的计算目的会有很多不同的类别;能够提供按需计算(compute-on-demand)服务。计算引擎可以具有如下特点:专注于计算本身;计算速度很快,支持交互式计算和复杂算法;可以包括通用计算引擎,可用它来完成各种各样的运算,也可以包括各种各样的计算引擎来分别处理不同的运算。

多核计算芯片100包括多个用于并行计算的计算引擎1、存储部件2以及控制与测试部件3。

存储部件2用于存储测试向量和所述测试向量对应的预期结果;控制与测试部件3用于控制所述计算引擎1根据所述存储部件2中存储的测试向量对自身进行测试得到所述计算引擎1的所述测试向量对应的测试结果,结合所述存储部件2中存储的所述测试向量对应的预期结果,确定所述多个计算引擎1中是否存在异常计算引擎。

本实施例中,测试向量可以是指用于测试芯片功能是否正常的一组激励数据,能够用来检测芯片内部是否有损坏,是否有瑕疵。测试向量对应的预期结果可以是指测试向量对应的芯片功能正常的预期测试结果,可以认为芯片没有损坏、没有瑕疵;测试向量和预期结果有映射关系,即确定的测试向量对应确定的预期结果。在实际应用中,可以通过电脑模拟仿真的方式确定测试向量和对应的预期结果。

如果多个计算引擎的结构都是一样的,多个计算引擎可以采用同一个测试向量和对应的同一个预期结果。如果采用不同的测试向量进行测试,对应的预期结果也不一样,测试向量和预期结果可以进行编号。

测试向量和所述测试向量对应的预期结果可以预先存储在存储部件2中(即预先将测试向量和对应的预期结果固定在芯片内部);也可以在芯片需要测试的时候再将测试向量和所述测试向量对应的预期结果通过芯片的通信写入到多核计算芯片内部的存储部件中,相比预先将测试向量和预期结果固定在芯片内部,这种方式更加灵活。

在实际应用中,多核计算芯片100可以根据外部控制系统的指令,多核计算芯片100自动执行将存储在存储部件2中的测试向量发送给计算引擎1,计算引擎1根据测试向量自动进行测试。或者,控制与测试部件3可以根据外部控制系统的指令,向计算引擎1和存储部件2发送控制指令,存储部件2自动将测试向量发送给计算引擎1,计算引擎1根据测试向量自动进行测试。或者,控制与测试部件3可以根据外部控制系统的指令,向计算引擎1和存储部件2发送控制指令,计算引擎1自动从存储部件2获取测试向量,并根据测试向量自动进行测试。

其中,多个计算引擎1可以同时收到测试向量并同步执行测试向量进行自动测试,也可以根据芯片空闲状态,依次将空闲的计算引擎1测试完毕,或者在固定时间依次将计算引擎1测试完毕,或者在需要的时候实时依次将计算引擎1测试完毕,等等。一般来说,依次测试每个计算引擎比较容易实现。计算引擎1测试后测试向量对应的测试结果可以携带计算引擎1的自身编号,这样可以在确定测试结果不正常时,能够得知是哪个计算引擎不正常。

需要说明的是,本申请实施例的多核计算芯片特别适用于隐私计算领域。在大数据时代中,海量的数据的交叉计算和人工智能的发展为各行各业提供了更好的支持,但这些被使用的数据往往包含用户的隐私数据,或企业/机构的内部数据。这些数据由于数据安全和隐私的考虑,往往是不对外开发,例如政府数据由于政策保密性完全不能对外公布,运营商、互联网公司收集到的客户数据,也不能透露给第三者,因此形成了一个个数据孤岛,数据之间不能互通,数据的价值无法体现。如何应用海量的数据,实现数据流动,同时能够保护数据隐私安全、防止敏感信息泄露是当前大数据应用中的重大挑战。隐私计算就是为了解决这些问题应运而生。隐私计算,广义上是指面向隐私保护的计算系统与技术,涵盖数据的生产、存储、计算、应用等信息流程全过程。隐私计算经过近几十年的发展,目前在产业互联网、人工智能、金融科技、医药保护共享数据等方面发挥重要的作用。目前在对数据隐私的保护方面,隐私计算技术的应用主要可以分为可信硬件、多方安全计算、联邦学习三个主要流派。

以联邦学习为例,联邦学习是一个机器学习框架,该框架针对不同企业、机构或用户之间,在保证数据安全性、私密性、合法性的前提下,打破数据孤岛的局面,实现双方数据的共享,如用企业之间用于人工智能(AI,Artificial Intelligence)的训练和学习,以达到优化共享双方的AI模型,提高AI预测准确率等效果。联邦学习涉及的业务计算类型包括但不限于同态加密、密态计算、RSA交集、秘钥交换、其他业务计算等等。因此在联邦学习中存在大量的复杂计算,非常耗费计算力,而且存在大批数据量,高并发的可能,这是一个很大的计算挑战。

本申请实施例的多核计算芯片100能够应用于联邦学习场景中,一方面通过本申请实施例的多核计算芯片100中的多个计算引擎1进行大量复杂的并行计算,能够大大提高整个系统的计算效率,让联邦学习应用更容易落地实现;另一方面,可以在芯片开机或计算引擎1空闲时或其他设定时间对计算引擎1进行测试,以便于预先获知芯片中计算引擎的状态:是正常还是异常,根据芯片中计算引擎的状态确定芯片是否可以继续有效利用以尽可能最大化利用芯片节省维修成本;再一方面,预先获知芯片中计算引擎的状态,上级系统在分配任务的时候可以根据芯片中计算引擎的状态合理分配芯片能够处理的并行任务数量,使分配的并行任务数量不超过正常计算引擎的数量,从而能够继续合理利用有异常计算引擎的多核计算芯片。

本申请实施例的多核计算芯片包括多个用于并行计算的计算引擎,还包括:存储部件,用于存储测试向量和所述测试向量对应的预期结果;控制与测试部件,用于控制所述计算引擎根据所述存储部件中存储的测试向量对自身进行测试得到所述计算引擎的所述测试向量对应的测试结果,结合所述存储部件中存储的所述测试向量对应的预期结果,确定所述多个计算引擎中是否存在异常计算引擎。由于存储测试向量和所述测试向量对应的预期结果的存储部件和控制所述计算引擎对自身进行测试的控制与测试部件和计算引擎集成在一起,属于芯片不可分割的部件,通过这种方式,能够对多核计算芯片中的多个计算引擎进行定时或实时检测。

结合参见图2,在一实施例中,所述存储部件2包括:测试向量存储部件21和预期结果存储部件22。测试向量存储部件21用于存储测试向量;预期结果存储部件22用于存储所述测试向量对应的预期结果。

进一步,在控制指令下,所述测试向量存储部件21将所述测试向量发送至所述计算引擎1,所述计算引擎1根据接收到的所述测试向量对自身进行测试得到所述测试向量对应的测试结果。

所述计算引擎1可以将所述测试向量对应的测试结果发给控制与测试部件3,控制与测试部件3可以从预期结果存储部件22获取测试向量对应的预期结果,根据测试向量对应的测试结果和测试向量对应的预期结果,即可确定所述多个计算引擎1中是否存在异常计算引擎。需要说明的是,根据测试向量对应的测试结果和测试向量对应的预期结果如何确定所述多个计算引擎1中是否存在异常计算引擎,需要根据具体的测试向量、具体的实际应用等来确定。

例如,比较测试向量对应的测试结果和测试向量对应的预期结果,如果测试向量对应的测试结果与测试向量对应的预期结果之间的差值的绝对值超出预定范围,可以认为存在异常计算引擎,该测试结果对应的计算引擎即为异常计算引擎。

又如,比较测试向量对应的测试结果和测试向量对应的预期结果,如果测试向量对应的测试结果不在测试向量对应的预期结果的范围内,可以认为存在异常计算引擎,该测试结果对应的计算引擎即为异常计算引擎。

结合参见图3,在一实施例中,所述测试向量存储部件21还用于接收上层系统200发送的测试向量,并存储所述测试向量;所述预期结果存储部件22还用于接收上层系统200发送的所述测试向量对应的预期结果,并存储所述测试向量对应的预期结果。上层系统200可以是测试机台或电脑主控系统等等。通过这种方式,能够根据实际情况对多核计算芯片进行灵活测试。

结合参见图4,在一实施例中,为了使多核计算芯片的部件的功能分工明确,所述控制与测试部件3包括:测试结果比对部件31和控制部件32。

测试结果比对部件31用于在控制指令下根据所述计算引擎1的所述测试向量对应的测试结果和所述存储部件2中存储的所述测试向量对应的预期结果,确定检测结果,所述检测结果包括所述多个计算引擎中是否存在异常计算引擎,在存在所述异常计算引擎时所述异常计算引擎的编号和所述异常计算引擎的数量。控制部件32用于分别向所述存储部件2、所述计算引擎1以及所述测试结果比对部件31发送控制指令,以控制所述计算引擎1根据所述存储部件2中存储的测试向量对自身进行测试得到所述计算引擎1的所述测试向量对应的测试结果,控制所述测试结果比对部件31确定所述检测结果。

在实际应用中,测试结果比对部件31中可以设置一个计数部件,如果确定计算引擎的测试结果异常则该计数部件的计数加1,并记录异常计算引擎的编号,测试完成后这个计数部件的计数值即是异常计算引擎的数量。

由于一个芯片中包括多个计算引擎,随着工艺节点的降低,芯片面积的增大,单芯片内部发生制造缺陷的概率也随之增加;芯片中计算引擎之间的计算是相互独立的,其中一个计算引擎异常不影响其它正常计算引擎的计算;如果检测出只有个别计算引擎有制造缺陷而丢弃掉该芯片,会大幅降低芯片良率并大幅增加芯片成本。另外,即使机台测试没有检测到异常计算引擎,如果芯片在使用过程中出现功能性错误,修复时直接更换芯片,这也会增加维修成本。

为了避免丢弃掉所有的检测出异常计算引擎的芯片而造成芯片良率大幅降低、芯片成本大幅增加,为了避免芯片在使用过程中出现功能性错误时直接更换芯片而造成维修成本增加,在一实施例中,所述多核计算芯片100还包括:异常核心处理部件4;异常核心处理部件4用于在所述多个计算引擎1中存在异常计算引擎时,在控制指令下对所述异常计算引擎进行处理,如图5所示。

具体地,异常核心处理部件4对所述异常计算引擎进行处理可以有如下几种处理情况:

结合参见图6,在一实施例中,可以对异常计算引擎进行标记,即所述异常核心处理部件4包括:异常核心标记部件41;异常核心标记部件41用于在所述多个计算引擎1中存在异常计算引擎时在控制指令下对所述异常计算引擎进行标记处理。

本实施例中,对异常计算引擎进行标记,能够知道哪些计算引擎是异常的,随时可以获知异常计算引擎的数量,可以当异常计算引擎的数量超过一定数量时,才将多核计算芯片丢弃掉,在异常计算引擎的数量没有超过一定数量时,仍然保留该多核计算芯片;使用该多核计算芯片时,也可以根据标记获知哪些计算引擎是异常的,后续可以尽量避免不再使用异常计算引擎。

结合参见图7,在另一实施例中,可以对异常计算引擎进行屏蔽处理,特别是多核计算芯片100在工作模式时。即所述异常核心处理部件4包括:异常核心屏蔽部件42;异常核心屏蔽部件42用于在所述多个计算引擎1中存在异常计算引擎时在控制指令下对所述异常计算引擎进行屏蔽处理。其中,所述异常核心屏蔽部件42还用于,在处于工作模式时若所述多个计算引擎1中存在异常计算引擎,则在控制指令下对所述异常计算引擎进行屏蔽处理。

对于多核芯片,其多核用于并行计算,核心之间的计算是相互独立的,其中一个核心异常不影响其它核心的计算;但是最后阶段所有核心计算后的数据会汇集到一起,如果不能及时排除和屏蔽有异常的核心(即异常计算引擎),可能会导致汇集后的数据错误或整体数据被污染。因此,本实施例中,对异常计算引擎进行屏蔽处理,一方面能够避免异常计算引擎参与计算,另一方面即使异常计算引擎参与计算,其计算后的数据也会被屏蔽和排除掉。

在又一实施例中,所述异常核心处理部件4还用于,若所述异常计算引擎的数量大于或等于数量阈值,则在控制指令下向上级系统汇报使所述上级系统对所述多核计算芯片进行处理。

本实施例中,数量阈值可以根据实际情况确定;例如数量阈值可以是多核计算芯片不合格或者不满足质量要求的异常计算引擎的数量;也可以是指能够影响整个多核计算芯片性能或功能的异常计算引擎的数量;等等。当异常计算引擎的数量大于或等于数量阈值,异常核心处理部件4在控制指令下向上级系统汇报使所述上级系统对所述多核计算芯片进行处理,能够为提前解决后续可能产生的问题提供技术支持。

如果多核计算芯片在质检阶段,即在处于测试模式时,所述异常核心处理部件向上级系统汇报,使上级系统将所述多核计算芯片作为废片处理;此时若所述异常计算引擎的数量大于或等于数量阈值,表明多核计算芯片不合格不达标,可以将所述多核计算芯片作为废片处理,丢弃掉。相比较于只要有一个异常计算引擎就将芯片作为废片丢弃掉,本实施例在异常计算引擎的数量大于或等于数量阈值时才将芯片作为废片丢弃掉,通过这种方式,能够大幅提高芯片良率并降低芯片成本,减少浪费。

如果多核计算芯片在使用阶段,即在处于工作模式时,当异常计算引擎的数量大于或等于数量阈值,所述异常核心处理部件除了向上级系统汇报外还启动报警系统,以提示所述上级系统需要更换所述多核计算芯片。相比较于芯片在使用过程中只要出现功能性错误,就采取更换芯片的方式修复而增加维修成本,本实施例在异常计算引擎的数量大于或等于数量阈值时,才提示所述上级系统需要更换所述多核计算芯片,通过这种方式,能够大幅降低维修成本。

在一实施例中,为了使上层系统及时了解多核计算芯片的状态,所述控制部件32还用于,将检测结果汇报给上层系统。

其中,多核计算芯片被集成到产品中后,还可以根据异常计算引擎的数量调整分配的并行任务数量。即所述控制部件32还用于,在产品模式下在开机后或者在所述多核计算芯片空闲时,控制所述计算引擎根据所述存储部件中存储的测试向量对自身进行测试得到所述计算引擎的所述测试向量对应的测试结果,控制所述测试结果比对部件确定所述检测结果,将所述检测结果汇报给上层系统,使上层系统根据所述异常计算引擎的数量,调整分配给所述多核计算芯片的并行任务数量,使分配的并行任务数量不超过正常计算引擎的数量。通过这种方式,能够继续合理利用有异常计算引擎的多核计算芯片。

此时,所述控制部件32还用于,接收上层系统分配的并行任务,并将所述并行任务分配给正常计算引擎。通过这种方式,能够避开在异常核心标记部件中被标记为异常的核心。

上述对所述异常计算引擎进行处理的几种情况可以根据具有应用以及实际情况结合起来实施。例如,当多核计算芯片被植入产品后,可以采取开机或者在所述多核计算芯片空闲时或定时进行自动测试方式,能够实时监控多核计算芯片工作状态;并且当多核计算芯片某些核心出现问题时,可以采取直接上报系统、屏蔽异常核心的方式,而无需停机更换多核计算芯片,从而可以达到实时保证系统稳定性和降低产品维修成本的目的。

参见图8,本申请还提供另一种多核计算芯片,所述多核计算芯片100包括多个用于并行计算的计算引擎1,本实施例的多核计算芯片与上述的多核计算芯片有相同的技术内容,相同的技术内容的详细说明请参见上述的多核计算芯片部分,在此不再赘叙。本实施例的多核计算芯片与上述的多核计算芯片不相同的关键在于:本实施例中的多核计算芯片100重点是将计算引擎1和异常核心处理部件4集成在一起,主要用来对所述异常计算引擎进行处理,便于后续具体的标记、屏蔽等处理,为尽可能合理利用有异常计算引擎的多核计算芯片提供技术支持。本实施例中,如何确定多个计算引擎中是否存在异常计算引擎等技术问题,可以采用上述的多核计算芯片的技术手段实现,也可以采用外部的测试手段对多核计算芯片进行测试来实现,在此不做限定。下面主要说明与上述多核计算芯片不相同的技术内容。

所述多核计算芯片100还包括:异常核心处理部件4。异常核心处理部件4用于在多个计算引擎中存在异常计算引擎时,在控制指令下对所述异常计算引擎进行处理;对所述异常计算引擎进行处理包括:对所述异常计算引擎进行标记处理和/或在处于工作模式时对所述异常计算引擎进行屏蔽处理。

本实施例中的多核计算芯片100是将计算引擎1和异常核心处理部件4集成在一起,主要是对所述异常计算引擎进行处理,便于后续具体的标记、屏蔽等处理,以为尽可能合理利用有异常计算引擎的多核计算芯片提供技术支持。

本实施例中,对于如何确定多个计算引擎中是否存在异常计算引擎等技术问题,可以采用上述的多核计算芯片的技术手段实现,即同时将存储部件2以及控制与测试部件3也集成在多核计算芯片100中;也可以采用外部的测试手段对多核计算芯片进行测试,将测试后确定的检测结果等信息发送给多核计算芯片100的异常核心处理部件4,通过异常核心处理部件4对异常计算引擎进行处理。

本申请实施例的多核计算芯片包括多个用于并行计算的计算引擎,还包括:异常核心处理部件,用于在多个计算引擎中存在异常计算引擎时,在控制指令下对所述异常计算引擎进行处理;对所述异常计算引擎进行处理包括:对所述异常计算引擎进行标记处理和/或在处于工作模式时对所述异常计算引擎进行屏蔽处理。由于在存在异常计算引擎时能够对异常核心进行处理,对异常计算引擎进行标记处理和/或在处于工作模式时对异常计算引擎进行屏蔽处理,这样当异常计算引擎数量不多时,可以保留该芯片,不用丢弃掉,能够提高芯片良率、降低芯片成本;对异常计算引擎进行屏蔽处理,其他正常计算引擎可以继续使用,不用更换芯片,从而能够降低维修成本,因此,对异常核心进行处理能够为降低芯片成本和降低维修成本提供技术支持。

其中,所述异常核心处理部件还用于,在处于测试模式时,若所述异常计算引擎的数量大于或等于数量阈值,则在控制指令下向上级系统汇报使所述上级系统将所述多核计算芯片作为废片处理;或者,所述异常核心处理部件还用于,在处于工作模式时,若所述异常计算引擎的数量大于或等于数量阈值,则在控制指令下向上级系统汇报,并启动报警系统,以提示所述上级系统需要更换所述多核计算芯片。

其中,所述多核计算芯片还包括:控制与测试结果部件,用于向所述异常核心处理部件发送控制指令,还用于将包括所述异常计算引擎的数量的检测结果汇报给上层系统。

其中,所述控制与测试结果部件还用于,在产品模式下在开机后或者在所述多核计算芯片空闲时,控制所述计算引擎根据存储部件中存储的测试向量对自身进行测试得到所述计算引擎的所述测试向量对应的测试结果,结合所述存储部件中存储的所述测试向量对应的预期结果,确定所述检测结果,将所述检测结果汇报给上层系统,使上层系统根据所述异常计算引擎的数量,调整分配给所述多核计算芯片的并行任务数量,使分配的并行任务数量不超过正常计算引擎的数量。

其中,所述控制与测试结果部件还用于,接收上层系统分配的并行任务,并将所述并行任务分配给正常计算引擎。

应当理解,在本申请说明书中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本申请。

还应当理解,在本申请说明书和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

应当理解,在本申请说明书中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本申请。

还应当理解,在本申请说明书和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

以上所述,仅为本申请的具体实施例,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以权利要求的保护范围为准。

- 多核SoC芯片的开发架构及多核SoC芯片的开发方法

- 多核SoC芯片的开发架构及多核SoC芯片的开发方法