存储器元件

文献发布时间:2023-06-19 10:29:05

技术领域

本公开属于半导体技术领域,有关于一种半导体结构,特别是有关于一种存储器元件。

背景技术

近来,由于对于更优异的存储器元件的需求已逐渐增加,已提供各种三维(3D)存储器元件,例如是立体与非门(3D NAND)存储器元件或立体只读存储器(3D ROM)。此类三维存储器元件可达到更高的储存容量,具有更优异的电子特性,例如是具有良好的数据保存可靠性和操作速度。

在三维存储器元件的制作过程中,需要形成电性连接于基板的多个共同源极线以将三维存储器元件区分为多个区块及次区块。然而,共同源极线的数量过多可能导致三维存储器元件的尺寸变大。

因此,有需要提出一种先进的存储器元件及其制作方法以解决现有技术所面临的问题。

发明内容

在本公开中,提供一种存储器元件及其制作方法,以解决至少一部分上述问题。

根据本发明的一实施例,存储器元件包括一基板、一叠层结构、多个通道结构、多个存储层以及多个浅隔离结构。基板具有一上表面。叠层结构位于基板的上表面上,其中叠层结构包括交替堆叠于上表面上的多个绝缘层及多个导电层。通道结构穿过部分叠层结构并电性连接于基板。各个存储层环绕所对应的各个通道结构。浅隔离结构由叠层结构的一顶面朝向基板的方向延伸,其中各个浅隔离结构包括一物质,此物质的介电常数小于3.9。

根据本发明的一实施例,存储器元件的制作方法包括下列步骤。首先,提供一基板,基板具有一上表面。接着,在基板的上表面上形成一叠层结构,其中叠层结构包括依堆叠于该基板的该上表面上的多个绝缘层及多个导电层。形成穿过部分叠层结构的多个通道结构及多个存储层,通道结构电性连接于基板,各个存储层环绕所对应的各个通道结构。形成穿过叠层结构的一上部部分的多个上部开口。此后,在上部开口中形成多个浅隔离结构,浅隔离结构由叠层结构的一顶面朝向基板的方向延伸,其中各个浅隔离结构包括一物质,此物质的介电常数小于3.9。

根据本发明的一实施例,存储器元件的制作方法包括下列步骤。首先,提供一基板,基板具有一上表面。接着,在基板的上表面上形成一叠层本体,其中叠层本体包括交替堆叠于基板的上表面上的多个绝缘层及多个牺牲层。形成穿过叠层本体的多个通道结构及多个存储层,通道结构电性连接于基板,存储层环绕所对应的通道结构。形成穿过叠层本体的多个垂直开口。经由垂直开口移除牺牲层。在牺牲层被移除的位置形成多个导电层,使得交替堆叠在上表面上的绝缘层及导电层形成一叠层结构。此后,形成穿过叠层结构的一上部部分的多个上部开口。在上部开口中形成多个浅隔离结构,浅隔离结构由叠层结构的一顶面朝向基板的方向延伸,其中各个浅隔离结构包括一物质,此物质的介电常数小于3.9。

为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附附图,作详细说明如下。然而,本发明的保护范围当以权利要求所界定的范围为准。

附图说明

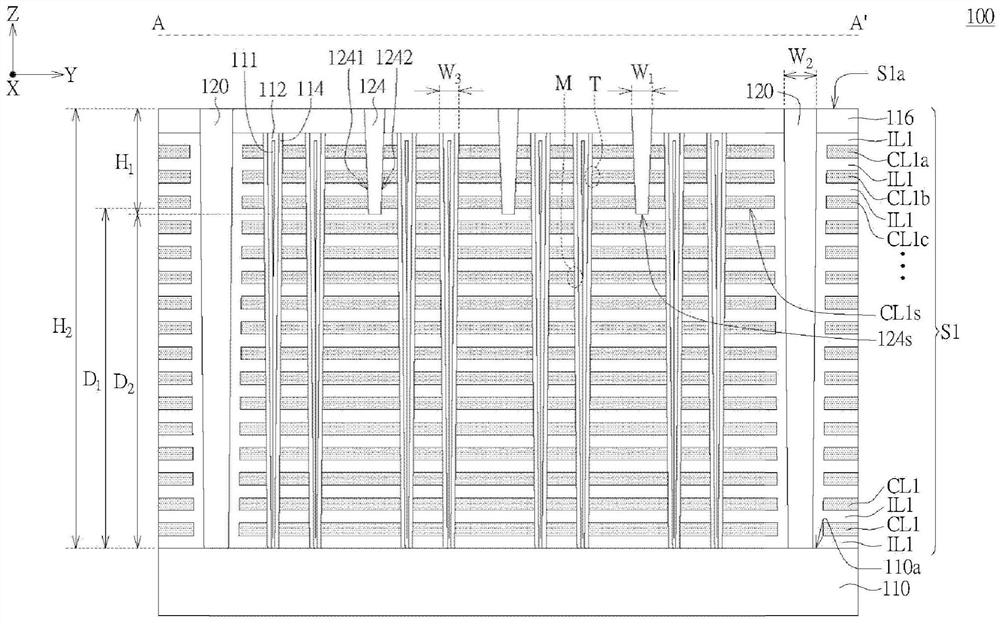

图1A绘示根据本公开的一实施例的存储器元件的上视图。

图1B绘示沿图1A的A-A’连线的根据本公开的一实施例的存储器元件的剖面图。

图2A至图2F绘示根据本公开的一实施例的存储器元件的形成方法的剖面图。

图3绘示根据本公开的另一实施例的存储器元件的剖面图。

图4A至图4F绘示根据本公开的又一实施例的存储器元件的形成方法的剖面图。

图5绘示根据本公开的又一实施例的存储器元件的剖面图。

【符号说明】

100、200、300、400、500:存储器元件

110、210、410:基板

110a、210a、410a:上表面

111、211、411:绝缘柱

112、212、412:通道结构

114、214、414:存储层

116、216、416:盖层

120、220、420:导电连接结构

124、224、324、424、524:浅隔离结构

124s、CL1s:底面

218、418:垂直开口

222、422:上部开口

224t、324t、424t、524t、S1a、S2a、S4a:顶面

324a、524a:空气间隙

324b、524b:氧化物内衬

1241:第一侧

1242:第二侧

B1、B2:区块

B1a、B1b、B1c、B1d、B2a、B2b、B2c、B2d:次区块

CL1、CL1a、CL1b、CL1c、CL2、CL2a、CL2b、CL2c:导电层

D1、D2:距离

H1、H2:深度

IL1、IL2、IL4:绝缘层

M:存储单元

Q2、Q4:内部开口

P2、P4:通道开口

S1、S2、S4:叠层结构

S2’、S4’:叠层本体

T:晶体管

V2、V4:通孔

W

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

在下文的详细描述中,为了便于解释,提供各种的特定细节以整体理解本公开的实施例。然而,应理解的是,一个或多个实施例能够在不采用这些特定细节的情况下实现。在其他情况下,为了简化附图,已知的结构及元件以示意图表示。

图1A绘示根据本公开的一实施例的存储器元件100的上视图;图1B绘示沿图1A的A-A’连线的根据本公开的一实施例的存储器元件100的剖面图。

请参照图1A,多个导电连接结构120沿着平行于基板110的上表面110a(绘示于图1B)的第一方向(例如是X轴方向)延伸,将存储器元件100分为多个区块B1、B2…。每个区块B1、B2…包括多个浅隔离结构124。浅隔离结构124将区块B1分为多个子区块B1a、B1b、B1c、B1d,将区块B2分为多个子区块B2a、B2b、B2c、B1d。在本实施例中,每个区块中具有3个浅隔离结构124,然而本发明并不以此为限。在其他实施例中,每个区块中可具有2个或大于3个浅隔离结构。在一些实施例中,导电连接结构120为共同源极线。

请同时参照图1A及图1B,存储器元件100包括一基板110、一叠层结构S1、多个绝缘柱111、多个通道结构112、多个存储层114、多个浅隔离结构124以及多个导电连接结构120。叠层结构S1形成于基板110的上表面110a上。叠层结构S1包括交替堆叠(例如是沿着Z轴)于基板110的上表面110a上的多个绝缘层IL1及多个导电层CL1,以及位于叠层结构S1的顶部部分的盖层116。

在一些实施例中,基板110可为硅基板或其他合适的基板。绝缘层IL1及盖层116可由氧化物所形成,例如是二氧化硅(SiO

在本发明的实施例中仅示例性绘示绝缘层及导电层的数量,然而本发明并不限于此,在一些实施例中绝缘层及导电层的数量可为任何合适的数量。

导电连接结构120穿过(例如是沿着Z轴)叠层结构S1并电性连接于基板110。导电连接结构120将存储器元件100分为多个区块B1、B2…。不同区块B1、B2…之间的导电层CL1是通过导电连接结构120完全分开。

通道结构112穿过(例如是沿着Z轴)部分的叠层结构S1并电性连接于基板110。通道结构112的顶部可电性连接于位线(未绘示)。在一些实施例中,通道结构112可由半导体材质所形成,例如是掺杂或未掺杂的多晶硅。在一些实施例中,绝缘柱111穿过(例如是沿着Z轴)部分的叠层结构S1,被通道结构112所环绕。

存储层114环绕所对应的通道结构112。在一些实施例中,存储层114可以由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride)层和氧化硅层的复合层(即,ONO层)所构成。

在一些实施例中,导电连接结构120及浅隔离结构124分别沿着一第一方向(例如是X轴方向)延伸,且在基板110上沿着一第二方向(例如是Y轴方向)配置,第一方向及第二方向皆平行于基板110的上表面110a,且第一方向与第二方向交错(例如,第一方向与第二方向之间可具有一非平角)。

浅隔离结构124可由叠层结构S1的顶面S1a朝向基板110的方向(例如是Z轴方向)延伸,穿过叠层结构S1的上部部分,而将每个区块(例如是B1、B2)分隔为多个子区块(例如是B1a、B1b、B1c、B1d、B2a、B2b、B2c、B1d)。每个浅隔离结构124包括一物质,此物质的介电常数小于3.9。例如,浅隔离结构124可包括低介电常数材料(low k material)或者是空气间隙(air gap)。低介电常数材料可以是氟掺杂的二氧化硅(fluorine-doped silicondioxide)、碳掺杂的氧化物(carbon-doped oxide)、多孔二氧化硅(porous silicondioxide)、旋涂式有机聚合物介电材料(spin-on organic polymeric dielectric)、旋涂式硅基聚合物介电材料(spin-on silicon based polymeric dielectric)、或其他合适的材料。在本实施例中,浅隔离结构124穿过依序设置于顶面S1a之下的第一顶导电层CL1a、第二顶导电层CL1b及第三顶导电层CL1c(亦即是3个导电层)。然而,本发明并不以此为限,浅隔离结构124可穿过大于3个的导电层。浅隔离结构124具有一底面124s,底面124s面对基板110的上表面110a。在基板110的上表面110a的法线方向(例如是第三方向或Z轴方向)上,浅隔离结构124的深度H1是小于导电连接结构120的深度H2。深度H1相当于叠层结构S1的顶面S1a与浅隔离结构124的底面124s之间的距离,深度H2相当于叠层结构S1的顶面S1a与基板110的上表面110a之间的距离。

在一些实施例中,浅隔离结构124的宽度W1可介于约40纳米(nm)~约145纳米(nm)。浅隔离结构124的深度H1大于130纳米(nm)。

在一些实施例中,浅隔离结构124所穿过的导电层CL1当中最邻近于底面124s的一导电层CL1具有一底面CL1s,此导电层CL1的底面CL1s与基板110的上表面110a之间的距离可等于或大于浅隔离结构124的底面124s与基板110的上表面110a之间的距离。在本实施例中,第三顶导电层CL1c是在浅隔离结构124所穿过的导电层(亦即是第一顶导电层CL1a、第二顶导电层CL1b及第三顶导电层CL1c)当中最邻近于底面124s的一导电层,第三顶导电层CL1c的底面CL1s与基板110的上表面110a之间的距离D1大于浅隔离结构124的底面124s与基板110的上表面110a之间的距离D2。

在一些实施例中,浅隔离结构124直接接触所对应的多个导电层CL1。在本实施例中,浅隔离结构124直接接触所对应的第一顶导电层CL1a、第二顶导电层CL1b及第三顶导电层CL1c,然而本发明并不以此为限。

在一些实施例中,浅隔离结构124所穿过的导电层可作为串行选择线。在本实施例中,第一顶导电层CL1a、第二顶导电层CL1b及第三顶导电层CL1c可作为串行选择线。换言之,浅隔离结构124可穿过位于叠层结构S1的上部的3个或大于3个的导电层,且每个浅隔离结构124将叠层结构S1的上部的3个或大于3个的导电层分隔成两个电性独立的串行选择线。

在本实施例中,由于不同的子区块B1a、B1b、B1c、B1d中的串行选择线(例如是第一顶导电层CL1a、第二顶导电层CL1b及第三顶导电层CL1c)受到包括介电常数小于3.9的物质的浅隔离结构124所分开,在对子区块B1a、B1b、B1c、B1d的串行选择线进行电压操作时,不同子区块B1a、B1b、B1c、B1d中的串行选择线之间的电容可降低,如此可避免不同子区块之间的串行选择线的电压互相干扰。例如,可降低位于浅隔离结构124的第一侧1241的第三顶导电层CL1c的电压与位于浅隔离结构124的第二侧1242的第三顶导电层CL1c的电压互相干扰的情形。第一侧1241位于第二侧1242的相反侧,例如参照图1B中沿着第二方向(y方向),第一侧1241与第二侧1242相对设置。因此,相较于不具有低介电常数的浅隔离结构的比较例而言,本公开通过浅隔离结构124的设置,不同子区块的串行选择线之间的电容值可减少,可降低不同子区块的串行选择线的充电延迟时间,使得串行选择线的电压更为稳定,故串行选择线可具有较优异的电特性,让存储器元件可具有较佳的性能。

再者,由于本公开的浅隔离结构124对应于多层的导电层(例如是3层或大于3层的导电层),相较于浅隔离结构仅对应于1层导电层的比较例而言,在升压期间可更有效防止漏电流的产生。

在一些实施例中,作为串行选择线的顶导电层(例如顶导电层CL1a、CL1b及CL1c)与存储层114之间的每个重叠位置(intersection)可形成一晶体管T,作为字线的其他导电层CL与存储层114之间的每个重叠位置可形成一存储单元M。晶体管T与存储单元M通过通道结构120互相串连,并可共同形成一存储单元串行。

在平行于基板110的上表面110a的一第二方向(例如是Y轴方向)上,浅隔离结构124垂直投影于基板110上的宽度W

在本实施例中,3个浅隔离结构124是介于相邻的2个导电连接结构120之间,将一个区块(例如是B1)分为4个次区块(例如是B1a、B1b、B1c、B1d)。然而本发明并不限于此,在其他实施例中,相邻的2个导电连接结构120之间可具有2个或大于3个的浅隔离结构124。相较于使用多个导电连接结构120将存储器元件的一个区块分为多个次区块的比较例而言,由于本公开使用浅隔离结构124将一个区块分为多个次区块,浅隔离结构124沿着第二方向上的宽度(例如是Y轴)小于导电连接结构120沿着第二方向上的宽度(例如是Y轴),故浅隔离结构124在存储器元件100中所占有的空间较小,可降低存储器元件100的尺寸。

在一些实施例中,存储器元件100可为通过下列图2A~图2F、图3、图4A~图4F及图5的工艺方法所形成的存储器元件200、300、400或500,然而本发明并不以此于限,本公开的存储器元件的形成方法亦包括其他合适的工艺方法。此外,图2A~图2F、图3、图4A~图4F及图5所绘示的存储器元件的剖面图是对应于图1B的存储器元件100的剖面图。

图2A至图2F绘示根据本公开的一实施例的存储器元件200的形成方法的剖面图。

请参照图2A,提供一基板210,并在基板210的上表面210a上形成一叠层本体S2’。叠层本体S2’包括依序(例如是通过沉积工艺)交替堆叠于基板210的上表面210a上的多个绝缘层IL2及多个导电层CL2。

在一些实施例中,基板210可为硅基板或其他合适的基板。绝缘层IL2可由氧化物所形成,例如是二氧化硅。导电层CL2可为掺杂或未掺杂的多晶硅(poly-silicon)或其他合适的材料,例如是n型掺杂的多晶硅层。

请参照图2B,通过刻蚀法(例如是干法刻蚀)形成多个穿过(例如是沿着Z方向)叠层本体S2’且暴露基板210的上表面210a的多个通道开口P2。接着,通过一沉积工艺形成一存储材料于叠层本体S2’上以及这些通道开口P2之中。再来,通过一刻蚀工艺移除部分位于通道开口P2中的存储材料以形成暴露基板210的上表面210a的多个通孔V2。之后,填充一导电材料及一绝缘材料于通孔V2中,以形成多个通道结构212、多个绝缘柱211及存储层214。通道结构212可由掺杂或未掺杂的多晶硅材料所形成。存储层214可以由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride)层和氧化硅层的复合层(即,ONO层)所构成。此后,通过一沉积工艺形成覆盖叠层本体S2’的盖层216,并形成包括叠层本体S2’及盖层216的叠层结构S2。叠层结构S2具有一顶面S2a。通道结构212穿过部分的叠层结构S2并电性连接于基板110。各个存储层214环绕所对应的通道结构212。

请参照图2C,通过一刻蚀工艺(例如是一干法刻蚀工艺)形成穿过叠层结构S2的多个垂直开口218。在本实施例中,垂直开口218穿过盖层216及叠层结构S2并暴露出基板210的上表面210a。接着,由垂直开口218移除部分的导电层CL2。

请参照图2D,填充一绝缘材料于垂直开口218中。之后,移除部分的绝缘材料以形成内部开口Q2。内部开口Q2穿过叠层结构S2并暴露基板210的上表面210a。此后,通过一沉积工艺将导电材料填充于内部开口Q2中,以形成导电连接结构220。导电连接结构220可包括钨(W)、铝(Al)、氮化钛(TiN)、氮化钽(TaN)或其他合适的材料。

请参照图2E,通过一刻蚀工艺(例如是干法刻蚀工艺)形成多个上部开口222。上部开口222穿过叠层结构S2上部部分。上部开口222例如是穿过3个导电层(亦即是第一顶导电层CL2a、第二顶导电层CL2b及第三顶导电层CL2c),然而本发明并不以此为限,在一些实施例中,上部开口222可穿过大于3个的导电层。

请参照图2F,通过一沉积工艺将低介电常数材料填充至上部开口222中,以在上部开口222中形成浅隔离结构224。如此一来便形成存储器元件200。在本实施例中,浅隔离结构224穿过3个导电层(亦即是第一顶导电层CL2a、第二顶导电层CL2b及第三顶导电层CL2c),然而本发明并不以此为限。在一些实施例中,浅隔离结构224可穿过大于3个的导电层。浅隔离结构224包括介电常数小于3.9的物质。在一些实施例中,浅隔离结构224的顶面224t可与叠层结构S2的顶面S2a共平面。

图3绘示根据本公开的一实施例的存储器元件300的剖面图。存储器元件300的形成方法是类似于存储器元件200,其不同之处在于浅隔离结构324的材料。

请参照图3,在经过如图2A~图2E所示的形成步骤之后,通过一沉积工艺将绝缘材料填充于上部开口222之中,以在上部开口222中形成氧化物内衬324b以及受到氧化物内衬324b所包覆的空气间隙324a。在本实施例中,浅隔离结构324穿过3个导电层(亦即是第一顶导电层CL2a、第二顶导电层CL2b及第三顶导电层CL2c),然而本发明并不以此为限,在一些实施例中,浅隔离结构324可穿过大于3个的导电层。在一些实施例中,浅隔离结构324的顶面324t可与叠层结构S2的顶面S2a共平面。

图4A至图4F绘示根据本公开的一实施例的存储器元件400的形成方法的剖面图。

请参照图4A,提供一基板410,并在基板410的上表面410a上形成一叠层本体S4’。叠层本体S4’包括依序(例如是通过沉积工艺)交替堆叠于基板410的上表面410a上的多个绝缘层IL4及多个牺牲层SL4。

在一些实施例中,基板410可为硅基板或其他合适的基板。绝缘层IL4可由氧化物所形成,例如是二氧化硅。牺牲层SL4可由氮化硅(SiN)所形成。

请参照图4B,通过刻蚀法(例如是干法刻蚀)形成多个穿过(例如是沿着Z方向)叠层本体S4’且暴露基板410的上表面410a的多个通道开口P4。接着,通过一沉积工艺形成一存储材料于叠层本体S4’上以及这些通道开口P4之中。再来,通过一刻蚀工艺移除部分位于通道开口P4中的存储材料以形成暴露基板410的上表面410a的多个通孔V4。之后,填充一导电材料及一绝缘材料于通孔V4中,以形成多个通道结构412、多个绝缘柱411及存储层414。通道结构412可由掺杂或未掺杂的多晶硅材料所形成。存储层414可以由包含氧化硅(silicon oxide)层、氮化硅(silicon nitride)层和氧化硅层的复合层(即,ONO层)所构成。通道结构412穿过叠层本体S4’并电性连接于基板410。各个存储层414环绕所对应的各个通道结构412。此后,通过一沉积工艺形成覆盖叠层本体S4’的盖层416。盖层416可由氧化物所形成,例如是二氧化硅。

请参照图4C,通过一刻蚀工艺(例如是一干法刻蚀工艺)形成穿过叠层本体S4’及盖层416的多个垂直开口418。在本实施例中,垂直开口418暴露出基板410的上表面410a。

请参照图4D,进行一回蚀(pull back)工艺,以经由垂直开口418移除牺牲层SL4。回蚀工艺可以是一各向同性刻蚀(isotropic etching)(例如是湿法刻蚀),且可以是一高选择性刻蚀,例如是选择性刻蚀氮化硅而不刻蚀二氧化硅及多晶硅。

此后,在牺牲层SL4所被移除的位置填充导电材料,借以在绝缘层IL4之间形成导电层CL4。如此一来,交替堆叠于上表面410a上的多个绝缘层IL4及多个导电层CL4以及盖层416形成叠层结构S4。导电层CL4可包括是钨(W)、铝(A1)、氮化钛(TiN)、氮化钽(TaN)或其他合适的材料。

请参照图4E,填充一绝缘材料于垂直开口418中。之后,移除部分的绝缘材料以形成内部开口Q4。内部开口Q4穿过叠层结构S4并暴露基板410的上表面410a。此后,通过一沉积工艺将导电材料填充于内部开口Q4中,以形成导电连接结构420。导电连接结构420可包括是钨(W)、铝(Al)、氮化钛(TiN)、氮化钽(TaN)或其他合适的材料。

此后,通过一刻蚀工艺(例如是干法刻蚀工艺)形成多个上部开口422。上部开口422穿过叠层结构S4上部部分。上部开口422例如是穿过3个导电层(亦即是第一顶导电层CL4a、第二顶导电层CL4b及第三顶导电层CL4c),然而本发明并不以此为限,在一些实施例中,上部开口422可穿过大于3个的导电层。

请参照图4F,通过一沉积工艺将低介电常数材料填充至上部开口422中,以在上部开口422中形成浅隔离结构424。如此一来便形成存储器元件400。在本实施例中,浅隔离结构424穿过3个导电层(亦即是第一顶导电层CL4a、第二顶导电层CL4b及第三顶导电层CL4c),然而本发明并不以此为限,在一些实施例中,浅隔离结构424可穿过大于3个的导电层。浅隔离结构424包括介电常数小于3.9的物质。在一些实施例中,浅隔离结构424的顶面424t可与叠层结构S4的顶面S4a共平面。

图5绘示根据本公开的一实施例的存储器元件500的剖面图。存储器元件500的形成方法是类似于存储器元件400,其不同之处在于浅隔离结构524的材料。

请参照图5,在经过如图4A~图4E所示的形成步骤之后,通过一沉积工艺将绝缘材料填充于上部开口422之中,以在上部开口422中形成氧化物内衬524b以及受到氧化物内衬524b所包覆的空气间隙524a。在本实施例中,浅隔离结构524穿过3个导电层(亦即是第一顶导电层CL5a、第二顶导电层CL5b及第三顶导电层CL5c),然而本发明并不以此为限,在一些实施例中,浅隔离结构524可穿过大于3个的导电层。在一些实施例中,浅隔离结构524的顶面524t可与叠层结构S4的顶面S4a共平面。

本公开提供一种存储器元件及其制作方法。本公开的存储器元件可应用于三维与非门存储器元件或三维只读存储器。

根据本公开的一实施例,存储器元件包括一基板、一叠层结构、多个通道结构、多个存储层以及多个浅隔离结构。基板具有一上表面。叠层结构位于基板的上表面上,其中叠层结构包括交替堆叠于上表面上的多个绝缘层及多个导电层。通道结构穿过部分的叠层结构并电性连接于基板。各个存储层环绕所对应的通道结构。浅隔离结构由叠层结构的一顶面朝向基板的方向延伸,其中浅隔离结构包括一物质,此物质的介电常数小于3.9。

相较于不具有低介电常数的物质的浅隔离结构的比较例而言,由于本公开的存储器元件包括浅隔离结构,且浅隔离结构包括介电常数小于3.9的物质,位于浅隔离结构的不同侧(不同子区块)的顶导电层(串行选择线)之间的电容值可减少,可降低不同子区块的顶导电层(串行选择线)的充电延迟时间,使得顶导电层(串行选择线)的电压更为稳定,故顶导电层(串行选择线)可具有较优异的电特性,让存储器元件可具有较佳的效能。

综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中具有公知常识的技术人员,在不脱离本发明的精神和范围内,当可作各种的改动与润饰。因此,本发明的保护范围当以权利要求所界定的范围为准。

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 存储器元件的制造方法、存储器元件与相变化存储器元件

- 随机存取存储器、存储器元件以及存储器元件的操作方法