接垫结构

文献发布时间:2023-06-19 10:29:05

技术领域

本发明是有关于一种接垫结构,且特别是有关于一种具有导电层的接垫结构。

背景技术

已知CUP(Circuit Under Pad)结构的工艺中,打线过程中工具施加在CUP结构的力量及电路测试过程中工具施加在CUP结构的力量容易导致CUP结构的二导电层之间的介电层发生裂痕或同一导电层的金属间介电层发生裂痕。因此,如何提出一种新的CUP结构以改善前述问题是本技术领域工作人员努力的方向之一。

发明内容

本发明是有关于一种接垫结构,可以改善前述已知问题。

本发明一实施例提出一种接垫结构。接垫结构包括多层导电层、一接垫层、一保护层及一介电层。导电层为一电路的一部分。保护层包覆接垫层并具有一开口,以露出部分接垫层。介电层形成于导电层与接垫层之间且完全隔开在开口的区域内的导电层与接垫层。导电层包括多个有效区块,这些有效区块的一第一区块的一区块面积与这些有效区块的一总区块面积的一比例介于40%~50%之间。第一区块具有至少一镂空部,镂空部具有一镂空面积,镂空面积与区块面积的比值介于0.1~0.5之间。

本发明另一实施例提出一种接垫结构。接垫结构包括多层导电层、一接垫层、一保护层及一介电层。导电层为一电路的一部分。保护层包覆接垫层并具有一开口,以露出部分接垫层。介电层形成于导电层与接垫层之间且隔开在开口的区域内的导电层与接垫层。导电层包括一第一区块及一第二区块,第一区块及第二区块分别具有一第一宽度及一第二宽度,第一区块与第二区块之间具有一第一间隔,第一宽度、第二宽度及第一间隔是沿相同方向的尺寸,第一宽度及第二宽度皆大于一门限宽度,而第一间隔大于一门限间隔。

附图说明

为了对本发明的上述及其他方面有更好的了解,下文特举实施例,并配合所附附图详细说明如下:

图1A绘示本发明一实施例的接垫结构的示意图。

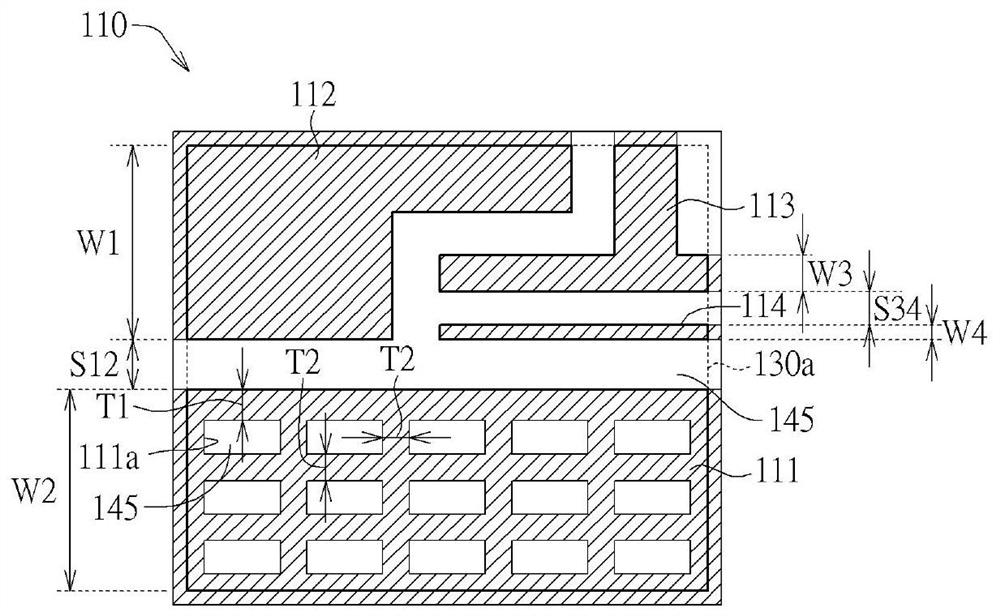

图1B绘示图1A的接垫结构的导电层的俯视图。

图2A~图2H绘示其它实施例的镂空部的示意图。

图3A~图3B绘示其它实施例的导电层的示意图。

图4A~图4B绘示图1B的接垫结构的导电层的设计过程图。

【符号说明】

10:衬底

100:接垫结构

110:导电层

111:第一区块

111a:镂空部

112:第二区块

113:第三区块

114:第四区块

114':区块

120:接垫层

130:保护层

130a:开口

140:介电层

145:介电材料

A1:总区块面积

A2:镂空总面积

A3:区块面积

S12:第一间隔

S34:第二间隔

T1、T2:最小间距

W1:第一宽度

W2:第二宽度

W3:第三宽度

W4:第四宽度

W4':宽度

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

请参照图1A及图1B,图1A绘示本发明一实施例的接垫结构100的示意图,而图1B绘示图1A的接垫结构100的导电层110的俯视图。

如图1A所示,接垫结构100可以形成于一衬底10上,衬底10例如是电路板(circuitboard)或晶圆(wafer)。在一实施例中,至少一接垫结构100与衬底10例如是一芯片的至少一部分,其中芯片例如是中央处理器(central processing unit,CPU)。

如图1A所示,接垫结构100包括多层导电层110、接垫层120、保护层130及多层介电层140。保护层130包覆接垫层120并具有开口130a,以露出部分接垫层120,使焊线(未绘示)通过开口130a形成于接垫层120上。这些介电层1405的至少一者形成于这些导电层110之间,以隔开这些导电层110。这些介电层1405的一者形成于这些导电层110与衬底10之间,以隔开这些导电层110与衬底10。这些介电层1405的一者形成于导电层110与接垫层120之间,以隔开导电层110与接垫层120。

导电层110形成在衬底10上方且导电层110也包含介电材料145在其中。在本实施例中,接垫结构100例如是CUP结构,因此多层导电层110为至少一电路(circuit)的一部分。如图1A所示,在开口130a的区域内,这些导电层110通过介电层140彼此分隔,然在开口130a的俯视区域外,二导电层110可以通过贯穿介电层140的导电孔(conductive via)(未绘示)电性连接。相似地,在开口130a的区域内,接垫层120与导电层110通过介电层140彼此分隔,然在开口130a的俯视区域外,接垫层120与导电层110可以通过贯穿介电层140的导电孔(未绘示)电性连接。

如图1B所示,导电层110包括多个区块(如图1B的粗线区域),如第一区块111、第二区块112、第三区块113及第四区块114。第一区块111、第二区块112、第三区块113及第四区块114彼此分离,且各区块为连续延伸区块。第一区块111、第二区块112、第三区块113及第四区块114皆导电层110投影至开口130a(即图1B所示的虚框)的部分。此外,本发明实施例不限定区块的数量,其可以少于四个或多于四个。

如图1B所示,在这些区块中,区块面积大于一门限值的区块可以具有至少一镂空部111a。例如,第一区块111的区块面积大于门限值,因此第一区块111具有至少一镂空部111a。此处的区块面积指的图1B所示的俯视面积,即第一区块111的外边界(超出开口130a的部分由开口130a的边界定义)所围绕的面积。各镂空部111a内可以填满介电材料145。此介电材料145为金属间介电层(inter-metal dielectric,IMD)。此外,二区块之间也可以填满介电材料145。相较于不具有镂空部111a的区块,具有镂空部111a的第一区块111能提升导电层110的刚度(stiffness),避免打线过程的施力造成导电层110的变形,以及避免介电层140及介电材料145发生裂痕。

前述门限值可以是一面积与多个有效区块的总区块面积A1的一预设比例,此预设比例例如是介于40%~50%。进一步来说,在这些区块中,第一区块111的区块面积、第二区块112的区块面积及第三区块113的区块面积大于一有效区块面积,因此第一区块111、第二区块112及第三区块113定义为有效区块。「有效区块」指的是有资格纳入总区块面积A1的计算的区块。总区块面积A1为第一区块111的区块面积、第二区块112的区块面积及第三区块113的区块面积的总和。由于第四区块114的区块面积小于有效区块面积,因此不纳入总区块面积A1的计算。在一实施例中,有效区块面积例如是开口130a的封闭面积的10%。

区块面积介于总面积A1的40%~50%的有效区块才需形成镂空部111a。在本实施例中,这些有效区块中只有第一区块111的区块面积介于总面积A1的40%~50%,因此只需在第一区块111形成镂空部111a。在另一实施例中,门限值可以高于50%或低于40%。当门限值愈低,导电层110镂空的部分愈多,此会导致导电层110的阻值增加。当门限值愈高,导电层110镂空的部分减少,对于导电层110刚度的提升效果不显著。由于本发明实施例的门限值介于40%~50%之间,因此可以兼顾导电层110的优良导电性与刚度提升的双重效果。

第一区块111的所有镂空部111a的面积和为镂空总面积A2。在实施例中,第一区块111的镂空总面积A2与第一区块111的区块面积A3的比值(A2/A3)介于0.1~0.5之间。如此,导电层110具有足够刚度,可以避免打线工艺中的施力,以避免镂空部111a内的介电材料145发生裂痕。前述区块面积A3例如是第一区块111的外边界所围绕的面积。

如图1B所示,镂空部111a的形状例如是矩形,且镂空部111a与第一区块111的外边界最小间距T1例如是介于5微米~10微米之间。相邻二镂空部111a的最小间距T2例如是介于5微米~10微米之间。

如图1B所示,第一区块111及第二区块112分别具有第一宽度W1及第二宽度W2,第一区块111与第二区块112之间具有第一间隔S12,第一宽度W1、第二宽度W2及第一间隔S12是沿相同方向的尺寸。第一宽度W1及第二宽度W2皆大于一门限宽度,而第一间隔S12大于门限间隔。如此,导电层110可以提供足够刚度,可以避免打线工艺中的施力,避免介电材料145因导电层110形变而发生裂痕。在一实施例中,前述门限宽度例如是等于或大于10微米,而前述门限间隔例如是等于或大于2微米(最小2微米)。

此外,若宽度小于门限宽度的区块可以不考虑扩大二区块之间的间隔。例如,如图1B所示,第三区块113及第四区块114分别具有第三宽度W3及第四宽度W4,第三区块113及第四区块114之间具有第二间隔S34。第三宽度W3及第四宽度W4皆小于门限宽度,表示区块具有一定刚度(宽度愈大,区块面积愈大,区块刚度愈低),因此可以不考虑第二间隔S34,例如第二间隔S34可以小于门限间隔。

请参照图2A~图2H,其绘示其它实施例的镂空部111a的示意图。从这些附图可知,在同一个区块中,多个镂空部111a的一者的形状可以是多边形,如正方形、矩形、长条形、梯形等,然亦可以为圆形或椭圆形。此外,多个镂空部111a的任二者的形状可以相同或相异。多个镂空部111a可以彼此平行排列。镂空部111a相对于区块的侧边可以倾斜配置或平行配置。

请参照图3A~图3B,其绘示其它实施例的导电层110的示意图。从这些附图可知,区块114'的宽度W4'小于门限宽度,因此相邻二区块114'与第一区块111之间的间隔S14可以小于门限间隔。

虽然前述实施例是以其中一层导电层110为例说明,但是这并非用以限定本发明实施例。前述任一导电层110都可以具有前述结构,在此不再赘述。

请参照图4A~图4B,其绘示图1B的接垫结构100的导电层110的设计过程图。接垫结构100的各导电层110的设计过程同以下流程。

首先,如图4A所示,提供一初步设计的导电层110'的图案。导电层110'的图案可以依据接垫结构110及/或衬底10的电路功能而定,本发明实施例不加以限定。

然后,定义开口130a的区域。

然后,决定导电层110'的多个区块,各区块是连续延伸区块,且任二区块是彼此分离。依据此原则,在导电层110'中决定出第一区块111'、第二区块112、第三区块113及第四区块114。接着,计算各区块的区块面积。例如,计算而得到第一区块111'的区块面积、第二区块112的区块面积、第三区块113的区块面积及第四区块114的区块面积。然后,排除区块面积小于有效区块面积的区块。在本例子中,第四区块114的区块面积小于有效区块面积,因此后续设计过程不考虑第四区块114。

然后,选出这些区块中,区块面积大于一门限值的区块。举例来说,第一区块111'、第二区块112与第三区块113的总区块面积为A1,门限值例如是40%~50%。在第一区块111'、第二区块112与第三区块113中,只有第一区块111'的区块面积介于总区块面积A1的40%~50%,因此选择第一区块111做为形成镂空部111a的对象。

然后,如图4B所示,在第一区块111'中形成至少一镂空部111a,以形成第一区块111。在实际半导体工艺中,镂空部111a内会填满介电材料145。由于第一区块111具有镂空部111a且其内填满介电材料145,因此能提高第一区块111的刚度。

然后,可以通过拉大二区块的间隔增强导电层110的刚度,避免二导电层110之间的介电层140(绘示在图1A的接垫结构100中)在打线过程中发生裂痕。例如,在任二相邻区块中,判断各区块的宽度是否大于门限宽度,其中各区块的宽度方向沿同一方向;若是,判断此二区块之间的间隔是否小于门限间隔。若此二区块之间的间隔小于门限间隔,则拉大此二区块之间的间隔实际上等于或大于门限间隔。

进一步举例来说,如图4B所示,第一区块111的第一宽度W1及第二区块112的第二宽度W2大于门限宽度,且第一区块111与第二区块112之间的间隔S12'小于门限间隔,因此可以拉大第一区块111与第二区块112之间的间隔S12'至图1B所示之间隔S12,其中间隔S12实际上等于或大于门限间隔。

在另一实施例中,若第一区块111与第二区块112之间的间隔大于门限间隔,则可以在第一区块111与第二区块112之间加入宽度小于门限宽度的区块,例如是图3A所示的第四区块114'。

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 接垫结构、应用该接垫结构的半导体芯片及其制造方法

- 接垫结构、导线接合结构及封装结构