一种FPGA芯片内各模块之间的布线拥塞优化方法

文献发布时间:2023-06-19 10:35:20

技术领域

本发明涉及微电子行业集成电路设计领域,尤其涉及一种FPGA芯片内各模块之间的布线拥塞优化方法。

背景技术

FPGA器件属于专用集成电路中的一种半定制电路,是可编程的逻辑门列阵,。FPGA的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用。FPGA的设计流程包括根据需求设计FPGA方案,编写设计代码,通过代码仿真保证设计方案和设计代码符合实际要求,通过EDA工具进行代码综合和布局布线,最后利用配置电路将相关文件下载至FPGA芯片中,验证实际运行效果。

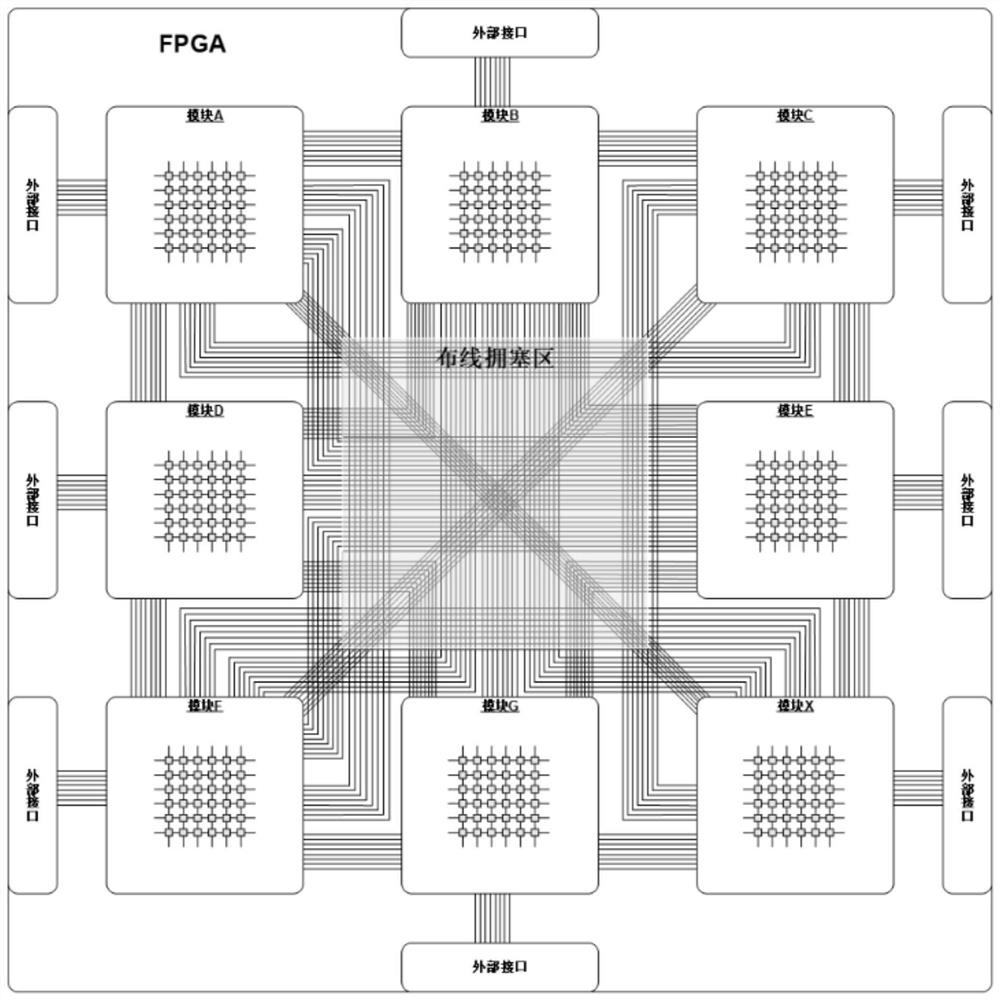

现有的FPGA芯片内模块众多,各模块间存在大量互连信号,如图1所示,而FPGA内布线资源有限,致使FPGA内部存在局部模块互连集中交叉区布线拥塞,布线拥塞会造成FPGA芯片工作频率降低,芯片工作不稳定,甚至会造成布局布线失败无法工作,同时,布局布线拥塞会大大增加EDA软件布局布线时间,使得设计开发迭代速度慢,FPGA开发效率变低。在FPGA芯片内模块之间有没有一种新的布线方法以解决上述问题,一直是个令业界困扰的难点。

发明内容

为了克服现有技术的缺陷,本发明所要解决的技术问题在于提出一种FPGA芯片内各模块之间的布线拥塞优化方法,避免了因模块间互连信号太多需要占用大量布线资源而造成的布线拥塞,杜绝了因布线拥塞造成的FPGA芯片工作频率降低、芯片工作不稳定,甚至会造成布局布线失败而无法工作的局面。

为达此目的,本发明采用以下技术方案:

一种FPGA芯片内各模块之间的布线拥塞优化方法,

步骤S1:通过EDA综合工具对FPGA芯片内部若干个电路模块进行预布线,并获取预布线结果;

步骤S2:对预布线结果进行数据分析,获取电路模块间布线方面是否存在拥塞问题,并统计存在布线拥塞的模块;

步骤S3:在存在布线拥塞的电路模块间插入布线优化模块,然后重新进行综合布局布线。

本发明优选地技术方案在于,通过EDA综合工具对FPGA芯片内部若干个电路模块进行预布线,并获取预布线结果之前包括:

通过EDA综合工具将FPGA设计代码转换成FPGA网表电路,并通过EDA综合工具将FPGA网表电路映射到FPGA芯片内部形成完整的电路模块。

本发明优选地技术方案在于,拥塞问题具体为,因FPGA芯片内部布线资源有限,FPGA内模块间低速并行信号过多导致的布线拥塞,造成布线时间过长、布线结果不满足电路设计时序要求、甚至因无布线线路而导致FPGA芯片布局布线失败。

本发明优选地技术方案在于,当存在拥塞问题时,步骤S3“在存在布线拥塞的模块间插入布线优化模块”的具体操作为:使用代码分析工具对获取的若干个存在布线拥塞的模块中插入布线优化模块进行优化,使低速并行信号转换成高速串行信号。

本发明优选地技术方案在于,当不存在拥塞问题时,FPGA芯片内部若干个电路模块继续进行布线,直至布线完毕。

本发明优选地技术方案在于,所述EDA综合工具为Synplify、Quartus、ISE、VivadoHLS或相关可等效代替工具。

本发明优选地技术方案在于,通过EDA综合工具将FPGA网表电路进行布局布线后再映射到FPGA芯片内部形成电路模块。

本发明优选地技术方案在于,使用移位寄存器或相关可等效代替电路实现低速并行信号转换成高速串行信号。

本发明优选地技术方案在于,对布线方面不存在拥塞问题的电路模块不进行插入布线优化模块。

本发明的有益效果为:

本发明提供的一种FPGA芯片内各模块之间的布线拥塞优化方法,通过EDA综合工具对FPGA芯片内部若干个电路模块进行预布线,并获取预布线结果;步骤S2:对预布线结果进行数据分析,获取电路模块间布线方面是否存在拥塞问题,并统计存在布线拥塞的模块;步骤S3:在存在布线拥塞的模块间插入布线优化模块,然后重新进行综合布局布线,通过此方法的实施,实现了FPGA芯片内各模块之间的线路优化,节省了FPGA芯片内部其他逻辑资源,并减少了因低速并行信号造成的走线过多,解决了线路拥塞问题。

附图说明

图1是现有技术中FPGA芯片各电路模块内部布线结构示意图;

图2是本发明具体实施方式中提供的FPGA芯片各电路模块内部布线结构示意图;

图3是本发明具体实施方式中提供的FPGA芯片工作时序图;

图4是本发明具体实施方式中提供的各电路模块芯通过布线优化模块优化示意图;

具体实施方式

下面结合附图并通过具体实施方式来进一步说明本发明的技术方案。

一种FPGA芯片内各模块之间的布线拥塞优化方法,包括:

步骤S1:通过EDA综合工具对FPGA芯片内部若干个电路模块进行预布线,并获取预布线结果;

在步骤S1中,EDA综合工具对FPGA芯片内部若干个电路模块进行预布线,并获取预布线结果,技术人员可以直观的获知预布线结果,提前发现若干个电路模块之间布线存在拥塞的问题,避免电路模块映射在FPGA芯片后出现问题,提高技术人员的工作效率;

步骤S2:对预布线结果进行数据分析,获取电路模块间布线方面是否存在拥塞问题,并统计存在布线拥塞的模块;

在步骤S2中,技术人员对预布线结果进行分析获取电路模块间布线方面是否存在拥塞问题,当预布线结果显示布线拥塞或布线时序违规时,技术人员可得知,哪些电路模块间存在布线拥塞问题;

步骤S3:在存在布线拥塞的电路模块间插入布线优化模块,然后重新进行综合布局布线;

在步骤S3中,这个方法,使得技术人员可以通过布线优化模块解决FPGA内部芯片间布局布线拥塞问题,提高了技术人员工作的效率。

通过EDA综合工具对FPGA芯片内部若干个电路模块进行预布线,并获取预布线结果之前包括:通过EDA综合工具将FPGA设计代码转换成FPGA网表电路,并通过EDA综合工具将FPGA网表电路映射到FPGA芯片内部形成完整的电路模块。

为了明确拥塞问题。进一步地,在实践中得出,拥塞问题具体为,因FPGA芯片内部布线资源有限,FPGA内模块间低速并行信号过多导致的布线拥塞,造成布线时间过长、布线结果不满足电路设计时序要求、甚至因无布线线路而导致FPGA芯片布局布线失败。

为了解决拥塞问题。进一步地,当存在拥塞问题时,步骤S3“在存在布线拥塞的模块间插入布线优化模块”的具体操作为:使用代码分析工具对获取的若干个存在布线拥塞的模块中插入布线优化模块进行优化,使低速并行信号转换成高速串行信号,这样的方式,技术人员通过将存在拥塞问题的电路模块代码导入代码分析工具进行分析,可以分析出存在拥塞问题的电路模块代码中存在并行信号过多,然后在存在拥塞问题的电路模块代码中插入布线优化模块代码,如图3所示,在发送端,使得低速并行信号转换成高速串行信号进行发送,减少了并行信号造成的走线过多,解决了布线拥塞的问题,在接收端,高速串行信号转换成低速并行信号,进一步地,如图4所示,以其中一个布线优化模块的发送侧为例,例如其中一个布线优化模块连接的模块上有八个触点,分别对应RX_D0至RX_D7,其中一个布线优化模块通过连接这八个触点获取到所连接的模块上的并行的信号,然后通过并行转串行,将低速并行的八个信号汇总成高速串行的信号,传递到其他布线优化模块;其他布线优化模块,例如另一个布线优化模块在接收到该汇总的信号后,会将汇总的信号复原为原始的由RX_D0至RX_D7触点得到的信号,再传递到另一个布线优化模块所连接的模块上,以此,对于各个模块而言,没有发生变化,而数据的传递过程由原来需要的八根并行的线路,变成了一根高速串行信号。另,八根线路为例,例如每个线路的传输速率为100M,则对应的高速串行信号的传输速度则至少需要为800M,需要大于或等于各个线路的传输速率的总和,以此保证数据传递的及时性。

为了提高布线效率。进一步地,当不存在拥塞问题时,FPGA芯片内部若干个电路模块继续进行布线,直至布线完毕,这样的方式,使得不存在拥塞问题的电路模块可以省去分析时间,提高了效率。

为了获得FPGA网表电路。进一步地,通过所述EDA综合工具为Synplify、Quartus、ISE、Vivado HLS或相关可等效代替工具获得FPGA网表电路。

通过EDA综合工具将FPGA网表电路进行布局布线后再映射到FPGA芯片内部形成电路模块。

为了使并行信号传转换成串行信号。进一步地,使用移位寄存器或相关可等效代替电路实现低速并行信号转换成高速串行信号。

为了提高布线工作效率及节省FPGA芯片内部资源空间。进一步地,对布线方面不存在拥塞问题的电路模块不进行插入布线优化模块。

本发明是通过优选实施例进行描述的,本领域技术人员知悉,在不脱离本发明的精神和范围的情况下,可以对这些特征和实施例进行各种改变或等效替换。本发明不受此处所公开的具体实施例的限制,其他落入本申请的权利要求内的实施例都属于本发明保护的范围。

- 一种FPGA芯片内各模块之间的布线拥塞优化方法

- 布线拥塞预估方法及布线拥塞预估系统