一种倒装LED芯片及其制备方法

文献发布时间:2023-06-19 10:54:12

技术领域

本发明属于芯片技术领域,具体涉及一种倒装LED芯片及其制备方法。

背景技术

正装LED芯片会出现电极挤占发光面积从而影响发光效率的问题,因此芯片研发人员设计了倒装结构,即把正装芯片倒置,使发光层激发出的光直接从电极的另一面发出(衬底最终被剥去,芯片材料是透明的),该结构在大功率芯片较多用到。

倒装LED芯片具有以下显著优点,一是可通大电流使用;二是尺寸可以做到更小,光学更容易匹配;三是散热功能的提升,使芯片的寿命得到了提升;四是抗静电能力的提升;五是为后续封装工艺发展打下基础。

目前的倒装LED芯片主要分两种工艺方向,一种以DBR作为反射层,一种以银镜作为反射层。但这两种反射层的倒装LED芯片都有各自的缺点:DBR反射层膜质比较脆,在切割崩裂时容易出现裂纹,进而影响可靠性,同时DBR反射层的亮度较银镜反射层低;银镜反射层,膜质比较容易氧化,因此必须添加金属保护层以防止银镜反射层的氧化;此外,银镜层跟ITO层的粘附性不好,因此需要在两者之间加上Ni金属层作为过渡层,而Ni本身有吸光的效果,这降低了银镜的反射率,进而导致了亮度的下降。

发明内容

本发明旨在至少解决上述现有技术中存在的技术问题之一。为此,本发明提出一种倒装LED芯片,通过调整芯片结构和制备工艺,在同时设置DBR反射层和银镜层的基础上,省略了银镜层的金属保护层,以及银镜层与ITO层之间的金属粘结层,因此提高了所述倒装LED芯片的亮度,同时简化工艺、节约成本。

本发明还提出一种上述倒装LED芯片的制备方法。

根据本发明的一个方面,提出了一种倒装LED芯片,包括,

ITO层,所述ITO层的一侧具有粗糙表面;

复合反射层,所述复合反射层设于所述粗糙表面上,所述复合反射层包括沿所述粗糙表面依次叠加的银镜层、二氧化硅层和DBR层。

根据本发明的一种优选的实施方式,至少具有以下有益效果:

(1)本发明中,由于ITO层的粗糙表面,增加了ITO层与银镜层之间的粘结强度,因此可省略传统倒装LED芯片中,ITO层与银镜层之间的金属粘结层,节约了成本。

(2)由于传统倒装LED芯片中,金属粘结层本身具有一定的吸光性,本发明省略了金属粘结层,进一步提升了倒装LED芯片的亮度。

(3)本发明中,二氧化硅层,兼具绝缘层和银镜层的金属保护层的作用,因此可省略传统倒装LED芯片中的金属保护层,节约了成本。

(4)本发明中,二氧化硅层还具有绝缘作用,避免了倒装LED芯片切割过程中,因DBR层崩裂而出现的漏电现象,增加了产品的良率。

(5)传统银镜层的保护层为TiW层,该材质进行高温合金反应后容易因应力不均而出现裂纹,本申请省略了金属保护层,因此提升了成品率。

(6)本发明提供的复合反射层,将银镜层与DBR层复合使用,两者发生协同作用,提升了倒装LED芯片的亮度。

在本发明的一些实施方式中,所述ITO层厚度为30nm~45nm。

在本发明的一些实施方式中,所述银镜层厚度为150nm~200nm。

在本发明的一些实施方式中,所述二氧化硅层厚度为250nm~400nm。

在本发明的一些实施方式中,所述DBR层厚度为2500nm~3000nm。

根据本发明的再一个方面,提出了所述倒装LED芯片的制备方法,包括如下步骤:

S1.在衬底上依次设置N型GaN层、发光量子阱、P型GaN层和所述ITO层;

S2.自所述ITO层开始,刻蚀步骤S1所得部件的局部区域直至露出所述N型GaN层,形成N-GaN台面;

S3.腐蚀所述ITO层,形成所述粗糙表面;

S4.刻蚀步骤S3所得部件边缘位置直至所述衬底,形成刻槽;

S5.在所述N-GaN台面表面设置金属绑定层;

S6.在步骤S5所得部件,所述粗糙表面上设置所述银镜层;

S7.在步骤S6所得部件远离所述衬底一侧,依次设置全覆盖的所述二氧化硅层和DBR层;

S8.垂直所述DBR层,自所述DBR层开始刻蚀步骤S7所得部件,至所述金属绑定层,形成N导电孔,至所述银镜层,形成P导电孔;

S9.自所述N导电孔开始设置负电极,自所述P导电孔开始设置正电极,即得所述倒装LED芯片。

在本发明的一些实施方式中,步骤S1中,所述衬底为蓝宝石。

在本发明的一些实施方式中,步骤S1中,所述N型GaN层、发光量子阱和P型GaN层的设置方法为MOCVD。

在本发明的一些实施方式中,步骤S1中,所述ITO层的设置方法为磁控溅射。

在本发明的一些实施方式中,步骤S2中,所述刻蚀,方法为,先充分过刻蚀掉对应区域的ITO层,再干法刻蚀掉发光量子阱和P型GaN层,直至N型GaN层。

在本发明的一些实施方式中,所述充分过刻蚀是采用蚀刻液把有光刻胶保护的ITO也蚀刻掉2~3μm。

在本发明的一些实施方式中,步骤S3中,所述粗糙表面,设置方法为以酸的水溶液进行腐蚀。

在本发明的一些实施方式中,所述酸的水溶液,为硝酸水溶液和硫酸水溶液中的至少一种。

在本发明的一些实施方式中,所述粗糙表面,设置方法为以浓硫酸(质量百分数≥90%),于50℃~70℃下腐蚀6min~10min。

在本发明的一些优选的实施方式中,所述粗糙表面,设置方法为以浓硫酸(质量百分数98%),于60℃下腐蚀8min。

在本发明的一些实施方式中,步骤S3中,所述粗糙表面上有粗糙凸起,所述粗糙凸起高度为3nm~5nm。

在本发明的一些实施方式中,步骤S4中,所述刻槽,设置方法为,先光刻保护所述刻槽之外的区域,再以等离子体刻蚀的方法,刻蚀至所述衬底。

在本发明的一些实施方式中,步骤S5中,所述金属绑定层,为金属复合层,所述金属复合层包括在N-GaN层表面设置的Cr层,以及沿所述Cr层设置的Al层、Ti层、Pt层、Au层中的至少一层。

在本发明的一些实施方式中,步骤S5中,所述金属绑定层的设置方法为,光刻保护与金属蒸镀相结合。

在本发明的一些实施方式中,步骤S6中,所述银镜层的设置方法为光刻保护与磁控溅射相结合。

在本发明的一些实施方式中,步骤S6和S7之间的等待时间≤3h。

限制等待时间的目的是,尽量减少所述银镜层与空气中氧气的接触,防止所述银镜层的氧化。

在本发明的一些实施方式中,步骤S7中,所述二氧化硅层的设置方法为等离子体增强化学的气相沉积法。

在本发明的一些实施方式中,步骤S7中,所述DBR层的设置方法为真空蒸镀。

在本发明的一些实施方式中,步骤S8中,所述N导电孔和所述P导电孔的设置方法为光刻保护与干法刻蚀相结合。

在本发明的一些实施方式中,步骤S9中,所述正电极和所述负电极的材质为AuSn合金。

在本发明的一些实施方式中,所述制备方法中,所有光刻保护步骤后,均需采用丙酮溶解光刻保护中应用的光刻胶。

由于步骤S6之后,清洗光刻胶用的试剂为丙酮,不会导致所述银镜层的氧化;由于步骤S6和步骤S7之间的等待时间≤3h,加之步骤S7中操作需在真空中进行,这进一步避免了所述银镜层与空气中氧气的接触;由于设置了全覆盖的二氧化硅层,因此隔绝了所述银镜层与空气的接触。综上,本发明提供的倒装LED芯片,由于其特殊的结构设置和独特的制备方法,因此不需要设置金属保护层。

附图说明

下面结合附图和实施例对本发明做进一步的说明,其中:

图1为本发明实施例1步骤S1所得部件的结构示意图;

图2为本发明实施例1步骤S2所得部件的结构示意图;

图3为本发明实施例1步骤S4所得部件的结构示意图;

图4为本发明实施例1步骤S5所得部件的结构示意图;

图5为本发明实施例1步骤S6所得部件的结构示意图;

图6为本发明实施例1步骤S8所得部件的结构示意图;

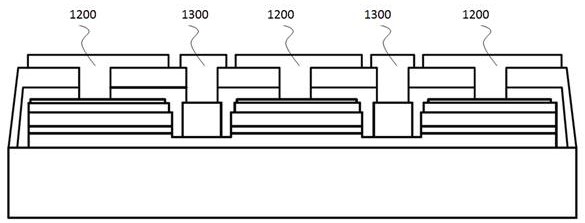

图7为本发明实施例1所得倒装LED芯片的结构示意图。

附图标记:

100:衬底;

200:外延层;201:N型GaN层;202:发光量子阱;203:P型GaN层;

300:ITO层;

400:N-GaN台面;

500:刻槽;

600:金属绑定层;

700:银镜层;

800:二氧化硅层;

900:DBR层;

1000:P导电孔;

1100:N导电孔;

1200:正电极;

1300:负电极。

具体实施方式

下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

在本发明的描述中,需要理解的是,涉及到方位描述,例如上、下、前、后、左、右等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

在本发明的描述中,若干的含义是一个以上,多个的含义是两个以上,大于、小于、超过等理解为不包括本数,以上、以下、以内等理解为包括本数。如果有描述到第一、第二只是用于区分技术特征为目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量或者隐含指明所指示的技术特征的先后关系。

本发明的描述中,除非另有明确的限定,设置、安装、连接等词语应做广义理解,所属技术领域技术人员可以结合技术方案的具体内容合理确定上述词语在本发明中的具体含义。

本发明的描述中,参考术语“一个实施例”、“一些实施例”、“示意性实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

实施例1

本实施例制备了一种倒装LED芯片,具体过程为:

S1.在蓝宝石衬底100上,先以MOCVD法依次设置N型GaN层201、发光量子阱202、P型GaN层203,再以磁控溅射法在P型GaN层表面设置30nm厚的ITO层300;

S2.自ITO层300开始,刻蚀步骤S1所得部件的部分位置,直至N型GaN层201,形成N-GaN台面400;

S3.以质量分数为98%的浓硫酸处理ITO层300,处理时间为8min,形成粗糙表面;

S4.以光刻保护与等离子体刻蚀相结合的方法,刻蚀步骤S3所得部件边缘位置直至衬底,形成刻槽500;

S5.采用光刻保护与金属蒸镀相结合的方法,在N-GaN台面400表面设置金属绑定层600;

S6.采用光刻保护与金属蒸镀相结合的方法,在步骤S5所得部件,粗糙表面上设置银镜层700,厚度为150nm;

S7.在完成步骤S6的3h之内,在步骤S6所得部件远离衬底一侧,依次以等离子增强化学的气相沉积法设置全覆盖的二氧化硅层800(厚度为270nm)、以真空蒸镀法设置全覆盖的DBR层900(厚度为2800nm);

S8.垂直DBR层900,自DBR层900开始干法刻蚀步骤S7所得部件,至金属绑定层600,形成N导电孔1100,至银镜层,形成P导电孔1000;

S9.自N导电孔1100开始设置材质为AuSn合金的负电极1300,自P导电孔1000开始设置材质为AuSn合金的正电极1200,即得倒装LED芯片。

本实施例步骤S1所得部件的结构示意图如图1所示;步骤S2所得部件的结构示意图如图2所示;步骤S4所得部件的结构示意图如图3所示;步骤S5所得部件的结构示意图如图4所示;步骤S6所得部件的结构示意图如图5所示;步骤S8所得部件的结构示意图如图6所示;本实施例所得倒装LED芯片的结构示意图如图7所示。

对比例1

本对比例制备了一种倒装LED芯片,与实施例1的区别在于,具体过程为:

(1)步骤S7中,不设置DBR层900;

(2)步骤S8中,垂直于二氧化硅层开始刻蚀。

对比例2

本实施例制备了一种倒装LED芯片,与实施例1的区别在于,具体过程为:

(1)不进行步骤S6,在步骤S5所得部件远离衬底一侧,依次以等离子增强化学的气相沉积发设置全覆盖的二氧化硅层、以真空蒸镀法设置全覆盖的DBR层。

试验例

本试验例测试了实施例和对比例制备的倒装LED芯片的性能。其中:

亮度的测试方法为:每个实施案例做3片,用点测机对各实施例所得芯片成品进行测试,取测试结果的范围值。测试结果如表1所示。

表1具体实施方式所得倒装LED芯片的亮度结果。

具体的成本核算如下:

相对于具有TiW金属保护层的LED芯片:由于TiW靶材的价格约为1000元/个;本发明省略了TiW保护层,可节约的成本为0.4元/个芯片。

相对于具有TiW金属保护层的LED芯片:由于TiW靶材的价格约为1000元/个;一个靶材可以作业180RUN,每RUN作业16片,本发明省略了TiW保护层,可节约的成本为0.35元/每片,TiW厚度200nm,采用溅射镀膜机进行镀膜。

相对于具有AgTiW/Pt/TiW/Pt/TiW/Pt金属保护层的LED芯片:参考商业上各层的常用厚度,用电子束金属蒸镀机镀膜,每炉60片,每炉需TiW厚度200nm,Pt厚度100nm,Pt的成本为240元/g,需要Pt的重量为12g,考虑Pt的回收率约为80%,TiW2.5元/g,需要10g左右。因此,平均计算可知,单片成本约节约10元。

综上,本发明提供的倒装LED芯片较单一设置银镜层作为反射层和单一设置DBR反射层的芯片均具有较高的亮度,虽然数据上仅升高了2 mW ~3 mW,本领域普通技术人员知晓当亮度大于95 mW时,要提升1 mW都是极为困难的。此外,本发明通过控制倒装LED芯片的制备方法,省略了金属保护层和金属粘结层的结构,节约了成本。

上面结合附图对本发明实施例作了详细说明,但是本发明不限于上述实施例,在所属技术领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下作出各种变化。此外,在不冲突的情况下,本发明的实施例及实施例中的特征可以相互组合。

- 用于倒装LED芯片的荧光粉膜及其制备方法与倒装LED芯片

- 一种LED倒装芯片及LED倒装芯片的图形化衬底