金属互连结构的制造方法

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及一种半导体集成电路的制造方法,特别是涉及一种金属互连结构的制造方法。

背景技术

在28nm以上技术节点的制程中,采用Cu作为互连金属,同时采用TaN作为Cu的扩散阻挡层(Barrier)以及采用Ta作为Cu的黏附层(glue layer),由TaN、Ta和Cu的叠加结构实现金属互连技术。随着器件尺寸的减小,尤其是进入14nm以下的技术节点的工艺制程后,Cu晶粒电子散射程度加剧,造成Cu电阻增大,从而导致严重的Rc延迟。Cu互连技术将越来越难以满足金属互连阻值技术指标与可靠性。因此,寻找合适的替代材料愈发迫切。

如图1所示,是现有金属互连结构的制造方法形成的金属互连结构的示意图;现有方法采用铜制程且采用大马士革工艺实现,这里以双大马士革工艺为例进行说明,现有金属互连结构的制造方法包括如下步骤:

步骤一、提供前层结构,所述前层结构中形成有定义金属互连结构的图形结构的凹槽104。

所述金属互连结构包括通孔(Vias)和金属连线(Lines)。所述凹槽104同时定义所述通孔和所述金属连线的图形结构,所述凹槽104由通孔开口104a和沟槽104b叠加而成,所述通孔开口104a位于部分区域的所述沟槽104b的底部,所述通孔开口104a和所述沟槽104b呈连通结构。后续,步骤四完成后同时形成所述通孔和所述金属连线,所述通孔由填充于所述通孔开口104a中的TaN层和Ta层的叠加层105和所述铜层106叠加而层,所述金属连线由填充于所述沟槽104b中的所述TaN层和Ta层的叠加层105和所述铜层106叠加而层。

所述凹槽104形成于层间膜103中。所述层间膜103的材料包括氧化层或低K介质层。

所述层间膜103的材料采用低K介质层,低K介质层的材料包括BD或BDⅡ。BD是由C,H,O,Si等元素组成的介质材料,K值为2.5~3.3。BDⅡ是BD改了的改进版本。

在所述低K介质层的底部还形成有第一氮掺杂碳化硅(N Doped SiC,NDC)层103a,TEOS氧化层103b。所述第一NDC103a作为底部金属互连结构102向上扩散的阻挡层。

在所述低K介质层的顶部还形成有第二NDC层103c、无氮抗反射涂层(NFDARC)103d和金属硬掩膜层103e。

所述前层结构中,在所述层间膜103的底部包括有半导体衬底以及位于所述半导体衬底和所述层间膜103之间的多层底部层间膜101和底部金属互连结构102。图1中未显示所述半导体衬底,并仅显示了一层底部层间膜101和一层底部金属互连结构102。

所述底部层间膜101的结构和所述层间膜103的结构以及形成工艺相同。所述底部金属互连结构102的形成工艺和当前层的所述金属互连结构的形成工艺相同,这里仅以当前层的所述金属互连结构的形成工艺为例进行说明,实际工艺中,所述金属互连结构会包括多层,各层的工艺都能采用现有方法所公开的工艺。

所述半导体衬底包括硅衬底。

在所述半导体衬底上形成有半导体器件。

步骤二、形成TaN层和Ta层的叠加层105,所述TaN层和Ta层的叠加层105形成在所述凹槽104的底部表面和侧面并延伸到所述凹槽104外的所述前层结构表面上,叠加层105中的TaN层作为扩散阻挡层,Ta层作为黏附层。

现有方法中,形成叠加层105需要采用3次PVD生长和一次干法刻蚀实现,工艺较为复杂,现说明如下:

如图2A至图2D所示,是现有金属互连结构的制造方法中形成TaN和Ta叠加形成的扩散阻挡层和粘附层的各分步骤中的示意图,包括:

如图2A所示,进行第一次PVD生长形成TaN层105a。图2A中仅简单示意了通孔开口104a和沟槽104b,TaN层105a形成在通孔开口104a和沟槽104b的内侧表面和外部表面上。

如图2B所示,进行第二次PVD生长形成Ta层105b。

如图2C所示,进行干法刻蚀将通孔开口104a底部表面的Ta层105b去除,这是为了降低通孔的接触电阻。

如图2D所示,进行第三次PVD生长形成Ta层105c。Ta层由两次PVD生长的Ta层105b和105c叠加而成。

步骤三、形成铜层106,所述铜层106将所述凹槽104完全填充并延伸到所述凹槽104外的所述TaN层和Ta层的叠加层105表面上。

铜层106采用电镀工艺(ECP)形成。

步骤四、进行化学机械研磨(CMP)将所述凹槽104外的所述铜层106和所述TaN层和Ta层的叠加层105去除以及将所述凹槽104区域内的所述铜层106和所述TaN层和Ta层的叠加层105的顶部表面和所述凹槽104的顶部表面相平,由填充于所述凹槽104中的所述TaN层和Ta层的叠加层105和所述铜层106叠加形成所述金属互连结构。

由图1所示可知,由于铜的硬度约为40,故进行CMP之后容易出现标记107所示的蝶形(dish)缺陷。

发明内容

本发明要解决的技术问题是提供一种金属互连结构的制造方法,能降低金属互连电阻且使金属互连电阻小于Cu互连电阻。

为解决上述技术问题,本发明提供的金属互连结构的制造方法包括如下步骤:

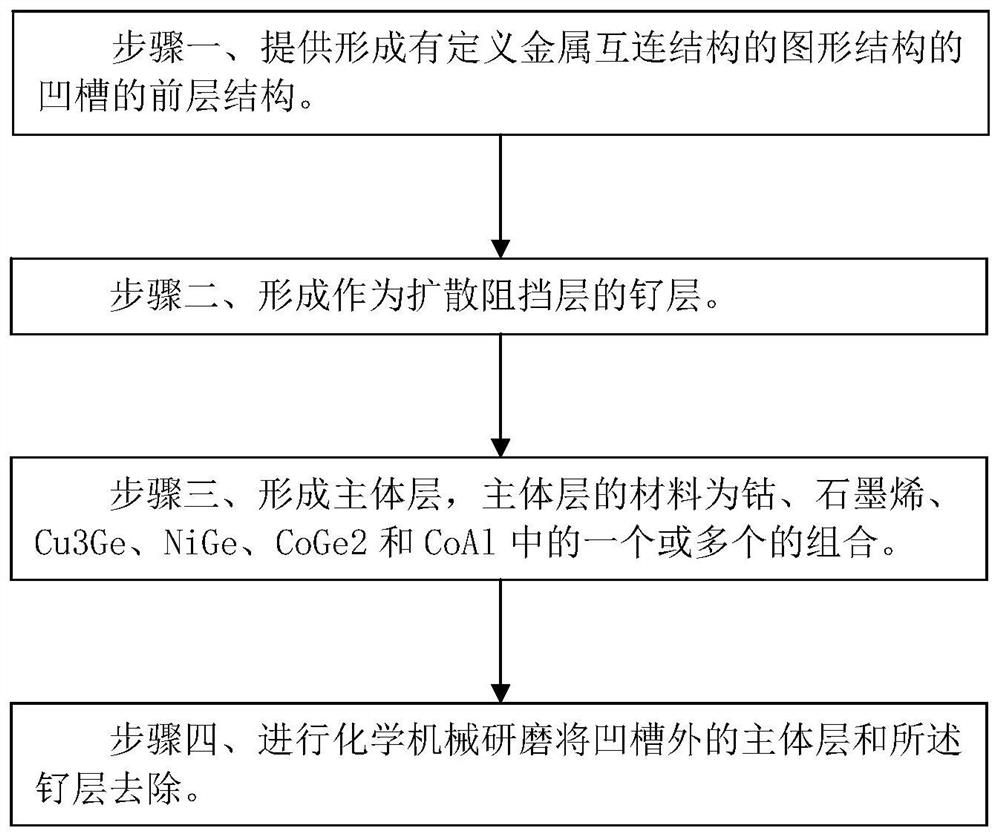

步骤一、提供前层结构,所述前层结构中形成有定义金属互连结构的图形结构的凹槽。

步骤二、形成钌(Ru)层,所述钌层形成在所述凹槽的底部表面和侧面并延伸到所述凹槽外的所述前层结构表面上,所述钌层作为扩散阻挡层。

步骤三、形成主体层,所述主体层将所述凹槽完全填充并延伸到所述凹槽外的所述钌层表面上,所述主体层的材料为钴(Co)、石墨烯、Cu3Ge、NiGe、CoGe2和CoAl中的一个或多个的组合。

步骤四、进行化学机械研磨(CMP)将所述凹槽外的所述主体层和所述钌层去除以及将所述凹槽区域内的所述主体层和所述钌层的顶部表面和所述凹槽的顶部表面相平,由填充于所述凹槽中的所述钌层和所述主体层叠加形成所述金属互连结构。

进一步的改进是,步骤二中,所述钌层的厚度大于1nm。

进一步的改进是,所述钌层的生长工艺为CVD、ALD和PVD中的一个或多个的组合。

进一步的改进是,步骤三中,所述主体层的材料为钴时,所述主体层的生长工艺为CVD、ALD和PVD中的一个或多个的组合。

进一步的改进是,所述金属互连结构包括通孔和金属连线。

进一步的改进是,步骤一中的所述凹槽用于单独定义所述通孔的图形结构,步骤四完成后所形成的所述金属互连结构为所述通孔。

进一步的改进是,步骤一中的所述凹槽用于单独定义所述金属连线的图形结构,步骤四完成后所形成的所述金属互连结构为所述金属连线。

进一步的改进是,步骤一中的所述凹槽同时定义所述通孔和所述金属连线的图形结构,所述凹槽由通孔开口和沟槽叠加而成,所述通孔开口位于部分区域的所述沟槽的底部,所述通孔开口和所述沟槽呈连通结构;步骤四完成后同时形成所述通孔和所述金属连线,所述通孔由填充于所述通孔开口中的所述钌层和所述主体层叠加而层,所述金属连线由填充于所述沟槽中的所述钌层和所述主体层叠加而层。

进一步的改进是,所述凹槽形成于层间膜中。

进一步的改进是,所述前层结构中,在所述层间膜的底部包括有半导体衬底以及位于所述半导体衬底和所述层间膜之间的多层底部层间膜和底部金属互连结构。

进一步的改进是,所述半导体衬底包括硅衬底。

进一步的改进是,在所述半导体衬底上形成有半导体器件。

进一步的改进是,所述半导体器件的工艺节点为14nm以下。

进一步的改进是,所述层间膜和所述底部层间膜的材料包括氧化层或低K介质层。

进一步的改进是,所述通孔和所述底部金属互连结构连接。

和现有Cu互连结构不同,本发明对金属互连结构的金属膜层进行了特别的设置,将扩散阻挡层设置为钌层,而主体层的材料设置为钴、石墨烯、Cu3Ge、NiGe、CoGe2和CoAl中的一个或多个的组合,以钴层为例,钌和钴的电阻率虽然高于Cu,但是随着厚度的减薄如减薄到7nm以下时,钌和钴具有和Cu相似的电阻值;但是,钌和钴的熔点高于铜的熔点,而熔点越高的金属的抗电迁移能力就越强,故本发明中扩散阻挡层的厚度占主体层的厚度比例较小,金属互连结构的电阻值主要由主体层确定;而由于铜的抗电迁移能力较差,故在工艺技术节点缩小后,铜互连结构中的TaN和Ta组成的阻挡层和粘附层的厚度占比增加,使得电阻率较高的TaN和Ta的电阻在整个铜互连结构中的电阻占比增加,故会使整个铜互连结构的电阻增加;而本发明由于扩散阻挡层的所需厚度较小且钌作为扩散阻挡层时本身的电阻率也较小,故本发明能降低金属互连电阻且使金属互连电阻小于Cu互连电阻,能改善Rc延迟问题,提升器件性能,特别适合在14nm以下工艺技术节点中应用。

另外,本发明的钌和钴的硬度都大于铜,故进行钌和钴的化学机械研磨时,不会产生蝶形缺陷和腐蚀(erosion)缺陷,而铜互连结构中由于铜较软,故容易在铜的化学机械研磨后产生蝶形缺陷,所以本发明能消除蝶形缺陷和腐蚀缺陷,对工艺实现优化。

另外,由于现有采用铜制程的方法中,TaN和Ta的形成工艺需要三次PVD生长和一次干刻实现,工艺复杂;本发明实施例方法中的Ru层采用一次生长工艺如CVD生长工艺即可实现,不仅Ru层的电性和防扩散性能更佳,而且工艺更加简单,所以本发明实施例方法还能在优化性能的同时简化工艺。

附图说明

下面结合附图与具体实施方式对本发明作进一步详细的说明:

图1是现有金属互连结构的制造方法形成的金属互连结构的示意图;

图2A-图2D是现有金属互连结构的制造方法中形成TaN和Ta叠加形成的扩散阻挡层和粘附层的各分步骤中的示意图;

图3是本发明实施例金属互连结构的制造方法的流程图;

图4是本发明实施例金属互连结构的制造方法形成的金属互连结构的示意图。

具体实施方式

如图3所示,是本发明实施例金属互连结构的制造方法的流程图;如图4所示,是本发明实施例金属互连结构的制造方法形成的金属互连结构的示意图;本发明实施例金属互连结构的制造方法包括如下步骤:

步骤一、提供前层结构,所述前层结构中形成有定义金属互连结构的图形结构的凹槽204。

本发明实施例方法中,所述金属互连结构包括通孔(Vias)和金属连线(Lines)。所述凹槽204同时定义所述通孔和所述金属连线的图形结构,所述凹槽204由通孔开口204a和沟槽204b叠加而成,所述通孔开口204a位于部分区域的所述沟槽204b的底部,所述通孔开口204a和所述沟槽204b呈连通结构。后续,步骤四完成后同时形成所述通孔和所述金属连线,所述通孔由填充于所述通孔开口204a中的所述钌层205和所述主体层206叠加而层,所述金属连线由填充于所述沟槽204b中的所述钌层205和所述主体层206叠加而层。这样,所述通孔和所述金属连线能同时形成,为双大马士革工艺。

在其他实施例方法中,也能为:所述凹槽204用于单独定义所述通孔的图形结构,后续步骤四完成后所形成的所述金属互连结构为所述通孔。或者,步骤一中的所述凹槽204用于单独定义所述金属连线的图形结构,或者,步骤四完成后所形成的所述金属互连结构为所述金属连线。这样,所述通孔和所述金属连线需要分开形成,为单大马士革工艺。

所述凹槽204形成于层间膜203中。所述层间膜203的材料包括氧化层或低K介质层。

在一较佳实施例方法中,所述层间膜203的材料采用低K介质层,低K介质层的材料包括BD或BDⅡ。BD是由C,H,O,Si等元素组成的介质材料,K值为2.5~3.3。BDⅡ是BD改了的改进版本。

在所述低K介质层的底部还形成有第一氮掺杂碳化硅(N Doped SiC,NDC)层203a,TEOS氧化层203b。所述第一NDC203a作为底部金属互连结构202向上扩散的阻挡层。

在所述低K介质层的顶部还形成有第二NDC层203c、无氮抗反射涂层(NFDARC)203d和金属硬掩膜层203e。

在实际工艺中,所述层间膜203的低K介质层的底部和顶部的材料层能根据需要进行相应的改变。

所述前层结构中,在所述层间膜203的底部包括有半导体衬底以及位于所述半导体衬底和所述层间膜203之间的多层底部层间膜201和底部金属互连结构202。图4中未显示所述半导体衬底,并仅显示了一层底部层间膜201和一层底部金属互连结构202。

所述底部层间膜201的结构和所述层间膜203的结构以及形成工艺相同。所述底部金属互连结构202的形成工艺和当前层的所述金属互连结构的形成工艺相同,这里仅以当前层的所述金属互连结构的形成工艺为例进行说明,实际工艺中,所述金属互连结构会包括多层,各层的工艺都能采用本发明实施例方法所公开的工艺。

所述半导体衬底包括硅衬底。

在所述半导体衬底上形成有半导体器件。

所述半导体器件的工艺节点为14nm以下。在14nm以下的工艺节点时,本发明实施例方法能取得比现有铜制程工艺更为明显的技术效果。

步骤二、形成钌层205,所述钌层205形成在所述凹槽204的底部表面和侧面并延伸到所述凹槽204外的所述前层结构表面上,所述钌层205作为扩散阻挡层。所述钌层205在图4中也用Ru标出。

本发明实施例方法中,所述钌层205的厚度大于1nm。

所述钌层205的生长工艺为CVD、ALD和PVD中的一个或多个的组合。

在一较佳实施例方法中,所述钌层205的沉积采用CVD沉积,所述钌层205的厚度不小于2nm,CVD沉积的温度为300℃,气压30Pa,退火2分钟,退火环境为非氧化性保护气,如氢气,氦气,氮气,氩气等,并不限于以上气体。

步骤三、形成主体层206,所述主体层206将所述凹槽204完全填充并延伸到所述凹槽204外的所述钌层205表面上。本发明实施例方法中,所述主体层206的材料为钴,所述主体层206在图4中也用Co标出。

本发明实施例方法中,所述主体层206的生长工艺为CVD、ALD和PVD中的一个或多个的组合。

在一较佳实施例方法中,所述主体层206的Co沉积采用CVD沉积,CVD沉积的温度为300℃,气压30Pa。Co填满整个Vias204a和Lines204b。

在其他实施例方法中也能为:所述主体层206的材料为石墨烯、Cu3Ge、NiGe、CoGe2和CoAl中的一个或多个的组合。

步骤四、进行化学机械研磨将所述凹槽204外的所述主体层206和所述钌层205去除以及将所述凹槽204区域内的所述主体层206和所述钌层205的顶部表面和所述凹槽204的顶部表面相平,由填充于所述凹槽204中的所述钌层205和所述主体层206叠加形成所述金属互连结构。

本发明实施例方法中,CMP研磨将过量的Co研磨平整,达到所需金属厚度。

正如前面所述,本发明实施例方法采用双大马士革工艺,会同时形成所述通孔和所述金属连线,所述通孔由填充于所述通孔开口204a中的所述钌层205和所述主体层206叠加而层,所述金属连线由填充于所述沟槽204b中的所述钌层205和所述主体层206叠加而层。所述通孔和所述底部金属互连结构202连接。

和现有Cu互连结构不同,本发明实施例方法对金属互连结构的金属膜层进行了特别的设置,将扩散阻挡层设置为钌层205,而主体层206的材料设置为钴、石墨烯、Cu3Ge、NiGe、CoGe2和CoAl中的一个或多个的组合,以钴层为例,钌和钴的电阻率虽然高于Cu,但是随着厚度的减薄如减薄到7nm以下时,钌和钴具有和Cu相似的电阻值,具体为:Ru、Co和Cu的电阻率分别为7.1μΩ·cm、5.6μΩ·cm和1.68μΩ·cm;但当厚度减小至7nm时,Co和Ru具有类似Cu的电阻值。但是,钌和钴的熔点高于铜的熔点,具体为:Ru和Co的熔点分别为2334℃和1495℃和,均高于Cu的1085℃的熔点;而熔点越高的金属的抗电迁移能力就越强,故本发明实施例方法中扩散阻挡层的厚度占主体层206的厚度比例较小,金属互连结构的电阻值主要由主体层206确定;而由于铜的抗电迁移能力较差,使其必须搭配TaN和Ta使用,故在工艺技术节点缩小后,铜互连结构中的TaN和Ta组成的阻挡层和粘附层的厚度占比增加,使得电阻率较高的TaN和Ta的电阻在整个铜互连结构中的电阻占比增加,故会使整个铜互连结构的电阻增加;而本发明实施例方法由于扩散阻挡层的所需厚度较小且钌作为扩散阻挡层时本身的电阻率也较小,故本发明实施例方法能降低金属互连电阻且使金属互连电阻小于Cu互连电阻,特别适合在14nm以下工艺技术节点中应用。

另外,本发明实施例方法的钌和钴的硬度都大于铜,故进行钌和钴的化学机械研磨时,不会产生蝶形缺陷和腐蚀缺陷,而铜互连结构中由于铜较软,故容易在铜的化学机械研磨后产生蝶形缺陷,所以本发明实施例方法能消除蝶形缺陷和腐蚀缺陷,对工艺实现优化。由图4所示可知,本发明实施例方法完成步骤四的CMP后,所述金属互连结构的表面平坦,不会出现凹陷即蝶形缺陷;而图1对应的现有方法完成铜的CMP之后,则会出现标记107对应的蝶形缺陷。

另外,由于现有采用铜制程的方法中,TaN和Ta的形成工艺需要三次PVD生长和一次干刻实现,工艺复杂;本发明实施例方法中的Ru层205采用一次生长工艺如CVD生长工艺即可实现,不仅Ru层205的电性和防扩散性能更佳,而且工艺更加简单,所以本发明实施例方法还能在优化性能的同时简化工艺。

以上通过具体实施方式对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

- 金属互连,制造金属互连的方法,半导体装置和制造半导体装置的方法

- 金属硬掩膜结构、制造方法及铜互连结构制造方法