Ka波段接地共面波导金丝过渡结构

文献发布时间:2023-06-19 11:49:09

技术领域

本申请属于微波无线电技术领域,更具体地说,是涉及一种Ka波段接地共面波导金丝过渡结构。

背景技术

Ka波段是指频率在26.5~40GHz的无线电波波段。多芯片组件(Mul ti-ChipModule,简称MCM)将多个集成电路芯片和其它片式元器件组装在一块高密度多层互连基板上,是微波/毫米波组件主流的实现方案。其中,传输线与芯片的连接是微波/毫米波组件组装流程的关键环节。常见的传输线结构有微带线、共面波导(Coplanar waveguide,简称CPW)、带状线等。其中,共面波导的大面积接地与信号线处于同一平面,可以有效抑制辐射损耗和高频色散,且结构设计灵活,可衍生出接地共面波导、非对称共面波导等,并可与多芯片组件中其它部件能更好的进行集成。对于较低频段的多芯片组件,传输线与芯片可通过金丝键合直接相连。然而,由于接地共面波导与金丝的阻抗差异巨大,将金丝与接地共面波导中信号线直接相连,会因阻抗失配引起较大的电磁波反射,使整个结构的回波损耗和驻波比性能恶化,且频率越高,恶化越严重。

发明内容

本申请实施例的目的在于提供一种Ka波段接地共面波导金丝过渡结构,以解决现有技术中存在的Ka波段接地共面波导与金丝连接,会因阻抗失配引起回波损耗和驻波比性能恶化的技术问题。

为实现上述目的,本申请采用的技术方案是:提供一种Ka波段接地共面波导金丝过渡结构,包括接地共面波导、芯片和连接所述芯片与所述接地共面波导的金丝,所述接地共面波导包括基板、设于所述基板背面的接地底层、设于所述基板正面的信号线和分别位于所述信号线两侧的接地表层,各所述接地表层设于所述基板正面,所述信号线与各所述接地表层间隔设置,所述基板正面开设有容置槽,所述芯片安装于所述容置槽中,所述信号线延伸至所述容置槽的一端,所述金丝与所述芯片相连,所述信号线邻近所述芯片的一端与所述金丝之间级联用于与所述金丝进行阻抗匹配的阻抗变换枝节,所述阻抗变换枝节设于所述基板的正面,所述阻抗变换枝节位于两个所述接地表层之间,所述阻抗变换枝节包括与所述信号线相连的第一阻抗段、与所述金丝相连的第二阻抗段和连接所述第一阻抗段与所述第二阻抗段的第三阻抗段,所述第一阻抗段的阻抗大于所述第三阻抗段的阻抗,所述第三阻抗段的阻抗大于所述第二阻抗段的阻抗。

在一个实施例中,所述第一阻抗段的一端与所述信号线沿所述信号线宽度方向的中部相连,所述第一阻抗段的另一端与所述第三阻抗段一端沿所述信号线宽度方向的中部相连,所述第三阻抗段的另一端与所述第二阻抗段沿所述信号线宽度方向的中部相连;沿所述信号线长度方向:所述第一阻抗段的长度、所述第二阻抗段的长度和所述第三阻抗段的长度均相等;沿所述信号线宽度方向:所述第一阻抗段的宽度小于所述第三阻抗段的宽度,所述第三阻抗段的宽度小于所述第二阻抗段的宽度。

在一个实施例中,所述接地共面波导的特征阻抗为50Ω,所述阻抗变换枝节为金层;所述第一阻抗段沿所述信号线长度方向的长度为0.2mm,所述第一阻抗段沿所述信号线宽度方向的宽度为0.12mm;所述第三阻抗段沿所述信号线长度方向的长度为0.2mm,所述第三阻抗段沿所述信号线宽度方向的宽度为0.4mm;所述第二阻抗段沿所述信号线长度方向的长度为0.2mm,所述第二阻抗段沿所述信号线宽度方向的宽度为0.7mm。

在一个实施例中,所述信号线远离所述芯片的一端设有渐变段,所述渐变段沿所述信号线长度方向设置,所述渐变段的宽度由所述渐变段与所述信号线相连的一端至所述渐变段的另一端逐渐减小。

在一个实施例中,所述信号线及所述接地表层均为金层,所述信号线的宽度为0.38mm,所述信号线与各所述接地表层之间的间隙为0.4mm。

在一个实施例中,所述渐变段的长度范围为0.8mm-1.6mm,所述渐变段一端的宽度等于所述信号线的宽度,所述渐变段另一端的宽度范围为0.15mm-0.5mm。

在一个实施例中,所述渐变段呈等腰梯形结构。

在一个实施例中,所述阻抗变换枝节通过两根所述金丝与所述芯片相连,两根所述金丝沿所述信号线长度方向呈八字型排布,两根所述金丝靠近所述芯片一端的距离小于两根所述金丝靠近所述阻抗变换枝节一端的距离。

在一个实施例中,各所述金丝的跨距的范围为小于或等于300μm,各所述金丝的拱高的范围为100μm-200μm,两根所述金丝靠近所述芯片一端的距离的范围为小于或等于50μm,两根所述金丝靠近所述阻抗变换枝节一端的距离的范围为100μm-250μm。

在一个实施例中,所述信号线为两段,两段所述信号线分别位于所述容置槽的两端,各所述信号线邻近所述芯片的一端分别连接有所述阻抗变换枝节,两个所述阻抗变换枝节分别通过所述金丝与所述芯片的两端相连。

本申请提供的Ka波段接地共面波导金丝过渡结构的有益效果在于:与现有技术相比,本申请的Ka波段接地共面波导金丝过渡结构通过在信号线与金丝加入阻抗变换枝节,既可以良好的实现接地共面波导与金丝之间的阻抗匹配,有效解决因阻抗失配引起回波损耗和驻波比性能恶化的问题,又符合平面电路制作工艺要求,易于加工制作;而且,第二阻抗段、第三阻抗段和第一阻抗段的阻抗逐段增大,能够增加阻抗变换枝节的工作频带,以便在较宽的频带内具有良好的匹配性能。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1为本申请实施例提供的Ka波段接地共面波导金丝过渡结构的立体结构示意图;

图2为图1中A处的放大图;

图3为图1中B处的放大图;

图4为图1中芯片、金丝、阻抗变换枝节等的局部结构的俯视图;

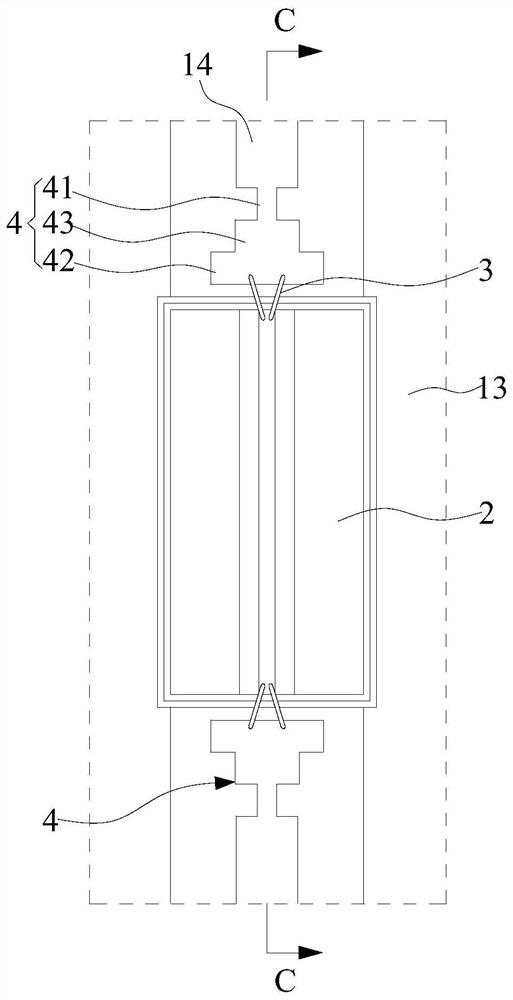

图5为图4中沿C-C的剖视图;

图6为接地共面波导的信号线通过金丝直接与芯片相连时的等效电路图。

图7为本申请实施例提供的Ka波段接地共面波导金丝过渡结构中一个阻抗变换枝节与相应金丝形成的等效电路图;

图8为本申请实施例提供的Ka波段接地共面波导金丝过渡结构的传输性能仿真的效果图。

其中,图中各附图标记:

1-接地共面波导;11-基板;111-容置槽;112-接地通孔;12-接地底层;13-接地表层;14-信号线;141-渐变段;

2-芯片;

3-金丝;

4-阻抗变换枝节;41-第一阻抗段;42-第二阻抗段;43-第三阻抗段。

具体实施方式

为了使本申请所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本申请进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本申请,并不用于限定本申请。

需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本申请的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

请参阅图1,为了方便描述,定义空间上相互垂直的三个坐标轴分别为X轴、Y轴和Z轴,其中,X轴为沿信号线的长度方向,Y轴为沿信号线的宽度方向,Z轴为沿信号线的厚度方向。

请参阅图1、图2和图5,现对本申请提供的Ka波段接地共面波导金丝过渡结构进行说明。Ka波段接地共面波导金丝过渡结构包括接地共面波导1、芯片2、金丝3和阻抗变换枝节4。接地共面波导1包括基板11、接地底层12、信号线14和两个接地表层13,接地底层12设于基板11背面,信号线14和两个接地表层13设于基板11正面,两个接地表层13分别位于的信号线14两侧,信号线14与各接地表层13间隔设置,从而形成接地共面波导1。基板11正面开设有容置槽111,信号线14延伸至容置槽111的一端,即容置槽111设于信号线14对应的位置,芯片2安装于容置槽111中,以方便安装芯片2,并且符合平面电路制作工艺要求,易于加工制作。金丝3与芯片2相连,阻抗变换枝节4设于基板11的正面,阻抗变换枝节4用于与金丝3进行阻抗匹配,并且阻抗变换枝节4连接信号线14邻近芯片2的一端与金丝3,即通过阻抗变换枝节4将信号线14与金丝3进行阻抗匹配相连,以有效解决因阻抗失配引起回波损耗和驻波比性能恶化的问题。这样既可以良好的实现接地共面波导1与金丝3之间的阻抗匹配,有效解决因阻抗失配引起回波损耗和驻波比性能恶化的问题,又符合平面电路制作工艺要求,易于加工制作。

进一步地,阻抗变换枝节4包括第一阻抗段41、第二阻抗段42和第三阻抗段43,第一阻抗段41与信号线14相连,第二阻抗段42与金丝3相连,第三阻抗段43连接第一阻抗段41与第二阻抗段42;第一阻抗段41的阻抗大于第三阻抗段43的阻抗,第三阻抗段43的阻抗大于第二阻抗段42的阻抗。这样使得第二阻抗段42、第三阻抗段43和第一阻抗段41的阻抗逐段增大,能够在Ka波段产生多个阻抗匹配性能良好的区间,以进一步提升Ka波段内多个区间内的阻抗匹配性能,能够增加阻抗变换枝节4的工作频带,以便在较宽的频带内具有良好的匹配性能。

在本申请的一个实施例中,请参阅图2、图4和图5,第一阻抗段41的一端与信号线14沿信号线14宽度方向的中部相连,第一阻抗段41的另一端与第三阻抗段43沿信号线14宽度方向的中部相连,第三阻抗段43的另一端与第二阻抗段42沿信号线14宽度方向的中部相连。这样形成了阻抗渐变的多段的阻抗变换枝节4,其阻抗特性可以等效于在金丝的等效电路中加入了L型阻抗匹配网络,较好地实现了阻抗匹配,以增加阻抗变换枝节4的工作频带。而且,这样有利于多个回波损耗较高的区间分布均匀。

可选地,请参阅图2、图4及图5,沿信号线14长度方向:第一阻抗段41的长度、第二阻抗段42的长度、第三阻抗段43的长度均相等。这样能够使得第一阻抗段41、第二阻抗段42、第三阻抗段43能够形成多节阻抗匹配,有利于提高阻抗匹配性能,并能够在Ka波段形成多个回波损耗较高的区间。沿信号线14宽度方向:第一阻抗段41的宽度小于第三阻抗段43的宽度,第三阻抗段43的宽度小于第二阻抗段42的宽度。这样使得第二阻抗段42、第三阻抗段43和第一阻抗段41的阻抗逐渐增大,在第二阻抗段42、第三阻抗段43和第一阻抗段41的阻抗大小能够呈梯度变化。这样方便设计过程中阻抗的计算,在调整特征阻抗时,可以通过各段宽度的调整提高设计效率,有利于简化设计。而且,第三阻抗段43的宽度介于第一阻抗段41和第二阻抗段42之间,使得第一阻抗段41和第三阻抗段43宽度的跨度渐变,有利于印刷工艺中控制图案形状,有利于提高阻抗变换枝节4的加工精度,有利于提高产品的一致性。

请参阅图6,图6所示的电路为使用金丝3直接将芯片2与信号线14连接时,金丝3的等效电路。该等效电路包括两个电感L1、两个电阻R1、两个电容C1和一个电容C2,其中电感L1、电阻R1、电阻R1和电感L1依次串联,且一个电感L1远离两个电阻R1的一端为用于连接芯片2的芯片端,另一个电感L1远离两个电阻R1的一端为用于连接信号线14的信号线端,即从芯片端到信号线端,电感L1、电阻R1、电阻R1和电感L1依次串联;并且芯片端通过一个电容C1接地,信号线端通过另一个电容C1接地,两个电阻R1之间通过电容C2接地。

请参阅图7,图7为使用上述实施例中阻抗变换枝节4连接金丝3与信号线14,阻抗变换枝节4与金丝3的等效电路,该等效电路包括两个电感L1、两个电阻R1、一个电感Lp、一个电容Cp1、一个电容Cp1、两个电容C1和一个电容C2,其中电感L1、电阻R1、电阻R1、电感L1和电感Lp依次串联,且远离电感Lp的一个电感L1的一端为用于连接芯片2的芯片端,电感Lp远离两个电阻R1的一端为用于连接信号线14的信号线端,即从芯片端到信号线端,电感L1、电阻R1、电阻R1、电感L1和电感Lp依次串联;并且芯片端通过一个电容C1接地,两个电阻R1之间通过电容C2接地,另一个电容C1与电容Cp1、电容Cp2并联,并且电感Lp远离信号线端的一端通过电容Cp1和电容Cp2接地。则电感Lp与相互并联的电容Cp1和电容Cp2可以形成L型阻抗匹配网络,即该使用阻抗变换枝节4的等效电路相当于在直接使用金丝3连接信号线14的等效电路的信号线端加入L型阻抗匹配网络,使从信号线端向芯片端观察到的输入阻抗Zin与信号线阻抗尽可能地接近,从而降低阻抗失配程度;且由于同时存在电容Cp1和电容Cp2,能够形成多个回波损耗较高的区间,增大阻抗变换枝节4的工作频带。其中,电容Cp1、电容Cp2和Lp分别对应第二阻抗段42、第三阻抗段43和第一阻抗段41的寄生效应。当然,电感Lp、电容Cp和电容Cp2的大小可以通过改变第一阻抗段41、第二阻抗段42和第三阻抗段43的尺寸调节,使得该阻抗变换枝节4具有可移植性,以适用于其它尺寸/形状的金丝或不同材料基板的接地共面波导。

在一个实施例中,请参阅图1、图4及图5,接地共面波导1的特征阻抗为50Ω,阻抗变换枝节4为金层;第一阻抗段41沿信号线14长度方向的长度为0.2mm,第一阻抗段41沿信号线14宽度方向的宽度为0.12mm;第三阻抗段43沿信号线14长度方向的长度为0.2mm,第三阻抗段43沿信号线14宽度方向的宽度为0.4mm;第二阻抗段42沿信号线14长度方向的长度为0.2mm,第二阻抗段42沿信号线14宽度方向的宽度为0.7mm,该结构的阻抗变换枝节4,可以良好的实现金丝3与50Ω特征阻抗的接地共面波导1之间在Ka波段的阻抗匹配,保证良好的链路传输性能。在实际加工过程中,阻抗变换枝节4的长度和宽度加工误差可以是±0.03mm,上述尺寸有利于减小加工精度误差带来的影响。

在本申请的一个实施例中,请参阅图1及图3,信号线14远离芯片2的一端设有渐变段141,渐变段141沿信号线14长度方向设置,渐变段141的宽度由渐变段141与信号线14相连的一端至渐变段141远离信号线14的一端逐渐减小。渐变段141在实际应用中与同轴接头内导体焊接,在信号线与同轴接头连接时,同轴接头内的导体焊接在渐变段上,这样能够加大输入/输出电感,用于抵消信号线与同轴接头内导体连接引入的寄生电容效应。

在一个实施例中,请参阅图1至图3,信号线14及接地表层13均为金层,信号线14的宽度为0.38mm,信号线14与各接地表层13之间的间隙为0.4mm,以使该接地共面波导1具有良好的传输性能,并且使该接地共面波导1具有50Ω特征阻抗,提升该接地共面波导1的适用范围。

在一个实施例中,请参阅图3和图4,金层的厚度范围为10-20μm,即上述阻抗变换枝节4使用金材料制作,阻抗变换枝节4的厚度范围为10-20μm,信号线14及接地表层13使用金材料制作,信号线14及接地表层13的厚度范围为10-20μm,以保证该接地共面波导1具有良好的传输性能,并使阻抗变换枝节4良好的实现金丝3与信号线14间的阻抗匹配。可选地,各金层的厚度可以为12μm、15μm或17μm等,可根据接地共面波导1和阻抗变换枝节4的传输性能和阻抗匹配特性进行选择。

在一个实施例中,请参阅图1及图3,渐变段141沿信号线14长度方向的长度范围为0.8mm-1.6mm,渐变段141靠近芯片2一端的宽度与信号线14的宽度相等,渐变段141远离芯片2一端的宽度范围为0.1mm-0.5mm。这样一方面方便渐变段141与信号线14的加工,便于同轴接头内导体的焊接,能够保障焊接部位的稳定,另一方面能够较好的抵消寄生电容效应的影响。可选地,渐变段141的长度可以为0.6mm、0.8mm或1mm等,渐变段141远离芯片2一端的宽度可以为0.2mm、0.3mm或0.4mm等。当然,渐变段141的长度和渐变段141另一端的宽度可以根据与同轴接头的匹配效果进行调节。

可选地,请参阅图1及图3,渐变段141呈等腰梯形结构。这样能够方便焊接同轴接头时导体的对位,且形状简单,加工较为方便。

在一个实施例中,请参阅图5,阻抗变换枝节4、信号线14及接地表层13的厚度相等,以方便加工制作,如可以印刷制作于基板11上。

在一个实施例中,请参阅图2、图4及图5,阻抗变换枝节4通过两根金丝3与芯片2相连,两根金丝3沿信号线14长度方向呈八字型排布,两根金丝3靠近芯片2一端的距离小于两根金丝3靠近阻抗变换枝节4一端的距离。使用两根金丝3连接阻抗变换枝节4与芯片2,使两根金丝3更好的形成对称结构,降低阻抗,提升传输性能。

在一个实施例中,请参阅图图2、图4及图5,各金丝3的跨距的范围为小于或等于300μm,各金丝3的拱高的范围为100μm-200μm,两根金丝3靠近芯片2一端的距离的范围为小于或等于50μm,两根金丝3靠近阻抗变换枝节4一端的距离的范围为100μm-250μm,以使金丝3具有更小的电阻与电感特性,即减小金丝3的阻抗,提升金丝3的传输性能,并良好的与阻抗变换枝节4匹配,同时也方便加工制作。

在一些实施例中,各金丝3的跨距为260μm,各金丝3的拱高为150μm,两根金丝3靠近芯片2一端的距离为25μm,两根金丝3靠近阻抗变换枝节4一端的距离为175μm,以使金丝3具有更小的电阻与电感特性,即减小金丝3的阻抗,提升金丝3的传输性能,以更好的保证金丝3良好的连接阻抗变换枝节4与芯片2,并且使金丝3更好的阻抗变换枝节4匹配。

在一个实施例中,请参阅图1、图4和图5,阻抗变换枝节4关于信号线14长度方向的中线对称设置,接地共面波导1关于信号线14长度方向的中线对称设置,两根金丝3关于信号线14长度方向的中线对称设置,从而使该接地共面波导1、金丝3及阻抗变换枝节4形成对称结构,方便加工制作,且保证Ka波段接地共面波导金丝过渡结构良好的传输性能和较低的回波损耗。当然,在一些实施例中,若基板11或芯片2本身为非对称结构,只需要将信号线14、阻抗变换枝节4和金丝3位置做相应调整,也可以实现金丝3与信号线14间良好的阻抗匹配,保证良好的传输性。

在一个实施例中,请参阅图1、图2和图5,信号线14为两段,两段信号线14分别位于容置槽111的两端,各信号线14邻近芯片2的一端分别连接有阻抗变换枝节4,两个阻抗变换枝节4分别通过金丝3与芯片2的两端相连,即方便安装芯片2,又可以实现芯片2的两端与两根信号线14的匹配连接。在其它一些实施例中,当芯片2仅需要一端与信号线14相连时,容置槽111可以设在基板11的一端,从而将芯片2安装在基板11的边缘。

在一个实施例中,请参阅图1和图2,当信号线14为两段时,两段信号线14的长度相等,容置槽111位于基板11的中部位置,从在使接地共面波导1关于基板11长度方向的中线对称设置,以方便设计制作,并保证接地共面波导1良好的传输性能。

在一个实施例中,请参阅图1和图2,基板11上于信号线14的两侧分别设有至少两排接地通孔112,各接地通孔112连接相应接地表层13与接地底层12,以提升该接地共面波导1的传输性,提升传输效率,降低损耗。

在一个实施例中,请参阅图1和图2,信号线14各侧邻近该信号线14的两排接地通孔112中:各排接地通孔112中相邻两个接地通孔112之间的距离范围为0.5-1.1mm;该两排接地通孔112之间的距离范围为0.5mm-1.5mm,相邻两排接地通孔112沿信号线14长度方向错位设置,沿信号线14长度方向的错位距离的范围为0.3-0.7mm,以更好的提升该接地共面波导1的传输效率,降低损耗。沿信号线14长度方向:各接地通孔112到基板11边缘的距离大于或等于0.3mm。

在一个实施例中,各接地通孔112的孔径范围为0.1mm-0.3mm,以方便加工制作。在一个实施例中,各接地通孔112的孔径为0.2mm,即方便制作,又可以提升该接地共面波导1的传输效率,使提升该接地共面波导1的传输效率与制作工艺简单性达到平衡。

在一个实施例中,信号线14各侧邻近该信号线14的两排接地通孔112中:任意相邻三个接地通孔112之轴线之间的连线呈等腰三角形,以更好的防止电磁泄露,提升该接地共面波导1的传输效率。可选地,信号线14各侧邻近该信号线14的两排接地通孔112中:任意相邻三个接地通孔112之轴线之间的连线呈等边三角形,即方便设计制作,又可以提升该接地共面波导1的传输效率。

在一个实施例中,信号线14各侧邻近该信号线14的两排接地通孔112中:各排接地通孔112中相邻两个接地通孔112之间的距离范围为0.7mm-1.2mm,以方便加工制作。

在一个实施例中,请参阅图4,阻抗变换枝节4与各接地表层13之间的间隙大于或等于0.225mm,以满足大多数平面电路加工工艺的要求,方便加工制作,降低成本。阻抗变换枝节4与各接地表层13之间的间隙可以为0.25mm、0.28mm或0.35mm等。

在一个实施例中,请参阅图1和图5,基板11的介电常数范围为5.0~10.0,基板11的介质损耗因子tanα≤0.004,以保证该接地共面波导1良好的传输性能。基板11可以使用陶瓷材料,以便该接地共面波导1可以进行低温共烧陶瓷工艺制作。当然,基板11也可以使用其他材料制作。

在一个实施例中,基板11呈矩形,信号线14沿基板11的长度方向设置,则基板11的长度方向为信号线14的长度方向,即为X轴方向;基板11的宽度方向为信号线14的宽度方向,即Y轴方向;基板11的厚度方向为信号线14的厚度方向,即Z轴方向。该结构可以更好的将接地共面波导1制作为对称结构,提升传输性能,降低传输损耗。

在一个实施例中,基板11的长度为25.4mm,基板11的宽度为12.7mm,基板11的厚度为0.31mm,以使该Ka波段接地共面波导金丝过渡结构体积尺寸较小,方便使用。

在一个实施例中,请参阅图5,容置槽111的内壁与芯片2侧面之间的距离范围为60-100μm,以方便将芯片2安装在容置槽111中。在一个实施例中容置槽111的内壁与芯片2侧面之间的距离为80μm,既方便将芯片2安装在容置槽111中,也便于固定芯片2。

在一个实施例中,芯片2正面与接地共面波导1的正面持平,可以更好的满足平面电路加工工艺要求,提升制作精确。

在一些实施例中,可以将芯片2的底面通过金属垫片与接地底层12接地相连,以减小传输损耗。

请参阅图8,本申请实施例提供的Ka波段接地共面波导金丝过渡结构的传输性能仿真的效果图,其中使用50Ω特征阻抗的背敷金属共面波导替代芯片2进行电磁仿真。图中横座标轴Freq为频率,单位为GHz;左侧的纵座标轴Insertion/Return Loss为插入/回波损耗,单位dB。Curve Info曲线信息,其中,线S(1,1)为各频率对应回波损耗的曲线,线S(1,1)上高点m1处的频率为37.33GHz,回波损耗为-21.7177dB;线S(2,1)为各频率对应插入损耗的曲线,线S(2,1)上低点m2处的频率为40GHz,插入损耗为-1.3599dB。由图可知,本申请实施例的Ka波段接地共面波导金丝过渡结构,在Ka波段内的传输性能优异,插入损耗小于1.4dB,回波损耗大于21.0dB,且在Ka波段内存在多个回波损耗值较大的区间(存在四个回波损耗大于40dB的区间,四个区间的频带分别大致对应30.3GHz、33.7GHz、35.7GHz和39.1GHz),多个区间的分布在Ka波段的分布也相对均匀,明显增加了阻抗变换枝节4的工作频带,在较宽的频带内具有良好的匹配性能。

本申请实施例的Ka波段接地共面波导金丝过渡结构,可以采用LTCC(LowTemperature Co-fired Ceramic,低温共烧陶瓷,简称LTCC)工艺,或其它平面印刷工艺进行制作,例如可以在生瓷片对应位置掏出空腔,从下往上进行堆叠并印制各层金属图案和填孔;再烧结成型,当然,还可以对基板11进行电镀与清洗,再依次采用贴片工艺安装芯片2、金丝3键合。

本申请实施例的Ka波段接地共面波导金丝过渡结构,可以应用于Ka波段收发组件中,也可以应用在微波通信、雷达系统、电子对抗等设备中。

以上所述仅为本申请的较佳实施例而已,并不用以限制本申请,凡在本申请的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本申请的保护范围之内。

- Ka波段接地共面波导金丝过渡结构

- Ka波段接地共面波导金丝过渡结构