具有紧凑无源部件布置的电路板

文献发布时间:2023-06-19 11:55:48

发明背景

所有集成电路都需要电力才能运行,并且封装集成电路也不例外。电力通常经由电源和某种形式的电力输送网络输送到集成电路。尽管当前可用的电源被设计为提供稳定的电压,但是输送到集成电路的实际电力可能含有大量噪声。噪声的来源很多,例如由耦合到电源的其他装置引起的电压波动、电磁干扰和其他原因。

常规的封装集成电路通常包括安装在承载衬底上的半导体芯片。承载衬底被配置成安装到例如主板或卡的印刷电路板上。典型的常规承载衬底包括互连系统,所述互连系统由多个通孔垂直连接的多层导体平面或迹线构成。承载衬底的管芯侧上的输入/输出焊盘连接到管芯,并且承载衬底的下侧上的输入/输出焊盘连接到印刷电路板。球状栅格阵列、岸面栅格阵列或针脚栅格阵列用于将下侧输入/输出焊盘电连接至印刷电路板。

为了解决与电源噪声相关的问题,常规的半导体芯片封装使用去耦电容器。这些去耦电容器中的许多都安装到承载衬底上。在一种常规变型中,去耦电容器围绕管芯的周边安装到承载衬底的管芯侧。在另一个常规变体中,去耦电容器安装到承载衬底的下侧。

附图说明

通过阅读以下详细说明并参考附图,本发明的前述和其他优点将变得显而易见,在附图中:

图1是示例性常规半导体芯片封装的部分分解示图;

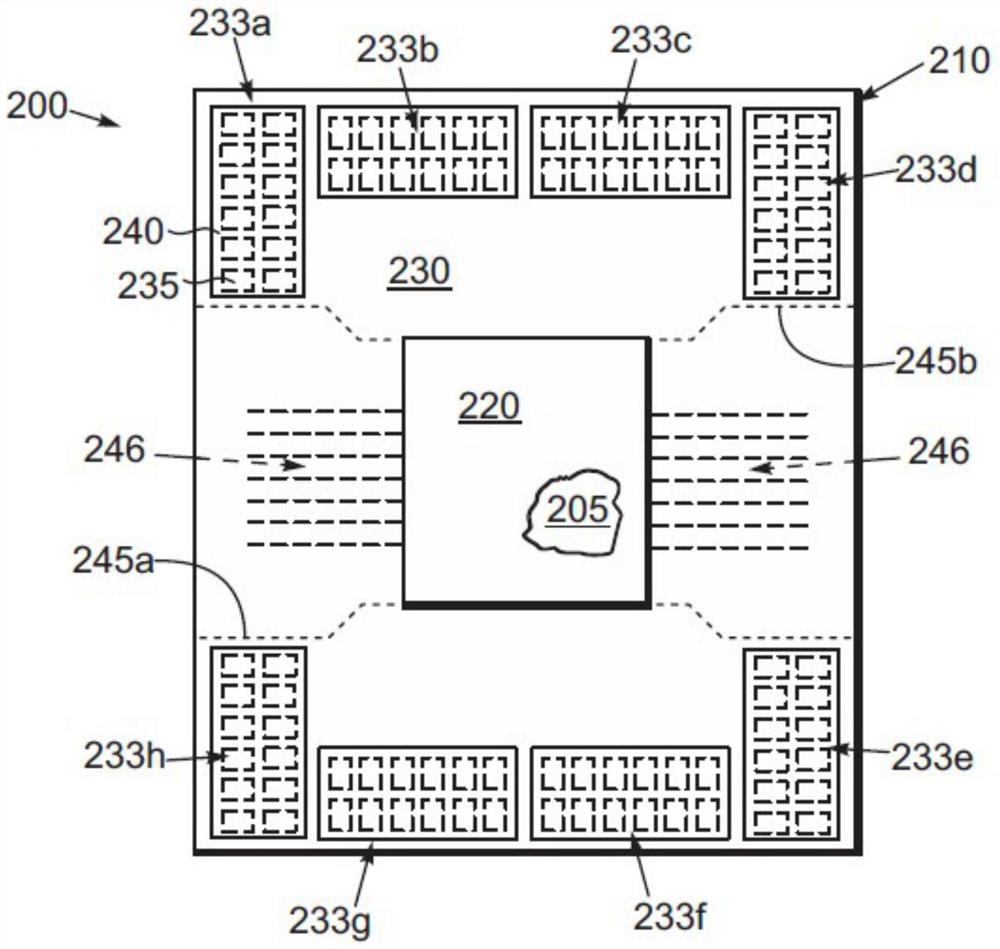

图2是示例性半导体芯片封装衬底的平面图;

图3是以更大放大率示出的图2的一部分;

图4是以更大放大率示出的图2的一部分;

图5是具有示例性模制无源部件组的示例性半导体封装布置的平面图;

图6是以更大放大率示出的图5的一部分;

图7是在截面7-7处截取的图6的截面图;

图8是模制的一部分被切除的图6中描绘的部分;

图9是具有示例性模制无源部件组的替代性示例性半导体封装布置的平面图;

图10是具有示例性模制无源部件组的替代性示例性半导体封装布置的平面图;

图11是描绘承载衬底上的无源部件组的示例性布置的截面图;

图12是类似于图11但描绘至少部分地包封无源部件的示例性模制的截面图;

图13是类似于图12但描绘移除承载衬底的截面图;

图14是类似于图13但描绘模制无源部件组的示例性分割的截面图;

图15是描绘模制无源部件组在电路板上的示例性安装的截面图;并且

图16是替代示例性模制无源部件组的平面图。

具体实施方式

去耦电容器通常一次一个地安装到半导体芯片封装衬底的表面上。每个电容器的电极均与封装衬底的下层焊料结构垂直对齐。执行回流以暂时液化焊料结构。冷却使焊料结构固化,并在电容器与封装衬底之间形成电连接和机械连接。安装过程涉及拾取和放置操作。拾取和放置操作中的缺陷和/或焊料结构的大小、高度和位置的变化可能会导致电容器在回流期间摆动、旋转或以其他方式移动。如果移动过大,则一个电容器可能会对另一个电容器短路。为了避免这种缺陷,常规的电容器安装技术遵循拾取和放置电容器的最小间距的设计规则。这严重限制了封装衬底的设计和大小。许多封装衬底利用存储器接口区域,其中大量紧密间隔的导体迹线从芯片安装区域散开。由于常规放置的电容器的封装限制,这种存储器接口区域通常具有叠置的电容器,这使得布线导体迹线的任务变得困难。

公开的布置利用模制无源部件组。模制无源部件组可以以更紧密的最小间距模制在一起。因此,对于相同大小的封装衬底,更多的无源部件可以安装和/或安装在存储器接口区域之外,或者以使得可以安装比常规可能更多的芯片的这样的方式安装。

根据本发明的一个方面,提供一种制造方法,所述方法包括将第一多个电容器至少部分地包封在模制材料中,以产生第一模制无源部件组。所述第一模制无源部件组安装在电路板的表面上。所述第一多个电容器电连接到所述电路板。

根据本发明的另一个方面,提供一种制造方法,所述方法包括通过将多组电容器至少部分地包封在模制材料中并将所述模制无源部件组分割来制造多个模制无源部件。所述模制无源部件组安装在半导体芯片封装衬底的表面上。所述电容器电连接到所述半导体芯片封装衬底。

根据本发明的另一方面,提供一种设备,所述设备包括:电路板,所述电路板具有表面;以及至少一个模制无源部件组,所述至少一个模制无源部件组安装在所述电路板的表面上并且电连接到所述电路板。所述至少一个模制无源部件组包括第一多个电容器,每个电容器具有上表面和连接在一起并覆盖所述第一多个电容器的所述上表面的模制材料。

在以下所述的附图中,通常在多于一个附图中出现相同的元件的地方重复附图标记。现在转向附图,特别是图1,其中描绘示例性常规半导体芯片封装100的部分分解示图,所述常规半导体芯片封装包括安装在封装衬底110上的半导体芯片105。盖115安装在封装衬底110上以用作散热器,并且通过热接口材料120与半导体芯片105热接触。在此说明性常规布置中,封装衬底110是针脚栅格阵列封装,其包括被设计为插入到针脚栅格阵列插座(未示出)中的多个导体针125。封装衬底120的上表面130上填充有多个表面部件135,在此常规布置中,所述表面部件通常是电容器。现在还可以通过参考图2来理解常规半导体芯片封装100的附加细节,该图是没有图1所示出的盖115的封装衬底110的平面图。热接口材料的一部分被切掉以显露下伏半导体芯片105。在拾取和放置操作中,常规电容器135作为单个物体安装在封装衬底110的上表面130上。在此说明性布置中,围绕半导体芯片105的周边设置有六个电容器组140a、140b、140c、140d、140e和140f。封装衬底110包括大量的导体迹线,这些导体迹线在整个封装衬底110上散开,但是在图2中未示出。这些不可见的导体迹线中的许多定位于封装衬底110的存储器接口区域145a和145b(虚线之间的区域)中。为了处理半导体芯片105与外部存储器装置(未示出)之间的大量信号路径,在存储器接口区域145a和145b中通常存在更多数量和更高密度的导体迹线。由于与安装常规电容器135相关联的大小和工艺限制,因此,例如电容器组140b、140c、140e和140f中的一些电容器135定位于存储器接口区域145a和145b的上方。这限制布线和放置底层导体迹线的能力。

现在还可以通过参考图3来理解常规封装衬底110和放置在其上的电容器135的附加细节,该图是电容器组140f位于其上的封装衬底110的一部分。如上所述,电容器135单独地放置在封装衬底110的上表面130上。典型的常规电容器135具有一些长度a和宽度b。在一种常规布置中,a为1.6mm并且b为0.8mm。由于放置电容器135的常规工艺中的限制,设计规则要求单个电容器135之间的沿x轴的最小间距x

A

将值a=1.6mm、b=0.8mm、x

图4描绘两个电容器135的平面图。电容器135中的每一者安装在常规封装衬底110的四个焊料焊盘155上,其位于每个电容器135的拐角附近。在拾取和放置操作期间,将每个电容器135安装在焊料焊盘155上方,并且执行回流工艺以便暂时液化焊料焊盘155,从而与电容器135建立冶金结合。由于电容器135在此回流阶段期间旋转不对准的可能性以及电容器135相对于下伏焊料焊盘155的垂直放置精度的缺陷,常规的设计规则要求上述最小间距x

图5中描绘半导体芯片装置200的示例性新布置,所述图是描绘安装在电路板210上的半导体芯片205的平面图,所述电路板可以是半导体芯片封装衬底、电路卡、系统板等。电路板210可以是有机堆积设计、多层预浸料设计、陶瓷或其他设计。可以将先前图中描绘的类型的热接口材料220放置在半导体芯片205上,并且实际上示出部分地切除以露出下伏半导体芯片205。图1所描绘类型的盖(未示出)或其他类型的盖也可用于将热从半导体芯片205传送出去。为了减轻与图1、图2、图3和图4所描绘的电容器135的常规布置相关联的技术问题,电路板210的上表面230填充有多个模制无源部件组233a、233b、233c、233d、233e、233f、233g和233h。模制无源部件组233a、233b、233c、233d、233e、233f、233g和233h中的每一者由在模制材料240内部模制的多个无源部件235(示出为虚线框)组成。在此说明性布置和所公开的替代布置中的无源部件235可以是电容器、电感器或电阻器。如以下更详细描述的,无源部件235以在给定的无源部件组233a、233b等中的无源部件235之间提供非常紧密间距的过程中被模制在模制材料240的内部。实际上,尽管常规布置需要0.8mm的最小间距x,但是所公开的新布置将无源部件235之间的最小间距减小到0.1mm或者甚至更小。这使得对于组233a、233b、233c、233d、233e、233f、233g和233h中的每一者的无源部件235具有更大的封装密度,从而为给定大小的电路板210,提供比常规更多的无源部件235,并且还使得无源部件组233a、233b、233c、233d、233e、233f、233g和233h能够定位于电路板210的存储器接口区域245a和245b的外部,这使得电路板210中下伏导体迹线246(以虚线示出)的数量和布置具有更大的灵活性。

现在通过参考图6至图7,可以理解无源部件组233a的附加细节。图6是与图5相比以更大放大率示出的无源部件组233a和电路板210的上表面230的平面图。图7是在截面7-7处截取的图6的截面图。无源部件组233a的以下描述将说明其他无源部件组233b、233c、233d、233e、233f、233g和233h。首先转向图6,并且如上所述,无源部件组233a由至少部分地嵌入或包封在模制材料240内的多个无源部件235组成,所述模制材料示出为被部分切除以显露几个无源部件235。无源部件235中的每一者包括中心绝缘涂层247以及端电极249a和249b。在此,无源部件组233a包括十二个无源部件235。然而,本领域技术人员将理解,实际上可以在模制材料240内将任何数量(例如两个或更多)聚集在一起。

现在将注意力转向如上所述的图7是在截面7-7处截取的图6的截面图。注意,由于截面7-7的位置,在所述截面中示出两个无源部件235以及一部分模制材料240。左侧无源部件235包括上述绝缘涂层247和电极249a和249b,所述电极与下伏焊料焊盘257a和257b欧姆接触。右侧无源部件235类似地具有绝缘中心区247和电极249a和249b,所述电极连接到相应的下伏焊料焊盘257a和257b。无源部件235实际上可以是任何电容器设计,例如多极板、单极板等,或者实际上是电阻器或电感器设计。焊料焊盘257a和257b通过形成在下伏电路板210上的焊料掩模252中的开口向下突出。焊料焊盘257a和257b连接到相应的下伏金属化焊盘258a和258b。应理解,用于无源部件235中的每一者的下伏焊料焊盘257a和257b的数量可以多于两个,并且实际上类似于图4所描绘的焊料焊盘155。可选地,可以使用其他数字,例如二或除四之外的数字。如上所述,模制材料240至少部分地包封无源部件235,并且与无源部件235一起产生上述模制无源部件组233a。期望模制件240覆盖无源部件235的上表面260,以保护无源部件235免受可能损坏或以其他方式使无源部件235电短路的材料(例如焊料热接口材料)的影响。然而,模制材料240被模制或以其他方式处理以暴露无源部件235中的每一者的电极249a和249b,从而可以与焊料焊盘257a和257b形成冶金结合。还应理解,模制无源部件组233a、233b、233c、233d、233e、233f、233g和233h(或任何公开的替代物)中的任一者或所有可以安装在电路板210的表面230上或电路板210的相对表面259上或任何公开的替代物上。这里,电路板210是具有多个岸面261的岸面栅格阵列设计。替代布置可以使用针脚栅格阵列、球状栅格阵列、其他I/O或不使用I/O。

现在将结合图8描述关于模制无源部件组233a的几何形状的附加细节,该图是类似于图3的但清楚地示出现在要描述的一些重要差异的常规电容器组140f的平面图。无源部件235可具有与先前附图中所描绘且如上所述的电容器135相同的长度a

A

通过用x

由模制件240的外部边界区域270占据的面积可以包括在由模制无源部件组233a占据的总面积中。边界区域270的该面积A

A

其中d是用于分割模制无源组的切割刀片的切缝宽度。典型值d为0.040mm至0.050mm。预计边界270的宽度t(并且由t=2(x

通过利用具有伴随较小覆盖区的模制无源部件组,可以实现多种益处。例如,图9是半导体芯片装置300的替代示例性布置的平面图,所述半导体芯片装置包括安装在电路板310上并且尤其是其上表面330上的多个半导体芯片305a、305b和305c。电路板310可被配置成类似于本文其他地方公开的电路板210。在此,八个模制无源部件组333a、333b、333c、333d、333e、333f、333g和333h安装在电路板310的上表面330上。但是,由于无源部件组333a按比例比常规设计(例如上面描绘的电容器组140f)所允许的小得多,因此电路板310的附加表面面积可用于放置大小相似的不是一个而是三个半导体芯片305a、305b和305c,而不必将无源部件组333a、333b、333c、333d、333e、333f、333g和333h中的任何一者放置在存储器接口区域345a和345b的范围内。换句话说,在电路板310的覆盖区与封装衬底110的常规设计大致相同的情况下,组333a、333b、333c、333d、333e、333f、333g和333h中的更多无源部件335可以定位于电路板310上,同时容纳更多和/或更大的半导体芯片,而不必限制存储器接口区域345a和345b中迹线的布线。

在又一替代示例性布置中,在图10的平面图中描绘的半导体芯片封装400可以包括安装在电路板410(并且尤其是安装在其上表面430)上的半导体芯片405a、405b、405c、405d和405e。电路板410可被配置成类似于本文其他地方公开的电路板210和310。因此,多个模制无源部件组433a、433b、433c和433d安装在芯片405a、405b、405c、405d和405e任一侧的上表面430上。然而,由于无源部件组433a、433b、433c和433d是使用以下将要描述的技术制造的,因此电路板410的上表面430的分别靠近安装芯片405d和405e的部分被释放用于芯片放置,而不是表面部件放置。因此,无源部件组433a、433b、433c和433d的某些部分可以定位于存储接口区域345a和345b上方,但是这种空间布置可以通过将以芯片405d和405e的形式的附加半导体添加在电路板410上的能力来补偿。

现在参考图11、图12、图13、图14和图15,并首先参考图11,可以理解用于制造公开布置中的任一者的模制无源部件组的示例性方法。最初,无源部件235的一个组507和无源元部件235的一个或多个其他组509可移除地安装在承载衬底511上。这可以通过使用定位于承载衬底511上的所描绘的承载带513或通过其他能够移除的技术(例如光或热激活的粘合剂)等来完成。所述处理可以基于晶片规模来执行,因此可以存在数十个或更多个无源部件组507、509等。承载衬底511可以是承载晶片或由玻璃、硅或其他材料组成的其他工件。组507的无源部件235可以是例如图5所描绘的最终模制无源部件组233a的无源部件235,且无源部件组509的无源部件235例如可以是例如亦如图5所描绘的最终模制无源部件组233h的无源部件235。组507的无源组件235以最小间距x

接下来,如图13所示出,移除承载衬底511和承载带513,以留下模制无源部件组233a和233h的重构组合532,其分别由无源部件组507和509的无源部件235组成,至少部分地被模制件522包住。如果模制件522中的任一者覆盖无源部件235的电极249a和249b的下侧,则应在此阶段执行合适的研磨或其他材料去除工艺以确保在衬底安装期间焊料将容易润湿至电极。在这一点上,如图14所示,期望通过合适的切割锯542切割模制件522或通过其他技术,将模制无源部件组233a与模制无源部件组233h分割。切割锯542将具有一些切口d,其至少部分地确定图8所描绘并在上面讨论的模制边界270的厚度t。在分割之后,模制无源部件组,例如,包括图15中所示出的无源部件235和模制件240的无源部件组233a可以安装在电路板210的下伏焊料焊盘257a和257b上,以与模制无源部件组233a的无源部件235建立必要的冶金连接等,用于其他无源部件组233b、233c、233d、233e、233f、233g和233h(见图5)。接下来,可执行合适的回流以便暂时液化焊料互连焊盘257a和257b,然后冷却以产生与电路板210的冶金结合。

如上所述,模制无源部件组可以是对称的或不对称的。图16是类似于图8的但描绘包括模制材料540中的无源部件535的模制无源部件组533a的替代示例性布置的平面图。示出各种不对称性。例如,左侧列包括六个无源部件535,而右侧列仅包括两个无源部件535。左上侧的无源部件具有一些尺寸a和b,而下一个较低的无源部件535具有较小的覆盖区。最低的左侧无源部件535相对于其他无源部件535旋转。这些仅代表一些可能的变化。

尽管本发明可能容易受到各种修改和替代形式的影响,但是在附图中通过示例的方式示出具体的实施方案,并且在此对其进行详细描述。然而,应理解,本发明不旨在限于所公开的特定形式。而是,本发明将涵盖落入由所附权利要求书所界定的本发明的精神和范围内的所有修改、等同物和替代物。

- 具有紧凑无源部件布置的电路板

- 用于将电子部件集成到印刷电路板中的方法以及具有在其中集成的电子部件的印刷电路板