一种FLASH芯片存储区及其高性能防掉电读写方法

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及芯片防掉电领域,尤其涉及一种FLASH芯片存储区及其高性能防掉电读写方法。

背景技术

对于FLASH芯片存储区而言,因设计和工艺的不同,擦写和读取数据存在或多或少的差异。然而,存储区都以页面为单位,允许编程擦写,擦写页面需要将页面中的所有数据擦除,然后再写入新的数据,如果此过程中失电,可能会丢失原有数据,芯片无法保证存储区数据的完整性和有效性,因此,现有技术中设计失电保护的机制,保证擦写数据时原有数据不丢失,或者新数据能被完整有效写入页面。

现有技术中失电保护机制分为两种方案,其一是备份原有旧数据,在擦写页面失败时,能将页面原有数据恢复,另一个方案则是备份新数据,即将要写入的新数据在写入第一数据区前,写入一个备份页面,擦写事务操作记录成功提交后,再将备份页面的数据写入用户数据页面,这个过程中,擦写操作事务提交前失电,用户数据页面依旧为原有旧数据,擦写操作事务提交后失电,每次芯片上电都可以通过查询擦写事务,将备份页面数据写入用户数据页面。上述两种方案都可以保证擦写FLASH页面数据不因失电而丢失,只是擦写事务操作记录成功提交的时机有差别,完成擦写页面的效率不同,且各有优缺点:

第一类失电保护机制,需要完成备份旧数据、提交擦写事务操作记录、将新数据写入用户数据页面后,才能读取新数据,擦写效率低,读取数据效率高。

第二类失电保护机制,只需要完成新数据写入备份页面后就可以读取新数据,不需要完成擦写事务操作记录成功提交,然而,读取数据需要查询擦写事务操作记录,需要确保新数据已经写入备份页面,然后再从备份页面读取新数据,擦写效率较备份旧数据高,然而读取数据效率相对较低。

以一个页面擦写耗时3ms为例,完成擦写N个页面,对于备份旧数据方案而言,需要擦写(2*N+N)个页面,耗时((2*N+N)*3)ms。对于备份新数据方案而言,则需要擦写(2*N+1)个页面,耗时((2*N+1)*3)ms时间,该耗时是没有失电保护只擦写用户页面的2倍以上。

然而在现有业务中为了满足用户良好体验需求,往往要求芯片高效率执行,如现金业务要求500ms完成交易,钱包交易在300ms以内,从优化性能的角度分析,耗时较大的是擦写FLASH页面,擦写越多,效率越低。现有的两类失电保护机制在效率上均不能满足现有业务的需求,因此急需一种能够提高FLASH芯片擦写高性能的防掉电保护方法。

发明内容

本发明提供了一种FLASH芯片存储区,包括第一数据区、第二数据区和擦写操作记录区;第一数据区用于存储用户数据,第二数据区用于存储被擦写页面的新数据,擦写操作记录区记录擦写FLASH页面擦写的记录,按页面擦写,轮换使用,不需要备份,并要求当前写入的擦写记录页面不能与在此之前写入的擦写记录页面相同;每个擦写记录单元在第二数据区或者第一数据区对应一个页面;

在擦写一个页面时,根据擦写操作记录区中擦写记录页面中的内容确定一个属于第一数据区或第二数据区的页面,然后将新的数据写入该页面;如果要擦写多个页面,则根据擦写记录页面中的内容确定多个页面,然后将新数据写入每个页面,并在完成擦写事务时将擦写记录写入擦写记录页面中。

如上所述的FLASH芯片存储区,其中,擦写操作记录区分配至少两个擦写记录页面,分别为有效记录页面和无效记录页面。

如上所述的FLASH芯片存储区,其中,擦除记录页面是以2个字节为单元的记录组成;首个两字节为记录信息,最后两个字节为所有有效记录的校验核,中间所有字节为擦写记录单元。

如上所述的FLASH芯片存储区,其中,首个两字节中,第一个字节记录擦写记录序号,最大值即为最新擦写序号,第二个字节记录擦写记录单元中有效记录的个数,包含处于事务中的擦写记录单元的个数。

如上所述的FLASH芯片存储区,其中,每个擦写记录单元中记录备份数据可用页面标识,根据备份数据可用页面标识的值确定页面属于第一数据区或第二数据区。

如上所述的FLASH芯片存储区,其中,当第二数据区中的页面被使用完或者现有业务中不要求性能的其他业务时,根据擦写记录单元编码将第二数据区中的用户数据写回到第一数据区中,并释放对应的擦写记录单元,用于后续擦写页面保护。

如上所述的FLASH芯片存储区,其中,在芯片上电时检查擦写记录单元,查找擦写记录单元中校验核正确,且擦写记录序号最大的擦写记录单元,并将该最大擦写记录单元作为有效擦写记录单元,用于后续有效数据的读取或擦写。

本申请还提供一种高性能防掉电擦写方法,应用于上述任一项所述的FLASH芯片存储区中,所述方法包括:

Step11、根据待写入数据的地址A,检查地址A内的数据是否在缓存中,如果是,则执行步骤Step14,否则执行步骤Step12;

Step12、判断在擦写记录页面中是否能够查找地址A对应的记录,如果是,则执行步骤Step13,否则在擦写记录页面中分配一个新的记录单元位置,将所述地址编码成记录单元后写入该记录单元位置内,然后执行步骤Step13;

Step13、根据缓存地址在擦写页面记录表中查找对应的擦写记录单元,根据擦写记录单元解码出地址B,将缓存中的数据写入该地址B,将地址A编码成擦写记录单元后写入擦写页面记录表中;

Step14、将要写入地址A的待写入数据写入缓存中,继续判断是否有新数据需要进行写操作,如果是,则返回执行Step11,否则将擦写页面记录表写入擦写记录页面中,数据擦写结束。

本申请还提供一种芯片存储区页面数据读取方法,应用于上述任一项所述的FLASH芯片存储区中,所述方法包括:

Step21、根据待读取地址C,检查地址C的数据是否已被缓存,如果是,则从缓存中读取数据,执行步骤Step24,否则执行步骤Step22;

Step22、在擦写页面记录表中查找地址C是否已被记录,如果没有被记录,则执行Step23,如果被记录,则从擦写记录单元中解码得到地址C的数据所在页面地址D,从地址D读取数据,执行Step24;

Step23、从地址C直接读取数据;

Step24、检查是否需要继续读取其他页面数据,如果是,则返回执行Step21,否则数据读取结束。

本申请还提供计算机可读存储介质,其特征在于,包括至少一个存储器和至少一个处理器;

存储器用于存储一个或多个程序指令;

处理器,用于运行一个或多个程序指令,用以执行高性能防掉电擦写方法和高性能防掉电读取方法。

本发明实现的有益效果如下:采用本申请技术方案,实现一种高效擦写防护机制,既能保护原有页面数据,也能高效写入新的数据。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明中记载的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。

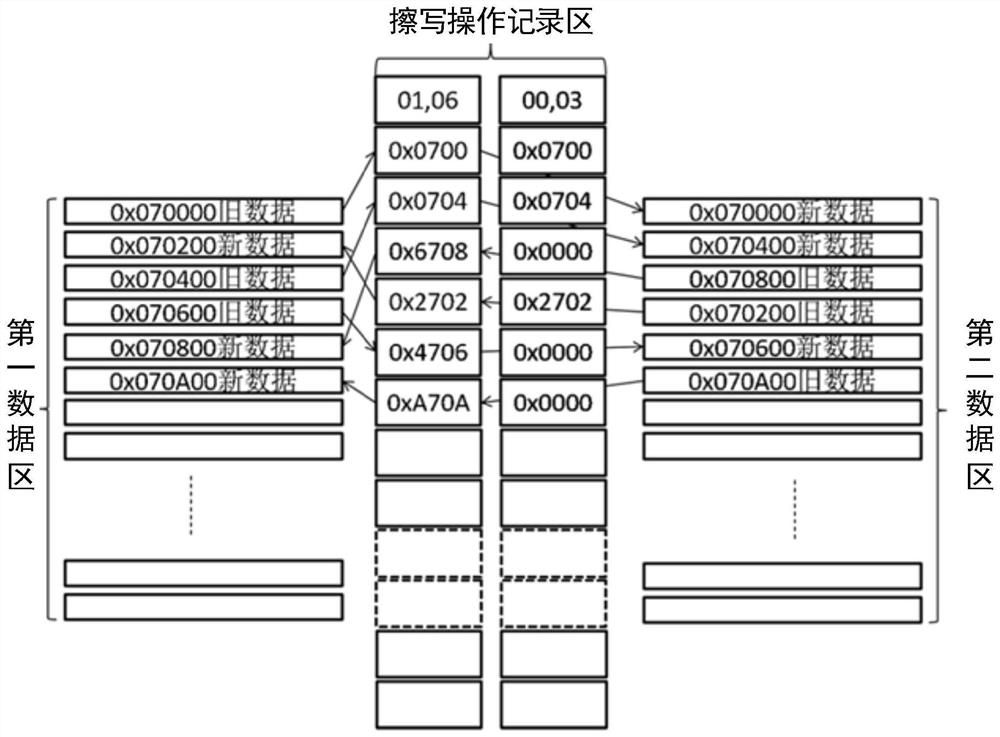

图1是FLASH芯片存储区示意图;

图2是擦写记录字节编码示意图;

图3是擦写记录单元的bit位编码示意图;

图4是一种高性能防掉电擦写方法流程图;

图5是一种芯片存储区页面数据读取方法流程图。

具体实施方式

下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

实施例一

从性能角度分析,擦写耗时要远大于查询读取数据的耗时,也就是说,提高擦写FLASH页面保护机制的性能即可提高整体业务的性能,基于此,本发明实施例一提供一种FLASH芯片存储区,能够实现高效擦写防护机制,使得FLASH芯片既能保护原有页面数据,也能高效写入新的数据。

如图1所示,所述FLASH芯片存储区包括三个区域,即第一数据区、第二数据区和擦写操作记录区,其中,第一数据区用于存储用户数据,第二数据区用于存储被擦写页面的新数据,擦写操作记录区记录擦写FLASH页面擦写的记录,按页面擦写,轮换使用,不需要备份,并要求当前写入的擦写记录页面不能与在此之前写入的擦写记录页面相同;每个擦写记录单元在第二数据区或者第一数据区对应一个页面。在擦写一个页面时,根据擦写记录页面中的内容确定一个页面,确定的页面可能在第一数据区也可能在第二数据区,然后将新的数据写入该页面;如果要擦写多个页面,则同样需要根据擦写记录页面中的擦写记录内容确定多个页面,然后将新数据写入每个页面,并在完成擦写事务后将所有擦写记录写入擦写记录页面中。

图2为擦写记录字节编码示意图,擦除记录页面是以2个字节为单元的记录组成。其中,首个两字节为记录信息(用于记录序号和记录个数的信息可以是大于2字节的,以首两字节为例),第一个字节(图2中的1、2)记录擦写记录序号,取值0~255,其中最大值即为最新擦写序号,第二个字节(图2中的3、4)记录擦写记录中有效记录的个数,即处于事务中的记录单元个数;最后两个字节(或者4字节,以两字节为例,图2中的x、y)为所有有效记录的校验核,校验核的计算可以采用现有CRC/SHA/DES/AES等算法;中间所有字节(图2中的5、6……n-1、n)为擦写记录单元。

每个擦写记录单元在第二数据区或者第一数据区对应一个页面,具体在每个擦写记录单元中记录备份数据可用页面标识,根据备份数据可用页面标识的值确定页面属于第一数据区或第二数据区。图3示例性地展示擦写记录单元的bit位编码,每个擦写记录单元也均由2个字节为单元的记录组成,包括如图3所示的bit0~bit15(需要说明的是,以下仅为擦写记录单元bit位设置的一种示例,可以根据实际需要随机设定bit位属性):

bit0~bit12为页面地址按页大小对齐后的bit位编码;

bit13记录备份数据可用页面标识,当bit13为0时表示该擦写记录单元对应的页面在第二数据区,该页面地址为该擦写记录单元的序号与页面大小的乘积加上第二数据区起始地址,当bit13为1表示该擦写记录单元对应的页面在第一数据区,该页面地址为该擦写记录单元去掉高3位后左移8位所得;

bit14记录当前标识是否处于备份事务中,当bit14为1时表示该擦写记录单元处于擦写事务中,当bit14为0时表示该擦写记录单元不在当前擦写事务中,对应的页面里的数据是最新数据;

bit15记录备份开启后当前页是否为非原子写,当bit15为1时表示为非原子写,当bit15为0时表示原子写。

需要说明的是,按照理论上讲,第一数据区与第二数据区的大小可以相等,此时擦写效率最高,但考虑到芯片可擦写存储区的空间有限,通过有限的第二数据区保护大量的第一数据区的页面擦写是现有业务的实际需要,所以当第二数据区中的页面被使用完或者正在进行现有业务中不要求性能的其他业务时,根据擦写记录单元编码将第二数据区中的用户数据写回到第一数据区中,并释放对应的擦写记录单元,用于后续擦写页面保护。

因第二数据区中可能会存在用户有效数据,所以在芯片上电时检查擦写记录单元,查找擦写记录单元中校验核正确,且擦写记录序号最大的擦写记录页面,并将该页面中的数据作为有效擦写记录单元,用于后续有效数据读取或擦写。

实施例二

本申请实施例二提供一种高性能防掉电擦写方法,应用于实施例一设计的FLASH芯片存储区中,如图4所示,所述擦写方法包括如下步骤:

步骤410、根据待写入数据的地址A,检查地址A内的数据是否在缓存中,如果是,则执行步骤440,否则执行步骤420;

步骤420、判断在擦写记录页面中是否能够查找地址A对应的记录,如果是,则执行步骤430,否则在擦写记录页面中分配一个新的记录单元位置,将所述地址编码成记录单元后写入该记录单元位置内,然后执行步骤430;

步骤430、根据缓存地址在擦写记录页面中查找对应的擦写记录单元,根据擦写记录单元解码出地址B,将缓存中的数据写入该地址B,将地址A编码成擦写记录单元后写入擦写记录页面中;

步骤440、将要写入地址A的待写入数据写入缓存中,继续判断是否有新数据需要进行写操作,如果是,则返回执行步骤410,否则数据擦写结束。

实施例三

本申请实施例三提供一种芯片存储区页面数据读取方法,应用于实施例一设计的FLASH芯片存储区中,如图5所示,所述读写方法包括如下步骤:

步骤510、根据待读取地址C,检查地址C的数据是否已被缓存,如果是,则从缓存中读取数据,执行步骤540,否则执行步骤520;

步骤520、在擦写页面记录表中查找地址C是否已被记录,如果没有被记录,则执行步骤530,如果被记录,则从擦写记录单元中解码得到地址C的数据所在页面地址D,从地址D读取数据,执行步骤540;

步骤530、从地址C直接读取数据;

步骤540、检查是否需要继续读取其他页面数据,如果是,则返回执行步骤510,否则数据读取结束。

本申请将上述设计应用到芯片擦写页面保护中,在备份数据页面没有写满的情况下,现有业务要擦写N个页面,一共要写N+1个页面就可以完成这N个页面擦写保护,与现有擦写保护机制相比,性能提高接近一倍。

与上述实施例对应的,本发明实施例提供一种FLASH芯片存储区,包括:至少一个存储器和至少一个处理器;

存储器用于存储一个或多个程序指令;

处理器,用于运行一个或多个程序指令,用以执行一种高性能防掉电读写方法,包括实施例二所述的高性能防掉电擦写方法和实施例三所述的一种芯片存储区页面数据读取方法。

与上述实施例对应的,本发明实施例提供一种计算机可读存储介质,计算机存储介质中包含一个或多个程序指令,一个或多个程序指令用于被处理器执行一种高性能防掉电读写方法。

本发明所公开的实施例提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序指令,当所述计算机程序指令在计算机上运行时,使得计算机执行上述的方法。

在本发明实施例中,处理器可以是一种集成电路芯片,具有信号的处理能力。处理器可以是通用处理器、数字信号处理器(Digital Signal Processor,简称DSP)、专用集成电路(Application Specific Integrated Circuit,简称ASIC)、现场可编程门阵列(FieldProgrammable Gate Array,简称FPGA)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。

可以实现或者执行本发明实施例中的公开的各方法、步骤及逻辑框图。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。结合本发明实施例所公开的方法的步骤可以直接体现为硬件译码处理器执行完成,或者用译码处理器中的硬件及软件模块组合执行完成。软件模块可以位于随机存储器,闪存、只读存储器,可编程只读存储器或者电可擦写可编程存储器、寄存器等本领域成熟的存储介质中。处理器读取存储介质中的信息,结合其硬件完成上述方法的步骤。

存储介质可以是存储器,例如可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。

其中,非易失性存储器可以是只读存储器(Read-Only Memory,简称ROM)、可编程只读存储器(Programmable ROM,简称PROM)、可擦除可编程只读存储器(Erasable PROM,简称EPROM)、电可擦除可编程只读存储器(Electrically EPROM,简称EEPROM)或闪存。

易失性存储器可以是随机存取存储器(Random Access Memory,简称RAM),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的RAM可用,例如静态随机存取存储器(Static RAM,简称SRAM)、动态随机存取存储器(Dynamic RAM,简称DRAM)、同步动态随机存取存储器(Synchronous DRAM,简称SDRAM)、双倍数据速率同步动态随机存取存储器(Double Data RateSDRAM,简称DDRSDRAM)、增强型同步动态随机存取存储器(EnhancedSDRAM,简称ESDRAM)、同步连接动态随机存取存储器(Synchlink DRAM,简称SLDRAM)和直接内存总线随机存取存储器(DirectRambus RAM,简称DRRAM)。

本发明实施例描述的存储介质旨在包括但不限于这些和任意其它适合类型的存储器。

本领域技术人员应该可以意识到,在上述一个或多个示例中,本发明所描述的功能可以用硬件与软件组合来实现。当应用软件时,可以将相应功能存储在计算机可读介质中或者作为计算机可读介质上的一个或多个指令或代码进行传输。计算机可读介质包括计算机存储介质和通信介质,其中通信介质包括便于从一个地方向另一个地方传送计算机程序的任何介质。存储介质可以是通用或专用计算机能够存取的任何可用介质。

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的技术方案的基础之上,所做的任何修改、等同替换、改进等,均应包括在本发明的保护范围之内。

- 一种FLASH芯片存储区及其高性能防掉电读写方法

- 一种外扩Flash程序存储区扩展EDAC校验电路及读写方法