极小度检测

文献发布时间:2023-06-19 18:34:06

背景技术

技术领域

本技术涉及数据处理领域。更具体地,本发明涉及用于浮点运算的极小度检测。

数据处理装置可提供支持用于处理以浮点表示表示的数字。在浮点表示中,使用有效数1.F或0.F、指数E和符号位S来表示数字。符号位S表示浮点数是正还是负。有效数1.F或0.F表示浮点数的有效数位(对于正规值和次正规值分别具有1或0的隐式位,并且F表示浮点数的存储位,其指示有效数在1或0的隐式位之后的剩余位)。对于正规数,指数E表示数基点(也称为二进制点)相对于有效数的位置。因此,通过改变指数的值,数基点可在有效数内左右浮动,使得对于预定位数,浮点表示可表示比其中数基点在有效数内具有固定位置的定点表示更宽范围的数字。

发明内容

至少一些示例提供了一种装置,该装置包括:浮点处理电路,该浮点处理电路用于执行具有舍入的浮点运算以生成浮点结果值;以及极小度检测电路,该极小度检测电路用于检测指示浮点运算的结果是否极小的极小度状态,其中极小结果对应于具有小于最小非零量值的量值的非零数,该最小非零量值可表示为待用于浮点结果值的浮点格式的正规浮点数;极小度检测电路包括硬件电路逻辑,该硬件电路逻辑被配置为支持舍入前极小度检测和舍入后极小度检测两者,以检测极小度状态。

至少一些示例提供了一种数据处理方法,该方法包括:执行具有舍入的浮点运算以生成浮点结果值;以及检测指示浮点运算的结果是否极小的极小度状态,其中极小结果对应于具有小于最小非零量值的量值的非零数,该最小非零量值可表示为待用于浮点结果值的浮点格式的正规浮点数;其中:使用极小度检测电路来检测极小度状态,该极小度检测电路包括硬件电路逻辑,该硬件电路逻辑被配置为支持舍入前极小度检测和舍入后极小度检测两者,以检测极小度状态。

至少一些示例提供了一种装置,该装置包括:浮点处理电路,该浮点处理电路用于执行具有注入舍入的浮点运算以生成用于浮点结果值的注入舍入有效数;以及极小度检测电路,该极小度检测电路用于检测指示浮点运算的结果是否极小的极小度状态,其中极小结果对应于具有小于最小非零量值的量值的非零数,该最小非零量值可表示为待用于浮点结果值的浮点格式的正规浮点数;其中:该极小度检测电路被配置为基于由浮点处理电路生成的注入舍入有效数来检测极小度状态。

本技术的另外的方面、特征和优点将从结合附图阅读的示例的以下描述中显而易见。

附图说明

图1示意性地示出了具有浮点处理电路的数据处理装置的示例;

图2示意性地示出了用于执行舍入前极小度检测的方法;

图3示出了用于执行舍入后极小度检测的方法;

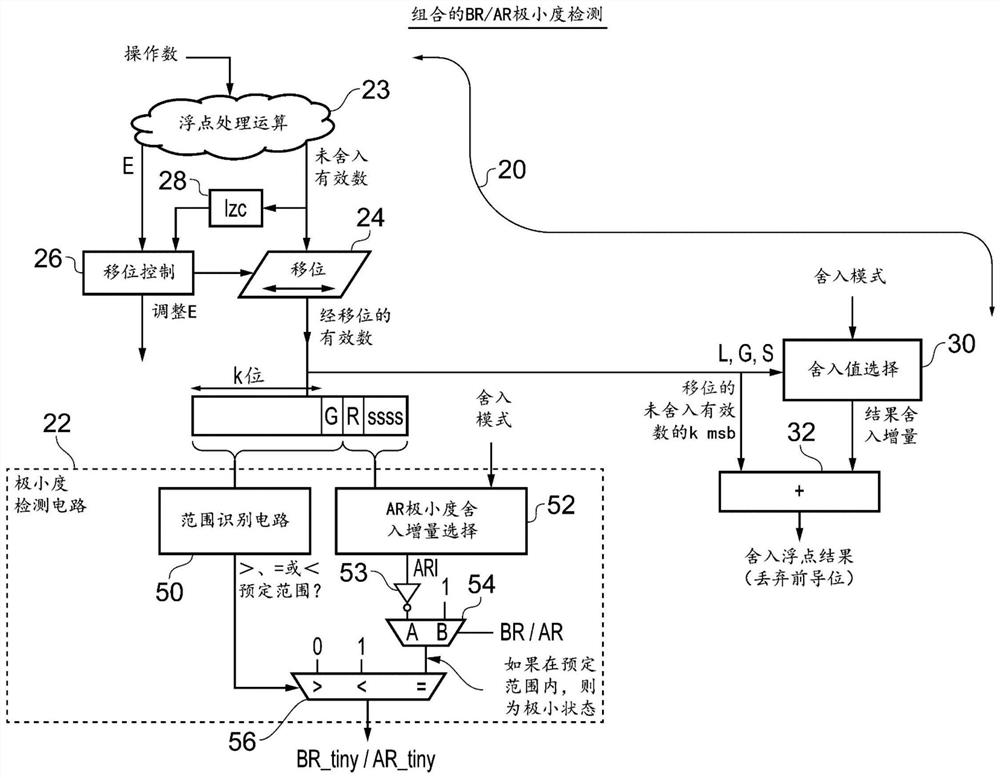

图4示出了可执行舍入前极小度检测和舍入后极小度检测两者的组合的极小度检测电路的第一示例;

图5是示出当非注入舍入用于浮点运算时执行舍入前和舍入后极小度检测两者的方法的流程图;

图6示出了能够执行舍入前和舍入后极小度检测两者的组合的极小度检测电路的另一示例,其中浮点处理电路执行注入舍入;并且

图7是示出在使用注入舍入的情况下执行舍入前极小度检测和舍入后极小度检测的方法的流程图。

具体实施方式

IEEE-754浮点标准定义了浮点运算结果的极小度概念。如果浮点运算的结果对应于具有小于最小非零量值的量值的非零数,则该结果被视为“极小”,该最小非零量值可表示为待用于浮点结果值的浮点格式的正规浮点数。因此,一种装置具有:浮点处理电路,该浮点处理电路用于执行具有舍入的浮点运算以生成浮点结果值;以及极小度检测电路,该极小度检测电路用于检测指示浮点运算的结果是否极小的极小度状态。极小度状态可用于确定是否发信号通知浮点运算的下溢异常,该下溢异常可向软件或程序员指示浮点运算的真实结果具有的量值太小而不能以所使用的浮点格式准确表示。

IEEE-754标准定义了为了将结果视为极小而必须满足的条件,但没有提供关于如何实现用于检测结果是否极小的极小度检测电路的实际建议。因此,处理器微架构师具有做出关于如何实现极小度检测电路的硬件电路逻辑的电路设计决策。极小度检测电路的设计涉及并不隐含在由标准提供的极小度的定义中的设计决策。

该标准定义了两种用于检测极小度的另选方式。例如,IEEE-754 1985标准定义(其中Emin是指在所使用的浮点格式中可表示正规浮点数的最小指数):

“可如下列中的任一项检测极小度:

1.舍入后-当计算的非零结果似乎指数范围为无界的时,将严格位于±2

2.舍入前-当计算的非零结果似乎指数范围和精度都为无界的时,将严格位于±2

通常期望处理器的任何特定具体实施将仅实现舍入前极小度检测和舍入后极小度检测中的一者。一般来讲,在电路中具体实施舍入前极小度检测可能更简单,但具体实施舍入后极小度检测可能有助于减少最终生成的下溢异常的数量(有时,舍入可能导致极小的未舍入结果被舍入到非极小的舍入值,因此在舍入后检测极小度可减少下溢的数量)。虽然舍入前和舍入后极小度的定义可能看起来类似,但在实践中,极小度检测通常以完全不同的方式来实现,这取决于给定处理器具体实施所使用的方式。例如,可预期,假设舍入后极小度不允许精度为无界的,则舍入后极小度检测可能需要计算舍入增量并将其加到从浮点运算导出的有效数,但这对于舍入前极小度检测将不是必需的。

在下文讨论的示例中,极小度检测电路包括硬件电路逻辑,该硬件电路逻辑被配置为支持舍入前极小度检测和舍入后极小度检测两者,以检测极小度状态。这是反直观的,因为IEEE标准仅要求支持这些标准中的一者,并且看起来支持第二种技术将不必要地引入额外的电路逻辑而没有益处。然而,本发明人认识到,令人惊讶地,尽管标准所提供的极小度的定义存在差异,但可在硬件中利用合理数量的电路逻辑共享来实现舍入前和舍入后极小度检测,并且因此在硬件中支持用于极小度检测的两种技术所需的附加电路逻辑的数量可能受到限制。此外,支持两种类型的极小度检测可能是有用的,使得单个硬件装置可仿真在可支持任一类型的极小度检测的不同处理器设计上实现的浮点处理的结果。对于一些计算,极小度状态可具有不同的结果,这取决于是使用舍入前还是舍入后极小度检测,并且如果为使用舍入后极小度检测的第一处理器而设计的软件在提供舍入前极小度检测的第二处理器上执行(如果必要,适当地转换为第二处理器的本机指令集),则下溢信令的差异对于软件来说可能是可见的,如果试图仿真第一处理器的行为,则这可能是不期望的。因此,为硬件电路逻辑提供对舍入前和舍入后极小度检测两者的支持可增加可由给定处理器具体实施处理的软件的范围。

极小度检测电路可包括用于舍入前极小度检测和舍入后极小度检测两者的共享数据路径。通过共享公共数据路径,这限制了硬件中支持两种极小度检测技术所需的附加电路逻辑的量。

极小度检测电路可具有选择电路,该选择电路基于该极小度检测电路是执行舍入前极小度检测还是舍入后极小度检测来选择用于在确定极小度状态中使用的中间值(除极小度状态本身之外)。因此,虽然极小度检测电路的一些部分对于两种技术可能是共同的,但其他部分可涉及基于使用舍入前还是舍入后极小度检测的选择,并且由选择电路选择的所选中间值可能对由极小度检测电路确定的总体极小度状态有贡献。由于选择电路选择在极小度检测电路的中间点处的中间值,而不是仅仅在舍入前极小度状态和舍入后极小度状态的最终值之间进行选择,这意味着两种技术之间共享的电路逻辑的量可高于如果分别为舍入前和舍入后极小度检测提供完全分离的数据路径并且仅在舍入前/舍入后极小度状态的最终值之间进行选择的情况。

极小度检测电路可基于软件可编程控制参数来选择是根据舍入前极小度检测还是舍入后极小度检测来检测极小度状态。例如,控制参数可以是保存在软件可写入寄存器中的值,或可被指定为使得浮点处理电路执行浮点运算的指令的参数。因此,软件可根据正在执行的软件的需要影响是否应根据舍入前极小度或舍入后极小度来定义极小度状态。在一些情况下,设置影响所执行的极小度检测的类型的参数的软件可与实际执行浮点运算本身(对极小度结果进行分析的运算)的软件相同。另选地,软件可编程控制参数可由比实际执行浮点运算的软件更有特权的软件来设置,该浮点运算的极小度状态正被检测。

浮点处理电路可以不同方式执行浮点运算的舍入。在一个示例中,浮点处理电路可执行注入舍入以生成用于浮点结果值的注入舍入有效数。注入舍入是一种技术,其中舍入值的相加作为与已作为浮点运算本身的一部分执行的相加相同的相加的一部分来执行,使得在浮点运算已生成其浮点结果值之后不需要舍入增量的任何单独相加。

在以下所示的示例中,当浮点处理电路使用注入舍入时,极小度检测电路可对于舍入前极小度检测和舍入后极小度检测两者基于注入舍入有效数来检测极小度状态。这可被视为反直观的,因为人们将认为在应用任何舍入之前,舍入前极小度检测将需要未舍入有效数的可见性。然而,本发明人认识到,有可能基于注入舍入有效数来推断舍入前极小度检测的极小度状态,以使得组合的极小度检测电路与注入舍入的使用兼容,这对于改善性能可能是有用的。类似地,对IEEE标准中的舍入后极小度的定义的分析可导致人们预期舍入后极小度检测将不与注入舍入兼容,因为极小度检测所需的舍入可不同于结果本身所需的舍入,但本发明人再次认识到,基于对注入舍入有效数的位的分析,有可能推断出极小度状态以使舍入后极小度检测与注入舍入兼容。

因此,在另一个示例中,一种装置,该装置包括:浮点处理电路,该浮点处理电路用于执行具有注入舍入的浮点运算以生成用于浮点结果值的注入舍入有效数;以及极小度检测电路,该极小度检测电路用于检测指示浮点运算的结果是否极小的极小度状态,其中极小结果对应于具有小于最小非零量值的量值的非零数字,该最小非零量值可表示为待用于浮点结果值的浮点格式的正规浮点数字。极小度检测电路被配置为基于由浮点处理电路生成的注入舍入有效数来检测极小度状态。因此,即使在仅支持舍入前和舍入后极小度检测中的一者(而非两者)的处理器中,提供支持基于注入舍入有效数的极小度状态检测的硬件电路逻辑也可有助于性能。

另选地,浮点处理电路可执行非注入舍入,其中该浮点处理电路生成未舍入有效数,并且浮点处理电路包括非注入舍入电路,该非注入舍入电路用于对未舍入有效数进行舍入以生成用于浮点结果值的舍入结果有效数。在这种情况下,极小度检测电路可对于舍入前极小度检测和舍入后极小度检测两者基于未舍入有效数来检测极小度状态。

无论浮点处理电路是执行注入舍入还是非注入舍入,浮点处理电路都可通过选择性地执行舍入相加来执行舍入,以生成浮点结果值的舍入结果有效数。如果正在执行注入舍入,则该舍入相加可为浮点运算本身中所使用的相同相加的一部分,或如果使用非注入舍入,则舍入相加可为与在正在执行的浮点运算中被执行以生成浮点结果的任何相加分开的相加。

对于舍入后极小度检测,极小度检测电路可执行舍入后极小度检测而不执行除已由浮点处理电路执行以生成用于舍入浮点结果的舍入结果有效数的舍入相加之外的任何其他舍入相加。这可能是反直觉的,因为人们将认为舍入后极小度检测确实需要执行舍入,由于在标准中定义的舍入后极小度的“无界指数”要求,这与对结果本身的舍入不是同一类型的舍入,并且因此通常人们将期望需要进一步的舍入相加。然而,本发明人认识到,这种进一步的舍入增量相加不是必需的,因为有可能利用相对简单的布尔逻辑门集合来分析从浮点处理电路的输出导出的有效数的位,以推断舍入后极小度状态,而不需要加上任何进一步的舍入增量。这对于使用非注入舍入的具体实施和使用注入舍入的具体实施两者都是可能的。这是有帮助的,因为相加在性能方面往往是缓慢的,并且因此避免进一步的舍入相加可减少极小度检测的等待时间,从而改善性能。

更具体地,极小度检测电路包括增量确定电路,该增量确定电路用于基于从由浮点处理电路输出的未舍入有效数或注入舍入有效数导出的有效数来确定用于舍入后极小度检测的舍入后极小度检测舍入增量;以及当执行舍入后极小度检测时,极小度检测电路被配置为基于由增量确定电路确定的舍入后极小度检测舍入增量来确定极小度状态,而不将舍入后极小度检测舍入增量加到从未舍入有效数或注入舍入有效数导出的有效数。因此,对于舍入后极小度检测,虽然可确定舍入后极小度检测舍入增量,但不需要将其加到有效数,而是相反可通过布尔逻辑门集合而不是加法器由舍入后极小度检测舍入增量来推断极小度状态。这改善了性能。

在浮点运算中,浮点处理电路可生成结果指数以及未舍入有效数或注入舍入有效数,这取决于如上所讨论的是通过非注入舍入还是注入舍入来执行舍入。该装置可具有移位电路,该移位电路用于将未舍入有效数或注入舍入有效数移位可变位数,以生成经移位的有效数。极小度检测电路可对于舍入前极小度检测和舍入后极小度检测两者基于由移位电路生成的经移位的有效数来检测极小度状态。因此,移位电路可被两种类型的极小度检测共享。

待用于移位的可变位数可由移位控制电路选择。当结果指数E小于用于非零正规浮点数的浮点格式所支持的最小指数Emin时,该移位为向右移位Emin-E位。当结果指数大于或等于最小指数并且未舍入有效数或注入舍入有效数的最高有效位为1时,可变位数为0。当结果指数大于或等于最小指数Emin并且未舍入有效数或注入舍入有效数的最高有效位为0时,该移位为向左移位对应于lzc和(E-Emin)中的最小值的位数,其中lzc为未舍入有效数或注入舍入有效数中前导零的数量。该方法提供了经移位的有效数,其可用作舍入前和舍入后极小度检测两者的基础。

极小度检测电路可具有范围识别电路,该范围识别电路识别由结果指数和未舍入有效数或注入舍入有效数表示的结果量值是否在预定范围内,对于该预定范围,舍入前极小度检测和舍入后极小度检测能够针对在至少一种舍入模式中的极小度状态提供不同的结果。通过提供此类范围识别电路,这意味着可简化电路硬件设计,因为对未舍入有效数或注入舍入有效数(或导出的有效数,诸如前面提到的经移位的有效数)的更细致的分析可被限制到其中极小度状态对于舍入前/后极小度可变化的那些情况。在该范围之外,可更简单地设置极小度状态,而无需细致分析经移位的有效数的较低有效位的特定位值。因此,识别结果量值是否在某一范围内减少了需要考虑的可能性的数量,并因此简化了电路硬件设计。

范围识别电路可基于经移位的有效数来识别在预定范围内的结果量值。例如,可分析经移位的有效数的特定数量的最高有效位以确定结果量值是否在预定范围内。

当结果量值由范围识别电路确定为在预定范围内时,至少对于舍入后极小度检测以及对于至少一种舍入模式,极小度检测电路被配置为基于经移位的有效数的一个或多个低位来设置极小度状态,该一个或多个低位处于在经移位的有效数被截断以适合待用于浮点结果的浮点格式的情况下将被丢弃的位位置处;以及当结果量值由范围识别电路确定为在预定范围之外时,极小度检测电路被配置为独立于经移位的有效数的所述一个或多个低位来设置极小度状态。

因此,对于在预定范围内的值,实际上仍不需要加上舍入增量,因为对经移位的有效数的一个或多个低位的分析足以使得能够确定极小度状态。在预定范围之外,可独立于经移位的有效数的那些一个或多个低位来设置极小度状态。例如,当结果量值由范围识别电路确定为大于预定范围时,对于舍入前极小度检测和舍入后极小度检测两者,极小度检测电路被配置为将极小度状态设置成指示浮点运算的结果不是极小的;以及当结果量值由范围识别电路确定为小于预定范围时,对于舍入前极小度检测和舍入后极小度检测两者,极小度检测电路被配置为将极小度状态设置成指示浮点运算的结果是极小的。因此,对于预定范围之外的量值,仅基于范围确定本身来设置极小度状态是相对简单的,而无需对范围内的特定值进行进一步分析,从而简化了电路。

在一些情况下,浮点处理电路可支持许多不同的舍入模式。虽然可存在至少一种舍入模式,对于该舍入模式,当结果量值在预定范围内时,舍入前和舍入后极小度检测可提供不同的结果,但这不一定适用于所有舍入模式,并且可存在至少一种其他舍入模式,当结果量值在预定范围内时,无论是使用舍入前还是舍入后极小度检测,该至少一个其他舍入模式都提供相同的结果。

在支持多种舍入模式的情况下,当结果量值由范围识别电路确定为在预定范围内时,至少对于舍入后极小度检测,极小度检测电路被配置为根据针对浮点处理运算选择哪种舍入模式来设置极小度状态;以及当结果量值由范围识别电路确定为在预定范围之外时,极小度检测电路被配置为独立于针对浮点处理运算选择哪种舍入模式来设置极小度状态。因此,提供范围识别电路的另一优点在于,仅当结果量值在预定范围内时,才需要做出特定于舍入模式的决策,当在该范围之外时,则为了设置极小度状态没有必要考虑舍入模式。舍入前极小度检测是否依赖于舍入模式可取决于非注入舍入还是注入舍入用于浮点运算-对于非注入舍入,舍入前极小度检测不必取决于舍入模式,但对于注入舍入,舍入前极小度检测可取决于在结果量值在预定范围内的情况下使用的舍入模式。

预定范围的定义可根据是使用注入舍入还是非注入舍入而变化。一般来讲,预定范围可覆盖接近可以浮点格式表示的最小正规正非零数的相对小的数字量值范围,并且因此在大多数浮点运算中,结果量值可被确定为在预定范围之外。由于其中极小度状态可根据舍入后或舍入前极小度检测而变化的范围相对较小,因此这将可能情形的数量减少到可从对经移位的有效数的较低有效位的检查中推断出已发生哪种情形的程度,并且因此相应地确定极小度状态,而无需舍入相加或规范化向左移位(用于舍入后极小度检测)。

在非注入舍入的情况下,浮点处理电路可生成未舍入有效数,并且因此范围确定可基于如上文所讨论的由移位电路从未舍入有效数生成的经移位的有效数。在该情况下,当结果量值x满足界限

在非注入舍入的情况下,可在使用舍入后极小度检测时执行对经移位的有效数的一个或一个多个低位的分析,以确定极小度状态。然而,对于舍入前极小度检测,极小度检测电路可简单地设置极小度状态以指示在结果量值在预定范围内的情况下浮点运算的结果是极小的。因此,利用非注入舍入和舍入前极小度检测,量值在预定范围内的确定足以能够推断出极小度状态而无需任何进一步分析。

另一方面,如果浮点处理电路正在使用注入舍入,并且因此由注入舍入的有效数生成经移位的有效数,则预定范围可与非注入舍入情况不同。在这种情况下,当结果量值x满足界限2

在注入舍入的情况下,当结果量值在预定范围内时,可对于舍入前极小度检测和舍入后极小度检测两者执行经移位的有效数的一个或多个低位的一些进一步分析。因此,当浮点处理电路执行注入舍入并且结果量值在预定范围内时,对于至少一种舍入模式,对于舍入前极小度检测和舍入后极小度检测两者,极小度检测电路被配置为基于经移位的有效数的一个或多个低位来设置极小度状态,该一个或多个低位处于在经移位的有效数被截断以适合待用于浮点结果的浮点格式的情况下将被丢弃的位位置处。用于将这些一个或多个低位映射到极小度状态的特定逻辑功能对于舍入前极小度检测与舍入后极小度检测相比可不同,但尽管如此,范围识别电路对于两种情况可为共用的以共享硬件电路逻辑并且因此通过具有共享数据路径而减少总电路面积。

图1示意性地示出了数据处理装置2的示例,例如处理器诸如CPU(中央处理单元)。装置2具有用于从高速缓存或存储器提取程序指令的指令提取电路4,以及用于对所提取的指令进行解码以生成用于控制执行单元8执行由指令表示的处理运算的控制信号的解码电路6。执行单元8对从寄存器10读取的操作数执行处理运算,并将运算的结果写入寄存器10。执行单元8可包括用于执行不同类别的指令的多个不同类型的执行单元,诸如用于对整数值执行算术和逻辑运算的整数算术/逻辑单元(ALU)12、用于对以浮点表示表示的数字执行浮点运算的浮点ALU 14、用于执行能够触发程序流的非连续改变的分支指令的分支执行单元16、以及用于处理将数据从高速缓存或存储器加载到寄存器10的加载操作或将数据从寄存器10存储到高速缓存或存储器的存储操作的加载/存储单元18。应当理解,这仅仅是可提供的一些类型的执行单元的示例,但其他示例可具有其他类型。

浮点ALU 14具有用于执行浮点处理运算的浮点处理电路20。此类浮点处理运算可包括算术运算诸如加法、减法、乘法、除法或平方根运算,以及用于在不同浮点表示之间转换或在浮点表示与非浮点表示(例如整数或定点)之间转换的转换运算。浮点ALU还包括极小度检测电路22,其将在下文中更详细地讨论并且被提供用于检测由浮点处理电路20执行的浮点运算的结果的极小度状态。极小度状态指示浮点运算的结果是否为极小的。如果结果对应于具有小于最小非零量值的量值的非零数,则该结果被认为是极小的,该最小非零量值可表示为待用于由浮点处理电路20正在执行的浮点运算中生成的浮点结果值的浮点格式的正规浮点数。

浮点(FP)是使用少量位来取实数的近似值的可用方式。IEEE 754-2008FP标准提出了用于FP数的多种不同格式,但是一些常用的格式是二进制64(也称为双精度或DP)、二进制32(也称为单精度或SP)和二进制16(也称为半精度或HP)。数字64、32和16是指在每种格式的存储值中所需的位数。

FP数非常类似于理科班中教的“科学记数法”,其中我们写-2.0×10

更确切地说,FP数全部由符号位、一定数量的偏移指数位和一定数量的小数位组成。具体地,感兴趣的格式由以下位组成:

负数的符号为1,正数的符号为0。每个数字(包括零)都具有符号。

指数是偏移的,这意味着真指数与以数字存储的指数不同。例如,偏移的SP指数为8位长并且在0至255的范围内。指数0和255为特殊情况,但所有其他指数均具有偏移127,这意味着真指数比偏移指数小127。最小偏移指数为1,其对应于-126的真指数。最大偏移指数为254,其对应于127的真指数。HP和DP指数以相同方式计算,其中偏移在上表中示出。

SP指数255(或DP指数2047或HP指数31)被保留为无穷大和称为NaN(非数字)的特殊符号。无穷大(其可为正或负)具有零小数。具有指数255和非零小数的任何数字为NaN。无穷大提供饱和值,因此这实际上意味着类似以下意思:“该计算得出了比我们可以这种格式表示的数字更大的数字”。返回NaN用于在数学上不在实数上定义的操作,例如除以零或取负数的平方根。

在任何格式中,指数零被保留为次正规数和零。正规数表示以下值:

-1

其中e为根据由偏移指数计算的真指数。术语1.小数被称为有效数,并且1不作为FP数的一部分存储,而是从指数推断。除零和最大指数之外的所有指数指示形式1.小数的有效数。指数零指示形式0.小数的有效数,以及对于给定格式等于1-偏移的真指数。这种数字被称为次正规的(在历史上这些数字被称为非正规的,但现代用法优选术语次正规的)。

指数和小数两者均等于零的数字为零。

下表具有HP格式的一些示例性数字。这些条目为二进制的,其中添加‘_’字符以增加可读性。需注意,次正规条目(表中的第4行,具有零指数)产生与前一行中的正规条目不同的有效数。

FP具体实施的大部分复杂性归因于次正规数,因此这些次正规数通常由微码或软件处理。一些处理器具体实施在硬件中处理次正规数,从而与软件或微码具体实施相比,将这些操作加速10倍至100倍。

处理符号的FP方式被称为符号量值,并且其不同于将整数存储在计算机中的常见方式(二进制补码)。在符号-量值表示中,相同数字的正版本和负版本仅在符号位上有所不同。由符号位和3个有效数位组成的4位符号量值整数将如下表示加一和减一:

+1=0001

-1=1001

在二进制补码表示中,n位整数i由二进制n+1位值2

+1=0001

-1=1111

该二进制补码格式对于有符号整数实际上是通用的,因为它简化了计算机算术。

固定点数看起来完全像整数,但实际上表示具有一定数量小数位的值。传感器数据通常为固定点格式,并且存在广泛采用FP之前编写的大量固定点软件。固定点数处理起来非常繁琐,因为编程器必须跟踪“二进制点”,即数字的整数部分与小数部分之间的分隔符,并且还必须不断地移位数字以将位保持在正确的位置。FP数不具有此困难,因此希望能够在固定点数与FP数之间转换。能够进行转换还意味着我们仍然能够使用固定点软件和数据,但我们在编写新软件时不限于固定点。

IEEE-754标准要求计算大多数FP运算,就好像该运算是以无界范围和精度进行的那样,然后舍入以拟合FP数。如果该计算恰好匹配FP数,则始终返回该值,但通常该计算得出位于两个连续浮点数之间的值。舍入是选取应返回两个连续数字中的哪个数字的过程。

存在多种舍入的方式,这些方式被称为舍入模式;其中的六种模式为:

该定义未告知我们如何以任何实际方式舍入。一种常见的具体实施是进行运算,查看截断值(即,拟合FP格式的值)以及所有剩余位,然后在某些条件成立的情况下调整该截断值。这些计算均基于:

L-(最小)截断值的最低有效位

G-(保留)下一个最高有效位(即,不包括在截断中的第一位)

S-(粘滞)不是截断的一部分的所有剩余位的逻辑OR

考虑到这三个值和截断值,我们可始终根据下表计算正确舍入的值:

例如,考虑两个4位有效数相乘,然后舍入为4位有效数。

符号1=1011(十进制11)

符号2=0111(十进制7)

相乘得到

符号1×符号2=1001_101(十进制77)

L Gss

截断的4位结果的最低有效位被标记为L,下一位被标记为G,并且S为被标记为s的剩余位的逻辑OR(即,S=0|1=1)。为了舍入,我们根据上表中的舍入模式和计算来调整4位结果(1001)。因此,例如在RNA舍入中,G被设置,因此我们返回1001+1=1010。由于RX舍入G|S为真,因此我们将L设置为1(它已经是1,因此在这种情况下没有改变)并返回1001。

在我们将FP数转换成整数或固定点的情况下,我们也必须进行舍入。该概念与FP舍入基本上相同。恰好为整数的FP数总是舍入为该整数。所有其他FP数均位于两个连续整数之间,并且舍入决定返回哪个整数。遗憾的是,由于二进制补码和符号量值形式之间的差异,整数的舍入逻辑在一定程度上较为困难。使符号量值数递增总是增加幅值,因此递增的数距离零更远。正二进制补码数也发生相同的情况,但负二进制补码数在递增时变得更接近零。这意味着舍入逻辑必须基于整数是正的还是负的来改变。这也意味着我们必须仔细选取基准值(将递增或不递增的值)。对于正整数,该值仅为截断的FP有效数,因此1.37将具有基准值1,以及为1或2的结果。对于负整数,我们再次截断有效数并获取结果的一的补码(一的补码是所有位被反转的原始数字),-1.37被截断为1,然后被反转,给出基准值-2。那么一切都是可行的,因为我们希望结果为-2或(当递增时)-1。

为了使事物进一步复杂化,我们的转换方法需要一些计算来找到负整数的L、G和S。正确的舍入将需要我们完成二进制补码过程(反转并加1),然后计算L、G和S,但与仅反转相比,加1较慢。理想的是,我们希望根据原始移位的输入(即,根据在我们已完成关于符号的任何事情之前的输入)计算实际L、G和S。因此浮点1.37或-1.37两者将向右移位至整数1)。

使L0、G0和S0为反转之前的最低有效位(lsb)、保留位和粘滞位,并且使Li、Gi和Si为反转之后的lsb、保留位和粘滞位,并且最终使L、G和S为反转并加1之后的lsb、保留位和粘滞位。

如果S0为零,则对Si有贡献的位全为一,因此S(通过将1加到那些Si位而获得的)也为零。如果S0不为零,则Si不全为一,因此S为非零。因此在所有情况下,S0=S。

如果G0为零,则Gi为1,并且G也为一,除了存在来自S位的进位时的情况之外,这仅在S0为零时发生。如果G0为1,则Gi为零,并且同样G也为零,除了存在来自S位的进位时的情况之外,这仅在S0为零时发生。因此G=G0^S0。

通过非常类似的逻辑,L=L0^(G0|S0)。

由于我们具有负整数和正整数的L、G和S,因此我们可得出舍入规则:

固定点数舍入的方式与整数完全相同。无符号转换(到整数或固定点)的规则与正转换的规则相同。

进行舍入的更快方式是注入舍入常数作为有效数相加的一部分,这是几乎每次FP运算的一部分。为了查看这种方式的效果,考虑将为美元和美分的数字相加,然后舍入为美元。如果我们进行以下相加:

$1.27

+$2.35

$3.62

我们看到,总和$3.62与$4的接近程度大于与$3的接近程度,因此任一种舍入到最接近模式都应返回$4。如果我们以二进制表示数字,则我们可使用来自最后部分的L、G、S方法获得相同的结果。但是假设我们只加五十美分,然后截断结果?

1.27

+2.35

+0.50(舍入注入)

4.12

如果我们刚刚从总和($4.12)返回美元金额($4),则我们已使用RNA舍入模式正确进行了舍入。如果我们加$0.99而不是$0.50,则我们将使用RP舍入正确进行舍入。RNE稍微更复杂:我们加$0.50,截断,然后查看剩余的美分。如果剩余的美分为非零,则截断的结果是正确的。如果剩余零美分,则我们在注入之前恰好在两个美元金额之间,因此我们选取偶数美元金额。对于二进制FP,这相当于将美元金额的最低有效位设置为零。

将三个数字相加仅比将两个数字相加稍微慢些,因此我们通过使用注入舍入以与将两个有效数相加的情况相比快得多的速度获得舍入结果,检查L、G和S,然后根据舍入模式使该结果递增。

对于FP,舍入注入是三个不同值(取决于舍入模式和(有时)结果的符号的值)中的一个值。

·RNA和RNE两者都需要我们在G位置处注入1(这就像在美元和美分示例中加$0.50)。

·RP和RM舍入取决于符号以及模式。RP将正结果向上舍入(朝正无穷大增大有效数的量值),但截断负结果(选取更接近正无穷大的有效数)。类似地,RM将负结果向上舍入(朝负无穷大增大有效数的量值),但截断正结果(选取更接近负无穷大的有效数)。因此,我们将RM和RP分成两种情况:当符号与舍入方向匹配时向上舍入(RU),以及当符号与舍入注入不同时截断(RZ)。对于RU案例,我们在G位位置处以及在逻辑上对S做出贡献的每个位置处注入1(这就像在美元和美分示例中加$0.99)。

·对于RZ和RX模式,以及对于减小到RZ模式的RP和RM模式,我们注入零。

对于大多数舍入模式,加舍入注入,然后截断给出正确的舍入结果。两个例外是RNE和RX,它们需要我们在相加之后检查G和S。对于RNE,如果G和S两者均为零,则我们将L设置为0。对于RX,如果G或S为非零,则我们将L设置为1。

很容易将FP数视为就像实数一样,但它们在本质上是不同的,即使对于最基本的属性也是不同的:

1.它们不是结合性的。例如,在SP中,我们可将3个数字相加并返回1百万或零,这可能不是人们认为的舍入误差:

(2

2

2.它们不遵守分配律。同样在SP中:

3,000,001*(4.00001+5.00001)=0x4bcdfe83

(3,000,001*4.00001)+(3,000,001*5.00001)=0x4bcdfe82

并且在存在溢出的情况下,情况变得更糟:

2

(2

3.在一些具体实施中,它们甚至不是可交换的,除非我们处于默认NaN模式(将所有NaN转换成单个NaN的模式),因为一般来讲,nanA+nanB!=nanB+nanA。数字相加和相乘是可交换的。

4.由于IEEE NaN规则,不存在乘法单位元或加法单位元。一和零用作数值的单位元。

考虑FP数的一种可用的方式是将其视为非常长的固定点数,其中至多几个(对于DP而言53个)连续位可为非零。例如,非无穷大DP数可在2046个位置中的任一个位置中具有有效数的第一位,并且该第一位之后是52个其他有效数位,并且存在符号位,因此任何有限DP数可被表示为2046+52+1=2099位固定点数。检查这种方式,变得非常明显的是,将两个FP数相加通常不会产生另一个FP数:相加的结果必须被舍入,使得其变成FP数。

IEEE-754浮点标准(1985、2008、2019)具有两种检测计算是否产生极小结果的不兼容方式,“舍入前”和“舍入后”。提供检测极小度的两种方式的部件是有用的,以帮助仿真可使用这些检测极小度的方式中的一种或另一种的不同处理器的行为。

该标准提供了两种检测极小度的方式。来自1985标准:

“可如下列中的任一项检测极小度

1.舍入后-当计算的非零结果似乎指数范围为无界的时,将严格位于±2

2.舍入前-当计算的非零结果似乎指数范围和精度都为无界的时,将严格位于±2

对于极小和不精确的最终结果,发信号通知下溢。为浮点运算返回的IEEE 754结果对于两种方法是相同的,并且不精确性对于两种方法也是相同的(不精确意味着舍入和未舍入结果是不同的)。

图2示出了一种具体实施舍入前极小度检测的方法。浮点处理电路20内的电路逻辑23首先执行浮点运算(例如,加法或乘法)以产生未舍入结果有效数x,计算该结果就像我们具有无界范围和精度一样,然后如果无界指数E小于Emin,则移位器24将该结果向右移位,使得未舍入有效数对应于指数Emin。移位控制电路26控制由移位器24使用的移位量。还提供前导零计数器28以对未舍入有效数中的前导零(lzc)的数量进行计数,并且如果前导零计数为非零并且无界指数E大于或等于Emin,则移位器24改为将未舍入有效数向左移位对应于lzc和E-Emin中的最小值的位数。因此,移位器的输出(经移位的有效数)为在E 无论哪种方式,确定x是否为“舍入前”极小的(BR_tiny)包括查看经移位的未舍入有效数的第一位: -如果前导位为一,则结果不为BR_tiny -如果前导位为零,则结果为BR_tiny。 因此,舍入前极小度状态由NOT门(反相器)34生成,其对经移位的有效数的最高有效位进行反转以生成舍入前极小度状态。在该示例中,舍入前极小度检测电路22将简单地包括NOT门34。移位电路24、移位控制电路26和前导零计数器28可被认为是浮点处理运算20的一部分,因为除了对极小度检测有用之外,以这种方式移位未舍入结果还具有使得容易计算正确的舍入结果的优点。对于具有k位有效数(即k-1位小数)的格式,我们现在简单地在位k处舍入。因此,舍入值选择电路30可基于对从经移位的有效数确定的状态值L、G、S的分析来决定将由加法器32加到经移位的有效数的舍入值,以生成舍入浮点结果。如上表4所示执行舍入值选择。 图3示出了用于执行舍入后极小度检测的方法。这不如舍入前极小度检测那样简单,因为存在舍入步骤,并且由于标准中舍入后极小度的定义,它不是通常的舍入:“当计算的非零结果似乎指数范围[而不是精度]为无界的时,将严格位于±2 无界指数范围意味着对总是规格化的数进行“舍入后”测试,即,有效数开始于“1”。因此,如图3所示,在极小度检测电路20中执行基于前导零检测的规格化移位38(并且指数E由电路40调整以考虑规格化)。这种规格化对于具有舍入的标准浮点结果是不需要的,因为对于次正规范围内的值,由移位电路24执行的移位将具有一些前导零,而移位器38确保无论指数E的值如何,用于极小度检测的移位的有效数都具有前导1。如果格式具有k个有效位,则将规格化的有效数舍入到以前导1开始的k位值(通过根据所使用的舍入模式基于状态值位L、G、S(其中S是标记为s的有效性比G低的所有位的逻辑OR)执行舍入后极小度舍入增量选择42,然后将舍入增量加到44由规格化移位器38输出的经移位的有效数)。由于舍入值必须具有前导1,因此在舍入相加44之后仍需要进一步的规格化移位46(如果极小度舍入引起溢出,则规格化移位46将被限于向右移位1位)。然后,使用电路46、48,我们计算k位舍入值是否位于“严格在±2 -如果舍入值严格位±2 -否则结果不是AR_tiny (这里“AR_tiny”表示使用舍入后极小度检测发现结果是极小的)。 注意,这种极小度舍入计算与由原始FP运算返回的值无关。“舍入后”极小度舍入严格用于确定极小度,之后丢弃极小度舍入值。因此,与舍入后极小度检测分开,由移位器24生成的经移位的有效数也以与图2中所示相同的方式经受舍入增量选择30和相加32。因此,在32和44处存在两个单独的舍入相加。

在典型的处理器硬件设计中,极小度检测电路22仅执行舍入前极小度检测和舍入后极小度检测中的一者。这是因为IEEE-754标准不要求同时支持这两者,因此可认为用于支持第二极小度检测技术的附加逻辑是不必要的。而且,如图2和图3所示,用于检测舍入前和舍入后极小度检测的技术通常被认为需要完全不同的电路逻辑,使得几乎不可能共享电路。 然而,本发明人已认识到,通过在结果量值在特定范围内的情况下分析经移位的有效数的位,可能提供用于舍入前和舍入后极小度检测两者的统一数据路径,即使在舍入后极小度检测的情况下,其也支持具有相对有效的电路逻辑的两种技术,其中与图3中所示的方法相反,实际上不必执行除已经执行的用于对浮点处理运算的实际浮点结果进行舍入的舍入相加以外的舍入相加。 这利用了如下的一系列实现。 调用舍入在两个连续FP数之间进行选择。将ulp定义为最低位置中的单位,具有给定指数的有效数的低阶位的量值(即,在指数为Emin的值的特定情况下,ulp为在所使用的浮点格式中可表示的最小次正规数),并且使x为我们的浮点运算的未舍入结果。 任何x>=2 任何x<=2 这留下需要进一步测试的非常小的数字范围, 2 对于具有k位有效数的格式,在该范围内的所有经移位的未舍入数x由前导零后面紧接着至少k-1个一组成。未舍入移位结果现在具有以下部分(从高阶位开始): 1)整数位(在该范围内总是为零)。 2)k-1个小数位(在该范围内总是全部为一)。 3)G,保留位 4)R,G之后的下一位 5)任意数量的s或粘滞位。 对于舍入前极小度检测,在2 为了确定x是否为AR_tiny,我们必须(理论上)规格化该值,以便存在前导零并且下一位为1,理论上存在向左移位一位的位置(在实践中,不需要执行该移位,因为我们可简单地将正规L、G、S右一个位置的位视为用于舍入增量选择的L、G、S值)。因此,G变为用于AR极小度确定的低阶有效位(相当于上表4中的L)。如果该位为零,则AR_rounding(将理论上已为AR极小度检测而执行但当如下所示确定AR极小度时实际上不执行的舍入)在上文中以2 唯一剩余的情况是当G为一时,对于上述x的范围,其适用于范围2 因此,要检查的范围为2 舍入计算与上文所示的FP概览的表4中使用的相同,但不是使用L、G和S作为正规值,而是使用以下计算舍入后增量(ARI): AR_L=G=1 AR_G=R AR_S=所有标记为s的位的逻辑OR (这考虑了上述理论上的一位向左移位)。 ARI的计算根据舍入模式而变化,但是对于感兴趣的3种舍入模式(RNE、RU、RZ),我们具有:

(注意,如果该值为正,则RU对应于表4中所示的RP,如果该值为负,则RU对应于RM)。 在所有这些示例中,ARI都容易计算而实际上不进行任何舍入,因此除已提供用于舍入的加法器32之外,不需要任何附加的舍入加法器。 综上所述,给定经移位的未舍入有效数x,我们可根据表7计算BR_tiny和AR_tiny两者:

其中k是所使用的浮点格式的有效数(包括将不是所存储的小数F的一部分的隐式前导1或0)中的位数。 在实践中,图4示意性地示出了在使用非注入舍入用于浮点运算的示例中用于检测舍入前和舍入后极小度状态两者的组合的极小度检测电路的示例。浮点处理电路20与图2和图3中所示的相同,并且因此包括用于执行浮点处理运算本身的电路逻辑23(例如,逻辑23可以是浮点加法器或乘法器)。而且,浮点处理电路20包括如图2所示的移位电路24、移位控制电路26和前导零计数电路28。移位电路24根据指数E与最小指数Emin之间的差值以及由浮点运算生成的未舍入有效数的前导零的前导零计数来应用可变的向右移位或向左移位,以生成经移位的有效数。此外,浮点处理电路20包括舍入值选择电路30和舍入加法器32,该舍入加法器用于将舍入值加到经移位的未舍入有效数,其中根据所使用的舍入模式基于经移位的未舍入有效数的LGS位来选择舍入值(例如,参见上表4)。 与图2和图3相比,图4中的极小度检测电路22包括范围识别电路50、舍入后(AR)极小度舍入增量选择电路52、以及多路复用器54、56,这些多路复用器用于根据正在执行舍入前还是舍入后极小度检测以及由范围识别电路50生成的指示由浮点处理运算23生成的结果的结果量值是大于预定范围、在预定范围内还是小于预定范围,来选择极小度状态的输出值。 如上所讨论,范围识别电路检查经移位的有效数的高k+1位。如果经移位的有效数的前导位为1,则结果量值被确定为大于预定范围(在其他示例中,也可根据指数E在考虑移位器24所应用的移位的调整之后是否大于Emin来识别大于预定范围的结果)。如果经移位的有效数的最高有效位为0,并且其后跟至少k个连续的1,则结果量值在预定范围内。如果经移位的有效数的最高有效位为0,并且其后跟小于k个连续的1,则结果量值小于预定范围。 AR极小度舍入增量选择电路52根据舍入模式和经移位的有效数的低位R和ssss来确定AR极小度舍入增量(虽然为了简明起见,图4示出了标记为s的4个位,但s位的数量将根据浮点运算所生成的精度而变化)。如果舍入模式为RZ,则AR极小度舍入增量为0。如果舍入模式为RNE,则AR极小度舍入增量等于位R,位R为将形成用于结果的截断k位有效数的一部分的最低有效位下方的两个位置。如果舍入模式为RU,则AR极小度舍入增量对应于在逻辑OR运算中将位R和所有低位ssss组合的结果(即,如果低位R、ssss中的任何一者或多者为1,则舍入后极小度舍入增量(ARI)也为1)。AR极小度舍入增量ARI由NOT门53反转并提供给多路复用器54,该多路复用器在ARI的反转值与单个位值1之间进行选择,这取决于是根据舍入后还是舍入前极小度检测正在执行极小度检测。多路复用器54的输出表示在结果量值被发现在预定范围内的情况下的极小度状态,并且如果正在执行舍入前极小度检测则被设置为1,并且如果执行舍入后极小度检测则被设置为ARI的倒数。 多路复用器56根据范围识别电路50的输出选择极小度状态的最终值。如果范围识别电路50确定结果量值大于预定范围,则对于舍入前和舍入后极小度检测两者输出极小度状态值0,以指示结果不是极小的。如果范围识别电路50识别出结果量值小于预定范围,则输出值1作为极小度状态,以指示对于舍入前和舍入后极小度检测两者结果是极小的。如果范围识别电路50识别出结果量值在预定范围内,则由多路复用器56输出的极小度状态为基于正在执行舍入前极小度检测还是舍入后极小度检测设置的多路复用器54的输出。 因此,利用这种方法,极小度检测电路可利用硬件中相对简单的电路逻辑并且对于舍入前和舍入后极小度检测两者利用公共数据路径来实现,使得在同一硬件具体实施中支持两种类型的极小度检测。计算结果量值是否在预定范围内不需要特定位值的任何困难比较,因为这仅仅是对未舍入有效数的前k+1位的简单检查,因此不需要位的更多任意模式相对于比较常数的相加/相减或比较。范围计算可用简单的布尔门集合来完成。例如,可简单地直接从经移位的有效数的最高有效位导出指示结果是否大于范围的信号。指示结果是否在范围内的信号可通过对经移位的有效数的最高有效位的倒数与经移位的有效位的下个k位中的每一者(的非反转值)执行逐位AND来生成。指示结果是否小于范围的信号可通过对经移位的有效数的最高有效位的倒数与经移位的有效位的下个k位的逐位AND的倒数执行AND运算来生成。当然,可设计另选的逻辑门组以给出相同的结果,因此这仅仅是一个示例。 此外,极小度检测电路22在执行舍入后极小度检测时不需要包括如图3的示例中的任何舍入增量相加电路44或规格化电路38、46,即使为了支持AR极小度检测,这极大地加速了极小度检测并减小了电路面积。在舍入后极小度舍入增量选择电路52中计算舍入后极小度舍入增量ARI所需的电路逻辑的量相对较小,因为范围识别电路50已识别出相对较窄的预定范围,其中待针对该预定范围确定增量ARI,并且因此可能性的数量受到限制。因此,该方法允许以相对小的电路面积和功率成本支持两种类型的极小度检测。 图5是示出在图4的示例中检测极小度的方法的流程图。在步骤200处,浮点处理电路20执行浮点运算以生成结果指数E和未舍入有效数。在步骤202处,移位控制电路26确定结果指数E是否小于最小指数Emin,该最小指数是在所使用的浮点格式中可表示的最小正规指数。如果结果指数E小于Emin,则在步骤204处,移位控制电路26控制移位电路24执行未舍入有效数向右移位(Emin-E)位,以生成经移位的有效数。 如果确定结果指数E大于或等于Emin,则在步骤206处,移位控制电路26基于由前导零计数电路28确定的未舍入有效数中的前导零的数量的计数来确定前导零计数是零还是非零。如果前导零计数为零(即,经移位的有效数的最高有效位为1),则在步骤208处,移位量为0,因此移位电路24简单地输出与未舍入有效数相同的值作为经移位的有效数。如果前导零计数为非零,则在步骤210处,移位控制电路26控制移位电路24执行未舍入有效数向左移位对应于前导零计数和结果指数与最小指数之间的差值E-Emin中的最小值的位数。向左移位的输出为经移位的有效数。 无论在步骤202至208处用于移位的可变位数如何(可变位数可表示根本没有移位、向右移位或向左移位),在步骤212处,范围识别电路50使用经移位的有效数的高k+1位来确定结果量值x是大于预定范围 如果在步骤212处,范围识别电路50确定经移位的有效数的最高有效位为0,并且经移位的有效数的下个k位中的任何一者或多者也为0,则结果量值x被确定为小于预定范围,并且因此在步骤216处,对于舍入前和舍入后极小度检测两者,多路复用器56输出指示结果是极小的值1作为极小度状态。 如果在步骤212处确定结果量值x在预定范围内,则在步骤218处,多路复用器54确定是正在执行舍入前极小度检测还是舍入后极小度检测,并且如果执行舍入前极小度检测,则在步骤220处将极小度状态设置为1以指示结果是极小的,而无论所使用的舍入模式如何。 如果在步骤218处确定在执行舍入后极小度检测,则多路复用器54选择非门53的输出,该输出取决于由舍入后极小度舍入增量选择电路52选择的舍入增量(ARI),该舍入增量继而取决于舍入模式。在步骤222处,确定使用哪种舍入模式。如果舍入模式为RNE,则在步骤224处,用于舍入后极小度检测的极小度状态输出对应于位R的倒数,位R为最低有效位位置下方的两个位置,该最低有效位位置将为结果值的截断k位有效数的一部分。如果所使用的舍入模式为RU,则在步骤226处,极小度状态对应于位R与所有低位sss的逻辑OR的倒数,使得如果所有低位R、s为0,则极小度状态将为1以指示结果是极小的,并且如果位R和s中的任何一者为1,则结果将不是极小的(这反映了对于RU舍入,将相加的舍入值在对应于R和ssss的所有位位置处具有1,因此,如果这些位中的任何一者为1,则这将导致到G位位置的增量,当考虑到在进行AR极小度舍入时需要理论上向左移位一个位置来确保前导位对于范围内的值为1时G位位置为舍入值的低位,并且因此如果G位位置被增加,则这将导致舍入到非极小值2 应当理解,图5中的流程图示出了可被执行以生成极小度状态的逻辑功能,但电路逻辑不一定需要以所示的顺序执行图5中所示的确切操作,并且对于极小度检测电路来说,以不同的顺序执行相同的操作,或者并行地而不是相继地执行步骤是可接受的。例如,在实践中,可与确定结果量值x是否在预定范围内并行地选择根据步骤222、224、226、228选择的舍入后极小度舍入增量,无论是使用舍入前极小度检测还是舍入后极小度检测,使得在确定结果x在预定范围内之后不需要开始考虑舍入模式。类似地,在确定是执行舍入前极小度检测还是舍入后极小度检测后不需要执行舍入模式的考虑-如图4所示,每次可选择ARI(即使使用BR极小度检测),但如果使用舍入前极小度检测,则多路复用器54将不选择ARI选择电路52的输出。而且,可提供与图4所示的多路复用器不同的多路复用器布置。例如,如果范围确定电路50识别出经移位的有效数表示预定范围内的结果x,则这将是可能的,即选择第一组多路复用器和第一组多路复用器下游的第二多路复用器用于输出作为待使用的极小度状态值,该第一组多路复用器用于针对每种舍入模式在舍入前/舍入后极小度值之间进行选择(除RZ舍入之外,其中对于BR和AR极小度检测两者结果是相同的,因此不需要基于极小度检测类型的明确选择),该第二多路复用器用于基于所用的舍入模式来选择第一组多路复用器的输出中的哪个输出(或者,在RZ舍入的情况下,默认值1以指示结果是极小的)。

在我们获得未舍入有效数之前,注入舍入将舍入注入加到计算中。因为我们无法获得未舍入有效数,所以我们不能使用先前给出的分析。在以下分析中,在注入舍入有效数中的位位置G、R、ssss处的值被标记为G'、R'、s’s’s’s’,以表示注入舍入值可不同于在使用非注入舍入的情况下将针对未舍入有效数生成的原始值G、R、ssss。 加上注入改变了感兴趣的范围,因此感兴趣的范围变为2 对于该范围内的值,这里存在两种感兴趣的注入: RNE:在位G处加一 RU:在G、R和所有s位处加一。 (RZ加0,并且因此注入舍入不会改变结果,因此对于舍入前和舍入后极小度检测两者,当值在范围2 对于RNE舍入,在位G处加一不改变较低阶位中的任一者,并且特别地不改变R,因此R’=R并且s’s’s’s’=ssss。然而,注入确实改变了位置G处的位,其中新的BR舍入增量=BRI=G。由于我们没有G,所以我们检查G’=G+1。BRI则由~G'给出。可将BR极小度状态设置为等于BRI。即,对于RNE舍入和BR极小度,如果G'=1,则这指示如果未执行注入舍入,G的未舍入值将为0,因此对于范围2 对于RU舍入,加上注入常数给出总和 sum[5:0]=L’G’R’s’s’s’=LGRsss+11111 (在实践中可存在多于或少于3个s位,每个位具有其对应的1个注入)。 我们可通过注意到舍入增量等同于为非零的G、R或s位中的任一者,这继而等同于~&sum[4:0],来计算用于RU舍入的BRI。如果G、R、s全部为0,则用于RU舍入的11111舍入值的相加将导致G'、R'、s's'全部变为1,并且如果注入舍入值在范围2^Emin+ulp>x≥2^Emin内,这意味着由于注入舍入,没有任何比G更有效的位的改变,因此如果尚未执行注入舍入,则结果将为2 对于舍入后极小度检测,可如下证明待用于设置RNE和RU舍入的AR极小度状态的关系: 断言:如果RNE和注入舍入结果为最小正规值,则AR_tiny=1<=>G'=R’=0。 证明:首先假设未舍入结果x为正规的(非极小):

显然,AR_tiny=0并且没有进位到lsb,这意味着G=0并且G'=1。因此,如果注入舍入结果为最小正规值并且G'=1,则舍入后极小度状态为0,因为结果在舍入后不是极小的。 现在,假设未舍入结果x为次正规的,同时仍生成最小正规值作为注入舍入结果。我们还可假设G=1;否则没有增量:

如果G'=1,则G=0,并且舍入注入不改变高位,因此假定我们知道注入舍入结果实际上为最小正规值(1.000…0G’R’s’s’s’),则G'不可能为1并且结果是极小的。 因此,如果G'=1,则AR_tiny=0。 这意味着对于舍入注入结果为最小正规值的情况,对于AR_tiny状态为1,G'必须为0。 在这种情况下:

如果G'=0,则G=1,并且预注入值为0.11…11Rsss。进行舍入后极小度检测意味着我们假设指数为无界的,所以我们进行(理论)向左移位以规格化为1.1…11Rsss,然后应用如表4中的舍入,但现在最低有效和保留位置处的位为G和R而不是L和G-即对于舍入后极小度检测舍入我们可视为AR_L=G和AR_G=R。从表4,当舍入模式为RNE时,我们知道如果(AR_L&AR_G)|(AR_G&AR_S),我们向上舍入。由于我们已推断出以上G=1,这简化为(1&R)|(R&S),其等同于R。因为注入不改变R的值,所以R'=R。 因此, 如果R'=AR_G=0,则不存在ARI(舍入后检测舍入增量),并且因此结果在舍入后保持极小。 如果R'=AR_G=1,则ARI=1,因此结果不是极小的。 这意味着,对于RNE舍入,如果(并且仅如果)G'=0且R'=0,则AR_tiny=1。 断言:如果RUP和舍入结果为最小正规值,则AR_tiny=1<=>G'=0。 证明:我们可通过分析G=0、Rsss=0的不同可能性来分解该证明,分别作为下面的情况1到4。 情况1:G=0,Rsss=0 如果G、R、s全部为零,则舍入注入将导致G’、R’s’s’s’全部为一。对于其中注入舍入结果大于或等于2 即,如果G’=1&(&sum[3:0])=1,则AR_tiny=0。 这也从以下观察得出:如果BR_tiny=0,则AR_tiny总是0。 情况2:G=0&Rsss!=0 在情况2中,如果Rss中的任一者为非零,则加上1111将意味着位R’s’s’s’中的至少一者为0(如果Rsss为0,则R’s’s’s’只能为1111)。因此,对于情况2,&sum[3:0]=0。 对于在G、R、ssss中的任一者非零的该范围中的结果,只有当ARI极小度增量引起溢出时,AR_tiny才为0。这可从以下推理中看出。 如果G、R、sss中的任一者为非零,则在注入舍入中加上11111将导致进位到注入舍入结果的L位,因此在这种情况下,原始未舍入结果(在不存在注入舍入的情况下)将必须为次正规的以使注入舍入值落在预定范围2 由于预注入舍入值将为次正规的并且因此具有形式0.1111…,如果将AR极小度检测舍入应用于预注入舍入次正规结果,则将执行理论规格化(向左移位一位)以提供最高有效位1,然后对于RU舍入,将在AR_G、AR_R和AR_s处,即在来自未舍入结果的位R、s、s、s处加1:

(注意,G”(在(理论)AR舍入相加之后的G位置处的值)与上文所示的G'(其为在规则注入舍入之后形成的G位置处的值)不同)。 如果不存在由AR舍入相加引起的溢出,则在AR极小度舍入增量之后的最高有效“1”将保持在对应于小于2 因此,当注入舍入值在预定范围内,并且G、R、sss中的任一者为非零时,如果ARI极小度增量引起溢出,则AR_tiny只能为0。 对于引起溢出的ARI(在1位向左移位之后),必须设置AR_L(G)位(否则由舍入增量引起的进位将不会传播超过位G)。因此,当G=0且结果位于预定范围内时,AR_tiny总是为1。 由于注入舍入,我们只有G'可用于分析,而不是G。我们可推断出G=0&Rsss!=0时G'的值是多少。由于R或s位中的至少一者为一,所以在注入舍入之后将存在到G位位置的进位输入。G’=G+1+cin(1来自用于RU舍入的注入舍入常数11111,并且cin来自在所有Rsss位位置处1的相加)。由于G=0并且cin=1,所以G’=0+1+1=0。 因此,如果G’=0&(&sum[3:0])=0,则AR_tiny=1。 情况3:G=1&Rsss=0 对于在G、R、ssss中的任一者非零的预定范围内的结果,只有当ARI极小度增量引起溢出时,AR_tiny才将为0(出于与对于情况2给出的相同的原因)。 在1位向左移位(规格化)之后,由于R&s位全为零,所以不能存在到位G”的舍入增量,因此不存在溢出的可能性,即ARI=0&AR_tiny=1。 在G=1并且Rsss=0的情况下,我们可推断出在注入舍入之后G'的值将是多少。由于R|S为零,(&sum[3:0])=1&在舍入注入期间不存在到G位位置的进位输入。 这意味着在情况3中G’=0,因为G’=G+1+cin=1+1+0=0。 因此,当G’=0&(&sum[3:0])=1时,AR_tiny=1。 情况4:G=1&Rsss!=0 由于R|S为非零,(&sum[3:0])=0,原因与对于情况2所解释的相同。 对于该范围中的结果,同样,只有当ARI极小度增量引起溢出时,AR_tiny才将为0。在1位向左移位(规格化以将指数视为无界)之后,由于R&s位不全为零,因此将存在舍入增量,即ARI=1。由于G=1,该增量可传播到结果并且将引起溢出,使得AR_tiny=0。 现在我们推断出在情况4中G'的值是多少。对于情况4,在舍入注入之后G’=1(因为G’=G+1+cin=1+1+1=1)。 即当G’=1&(&sum[3:0])=0时AR_tiny=0。 查看所有四种情况,我们看到如果结果位于预定范围内,并且舍入模式为RU,则AR_tiny=1当且仅当G'=0。 综上所述,当使用注入舍入时,用于确定预定范围内的值的极小度状态的舍入前增量(BRI)和舍入后增量(ARI)如表8中所列:

在表9中列出了用于基于经移位的注入舍入结果确定结果量值是否在预定范围内以及用于确定极小度状态的测试:

在实践中,图6示出了当使用注入舍入时用于组合的舍入前和舍入后极小度检测的电路22的电路逻辑。在该示例中,浮点处理电路20包括浮点处理运算电路70,该浮点处理运算电路执行处理运算本身和由注入舍入值选择电路72根据所使用的舍入模式选择的注入舍入值的相加两者。如果正在执行RZ舍入,则注入舍入值为0,如果正在使用RNE舍入,则注入舍入值对应于在截断之后k位有效数的低位下方一个位置的位位置处的位1,或者如果正在使用RU舍入,则注入舍入值对应于在低于有效数将被截断的点的所有位位置处具有位1的值。浮点处理运算可为例如相加或相乘,其可涉及将两个或更多个操作数相加,或者将一定数量的部分乘法乘积相加,并且因此注入舍入值的相加可被折叠为已作为浮点处理运算本身的一部分而执行的相同的相加或多个相加,使得由处理逻辑70输出的有效数为已在舍入中考虑到的注入舍入有效数,并且因此在该示例中,浮点处理电路20不需要舍入值选择电路30和加法器32来检查结果有效数的位并且加上另外的舍入增量。然而,浮点处理电路20包括移位电路24、移位控制电路26和前导零计数电路28,以执行规格化移位,从而确保如果结果指数E小于最小正规指数或者前导零计数为非零,则应用向右移位或向左移位,以确保将有效数调整为具有前导1的正规格式或者具有前导0的次正规格式,后者对应于在所使用的浮点格式中具有支持正规浮点数的最小值的指数。经移位的注入舍入有效数的最高k位可被截断并作为浮点运算的总体浮点结果输出,而不需要任何进一步舍入。丢弃前导位以产生结果浮点值的k-1位所存储的小数。 同时,极小度检测电路接收全注入舍入有效数(没有截断),并且包括范围识别电路80、舍入后极小度舍入增量选择电路82、舍入前极小度舍入增量选择电路84和多路复用器86、88。 图6的注入舍入示例中的范围识别电路80与图4的范围识别电路50的不同之处在于,感兴趣的预定范围不同,但以类似的方式,范围识别电路识别由移位器24输出的经移位的有效数是大于预定范围、在预定范围内还是小于预定范围。在这种情况下,感兴趣的范围是2 同时,舍入后极小度舍入增量选择电路82和舍入前极小度舍入增量选择电路84根据对经移位的有效数的位G'、R'和低位s'的分析来进行舍入增量的舍入模式特定选择,这些位G'、R'和低位s'位于当经移位的有效数被截断以生成浮点结果值时将被丢弃的位位置处。用于选择极小度舍入增量的函数对于舍入前和舍入后极小度舍入增量选择是不同的,如上表9所示,并且在下图7的流程图中进一步讨论。由电路84选择的舍入前极小度舍入增量(BRI)被输出到多路复用器86的一个输入端,并且舍入后极小度舍入增量(ARI)的反转版本被输出到多路复用器86的另一个输入端。如果要对当前运算执行舍入前极小度检测,则多路复用器86选择BRI,并且当要执行舍入后极小度检测时,则选择ARI的反转版本。 当范围识别电路80识别出结果量值大于预定范围时,最终多路复用器88输出值0作为极小度状态,以指示非极小结果,并且当确定结果量值小于预定范围时,输出极小度状态1,以指示极小结果。对于舍入前和舍入后极小度检测两者都是这种情况。另一方面,在预定范围内,多路复用器86的输出被输出为极小度状态。 图7是示出在使用注入舍入的情况下用于执行极小度检测的方法的流程图。同样,应当理解,这示出了步骤的一种可能的顺序,但可彼此并行地或以不同的顺序执行这些步骤中的一些步骤。 在步骤250处,浮点处理电路20执行浮点运算以产生结果指数E和注入舍入有效数,其中注入舍入值的相加已作为浮点运算本身的一部分执行。这可根据任何标准注入舍入技术来完成。 步骤252、254、256、258、260与图5的对应步骤202、204、206、208、210相同,其选择性地应用向右移位或向左移位,以规范化该注入舍入有效数或者将其置于适当的次正规形式,这取决于结果指数E与所使用的浮点格式中所支持的最小正规指数Emin的比较以及注入舍入有效数的前导零计数。这些步骤的结果被称为经移位的有效数(尽管认识到在步骤258处移位量可为0,并且在该情况下经移位的有效数简单地等于注入舍入有效数)。 在步骤262处,范围识别电路80基于经移位的有效数的最高k位来识别结果量值x是大于预定范围2 如果经移位的有效数的最高有效位为1并且经移位的有效数的下个k-1位中的任一者为非零的,则结果量值x大于预定范围,并且在步骤264处,浮点运算的结果被确定为不是极小的,并且因此对于舍入前和舍入后极小度检测两者,极小度状态为0。 如果在步骤262处,范围识别电路80识别出经移位的有效数的最高有效位为0,则结果量值x小于预定范围,并且因此对于舍入前和舍入后极小度检测两者,极小度状态被设置为1以指示结果是极小的。 如果在步骤262处,范围识别电路80识别出经移位的有效数的最高有效位为1并且后跟k-1个零,则结果量值x被确定在预定范围内,并且因此在这种情况下,极小度状态取决于由舍入前和舍入后极小度舍入增量选择电路84、82进行的分析。在步骤268处,多路复用器86确定是正在执行舍入前极小度检测还是舍入后极小度检测。 如果正在执行舍入后极小度检测,则在步骤270处,极小度状态取决于所使用的舍入模式。如果舍入模式为RNE,则在步骤272处,舍入后极小度舍入增量选择电路82将舍入后极小度舍入增量ARI确定为G'和R'的逻辑OR,G'和R'为当有效数被截断以形成浮点结果时将被丢弃的部分内最高有效位位置处的两个位,并且极小度状态根据该ARI的倒数来设置,因此,如果G'和R'均为0,则结果是极小的,而如果G'或R'为1,则结果不是极小的。 如果待使用的舍入模式为RU,则在步骤274处,对于舍入后极小度检测,ARI等于位G’,G’为经移位的有效数被截断以形成浮点结果的点下方的一个位置,并且极小度状态等于G’的倒数,使得如果位G’为1,则结果不是极小的,而如果G’为0,则结果是极小的。 如果舍入模式在步骤270处被确定为RZ舍入,则在步骤276处确定结果不是极小的,因此多路复用器88将输出值0。 另一方面,如果在步骤268处确定待使用舍入前极小度检测,则在步骤280处极小度状态取决于确定待使用的舍入模式。在步骤282处,如果正在使用RNE舍入,则极小度状态对应于位G'的倒数,位G'是截断中丢弃的部分的最高有效位。如果所使用的舍入模式为RU舍入,则在步骤284处,极小度状态对应于在逻辑逐位AND运算中组合位G'和低于G'的经移位的有效数的所有位的结果的倒数。这意味着,如果在截断中丢弃的部分内的所有位为1,则极小度状态为0以指示结果不是极小的,而如果低位G'、R'和s'中的任一者为0,则结果将被指示为极小的。 另一方面,在步骤286处,如果所使用的舍入模式为RZ,则确定结果不是极小的。 因此,利用这种方法,即使在使用注入舍入时,仍有可能提供组合的极小度检测电路22,其对于舍入前和舍入后极小度检测两者,通过分析经移位的有效数的位利用相对简单的布尔逻辑集合来计算极小度状态,而不需要除已作为浮点运算70本身的一部分而执行的用于注入舍入的相加以外的任何舍入增量相加。这提供了能够在共享数据路径中执行两种类型的极小度检测的快速极小度检测。 本文所描述的概念可体现于用于制造体现所描述概念的装置的计算机可读代码中。例如,计算机可读代码可在半导体设计和制造过程的一个或多个阶段(包括电子设计自动化(EDA)阶段)使用,以制造包括体现这些概念的装置的集成电路。以上计算机可读代码可另外地或另选地使得能够对体现本文所描述概念的装置进行定义、建模、模拟、验证和/或测试。 例如,用于制造体现本文所描述概念的装置的计算机可读代码可体现在定义这些概念的硬件描述语言(HDL)表示的代码中。例如,代码可定义用于定义体现这些概念的装置的一个或多个逻辑电路的寄存器传送级(RTL)抽象。代码可用Verilog、SystemVerilog、Chisel或VHDL(超高速集成电路硬件描述语言)以及诸如FIRRTL的中间表示来定义体现装置的一个或多个逻辑电路的HDL表示。计算机可读代码可提供使用系统级建模语言诸如SystemC和SystemVerilog体现概念的定义或概念的其他行为表示,这些行为表示可由计算机解译以使得能够对概念进行模拟、功能和/或形式验证和测试。 附加地或另选地,计算机可读代码可以体现一个或多个网络列表的计算机可读表示。可以通过向RTL表示应用一个或多个逻辑合成过程来生成一个或多个网络列表。另选地或另外地,一个或多个逻辑合成过程可从计算机可读代码生成待加载到现场可编程门阵列(FPGA)中以将FPGA配置为体现所描述概念的位流。FPGA可出于在制造集成电路之前验证和测试概念的目的被部署,或者FPGA可直接部署在产品中。 计算机可读代码可包括用于制造装置的代码表示的混合,例如包括RTL表示、网表表示或在半导体设计和制造过程中用于制造体现本发明的装置的另一计算机可读定义中的一者或多者的混合。另选地或另外地,概念可在半导体设计和制造过程中用于制造装置的计算机可读定义和定义一旦制造就将由所定义装置执行的指令的计算机可读代码的组合中定义。 此类计算机可读代码可设置在任何已知的暂态计算机可读介质(诸如通过网络进行的有线或无线代码传输)或非暂态计算机可读介质诸如半导体、磁盘或光盘中。使用计算机可读代码制造的集成电路可包括诸如以下中的一者或多者的部件:中央处理单元、图形处理单元、神经处理单元、数字信号处理器或单独或共同体现概念的其他部件。 在本申请中,字词“被配置为…”用于意指装置的元件具有能够执行所限定的操作的配置。在该上下文中,“配置”意指硬件或软件的互连的布置或方式。例如,该装置可具有提供所限定的操作的专用硬件,或者可对处理器或其他处理设备进行编程以执行该功能。“被配置为”并不意味着装置元件需要以任何方式改变以便提供所限定的操作。 虽然本文已结合附图详细描述了本发明的示例性实施方案,但应当理解,本发明并不限于那些精确的实施方案,并且在不脱离所附权利要求书所限定的本发明的范围的前提下,本领域的技术人员可在其中实现各种变化和修改。

- 一种具有极小偏心度的高利用率不锈钢焊条

- 一种新型高对比度第三极小液晶显示屏