一种实现一条指令对多组并行处理的数据处理方法

文献发布时间:2023-06-19 19:00:17

技术领域

本发明涉及多媒体计算技术领域,特别涉及一种实现一条指令对多组并行处理的数据处理方法。

背景技术

随着互联网的普及,图片、音频、视频等多媒体应用迅速崛起,为应对多媒体领域密集的计算需求,对处理器硬件计算能力的需求越来越高。而传统的通过提高主频和增加硬件流水线级数来提升计算能力的方式逐渐达到极限,硬件设计者们开始考虑通过并行手段来提高计算能力,于是出现了多机结构、多核结构、SIMD结构等。其中,SIMD是一种能高效实现并行处理的扩展指令集,即使用一条指令同时对一组数据执行相同的操作从而实现对数据并行处理的技术。

多媒体应用中通常存在大量同质、独立的访存和计算操作,且使用的数据类型一般都很窄(如图形系统中颜色数据位宽为8位;音频采样位宽通常为8位或16位)。SIMD扩展指令集具有独立的长位宽向量寄存器(64/128/256/512/1024......),允许将原来需要多次装载的连续内存地址数据一次性装载到向量寄存器中,并使用分裂模式将长的向量寄存器当做多个独立的窄位宽元素(通常支持的数据类型包括有符号或者无符号的8位、16位、32位和64位的整型数据或者32位的单精度浮点数据),通过一条SIMD扩展指令实现对SIMD向量寄存器中所有数据元素的并行处理,每条指令可并行处理的数据个数由向量寄存器的长度和数据类型共同决定,如一个128位的向量寄存器每次可同时处理4个32位的数据或8个16位的数据或16个8位的数据,并且随着SIMD矢量寄存器长度变长,指令能够同时处理的数据量也越来越大,从而获得更高的加速性能。这种执行方式非常适合处理计算密集、数据相关性少的音视频解码等多媒体程序。

SIMD扩展部件仅需要在原来标量部件的基础上复制几份同样的处理单元,不需要增加太多的额外硬件,就能对多媒体等特定应用带来显著的性能提升,因此SIMD已经成为当代处理器必备的扩展部件,如Intel陆续推出的MMX/SSE/AVX/FMA扩展指令和ARM的NEON扩展指令等。

SIMD扩展指令在实现机制上与普通的标量指令没有太多差别。在SIMD扩展指令集上均可以实现标量指令集支持的各种操作,如存取操作、算数运算、逻辑运算、比特操作,以及常用的饱和处理、四舍五入、条件执行等功能。同时,随着计算机技术的发展,各类新型的计算需求不断出现,SIMD扩展指令集支持的计算功能也在不断丰富,如今很多处理器支持的SIMD扩展指令达上百条之多。很多指令的设计初衷早已跨越多媒体应用处理范畴,延伸到信号处理、科学计算等需要高性能计算能力的领域。

例如,近年来随着机器学习等人工智能技术的飞速发展,涉及卷积运算、矩阵乘法等点积操作的应用越来越多,因此各主流处理器的SIMD扩展均增添了针对点积运算的相关指令,来实现对人工智能领域相关应用的高效处理。

如上文中介绍,对于近年来出现的人工智能领域的卷积运算和矩阵乘法等相关计算需求,SIMD扩展指令集中的点积运算指令能够高效的实现对此类应用的加速运行。下面将举例介绍SIMD点积运算指令的具体操作和实现。考虑到卷积运算最终均是转化为矩阵的乘法运算,因此本文以矩阵乘法的实例来分析介绍点积运算指令的操作。

假设参与乘法运算的两个矩阵分别为矩阵A(大小为16*16)和矩阵B(大小为16*16),矩阵中数据元素大小均为8位。根据矩阵乘法的运算规则,计算过程就是把矩阵A中每一行的元素(16个元素)与矩阵B中每一列的元素(16个元素)对应相乘,然后把乘积结果相加,乘累加的结果作为结果矩阵的一个元素。当完成对矩阵A中所有行与矩阵B中所有列的全部可能组合情况的计算之后,即可得到一个16*16大小的结果矩阵。矩阵A每一行的16个元素与矩阵B每一列的16个元素对应相乘并累加的过程即对应了两个向量的点积运算操作,因此可以用点积运算指令来实现该过程。

为了实现对上述矩阵乘法运算中16个8位数据乘累加运算的并行处理,用于加载存放数据的矢量寄存器的大小只需达到128位即可。考虑到当前SIMD扩展指令为了能够实现更高的并行度,矢量寄存器的大小已经达到512位甚至1024位,因此本文以当前比较主流的512位的矢量寄存器大小为例来说明点积运算的实现过程。对于8位的数据来说,512位的矢量寄存器可同时支持对64个数据的并行处理,因此SIMD指令对应的扩展硬件部件包含64个并行计算单元。

以矩阵A中第一行的16个元素a(1,1)~a(1,16)与矩阵B中第二列的16个元素b(1,2)~b(16,2)之间的点积运算为例,把矩阵A中元素和矩阵B中元素分别加载到矢量寄存器vrp和vrs,点积计算结果存储到目标寄存器vrd中,即完成了矩阵A一行数据与矩阵B一列数据的点积计算。因为此运算过程只需处理两组16个8位数据的乘累加计算,所以分别只占用了512位矢量寄存器vrp和vrs的四分之一的空间,剩余的寄存器空间进行零填充,对应的硬件计算单元处理零操作。

按照上述过程依次加载矩阵A的每一行数据与矩阵B中的每一列数据到矢量寄存器中参与计算,完成矩阵A中所有行与矩阵B中所有列的全部可能组合的计算,即可得到最终结果矩阵。

如上文中对当前技术方案的描述,当前SIMD扩展指令中的点积运算指令通过对参数特殊的并行处理,能够实现对卷积运算与矩阵乘法运算等相关的人工智能领域应用的高效运行。同时伴随着SIMD矢量寄存器的宽度越来越大,SIMD指令能够支持并行处理的数据量也越来越大,进而能得到更高的加速性能。

但是随着SIMD矢量寄存器宽度逐渐变大,即SIMD扩展指令支持的并行度越来越高,当需要并行处理的元素个数少于一条SIMD扩展指令所能支持的并行操作的数据个数时,则会出现硬件资源利用率低,计算性能降低的问题。

如上文例子中,矢量寄存器的宽度为512位,对于8位的数据元素,可同时对64个数据元素进行并行处理,即SIMD矢量指令对应的扩展硬件包含64个计算单元。但需要处理的操作为16*16大小的矩阵A与16*16大小的矩阵B的乘法运算,该矩阵乘法运算最终拆分为多组包含16个元素的一维向量的点积运算,即每次SIMD点积运算指令需要处理的数据仅为16个(两组),只用到四分之一的寄存器存储空间和计算单元,而剩余的矢量寄存器空间则如上文例子中描述进行零填充,对应的计算单元则处理零操作,这将造成硬件资源的浪费,硬件资源的利用率仅为四分之一,进而导致计算性能下降。

此外,现有技术中常用的术语包括:

SIMD:指令流多数据流(single instruction multiple data),是一种能高效实现并行处理的扩展指令集;

vrp:SIMD指令中的一号源操作数;

vrs:SIMD指令中的二号源操作数;

vrd:SIMD指令中目的操作数。

发明内容

本申请是基于对当前SIMD扩展指令中点积运算指令具体操作的分析,对于需要并行处理的数据个数小于一条SIMD扩展指令所能支持的并行操作的数据个数而造成的硬件资源浪费的问题,本申请创新性的提出了一种分段式的矢量指令类型,通过对矢量寄存器和指令所能支持操作数进行分段处理,进而实现一条指令对多组需要并行处理的数据的并行处理,不仅能提高硬件资源的利用率,同时也提升了指令的计算效率。

具体地,本发明提供一种实现一条指令对多组并行处理的数据处理方法,所述方法包括一种分段SIMD矢量指令定义为SMAC指令,其是基于SIMD指令集设计一种分段指令,包括:根据计算需求中需要并行处理的数据的个数和数据的大小对矢量寄存器进行分段处理,每个段内处理一组需要并行处理的数据;对需要两两组合处理的数据组,采用对其中一个数据集的每个组数据逐一复制到同一个矢量寄存器的每个段的方式,实现对数据加载和运算的处理。

由于卷积运算最终均是转化为矩阵的乘法运算,所以所述方法以矩阵乘法分析点积运算指令的操作,对高位宽的SIMD矢量寄存器进行分段处理,分段的数目由SMAC指令需要处理的数据类型和需要并行处理的数据的个数来决定;每个段具有独立的矢量寄存器片段和对应的计算单元,且段内进行独立的一组数据的并行计算,各段之间不存在计算关系;

通过这种分段的处理,对于需要处理的数据个数远小于矢量寄存器所支持并行计算的数据个数的情况,所述SMAC指令,每条指令一次最多能处理512bit即16个word数据,指令名称的基本格式为SR

所述点积运算指令的设计是将多个融合乘法加法运算组合成单个步骤,仅一条指令即可实现两组数据中每对数据元素两两相乘并把乘积结果进行求和,然后把求和结果存入相应寄存器,即同时实现了两个SIMD矢量寄存器之间的运算和各寄存器中各元素之间的运算。

参与乘法运算的两个矩阵分别设为矩阵A与矩阵B,矩阵中的数据元素大小均为无符号byte类型,A大小为m*p,其中m=16,p=16,矩阵

设占用三个源矢量寄存器vrp、vrs、new vrp和一个目的矢量寄存器vrd,寄存器的位宽均为512位;

根据分段SMAC指令的设计,针对计算需求,把512位的矢量寄存器根据实际待处理的数据决定分为4段,每段均能够实现对一组向量数据的点积运算。

所述方法进一步包括以下步骤:

S1,同时加载矩阵A中的四行数据到矢量源寄存器vrp中,同理加载矩阵B中的四列数据到矢量源寄存器vrs中,矩阵A中的每行数据和矩阵B中的每列数据分别占用矢量寄存器中的一个段;

S2,从矢量源寄存器vrp中选择一个段内的数据,拷贝到一个新的矢量寄存器newvrp中的四个段中;

S3,把矢量寄存器new vrp和vrs中对应的段内的数据元素做点积操作,并把计算结果存储到矢量寄存器vrd对应的段中;

S4,按照上述步骤S1-S3依次把矢量源寄存器vrp中每一个段内的数据拷贝到矢量寄存器new vrp的四个段中,分别与矢量寄存器vrs中对应段的数据元素做点积运算,最终即可完成初始加载的矩阵A中的四行数据与矩阵B中的四列数据的所有可能组合的运算。

由此,本申请的优势在于:

针对当前SIMD扩展点积运算指令计算过程中存在的硬件资源利用率低的缺陷,本申请提出一种创新的分段处理的指令类型,对指令操作的数据和矢量寄存器进行分段处理,可同时完成对多组运算数据的矢量运算,提高硬件资源的利用率,提升指令计算效率。

附图说明

此处所说明的附图用来提供对本发明的进一步理解,构成本申请的一部分,并不构成对本发明的限定。

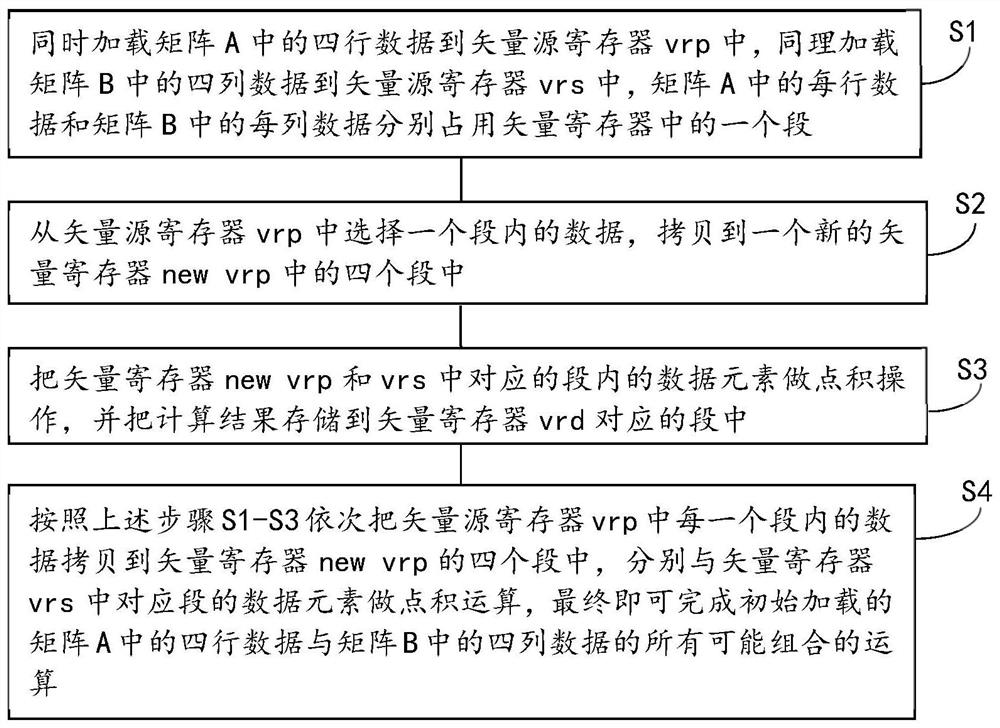

图1是本发明方法的流程图。

图2是本发明实施例中将矢量寄存器分为四段实现运算的示意图。

具体实施方式

为了能够更清楚地理解本发明的技术内容及优点,现结合附图对本发明进行进一步的详细说明。

本发明涉及一种实现一条指令对多组并行处理的数据处理方法,对于需要并行处理的数据个数小于一条SIMD扩展指令所能支持的并行操作的数据个数而造成的硬件资源浪费的问题,本申请创新性的提出了一种分段式的矢量指令类型,通过对矢量寄存器和指令所能支持操作数进行分段处理,进而实现一条指令对多组需要并行处理的数据的并行处理,不仅能提高硬件资源的利用率,同时也提升了指令的计算效率。

所述方法中,参与乘法运算的两个矩阵分别设为矩阵A与矩阵B,矩阵中的数据元素大小均为无符号byte类型,A大小为m*p,其中m=16,p=16,矩阵

如图1所示,所述方法进一步包括以下步骤:

S1,同时加载矩阵A中的四行数据到矢量源寄存器vrp中,同理加载矩阵B中的四列数据到矢量源寄存器vrs中,矩阵A中的每行数据和矩阵B中的每列数据分别占用矢量寄存器中的一个段;

S2,从矢量源寄存器vrp中选择一个段内的数据,拷贝到一个新的矢量寄存器newvrp中的四个段中;

S3,把矢量寄存器new vrp和vrs中对应的段内的数据元素做点积操作,并把计算结果存储到矢量寄存器vrd对应的段中;

S4,按照上述步骤S1-S3依次把矢量源寄存器vrp中每一个段内的数据拷贝到矢量寄存器new vrp的四个段中,分别与矢量寄存器vrs中对应段的数据元素做点积运算,最终即可完成初始加载的矩阵A中的四行数据与矩阵B中的四列数据的所有可能组合的运算。

所述点积运算指令的设计原则就是将多个融合乘法加法运算组合成单个步骤,例如,在两个128位SIMD矢量寄存器上执行四个32位元素点积a0×b0+a1×b1+a2×b2+a3×b3,操作具有单周期吞吐率。点积运算指令区别于矢量乘累加运算指令的操作在于:仅一条指令即可实现两组数据中每对数据元素两两相乘并把乘积结果进行求和,然后把求和结果存入相应寄存器,即同时实现了两个SIMD矢量寄存器之间的运算和各寄存器中各元素之间的运算。

本申请提出的创新性的分段SIMD指令命名为SMAC(段乘加)指令,下面介绍该指令的具体操作和实现方法:

SMAC指令的主要设计思想即对高位宽的SIMD矢量寄存器进行分段处理,分段的数目由指令需要处理的数据类型和需要并行处理的数据的个数来决定。每个段具有独立的矢量寄存器片段和对应的计算单元,且段内进行独立的一组数据的并行计算,各段之间不存在计算关系。通过这种分段的处理,对于上文中需要处理的数据个数远小于矢量寄存器所支持并行计算的数据个数的情况,使用SMAC指令可实现单条指令在每个段内处理一组需要并行处理的数据、多个段同时处理多组需要并行处理的数据的操作,可高效提升硬件资源的利用率,提升单指令计算性能。

下面通过附图举例方式说明SMAC指令的具体实现过程:

如图2中所示,为了与当前技术方案的操作方法形成对比,此处同样以矩阵的乘法运算为例来说明,与上文例述中一样,参与乘法运算的两个矩阵分别为矩阵A(大小为16*16)与矩阵B(大小为16*16),矩阵中的数据元素大小均为8位,矩阵A与矩阵B的乘法操作最终转化为多组包含16个8位数据元素向量的点积运算。三个源矢量寄存器vrp、vrs、new vrp和目的矢量寄存器vrd的位宽均为512位。

根据SMAC指令的设计思路,针对上述计算需求,可把512位的矢量寄存器分为四段,每段均可以实现对一组向量数据的点积运算。具体的实现可分为以下几个步骤:

S1:同时加载矩阵A中的四行数据到矢量源寄存器vrp中,同理加载矩阵B中的四列数据到矢量源寄存器vrs中,矩阵A中的每行数据和矩阵B中的每列数据分别占用矢量寄存器中的一个段。

S2:从矢量源寄存器vrp中选择一个段内的数据,拷贝到一个新的矢量寄存器newvrp中的四个段中。

S3:把矢量寄存器new vrp和vrs中对应的段内的数据元素做点积操作,并把计算结果存储到矢量寄存器vrd对应的段中。

S4:按照上述步骤S1-S3依次把矢量源寄存器vrp中每一个段内的数据拷贝到矢量寄存器new vrp的四个段中,分别与矢量寄存器vrs中对应段的数据元素做点积运算,最终即可完成初始加载的矩阵A中的四行数据与矩阵B中的四列数据的所有可能组合的运算。

本发明中创新性的提出分段的处理方式,可并行的处理矩阵A中多个行数据与矩阵B中多个列数据的点积运算,高效的提升了硬件计算资源的利用率,同时提高计算性能。如本例中硬件计算资源利用率达到百分之百,并且单周期可以处理四组数据的运算,指令的单周期吞吐率显著增大。

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明实施例可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种网络处理器微引擎的多发射指令并行处理方法及装置

- 一种网络处理器微引擎的多发射指令并行处理方法及装置