存储器器件

文献发布时间:2024-01-17 01:17:49

技术领域

本申请的实施例涉及一种存储器器件。

背景技术

集成电路处理器需要从存储器获取数据。动态随机存取存储器(DRAM)是经常使用的。然而,DRAM在存取速度和功耗方面不够高效。数据存取的低效率被称为“存储器墙”。高性能计算处理器必须克服“存储器墙”。

发明内容

根据本申请的实施例的一个方面,提供了一种存储器器件,包括:写入位线和读取位线,在第一方向上延伸;第一写入字线和第一读取字线,在垂直于所述第一方向的第二方向上延伸;以及第一存储器单元,所述第一存储器单元包括:第一写入晶体管,所述第一写入晶体管包括:第一栅极,连接到所述第一写入字线;第一源极/漏极,连接到所述写入位线;和第二源极/漏极,连接到第一数据储存节点;以及第一读取晶体管,所述第一读取晶体管包括:第二栅极,连接到所述第一数据储存节点;第三源极/漏极,连接到所述读取位线;和第四源极/漏极,连接到所述第一读取字线。

根据本申请的实施例的另一个方面,提供了一种存储器器件,包括:存储器阵列,所述存储器阵列包括:多个存储器单元对,排列成多个列和多个行,其中多个存储器单元对中的每个存储器单元对包括:第一存储器单元,所述第一存储器单元包括:第一写入晶体管,被配置为响应于第一写入信号将第一输入数据写入到第一数据储存节点;第一读取晶体管,被配置为响应于所述第一数据储存节点上的所述第一输入数据和第一读取信号向读取位线输出第一输出数据;以及第二存储器单元,所述第二存储器单元包括:第二写入晶体管,被配置为响应于第二写入信号将第二输入数据写入到第二数据储存节点;和第二读取晶体管,被配置为响应于所述第二数据储存节点上的所述第二输入数据和第二读取信号向所述读取位线输出第二输出数据。

根据本申请的实施例的又一个方面,提供了一种存储器器件,包括:写入位线和读取位线,在第一方向上延伸;写入字线和读取字线,在垂直于所述第一方向的第二方向上延伸;存储器单元,所述存储器单元包括:写入晶体管,包括:第一栅极,连接到所述写入字线;第一源极/漏极,连接到所述写入位线;和第二源极/漏极,连接到数据储存节点;以及读取晶体管,包括:第二栅极,连接到所述数据储存节点;第三源极/漏极,连接到所述读取位线;和第四源极/漏极,连接到所述读取字线;电源供电节点,所述电源供电节点为VDD节点或VSS节点;以及伪晶体管,所述伪晶体管包括:第三栅极,连接到所述电源供电节点;和第五源极/漏极,连接到所述数据储存节点。

附图说明

当结合附图进行阅读取时,从以下详细描述可最佳理解本发明的各个方面。应该强调,根据工业中的标准实践,各个部件未按比例绘制并且仅用于说明的目的。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

图1图示了根据一些实施例的存储器阵列的示意图。

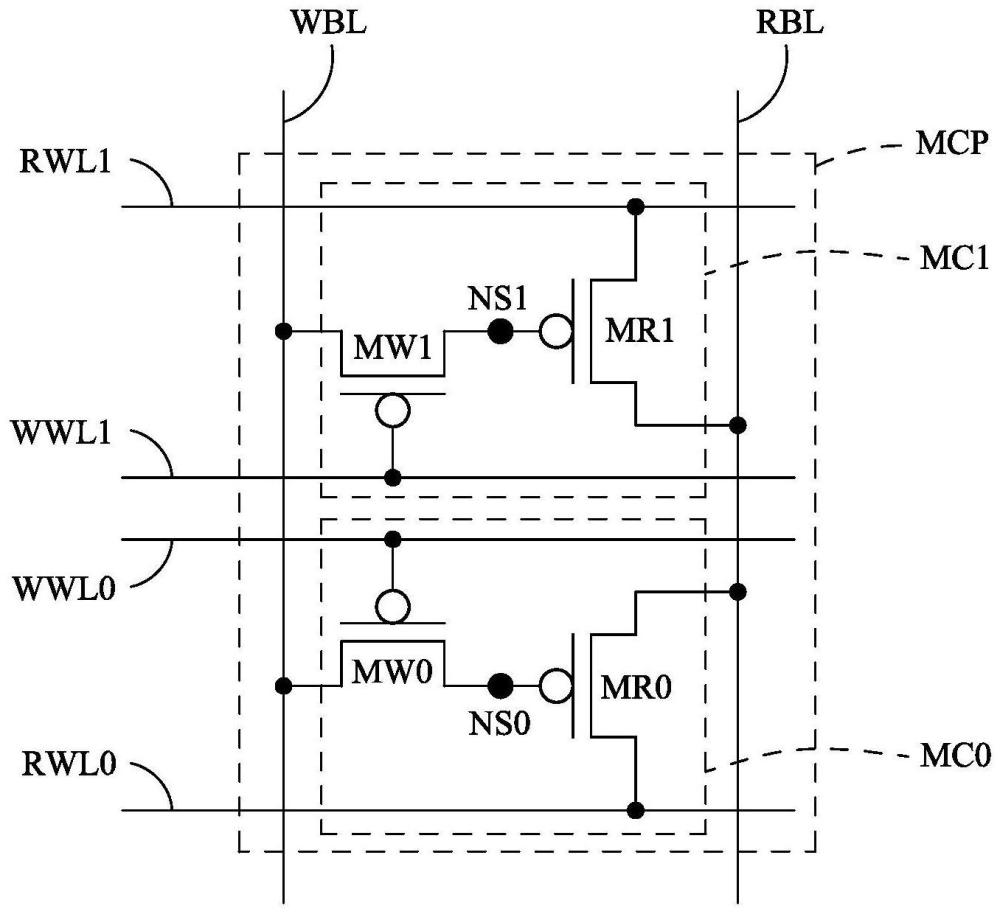

图2A图示了根据一些实施例的存储器单元对的电路图。

图2B图示了根据一些实施例的相邻行中的多个存储器单元对的电路图。

图3图示了根据一些实施例的包括伪晶体管的存储器单元对的布局。

图4和图5示出了根据一些实施例的存储器单元对的写入操作。

图6图示了根据一些实施例的存储器单元对的读取操作。

图7图示了根据一些实施例的包括伪晶体管的存储器单元对的电路图。

图8图示了根据一些实施例的共享伪晶体管的两个相邻存储器单元对的电路图。

图9A和图9B分别图示了根据一些实施例的包括共享伪晶体管的单鳍存储器单元对和多鳍存储器单元对的布局。

图10图示了根据一些实施例的包括细长栅极的存储器单元对的布局。

图11图示了根据一些实施例的使用n型晶体管形成的存储器单元对的电路图。

图12图示了根据一些实施例的使用n型晶体管形成的存储器单元对的布局。

图13和图14分别图示了根据一些实施例的使用n型晶体管形成的存储器单元对的写入操作和读取操作。

图15图示了根据一些实施例的使用n型晶体管形成的多鳍存储器单元对的布局。

具体实施方式

以下公开内容提供了许多用于实现本发明的不同特征不同的实施例或实例。下面描述了组件和布置的具体实施例或实例以简化本发明。当然,这些仅是实例而不旨在限制。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可以在各个示例中重复参考数字和/或字母。该重复是为了简单和清楚的目的,并且其本身不指示讨论的各个实施例和/或配置之间的关系。

此外,为了便于描述,本文中可以使用诸如“在…下方”、“在…下面”、“下部”、“在…上面”、“上部”等的间隔关系术语,以描述如图中所示的一个元件或部件与另一元件或部件的关系。除了图中所示的方位外,间隔关系术语旨在包括器件在使用或操作工艺中的不同方位。器件可以以其它方式定位(旋转90度或在其它方位),并且在本文中使用的间隔关系描述符可以同样地作相应地解释。

提供了一种存储器单元以及对应的存储器单元对和存储器阵列。根据本公开的一些实施例,存储器单元包括被配置为响应于写入信号将输入数据写入数据储存节点的写入晶体管,以及被配置为响应于数据储存节点处所储存的数据和读取信号而输出输出数据的读取晶体管。写入晶体管具有连接到写入位线的第一源极/漏极区(其可以是源极区或漏极区),以及连接到数据储存节点的第二源极/漏极区。写入晶体管的第一栅极连接到写入字线。读取晶体管具有连接到数据储存节点的第二栅极、连接到读取字线的第三源极/漏极区以及连接到读取位线的第四源极/漏极区。存储器单元可以包括或者不包括伪晶体管。由于晶体管数量少(少至两个),存储器单元具有高操作速度和小尺寸。本文讨论的实施例提供示例以实现或使用本公开的主题,并且本领域普通技术人员将容易理解在保持在不同实施例的预期范围内的同时可以进行的修改。在各个视图和说明性实施例中,相同的附图标记用于表示相同的元件。尽管可以将方法实施例讨论为以特定顺序执行,但是其他方法实施例可以以任何逻辑顺序执行。

参考图1,形成存储器阵列20。存储器阵列20包括多个存储器单元对(MCP),MCP分配为多个行和多个列。存储器单元对的总行数为m,m为整数。存储器单元对的行因此表示为行-1、行-2...到行-m。整数m可以是2的倍数,并且可以是选自例如64、128、256、512、1024等的数字。由于多个存储器单元对MCP中的每个都包括两个存储器单元,所以存储器阵列中的存储器单元的总数等于2*m。

存储器单元对的总列数为n,n为整数。存储器单元对的列因此表示为列-1、列-2...至列-n。整数n也可以是2的倍数,并且可以是选自例如64、128、256、512、1024等的数字。存储器单元对MCP的位置由它们对应的行号后跟列号指示。例如,m行n列中的存储器单元对被标识为存储器单元对MCPmn(或MCPm_n)。需要说明的是,当行号和列号中的一个或两个包括多于一位时,行号和列号可以通过符号“_”分隔。例如,行10和列12处的存储器单元MCP可以称为MCP10_12,而不是MCP1012。因此存储器单元对的总数等于(m×n),而存储器阵列20中的存储器单元的总数等于(2×m×n)。

图2A图示了根据一些实施例的两个晶体管(2T)存储器单元对MCP的电路图。存储器单元对MCP包括存储器单元MC0和存储器单元MC1。存储器单元MC0和MC1可以彼此翻转镜像。因此,存储器单元MC0和MC1有时也被称为彼此线对称。根据一些实施例,存储器单元MC0和MC1中的每个包括两个晶体管,因此对应的存储器单元MC0和MC1称为2T增益单元。根据替代实施例,存储器单元MC0和MC1中的每个可以包括多于两个的晶体管,诸如2.5个晶体管、三个晶体管等。

存储器单元MC0包括写入晶体管MW0和读取晶体管MR0。存储器单元MC1包括写入晶体管MW1和读取晶体管MR1。写入晶体管MW0的第一端子(例如源极)耦合到(并且可以直接连接到)写入位线WBL。写入晶体管MW0的第二端子(例如漏极)耦合到(并且可以直接连接到)数据储存节点NS0。写入晶体管MW0的控制端子(栅极)耦合到(并且可以直接连接到)写入字线WWL0。

读取晶体管MR0的第一端子(例如源极)耦合到(并且可以直接连接到)读取位线RBL。读取晶体管MR0的第二端子(例如漏极)耦合到(并且可以直接连接到)读取字线RWL0。读取晶体管MR0的控制端子(栅极)耦合到(并且可以直接连接到)数据储存节点NS0。

存储器单元MC1包括写入晶体管MW1和读取晶体管MR1。写入晶体管MW1的第一端子(例如源极)耦合写入位线WBL。写入晶体管MW1的第二端子(例如漏极)耦合到数据储存节点NS1。写入晶体管MW1的控制端子(栅极)耦合到写入字线WWL1。

读取晶体管MRl的第一端子(例如源极)耦合到读取位线RBL。读取晶体管MR1的第二端子(例如漏极)耦合到读取字线RWL1。第一读取晶体管MR1的控制端子(栅极)耦合到数据储存节点NS1。

根据一些实施例,写入晶体管MW0和读取晶体管MR0到读取位线、写入位线、读取字线、写入字线等的连接是直接连接,无需诸如电阻器、电容器等的附加器件。根据替代实施例,写入晶体管MW0和读取晶体管MR0到读取位线、写入位线、读取字线、写入字线等的连接中的一些是间接连接,间接连接可以包括诸如电阻器、电容器等的附加器件。

根据一些实施例,存储器单元对CMP中的所有晶体管(包括写入晶体管MW0和MWl以及读取晶体管MR0和MRl)是相同类型的,例如p型(具有p型源极和漏极区)或n型(具有n型源极区和漏极区)。此外,存储器单元对中的所有晶体管可以具有相同的结构,诸如平面晶体管结构、鳍式场效应晶体管(FinFET)结构、全环栅(GAA)晶体管结构等。

图2B示出了根据一些实施例的在相同列中的多个相邻的两个晶体管(2T)存储器单元对MCP的电路图。多个存储器单元对MCP共享相同的写入位线WBL和相同的读取位线RBL,并且具有单独的写入位线和读取位线。

根据一些实施例,存储器单元对MCP的相邻行可以通过伪晶体管MDl和/或MD2彼此分离。伪晶体管MD1和MD2是功能完全正常的晶体管,并且在存储器阵列20的操作期间一直截止。根据其中伪晶体管MD1和MD2是p型晶体管的一些实施例,高电压(诸如VDD)可以连接到伪晶体管MD1和MD2的栅极以截止这些晶体管。伪晶体管MD1和MD2的源极和漏极区连接到相邻存储器单元对MCP中的数据储存节点NS0和NS1。伪晶体管MD1和MD2的功能可以在后续图3的讨论中找到。伪晶体管MD1和MD2的导电类型可以与写入晶体管MW0和MW1以及晶体管MR0和MR1的导电类型相同,或者导电类型相反。

图3图示了图2B中所示实施例的示例布局。可以理解,图3所示的布局(以及其他图中的布局)也是形成在物理晶圆(诸如硅晶圆)上的存储器件的俯视图。所示的布局使用FinFET作为示例,而其他类型的晶体管也可以使用。

多个(半导体)鳍(标记为FIN,包括多个鳍FIN0和FIN1)形成为彼此平行,并且在Y方向上延伸。多个栅极堆叠件(栅极)在X方向上延伸。栅极堆叠件包括栅极堆叠件GD,栅极堆叠件G是伪晶体管MD1和MD2的栅极堆叠件。当伪晶体管MD1和MD2是p型晶体管时,栅极堆叠件GD可以连接到正电源供电电压VDD,并且当伪晶体管MD1和MD2是n型晶体管时,可以连接到电源供电电压VSS(电接地)。栅极堆叠件还包括栅极堆叠件GF,栅极堆叠件GF是包括写入晶体管MW0和MW1以及读取晶体管MR0和MR1的功能晶体管的栅极堆叠件。

数据储存节点NS0和NS1可以形成在相邻的栅极堆叠件GF和GD之间。根据一些实施例,数据储存节点NS0和NS1、读取字线RWL0和RWL1、读取位线RBL和写入位线WBL可以包括源极/漏极区和相应的源极/漏极接触插塞。

如图3所示,三个存储器单元对MCP11、MCP21和MCP31位于相邻的行中。在存储器单元对MCP11、MCP21和MCP31中的每个中,存储器单元MC0和MC1相对于位于对应存储器单元对的中间并且在X方向上延伸的直线彼此线对称。例如,存储器单元对MCP11中的存储器单元MC0和MC1相对于直线26线对称。或者说,每个存储器单元对中的存储器单元MC0和MC1相对于位于对应存储器单元对的中间的第一直线(在X方向上延伸的直线)翻转。

根据一些实施例,相同列中的所有存储器单元对的写入晶体管MW0和MWl共享相同的半导体鳍(诸如FIN0),该半导体鳍可以在选定位置处断开。相同列中的所有存储器单元对的读取晶体管MR0和MR1共享相同的半导体鳍(诸如FIN1)。此外,半导体鳍FIN0连接到写入位线WBL,并延伸到相同列中的所有存储器单元中。半导体鳍FIN1连接到读取位线RBL并延伸到相同列中的所有存储器单元中。

如图3所示,由于存储器单元对的紧凑尺寸,存储器单元对MCP11中的数据储存节点NS0与存储器单元对MCP21中的数据储存节点NS1以小距离相邻。伪晶体管MD1形成在相邻的数据储存节点NS0和NS1之间。根据其中伪晶体管MD1是p型晶体管的一些实施例,将电压VDD施加到伪晶体管MD1的栅极GD。伪晶体管MD1截止,并且因此将存储器单元对MCP11中的数据储存节点NS0与存储器单元对MCP21中的数据储存节点NS1电断开并且信号断开。

根据替代实施例,代替使两个相邻的数据储存节点NS0和NS1通过伪晶体管MD1电断开,可以在栅极GD所在的位置物理切割鳍FIN0,使得相邻的数据储存节点NS0和NS1彼此物理(并且也电)分离。在这种情况下,将不形成伪晶体管MD1的伪栅极GD。对应的电路图与图2B所示的相似,不同之处在于将不形成伪晶体管MD1。

类似地,由于存储器单元对的紧凑尺寸,存储器单元对MCP11中的读取字线RWL0与存储器单元对MCP21中的读取字线RWL1以小距离相邻。伪晶体管MD2形成在相邻的读取字线RWL0和RWL1之间。根据其中伪晶体管MD2是p型晶体管的一些实施例,将电压VDD施加到伪晶体管MD2的栅极GD。伪晶体管MD2截止,并且将存储器单元对MCP11中的读取字线RWL0与存储器单元对MCP21中的读取字线RWL1电断开并且信号断开。

根据替代实施例,代替使两个相邻的读取字线RWL0和RWL1通过伪晶体管MD2电断开,可以在栅极GD所在的位置物理切割鳍FINl,使得相邻的读取字线RWL0和RWL1彼此物理(并且也电)分离。在这种情况下,将不形成伪晶体管MD2的伪栅极GD。对应的电路图与图2B所示的相似,不同之处在于将不形成伪晶体管MD2。

根据一些实施例的示例写入操作参考图4和图5讨论如下。图4图示了用于写入操作的对应信号,而图5图示了显示存储器单元对MCP中的线和节点以及写入操作期间的对应信号/电压的表。参考图4讨论的示例晶体管是p型晶体管。

参考图4,假设在一时间处,要写入存储器单元MC0,通过写入信号SW0选择写入晶体管MW0,写入信号SW0可以等于电压VSS,如图5所示。因此,写入晶体管MW0导通。写入晶体管MW0将写入位线WBL上的第一输入数据DIN0写入数据储存节点NS0。因此,数据储存节点NS0上的逻辑值被写入与输入数据DIN0的逻辑值相同的逻辑值。储存的数据可以是分别对应于高电压信号(诸如VDD)和低电压信号(诸如VSS)的“H”(高)或“L”(低)。

在执行写入操作的时间处,读取字线RWL0上的读取信号DR0(图4)等于低电压VSS。因此,无论数据储存节点NS0上的逻辑值(高或低,如图5)如何,读取位线RBL上无电流。因此,降低了写入操作期间的功耗。

图4和图6组合图示了根据一些实施例的示例读取操作。图4图示了用于读取操作的对应信号,而图6图示了显示读取操作期间的线和节点以及对应信号的表。假设在一时间处,要读取存储器单元MC0,通过写入字线WWL0上的第一写入信号SW0(SW0=VDD)选择写入晶体管MW0。因此,写入晶体管MW0截止。数据节点NS0现在是浮动节点。将读取信号DR0施加到读取字线RWL0。读取信号DR0等于读取电压Vread,读取电压Vread为非零电压。读取电压Vread是大于VSS的电压,并且可以等于或小于电压VDD。可以由电压源22生成读取电压Vread。

当数据储存节点NS0储存数据“H”时,读取晶体管MR0截止(图6)。因此,读取位线RBL上的输出数据与读取位线RBL上的“无电流”相关联。相反地,当数据储存节点NS0储存数据“L”时,读取晶体管MR0导通(图6)。因此,读取位线RBL上的输出数据与读取位线RBL上的“读取电流”相关联。读取位线RBL上的电流可以通过连接到读取位线RBL的电流检测电路24检测。“读取电流”与电压Vread有关,电压Vread越高,读取位线RBL上的电流越高。为了降低功耗,只要通过电流检测电路能够可靠地检测到生成的电流,就降低电压Vread。例如,电压Vread可以在约(1/5)×VDD和VDD之间的范围内,并且根据一些实施例,也可以在约(1/5)×VDD和约(4/5)×VDD之间的范围内。存储器单元MC1的操作本质上与存储器单元MC0相同。

返回参考图1,控制电路28连接到存储器阵列20,并控制存储器阵列20的操作。例如,存储器阵列20的写入操作和读取操作通过控制电路28来控制。控制电路28的电路可以包括字线控制器、位线控制器、电压源(包括图4中的电压源22)、图4中的电流检测电路24、伪晶体管的截止等。控制电路28可以控制并同步存储器阵列20的写入操作和读取操作。

图7图示了三个晶体管(3T)存储器单元对MCP,其中存储器单元MC0和MC1中的每个包括写入晶体管(MW0或MW1)、读取晶体管(MR0或MR1)和伪晶体管(MD0或MD1)。伪晶体管MD0和MD1的栅极连接到诸如电压VDD的高电压。因此,在存储器阵列20的整个操作期间,伪晶体管MD0和MD1一直由电压VDD截止。伪晶体管MD0和MD1的作用是防止存储器单元和/或存储器单元对中的节点(诸如数据储存节点NS0和数据储存节点NS1)由它们相邻的存储器单元或存储器单元对干扰。在读取操作和写入操作期间写入晶体管MW0和MW1以及读取晶体管MR0和MR1的操作与参考图4、图5和图6所讨论的相同,在此不再赘述。

图8图示了根据一些实施例的在相邻存储器单元对(在相邻的行中)中的存储器单元对MCPA和MCPB的部分的电路图。这些实施例类似于图7中所示的实施例,不同之处在于不是在每个存储器单元MC0和MC1中具有专用的伪晶体管,而是形成两个伪晶体管MD1和MD2,分别由相邻的存储器单元对MCPA和MCPB共享。这也可以认为每个存储器单元MC拥有每个伪晶体管MD1和MD2的一半。因此,每个存储器单元MC平均拥有三个晶体管,包括一个写入晶体管、一个读取晶体管以及两个伪晶体管MD1和MD2中的每个的一半。类似地,写入字线WWL连接到写入晶体管MW的栅极。写入位线WBL连接到写入晶体管MW的源极/漏极区。读取位线RBL连接到读取晶体管MR的源极/漏极区。读取字线RWL连接到读取晶体管MR的源极/漏极区。

伪晶体管MD1和MD2在存储器单元和对应存储器阵列20(图1)的整个操作期间也截止。根据一些实施例,伪晶体管MD1和MD2是p型晶体管,并且高电压VDD可以连接到p型伪晶体管MD1和MD2的栅极以将它们截止。根据可选实施例,形成两个n型伪晶体管MD1和MD2,并且它们的栅极连接到电压VSS,使得n型伪晶体管MD1和MD2截止。伪晶体管MD1的源极/漏极区连接到相邻存储器单元对MCPA和MCPB中的相邻数据储存节点NS,因此将相邻数据储存节点NS彼此电去耦且信号去耦。伪晶体管MD2的源极/漏极区连接到读取字线RWL0和RWL1,因此将相邻的存储器单元对MCPA和CMPB中的读取字线RWL0和RWL1彼此电去耦且信号去耦。

图9A图示了图8所示电路的布局。可以观察到,伪晶体管MD1的栅极GD在半导体鳍FIN1上延伸。存储器单元对MCPA中的半导体鳍FIN1的部分连接到数据储存节点NS(标记为NSA)。存储器单元对MCPB中的半导体鳍FIN1的部分连接到数据储存节点NS(标记为NSB)。因此,伪晶体管MD1将数据储存节点NSA和NSB彼此电去耦。伪晶体管MD2的栅极GD在半导体鳍FIN0上。存储器单元对MCPA中的半导体鳍FIN0的部分连接到读取字线RWL(标记为RWLA)。存储器单元对MCPB中的半导体鳍FIN1的部分连接到读取字线RWL(标记为RWLB)。因此,伪晶体管MD2将读取字线RWLA和RWLB彼此电去耦。根据一些实施例,相同行中的伪晶体管MD1和MD2共享相同栅极GD,该栅极GD是延伸到存储器阵列20的所有列中的细长栅极。

图9B图示了图8中所示电路的布局。该布局类似于图9A中所示的布局,除了图9B图示了多鳍晶体管,而图9A图示了单鳍晶体管。此外,在图9B中,多个半导体鳍FIN2连接到一列中的写入位线WBL并用作一列中的写入位线WBL。多个半导体鳍FIN3连接到一列中的读取位线RBL并用作一列中的读取位线RBL。存储器单元的响应速度和输出电流值会随着半导体鳍数量的增加而增加。根据一些实施例,基于鳍FIN0和FIN1的存储器单元对线对称于基于鳍FIN2和FIN3的存储器单元对。

图10图示了存储器单元对MCP11和MCP21的布局。根据这些实施例,存储器单元对MCP21中的单个栅极堆叠件GD延伸到半导体鳍FIN0和FIN1两者,并因此形成伪晶体管MD1和MD2两者。

图11图示了根据一些实施例的存储器单元对MCPA和MCPB的部分。这些实施例类似于图8中所示的实施例,除了使用n型晶体管代替使用p型晶体管来形成存储器单元MC和MCP对MCPA和MCPB。示出的部分包括存储器单元对MCPA的一半和存储器单元对MCPB的一半。每个存储器单元对MCPA和MCPB的整体结构类似于图2A、图2B和图4中所示的存储器单元对,其中晶体管改变为n型晶体管。

根据一些实施例,形成两个n型伪晶体管MDl和MD2,分别由两个存储器单元对MCPA和MCPB共享。这也可以认为每个存储器单元MC拥有每个伪晶体管MD1和MD2的一半。因此,每个存储器单元MC平均拥有三个晶体管,包括一个写入晶体管、一个读取晶体管以及两个伪晶体管MD1和MD2中的每个的一半。类似地,写入字线WWL连接到写入晶体管MW的栅极。写入位线WBL连接到写入晶体管MW的源极/漏极区。读取位线RBL连接到读取晶体管MR的源极/漏极区。读取字线RWL连接到读取晶体管MR的源极/漏极区。

伪晶体管MD1和MD2在存储器单元和对应存储器阵列20的整个操作期间也截止。根据一些实施例,使用n型伪晶体管MD1和MD2,并且低电压(诸如电压VSS)可以连接到n型伪晶体管MD1和MD2的栅极以将它们截止。伪晶体管MD1的源极/漏极区连接到相邻存储器单元对MCPA和MCPB中的相邻数据储存节点NS,因此将相邻数据储存节点NS彼此电去耦且信号去耦。伪晶体管MD2的源极/漏极区连接到相邻的读取字线RWL,因此将相邻存储器单元对MCPA和CMPB中的读取字线RWL彼此电去耦且信号去耦。根据替代实施例,可以在图11所示的结构中使用两个p型伪晶体管MD1和MD2,并且p型伪晶体管MD1和MD2的栅极连接到诸如电压VDD的高电压,使得p型伪晶体管MD1和MD2截止。

图12示出了图11中所示电路的布局。可以观察到,伪晶体管MD1的栅极GD在半导体鳍FIN1上延伸。存储器单元对MCPA中的半导体鳍FIN1的部分连接到数据储存节点NS(标记为NSA)。存储器单元对MCPB中的半导体鳍FIN1的部分连接到数据储存节点NS(标记为NSB)。因此,伪晶体管MD1将数据储存节点NSA和NSB彼此电去耦。伪晶体管MD2的栅极GD在半导体鳍FIN0上延伸。存储器单元对MCPA中的半导体鳍FIN0的部分连接到读取字线RWL(标记为RWLA)。存储器单元对MCPB中的半导体鳍FIN1的部分连接到读取字线RWL(标记为RWLB)。因此,伪晶体管MD2将读取字线RWLA和RWLB彼此电去耦。

根据一些实施例,以下讨论了由n型晶体管(图11)形成的MCP单元的示例写入操作。图13图示了显示存储器单元对MCP中的线和节点以及写入操作期间的对应信号的表。

假设在一时间处,要写入存储器单元MC,通过写入信号SW选择写入晶体管MW,写入信号SW可以等于电压VDD,如图13所示。因此,导通写入晶体管MW。写入晶体管MW将写入位线WBL上的输入数据写入对应的数据储存节点NS。因此,数据储存节点NS上的逻辑值被写入与输入数据的逻辑值相同的值。储存的数据可以是分别对应于高电压信号(诸如电压VDD)和低电压信号(诸如电压VSS)的“H”(高)或“L”(低)。

在执行写入操作的时间处,对应读取字线RWL上的读取信号DR等于低电压(诸如电压VSS)。因此,无论数据储存节点NS上的逻辑值(高或低,如图5所示)如何,读取位线RBL上无电流。因此,降低了写入操作期间的功耗。

图14图示了根据一些实施例的示例读取操作。图14图示了显示读取操作期间对应存储器单元中的线和节点的表。假设在一时间处,要读取存储器单元MC(图11),通过信号SW选择写入晶体管MW,信号SW是低电压VSS。因此,写入晶体管MW截止。数据节点NS现在是浮动节点。读取信号DR被施加到读取字线RWL。读取信号等于读取电压Vread,读取电压Vread为非零电压。读取电压Vread是大于VSS的电压,并且可以等于或小于电压VDD。读取电压Vread可以通过控制电路28(图1)中的电压源25(图11)生成。

当数据储存节点NS储存数据“L”时,读取晶体管MR截止(图11)。因此,读取位线RBL上的输出数据与读取位线RBL上的“无电流”相关联。相反地,当数据储存节点NS储存数据“H”时,读取晶体管MR导通(图11)。因此,读取位线RBL上的输出数据与读取位线RBL上的“读取电流”相关联,该“读取电流”可以通过连接到读取位线RBL的电流检测电路24(图4)检测。“读取电流”与电压Vread有关,电压Vread越高,读取位线RBL上生成的电流越高。为了降低功耗,只要通过电流检测电路能够可靠地检测到生成的电流,就保持电压Vread为低。例如,根据一些实施例,电压Vread可以在约(1/5)×VDD和VDD之间的范围内,也可以在约(1/5)×VDD和约(4/5)×VDD之间的范围内。

图15图示了图11中所示电路的布局。该布局类似于图9B中所示的布局,不同之处在于晶体管的源极/漏极区是掺杂有n型掺杂剂的n型源极/漏极区。存储器单元中的晶体管是多鳍晶体管。相应地,存储器单元的响应速度和输出电流值将随着半导体鳍数量的增加而增加。

本公开的实施例具有一些有利特征。根据本发明实施例的存储器单元具有小数量的晶体管。改进了对应的存储器阵列的操作速度。增加了存储器阵列的密度。存储器阵列因此可以用作高性能计算处理器的高速缓冲存储器。

根据本公开的一些实施例,一种存储器器件包括:写入位线和读取位线,在第一方向上延伸;第一写入字线和第一读取字线,在垂直于第一方向的第二方向上延伸;第一存储器单元,包括第一写入晶体管,第一写入晶体管包括:连接到第一写入字线的第一栅极;连接到写入位线的第一源极/漏极;连接到第一数据储存节点的第二源极/漏极;第一读取晶体管,第一读取晶体管包括:连接到第一数据储存节点的第二栅极;连接到读取位线的第三源极/漏极;连接到第一读取字线的第四源极/漏极。在一个实施例中,第一栅极通过直接连接而连接到第一写入字线;第一源极/漏极通过直接连接而连接到写入位线;第二栅极通过直接连接而连接到第一数据储存节点;并且第三源极/漏极通过直接连接而连接到读取位线。

在一个实施例中,第一存储器单元中的晶体管的总数等于两个。在一个实施例中,第一写入晶体管和第一读取晶体管均为p型晶体管。在一个实施例中,第一写入晶体管和第一读取晶体管均为n型晶体管。在一个实施例中,该存储器器件还包括:第二写入字线和第二读取字线,在第二方向上延伸;以及第二存储器单元,具有与第一存储器单元相同的结构,其中,第二存储器单元连接到写入位线、读取位线、第二写入字线和第二读取字线,并且其中,第一存储器单元和第二存储器单元组合形成第一存储器单元对。在一个实施例中,该存储器器件还包括:第二存储器单元对,与第一存储器单元对相邻;以及伪晶体管,连接在第一存储器单元对和第二存储器单元对之间。

在一个实施例中,伪晶体管包括:第一源极/漏极区,连接到第一存储器单元对中的第一存储器单元的第一数据储存节点;以及第二源极/漏极区,连接到第二存储器单元对中的第二存储器单元的第二数据储存节点。在一个实施例中,伪晶体管包括:第一源极/漏极区,连接到第一存储器单元对中的第一存储器单元的第一读取字线;和第二源极/漏极区,连接到第二存储器单元对中的第二存储器单元的第二读取字线。在一个实施例中,该存储器器件还包括连接到读取位线的电流检测电路。在一个实施例中,该存储器器件还包括连接到第一写入字线的电压源电路,其中,电压源电路被配置为输出低于正电源供电电压VDD的非零电压。

根据本公开的一些实施例,一种存储器器件包括存储器阵列,该存储器阵列包括布置成多个列和多个行的多个存储器单元对,其中多个存储器单元对中的每个包括第一存储器单元,第一存储器单元包括:第一写入晶体管,被配置为响应于第一写入信号将第一输入数据写入到第一数据储存节点;第一读取晶体管,被配置为响应于第一数据储存节点上的第一输入数据和第一读取信号向读取位线输出第一输出数据;第二存储器单元,第二存储器单元包括:第二写入晶体管,被配置为响应于第二写入信号将第二输入数据写入到第二数据储存节点;和第二读取晶体管,被配置为响应于第二数据储存节点上的第二输入数据和第二读取信号向读取位线输出第二输出数据。在一个实施例中,第一存储器单元和第二存储器单元位于存储器阵列的相邻行中。

在一个实施例中,该存储器器件还包括VDD电压节点;和p型伪晶体管,包括连接到第一数据储存节点的源极/漏极区,其中,p型伪晶体管包括连接到VDD电压节点的栅极。在一个实施例中,该存储器器件还包括:VSS电压节点;和n型伪晶体管,包括连接到第一数据储存节点的源极/漏极区,其中,n型伪晶体管包括连接到VSS电压节点的栅极。在一个实施例中,该存储器器件还包括:电流检测电路,连接到读取位线,其中,电流检测电路被配置为测量读取位线上的电流。

根据本公开的一些实施例,一种存储器器件包括:第一方向上延伸的写入位线和读取位线;垂直于第一方向的第二方向上延伸的写入字线和读取字线;存储器单元,包括:第一栅极,连接到写入字线;第一源极/漏极,连接到写入位线;和第二源极/漏极,连接到数据储存节点;以及读取晶体管,包括:第二栅极,连接到数据储存节点;第三源极/漏极,连接到读取位线;和第四源极/漏极,连接到读取字线;电源供电节点,电源供电节点为VDD节点或VSS节点;以及伪晶体管,包括:连接到电源供电节点的第三栅极;连接到数据储存节点的第五源极/漏极。在一个实施例中,伪晶体管是p型晶体管,并且其中电源供电节点是VDD节点。在一个实施例中,伪晶体管是n型晶体管,并且其中电源供电节点是VSS节点。在一个实施例中,存储器单元是两个晶体管单元。

上述概述了几个实施例的特征,以便本领域技术人员可以更好地理解本公开的各个方面。本领域技术人员应当理解,他们可以容易地使用本公开作为设计或修改用于实现本文所介绍的实施例的相同目的和/或实现其相同优点的其它过程和结构的基础。本领域技术人员还应当认识到,此类等效结构不背离本发明的精神和范围,并且它们可以在不背离本发明的精神和范围的情况下在本发明中进行各种改变、替换以及改变。

- 浮栅存储器件及其控制方法、3D存储器件与2D存储器件

- 一种三维存储器件的形成方法及三维存储器件

- 3D存储器件的制造方法及3D存储器件

- 存储器器件和存储器器件的操作方法

- 存储器件的测试装置及相关的存储器件的测试和制造方法

- 存储器件、用于控制存储器件的控制器、包括存储器件的存储系统以及存储器件的操作方法

- 存储器件、存储器件的操作方法和包含该存储器件的存储系统