面板断线检测装置

文献发布时间:2024-01-17 01:20:32

技术领域

本公开涉及一种检测装置。详细而言,本公开涉及一种面板断线检测装置。

背景技术

现有面板趋势为无缝拼接面板或无边框拼接面板。无缝拼接面板代表面板仅包含仅显示区,不允许其他区域存在。因此,无法于无缝拼接面板的显示区设置检测板,以进行无缝拼接面板的信号线的断线测试。

再者,若无进行无缝拼接面板的信号线的断线测试,批次量产的面板中将存在些许不良产品,而这些不良产品将造成制造成本的提高,且面板的良率不易改善。

因此,上述技术尚存诸多缺陷,而有待本领域从业人员研发出其余适合的断线检测电路设计。

发明内容

本公开的一面向涉及一种面板断线检测装置。面板断线检测装置包含面板及检测电路。面板包含显示区、导电网格线、栅极线及数据线。导电网格线位于显示区中,并用以传输直流信号。栅极线位于显示区中,并用以传输交流信号。数据线位于显示区中,并用以传输数据信号。检测电路分别耦接于显示区中的导电网格线、栅极线及数据线。检测电路包含第一子检测电路、第二子检测电路及第三子检测电路。第一子检测电路耦接于导电网格线,并用以产生第一检测信号,以检测导电网格线是否断线。第二子检测电路,耦接于栅极线,并用以产生第二检测信号,以检测栅极线是否断线。第三子检测电路耦接于数据线,并用以产生第三检测信号,以检测数据线是否断线。

附图说明

参照后续段落中的实施方式以及下列附图,当可更佳地理解本公开的内容:

图1为根据本公开一些实施例示出的面板断线检测装置的电路方框示意图;

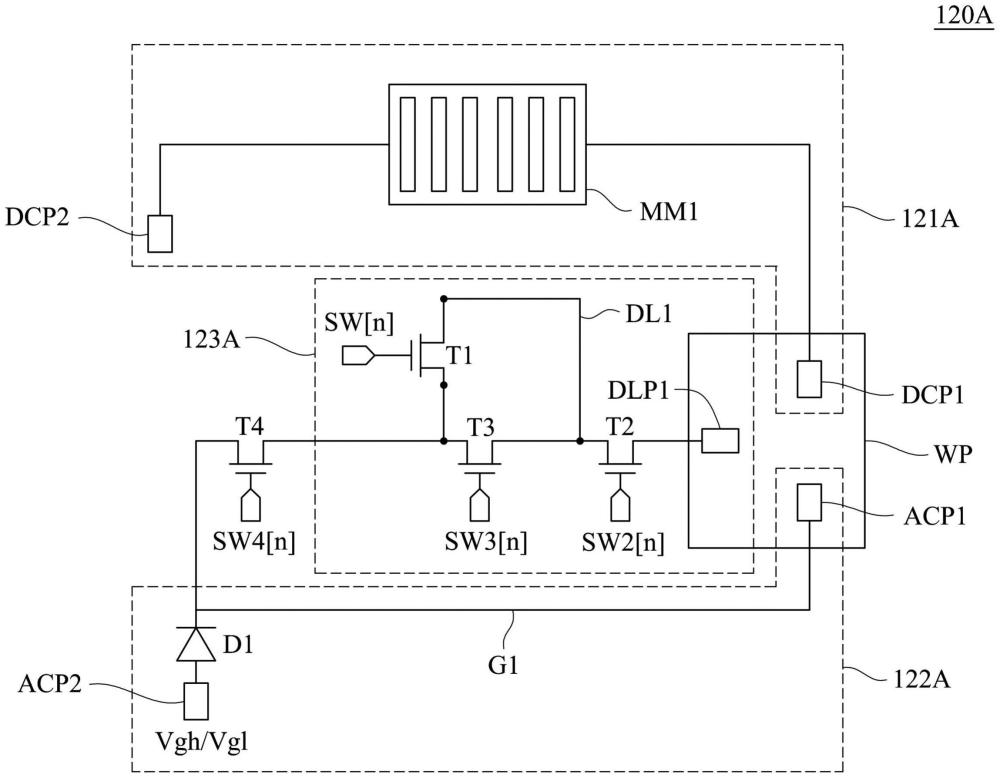

图2为根据本公开一些实施例示出的面板断线检测装置的检测电路的示意图;

图3为根据本公开一些实施例示出的面板断线检测装置的检测电路的示意图;以及

图4为根据本公开一些实施例示出的面板断线检测装置的检测电路的示意图。

附图标记说明:

100:面板断线检测装置

D:显示区

110:面板

120~120B:检测电路

121~121B:第一子检测电路

122~122B:第二子检测电路

123~123B:第三子检测电路

MM1:导电网格线

DL1~DL4:数据线

G1~G2:栅极线

P1~P4:像素电路

T1~T4:晶体管

SW[n]~SW4[n]:控制信号

DCP1~DCP2:直流信号检测板

ACP1~ACP2:交流信号检测板

DLP1:数据信号检测板

WP:整合检测板

D1:检测二极管

Vgh/Vgl:高电平或低电平

具体实施方式

以下将以附图及详细叙述清楚说明本公开的构思,任何所属技术领域中技术人员在了解本公开的实施例后,当可由本公开所启示的技术,加以改变及修饰,其并不脱离本公开的构思与范围。

本文的用语只为描述特定实施例,而无意为本公开的限制。单数形式如“一”、“这”、“此”、“本”以及“该”,如本文所用,同样也包含复数形式。

关于本文中所使用的“包含”、“包括”、“具有”、“含有”等等,均为开放性的用语,即意指包含但不限于。

关于本文中所使用的用词(terms),除有特别注明外,通常具有每个用词使用在此领域中、在本公开的内容中与特殊内容中的平常意义。某些用以描述本公开的用词将于下或在此说明书的别处讨论,以提供本领域技术人员在有关本公开的描述上额外的引导。

图1为根据本公开一些实施例示出的面板断线检测装置100的电路方框示意图。在一些实施例中,请参阅图1,面板断线检测装置100包含面板110及检测电路120。在一些实施例中,面板110包含多个面板所拼接形成的整合拚接面板。面板110的显示区D的外侧不包含周边区。须说明的是,现有面板趋势为无缝拼接面板或无边框拼接面板。无缝拼接面板代表面板仅包含仅显示区域,不允许其他区域(例如:周边区域)存在。在一些实施例中,检测电路120位于面板110的侧边、面板110的正面或面板110的背面。

在一些实施例中,面板110包含显示区D、导电网格线MM1、栅极线G1~G2及数据线DL1~DL4。导电网格线MM1位于显示区D中,并用以传输直流信号。栅极线G1~G2位于显示区D中,并用以传输交流信号。数据线DL1~DL4位于显示区D中,并用以传输数据信号。

在一些实施例中,导电网格线MM1、栅极线G1~G2及数据线DL1~DL4位于面板断线检测装置100的不同结构层上。

在一些实施例中,检测电路120分别耦接于显示区D中的导电网格线MM1、栅极线G1~G2及数据线DL1~DL4。检测电路120包含第一子检测电路121、第二子检测电路122及第三子检测电路123。第一子检测电路121耦接于导电网格线MM1,并用以产生第一检测信号,以检测导电网格线MM1是否断线。第二子检测电路122耦接于栅极线G1~G2,并用以产生第二检测信号,以检测栅极线G1~G2是否断线。第三子检测电路123耦接于数据线DL1~DL4,并用以产生第三检测信号,以检测数据线DL1~DL4是否断线。

须说明的是,导电网格线MM1通常于面板110中具有整面(global)网格图案,其形状不以本公开实施例为限。栅极线G1~G2通常耦接至面板110的玻璃基板上的栅极驱动电路(图中未示)。栅极驱动电路设置于面板110两侧或设置于面板110的有效区域(ActiveArea,AA)。数据线DL1~DL4通常耦接于面板110的不同列(row)或不同行(column)的像素电路P1~P4。数据线DL1~DL4及像素电路P1~P4的数量通常由面板110的分辨率所决定,并不以本公开附图实施例为限。导电网格线MM1及栅极线G1~G2的数量不以本公开附图实施例为限。

在一些实施例中,第一子检测电路121、第二子检测电路122及第三子检测电路123位于面板断线检测装置100的同一结构层上。在一些实施例中,检测电路120、导电网格线MM1、栅极线G1~G2及数据线DL1~DL4位于面板断线检测装置100的不同结构层上。

图2为根据本公开一些实施例示出的图1的面板断线检测装置100的检测电路120的示意图。在一些实施例中,为使图1的面板断线检测装置100的结构易于理解,请一并参阅图2。在一些实施例中,图2的检测电路120的电路架构基本上对应于图1的面板断线检测装置100的检测电路120。在一些实施例中,检测电路120还包含整合检测板WP。

在一些实施例中,请以图示中元件的上方及右方起算为第一端,第一子检测电路121包含第一直流信号检测板DCP1及第二直流信号检测板DCP2。第一直流信号检测板DCP1耦接于导电网格线MM1的第一端,并用以输入第一检测信号至导电网格线MM1。第二直流信号检测板DCP2耦接于导电网格线MM1的第二端,并用以根据第一检测信号以判断导电网格线MM1是否断线。

须说明的是,由第一直流信号检测板DCP1输入第一检测信号至导电网格线MM1,若第二直流信号检测板DCP2接收到第一检测信号,则可判定导电网格线MM1于拼接的面板110中未断线。相反地,若第二直流信号检测板DCP2未接收到第一检测信号,则可判定导电网格线MM1于拼接的面板110中断线。

在一些实施例中,导电网格线MM1位于面板110的显示区D的有效区域(AA区)中。在一些实施例中,导电网格线MM1位于面板110的显示区D的有效区域(AA区)之外。

在一些实施例中,第二子检测电路122包含第一交流信号检测板ACP1、第二交流信号检测板ACP2及检测二极管D1。第一交流信号检测板ACP1耦接于栅极线G1,并用以输入第二检测信号至栅极线G1。第二交流信号检测板122耦接于栅极线G1。检测二极管D1耦接于栅极线G1及第二交流信号检测板ACP2,并用以根据第二检测信号以判断栅极线G1是否断线。

请同时参阅图1及图2,须说明的是,图1的栅极线G1连接第二子检测电路122的底部分叉为两条。一条连接至第一交流信号检测板ACP1。另一条连接至第二交流信号检测板ACP2及检测二极管D1。检测二极管D1可为正偏压设计、逆偏压设计或正逆偏压设计,并通过检测二极管D1形成跨压差异,借此形成交流信号线的断线检测回路。

进一步说明的是,由第一交流信号检测板ACP1输入第二检测信号至栅极线G1,若第二交流信号检测板ACP2接收到第二检测信号,则可判定栅极线G1于拼接的面板110中未断线。相反地,若第二交流信号检测板ACP2未接收到第二检测信号,则可判定栅极线G1于拼接的面板110中断线。

在一些实施例中,请参阅图1及图2,第三子检测电路123包含第一晶体管T1、第二晶体管T2及数据信号检测板DLP1。第一晶体管T1耦接于数据线DL1。第二晶体管T2耦接于数据线DL1,并与第一晶体管T1形成数据线DL1的断线检测回路。数据信号检测板DLP1耦接于数据线DL1及第二晶体管T2,并用以输入第三检测信号至检测回路,且根据第三检测信号判断数据线DL1是否断线。

接着,第一晶体管T1位于面板110的显示区D的有效区域(AA区)的多个像素电路其中一者(例如:图1的像素电路P1)。第二晶体管T2位于面板110侧边的检测电路120中。

在一些实施例中,第一晶体管T1响应第一控制信号SW[n]导通。第二晶体管T2响应第二控制信号SW2[n]导通。此时,通过第一晶体管T1及第二晶体管T2所形成的跨压差异,借此形成数据线DL1的断线检测回路。

须说明的是,由数据信号检测板DLP1输入第三检测信号至数据线DL1,若数据信号检测板DLP1接收到传送回来第三检测信号,则可判定数据线DL1于拼接的面板110中未断线。相反地,若数据信号检测板DLP1未接收到传送回来第三检测信号,则可判定数据线DL1于拼接的面板110中断线。

在一些实施例中,第三子检测电路123还包含第三晶体管T3。第三晶体管T3耦接于第一晶体管T1及第二晶体管T2,并与第一晶体管T1及第二晶体管T2形成检测回路。须说明的是,第三晶体管T3响应第三控制信号SW3[n]导通。第三晶体管T3的数量不以附图实施例为限。

在一些实施例中,第一直流信号检测板DCP1、第一交流信号检测板ACP1及数据信号检测板DLP1设置于图2的检测电路120的整合检测板WP上。在一些实施例中,第一直流信号检测板DCP1、第二直流信号检测板DCP2、第一交流信号检测板ACP1、第二交流信号检测板ACP2及数据信号检测板DLP1皆为导电材质,并包含但不限于金属。

须说明的是,请参阅图2,第二子检测电路122耦接第三子检测电路123的目的在于表示栅极驱动电路(Gate driver On Array,GOA)直接产生交流控制信号至面板110的有效区域(AA区)的多个像素电路其中一者(通过位在像素电路P1的第一晶体管T1进行表示)或多个子像素电路中。

在一些实施例中,检测电路120分别检测导电网格线MM1、栅极线G1及数据线DL1。

图3为根据本公开一些实施例示出的面板断线检测装置100的检测电路120A的示意图。图3的检测电路120A与图2的检测电路120的差异在于检测电路120A还包含第四晶体管T4。在一些实施例中,于同时检测数据线DL1及栅极线G1的情况下,第四晶体管T4耦接于第二子检测电路122A及第三子检测电路123A,并用以响应第四控制信号SW4[n]关闭,借此隔绝、第二子检测电路122A的第二检测信号及第三子检测电路123A的第三检测信号,进而避免检测信号之间互相影响。图3的检测电路120A的电路架构基本上于图2的检测电路120的电路架构相同。

须说明的是,第四晶体管T4的设置目的在于表示栅极驱动电路的位置。详言之,第四晶体管T4用以表示交流控制信号经过栅极驱动电路(即第四晶体管T4的位置),并延伸至图1的面板110的有效区域(AA区)的多个像素电路其中一者(通过位在像素电路P1的第一晶体管T1进行表示)或多个子像素电路中。

图4为根据本公开一些实施例示出的面板断线检测装置100的检测电路120B的示意图。图4的检测电路120B与图3的检测电路120A的差异在于检测电路120B的第三子检测电路123B中多设置一个电容C1。电容C1耦接于第一晶体管T1、第二晶体管T2及第三晶体管T3,并与第一晶体管T1、第二晶体管T2及第三晶体管T3形成检测回路。图4的第三子检测电路123B的电路架构基本上于图3的第三子检测电路123A的电路架构相同。

须说明的是,电容C1可用于存储检测信号,以于不同时序将检测信号读取出来。此外,电容C1的数量及位置不以附图实施例为限。进一步说明的是,第三晶体管T3及电容C1的数量及位置可依据实际需求所设计,均不以本公开附图实施例为限。

在一些实施例中,上述检测电路120A~120B可同时检测导电网格线MM1、栅极线G1及数据线DL1。在一些实施例中,上述检测电路120A~120B亦可分时序检测导电网格线MM1、栅极线G1及数据线DL1。

依据前述实施例,本公开提供一种面板断线检测装置,借此通过本公开检测电路的电路架构检测无缝拚接面板的多个种信号线是否断线。

虽然本公开以详细的实施例公开如上,然而本公开并不排除其他可行的实施方式。因此,本公开的保护范围当视权利要求所界定者为准,而非受于前述实施例的限制。

对本领域技术人员而言,在不脱离本公开的构思和范围内,当可对本公开作各种的变动与润饰。基于前述实施例,所有对本公开所作的变动与润饰,亦涵盖于本公开的保护范围内。

- 缝纫机底线断线检测装置及其检测和余量判断方法

- 一种缝纫机断线检测控制装置及缝纫机

- 纱线断线检测装置

- 一种刺绣断线自检测的装置

- 一种簇绒机断线自动检测装置

- 一种显示面板、显示装置及其断线检测方法

- 触控面板传感器断线检测方法及装置