半导体元件封装结构

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及一种半导体制造技术,且特别是涉及半导体元件封装结构。

背景技术

通过半导体制造技术,集成电路可以在一个基板上制造。集成电路的功能随着整体电子产品的研发的需求也趋向更复杂的设计。集成电路所包含的元件以及内联机结构也因此大量增加。由于一个基板可用于制造形成元件的面积有其限制。因应集成电路所需要增大其功能而涉及的大量元件,集成电路的制造例如已往基板垂直的方向堆栈形成更多的元件与线路。

再进一步的制造研发,其可以将集成电路分为两个部分,分别在其对应的基板上制造完成。基板的上层会形成有接合层(bonding layer)。接合层包含介电层以及在介电层中设置有多个接合垫。接合垫是与其基板上所形成的电路连接,用以接合到另一个基板上的电路。两个基板的接合层的多个接合垫的位置是相同。在后续的封装制作工艺中,两个基板是相对,且通过接合层的接合可以构成整体的集成电路。

在上述的封装过程中,如果两个基板之间的接合力不足时,在后续电路切割成单个的芯片(die)时,可能因为接合力不足造成接合垫的接触不良或是甚至分离,其结果导致集成电路的制造失败,降低制造的良率(yield)。两个基板之间的接合力有需要提升来至少减少后续切割芯片时造成电路的损坏。

发明内容

本发明提出在基板上的接合垫图案的规划,可以提升接合层的接合程度,减少两个基板之间的接合层分离的现象。

在一实施例中,本发明提出一种半导体元件封装结构,包括第一基板、第二基板以及接合层。接合层将所述第一基板与所述第二基板接合。所述接合层包含形成在介电层中的内部接合垫图案与外部接合垫图案,所述外部接合垫图案围绕所述内部接合垫图案。所述外部接合垫图案的第一接合垫密度是大于所述内部接合垫图案的第二接合垫密度。

在一实施例中,对于所述的半导体元件封装结构,所述外部接合垫图案中的相邻两个接合垫之间在所述第一接合垫密度下有第一距离,所述内部接合垫图案中的相邻两个接合垫之间在所述第二接合垫密度下有第二距离,其中所述第一距离小于所述第二距离。

在一实施例中,对于所述的半导体元件封装结构,所述第一基板包含第一接合层且所述第二基板包含第二接合层,其中所述第一接合层与所述第二接合层接合在一起成为所述接合层。

在一实施例中,对于所述的半导体元件封装结构,所述外部接合垫图案是虚置图案,所述内部接合垫图案是连接于所述第一基板中的电路与所述第二基板中的电路之间。

在一实施例中,对于所述的半导体元件封装结构,所述内部接合垫图案的多个接合垫是均匀分布在正方形区域、长方形区域或是圆形区域中。

在一实施例中,对于所述的半导体元件封装结构,所述外部接合垫图案的多个接合垫是分布成至少一垫圈,围绕所述内部接合垫图案。

在一实施例中,对于所述的半导体元件封装结构,所述外部接合垫图案的多个接合垫包含多个垫圈,围绕所述内部接合垫图案。

在一实施例中,对于所述的半导体元件封装结构,所述多个垫圈的所述多个接合垫,在水平方向或是垂直方向对准。

在一实施例中,对于所述的半导体元件封装结构,所述多个垫圈的所述多个接合垫,在水平方向或是垂直方向是交替位移。

在一实施例中,对于所述的半导体元件封装结构,所述外部接合垫图案的多个接合垫是分布成一个垫圈。

在一实施例中,对于所述的半导体元件封装结构,所述外部接合垫图案是直角四边形,所述直角四边形的每一边包含沿着所述边的多个接合垫行。

在一实施例中,对于所述的半导体元件封装结构,在该些接合垫行的每一个中的多个接合垫的分布是相同。

在一实施例中,对于所述的半导体元件封装结构,在该些接合垫行的每一个中的多个接合垫的分布,对于相邻两个该接合垫行是不同。

在一实施例中,对于所述的半导体元件封装结构,所述外部接合垫图案的多个接合垫是分布成至少两个垫圈,其中所述至少两个垫圈的内圈的垫分布包含不连续区域,在所述直角四边形的角落处。

在一实施例中,对于所述的半导体元件封装结构,所述至少两个垫圈的多个接合垫在所述直角四边形的每一边是分布成至少两个接合垫行,所述至少两个接合垫行的每一个的长度是等于对应边的长度。

附图说明

包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

图1A到图1C是两个基板接合机制示意图;

图2是在基板上的接合垫图案的示意图;

图3到图6是依据本发明多个实施例,在基板上的接合垫图案的示意图;及

图7是依据本发明多个实施例,检视接合层的接合品质示意图。

附图标号说明

50、50A:基板

52、52A:内联机层

54、54A:接合层

56、56A:接合垫

57:内部接合垫图案

58:外部接合垫图案

58a、58b、58c:接合垫

60:内部区域

62:外部区域

64:刀工具

d1、d2:距离

具体实施方式

本发明是关于半导体的封装技术。通过在基板上的接合垫图案的规划,本发明可以提升两个基板之间的接合层的接合程度。本发明可以减少例如切个芯片时造成两个基板之间的接合层分离的现象。

以下举一些实施例来说明本发明,但是本发明不限于所举的多个实施例。所举的多个实施例之间也允许有是可能结合。

对于基板与基本板之间的接合技术有多种方式,其中例如是介电层对介电层(dielectric-to-dielectric)的接合技术。介电层对介电层接合的机制是利用介电层与介电层之间在相对较低温下进行或化学反应,使介电材料接合。而介电层之间的接合垫(Bonding Pad)会接触达到电性连接。其后会再进行较高温的回火(annealing)过程,加强接合的强度,而接合垫之间的接合程度回进一步达到良好接合。

图1A到图1C是两个基板接合机制示意图。参阅图1A,载两个基板50、50A中分别完成所预定的电路结构,在基板50、50A的上端例如也会分别形成内联机层52、52A,其也可以例如是重新分布层(redistribution layer,RDL),可以将连接端点较平均地重新分布,使两个内联机层52、52A之间预定要电性连接的端点配置在相同位置,以使在两个基板50、50A的两个电路连接成一个整体的电路。针对要连接的端点会通接合层(bonding layer)54、54A形成对应连接的端点的多个接合垫56、56A。接合层54、54A的材料包含介电层,而多个接合垫56、56A以相同的图案分别形成在两个基板50、50A的接合层54、54A中。接合垫56、56A例如是铜,或是所选择的金属或是导电材料。本发明的接合垫56、56A不限于特定材料。两个基板50、50A上的电路结构是分别制造完成。

参阅图1B,将两个基板50、50A的接合层54、54A相互对准后进行第一阶段的介电材料接合,例如是在相对较低温下进行介电材料之间化学反应,使介电材料接合。属于两个基板50、50A的对应接合垫56、56A会接触连接。介电材料一般例如是氧化硅,但是不限于此。介电材料又例如也可以是氮氧化硅、氮化硅、或是其相似材料等。

参阅图1C,将两个基板50、50A的接合层54、54A之间通过第一阶段的接合后,再将行较高温的回火(annealing)得到接合层54B。回火的作用再强化介电材料之间的接合力,也同时促使接合垫56、56A有更良好的接合。

图2是在基板上的接合垫图案的示意图。以基板50上的接合层为例,本发明观察到在接合层54中的多个接合垫56的密度即使经由内联机层52的重新规划,其密度相对地仍是稀疏的分布。这是因为两个电路之间实际要连接的端点数量不多。于此,一个端点可能会配置多个接合垫56,但是其密度仍是相对地小,其可能会造成两个基板之间的接合力不足,导致两个基板在切割机片时分离。本发明至少探究(look into)在接合层54的接合垫56的问题后提出关于在接合层54中的接合垫的规划。

图3到图6是依据本发明多个实施例,在基板上的接合垫图案的示意图。

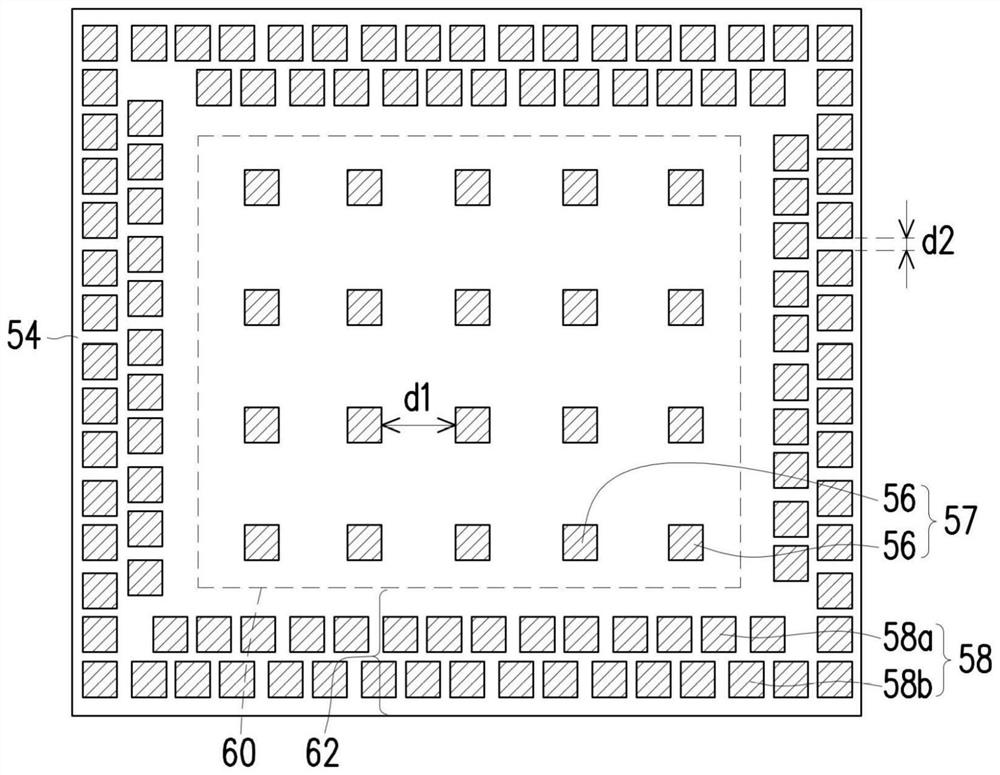

参阅图3,以下以基板50的接合层54为例来描述接合垫图案(pattern)的规划。在基板50A的接合层54A的接合垫图案是与基板50的接合层54的接合垫图案相同,其例如经由图1A到图1C的接合达到两个电路的整体连接。

在一实施例中,接合层54包含内部区域60与外部区域62。外部区域62是环绕内部区域60。内部区域60的几何形状例如是长方形或是正方形,但是不限于此。内部区域60的几何形状有可以是圆形或是其它图形。以下以长方形或是正方形为例来说明。

在内部区域60中有多个接合垫56,其均匀分布构成内部接合垫图案57。在外部区域62中有多个接合垫58a、58b构成外部接合垫图案58。接合层54包含介电层,其包围内部的接合垫56与外部的接合垫58a、58b。内部接合垫图案57是用于电路的实际接合。外部接合垫图案58是虚置的接合垫58a、58b,位于在接合层54的外部区域62,可以增强接合后的接合力。

在切割芯片时,切割的外力会沿着切割线(scribe line)施加,此接合层54的边缘会受到切割力的施加,容易破损。虚置的外部接合垫图案58可以承受切割力。如此,外部接合垫图案58的接合垫密度要大于内部接合垫图案57的接合垫密度。

关于接合垫密度的大小,在一实施例中,外部接合垫图案58中的相邻两个接合垫之间,在预定的第一接合垫密度下有一距离d2。在内部接合垫图案57中的相邻两个接合垫之间,在预定的第二接合垫密度下有一距离d1。高密度的距离d2是小于低密度的距离d1。由于外部接合垫图案58的接合垫58a、58b的接合垫密度大,其机械强度以及结合力是较大,能够承受切割外力。两个接合层54、54A较不易分离。

在内部接合垫图案57的多个接合垫56的分布可以依照电路接合的实际需要来规划。在外部接合垫图案58的多个接合垫58a、58b采用较大密度来规划。在一实施例中,在外部接合垫图案58的多个接合垫58a、58b例如以两垫圈(pad ring)为例。多个接合垫58a构成内垫圈,接合垫58b构成外垫圈。基于内部区域60的几何形状,接合垫所构成的内垫圈或外垫圈可以是连续,也可以包含不连续的局部区域,例如是内垫圈在角落处会有局部区域是不连续。另外,内垫圈的接合垫58a与外垫圈的接合垫58b可以是交替移位的规划。在垂直方向,例如长方形的宽边的方向,接合垫58a与接合垫58b是左右移位。类似地,在水平方向,例如长方形的长边的方向,接合垫58a与接合垫58b是上下移位。如此,内垫圈接合垫58a可以阻檔由外垫圈的接合垫58b之间通过的应力。在一实施例中,外部接合垫图案58的多个接合垫58a、58b不需要与内部接合垫图案57的多个接合垫56的延伸方向对准。然而本发明不限于图3的外部接合垫图案58的多个接合垫58a、58b的规划。

参阅图4,在一实施例中,外部接合垫图案58的多个接合垫58a、58b所构成内垫圈的接合垫58a与外垫圈的接合垫58b也是可以对准。

在一实施例中,以长方形的宽边与长边来看,其边上可以叠置多个行(row)的接合垫58a、58b,其例如两行的接合垫58a、58b,但是如后面会描述,本发明不限于此规划。图4的接合垫58a、58b的规划仅是所取用来说明的实施例。在一实施例中,在角落(corner)的接合垫58a、58b也可以不需要设置。接合垫58a、58b的几何形状也例如可以是长方形、多角形或是圆形,而不限于正方形。在一实施例中,例如图4A,接合垫58a、58b的几何形状是以圆形为例。在一实施例中,例如图4B,接合垫58a、58b的几何形状是以六角形为例。

在一实施例中,参阅图5,外部接合垫图案58的多个接合垫也例如可以是单垫圈的规划,其也能够增强在周边的接合力强度,不限于图3、图4的两个垫圈规划。

在一实施例中,参阅图6,外部接合垫图案58的多个接合垫也例如可以是多垫圈的规划,例如是三圈的规划,不限于图3、图4的两圈规划。在三垫圈的接合垫58a、58b、58c是以图3或图4的两个垫圈规划为基础再加上接合垫58c的一个垫圈。

也就是说,外部接合垫图案58的接合垫的规划可以依照实际需要改变,以较大的接合垫密度来增强在周边区域的机械强度以及接合力,减少在切割时两个基板的分离。

图7是依据本发明多个实施例,检视接合层的接合品质示意图。参阅图7,本发明针对接合层54B的两个接合层54、54A之间接合力进行测试。例如使用刀工具64变化施加的外力,观察可以使两个接合层54、54A剥离施力大小来判断接合力的大小。从测试数据来看,当周边的密度增加时,产生剥离的应力也增加,且是大于线性的一次方(one-order)的增加率。也就是,本发明的外部接合垫图案58的设置,可以有效防止两个接合层54、54A的剥离。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 半导体元件以及半导体元件的封装结构

- 半导体元件、封装结构、及半导体元件的形成方法