阵列基板、显示设备和制造阵列基板的方法

文献发布时间:2023-06-19 11:14:36

技术领域

本发明涉及显示技术,更具体地,涉及阵列基板、显示设备和制造阵列基板的方法。

背景技术

近年来,提出和开发了小型化的光电器件,包括微发光二极管(micro LED,微LED)。基于微LED的显示面板具有高亮度、高对比度、快速响应以及低功耗的优点。基于微LED的显示技术在显示领域中获得了广泛的应用,包括智能电话和智能手表。

发明内容

一方面,本发明提供了一种阵列基板,其包括:数据线;第一电压供应线;第二电压供应线;和像素驱动电路;其中,像素驱动电路包括第一组的一个或多个晶体管和第二组的一个或多个晶体管;其中,第一组中的至少一个晶体管的源电极和漏电极、数据线、第一电压供应线和第二电压供应线位于相同层;并且,第二组中的至少一个晶体管的源电极和漏电极位于与第一电压供应线和第二电压供应线不同的层。

可选地,像素驱动电路还包括存储电容器;存储电容器包括第一电容器电极、第二电容器电极和位于第一电容器电极与第二电容器电极之间的绝缘层;第二组包括驱动晶体管;第一电容器电极连接至驱动晶体管的栅电极;并且第二电容器电极连接至电压电源。

可选地,阵列基板还包括:层间介电层,其位于第二电容器电极的远离绝缘层的一侧并且与第二电容器电极直接接触;其中,第一电压供应线和第二电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极以及数据线与层间介电层直接接触,并且位于层间介电层的远离第二电容器电极的一侧。

可选地,第一组中的所述至少一个晶体管的源电极和漏电极、数据线、第二电压供应线、第一电压供应线以及连接电极位于相同层;第二组包括输出晶体管;并且连接电极将第二组中的输出晶体管的漏电极与阳极接触焊盘相连接。

可选地,阵列基板还包括:层间介电层,其位于第二电容器电极的远离绝缘层的一侧并且与第二电容器电极直接接触;其中,第一电压供应线、第二电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极与层间介电层直接接触,并且位于层间介电层的远离第二电容器电极的一侧。

可选地,阵列基板还包括:平坦化层,其位于第二电压供应线和第一电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极的远离层间介电层的一侧;阴极接触焊盘,其位于平坦化层的远离第一电压供应线的一侧,并且延伸穿过平坦化层以连接至第一电压供应线;以及,阳极接触焊盘,其位于平坦化层的远离连接电极的一侧,并且延伸穿过平坦化层以连接至连接电极;其中,平坦化层在第一侧与阴极接触焊盘和阳极接触焊盘直接接触,并且在与第一侧相对的第二侧与第一电压供应线、第二电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极直接接触。

可选地,第二组中的所述至少一个晶体管的源电极和漏电极与第二电容器电极位于相同层。

可选地,第二组中的所述至少一个晶体管的源电极和漏电极与第二组中的所述至少一个晶体管的有源层位于相同层,并且由半导体材料制成。

可选地,像素驱动电路包括电流调制子电路和持续时间调制子电路;其中,电流调制子电路配置为基于数据信号生成补偿电流信号,并且将补偿电流信号发送至持续时间调制子电路;并且,持续时间调制子电路配置为从电流调制子电路接收补偿电流信号,并且基于补偿电流信号的时间积分来控制与持续时间调制子电路连接的电组件。

可选地,电流调制子电路包括:驱动晶体管;存储电容器;第一晶体管,其具有与复位控制信号线连接的栅电极、与复位信号线连接的源电极以及与第一电容器电极和驱动晶体管的栅电极连接的漏电极;第二晶体管,其具有与第一栅线连接的栅电极、与数据线连接的源电极以及与驱动晶体管的源电极连接的漏电极;第三晶体管,其具有与第一栅线连接的栅电极、与第一电容器电极和驱动晶体管的栅电极连接的源电极以及与驱动晶体管的漏电极连接的漏电极;第四晶体管,其具有与发光控制信号线连接的栅电极、与第二电压供应线连接的源电极以及与驱动晶体管的源电极和第二晶体管的漏电极连接的漏电极;以及,第五晶体管,其具有与发光控制信号线连接的栅电极、与驱动晶体管的漏电极和第三晶体管的漏电极连接的源电极以及与持续时间调制子电路连接的漏电极;其中,持续时间调制子电路包括:输出晶体管,其具有与第五晶体管的漏电极连接的源电极以及与连接电极连接的漏电极;第六晶体管,其具有与第二栅线连接的栅电极、与数据线连接的源电极以及与输出晶体管的栅电极连接的漏电极;以及,电容器,其具有与第六晶体管的漏电极和输出晶体管的栅电极连接的第一电极以及配置为提供有公共电压的第二电极。

可选地,驱动晶体管、第四晶体管、第五晶体管和输出晶体管中的任一个的源电极和漏电极位于与第一电压供应线和第二电压供应线不同的层。

可选地,驱动晶体管、第四晶体管、第五晶体管和输出晶体管的各源电极和各漏电极位于与第一电压供应线和第二电压供应线不同的层。

可选地,阵列基板还包括与像素驱动电路连接的微发光二极管(微LED)。

可选地,阵列基板还包括:层间介电层,其位于第二电容器电极的远离绝缘层的一侧并且与第二电容器电极直接接触;平坦化层,其位于第一电压供应线和第二电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极的远离层间介电层的一侧;阴极接触焊盘,其位于平坦化层的远离第一电压供应线的一侧,并且延伸穿过平坦化层以连接至第一电压供应线;以及,阳极接触焊盘,其位于平坦化层的远离连接电极的一侧,并且延伸穿过平坦化层以连接至连接电极;其中,第一组中的所述至少一个晶体管的源电极和漏电极、数据线、第二电压供应线、第一电压供应线以及连接电极位于相同层;第二组包括输出晶体管;连接电极将输出晶体管的漏电极与阳极接触焊盘相连接;第一电压供应线和第二电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极与层间介电层直接接触,并且位于层间介电层的远离第二电容器电极的一侧;并且,平坦化层在第一侧与阴极接触焊盘和阳极接触焊盘直接接触,并且在与第一侧相对的第二侧与第一电压供应线和第二电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极直接接触;其中,微LED包括:第一类型掺杂半导体层;第二类型掺杂半导体层;量子阱层,其连接第一类型掺杂半导体层和第二类型掺杂半导体层;N焊盘,其与第一类型掺杂半导体层电连接;以及P焊盘,其与第二类型掺杂半导体层电连接;其中,N焊盘与阴极接触焊盘直接接触,并且P焊盘与阳极接触焊盘直接接触。

另一方面,本发明提供了一种显示设备,其包括本文所述的或通过本文所述方法制造的阵列基板以及与阵列基板连接的一个或多个集成电路;

另一方面,本发明提供了一种制造阵列基板的方法,包括:形成数据线;形成第一电压供应线;形成第二电压供应线;以及形成像素驱动电路;其中,形成像素驱动电路包括形成第一组的一个或多个晶体管和形成第二组的一个或多个晶体管;其中,使用相同材料和相同掩膜板在相同层形成第一组中的至少一个晶体管的源电极和漏电极、数据线、第二电压供应线和第一电压供应线;并且,在与第一电压供应线和第二电压供应线不同的层形成第二组中的至少一个晶体管的源电极和漏电极。

可选地,形成像素驱动电路还包括形成存储电容器;形成存储电容器包括形成第一电容器电极、形成第二电容器电极和形成绝缘层,绝缘层形成于第一电容器电极与第二电容器电极之间;第二组包括驱动晶体管;第一电容器电极连接至驱动晶体管的栅电极;并且第二电容器电极连接至电压电源。

可选地,所述方法还包括:形成阳极接触焊盘;形成阴极接触焊盘;以及形成将第二组中的输出晶体管的漏电极与阳极接触焊盘相连接的连接电极;其中,使用相同材料和相同掩膜板在相同层形成第一组中的所述至少一个晶体管的源电极和漏电极、数据线、第二电压供应线、第一电压供应线和连接电极。

可选地,使用相同材料和相同掩膜板在相同层形成第二组中的所述至少一个晶体管的源电极和漏电极以及第二电容器电极。

可选地,使用相同半导体材料和相同掩膜板在相同层形成第二组中的所述至少一个晶体管的源电极和漏电极以及第二组中的所述至少一个晶体管的有源层。

可选地,所述方法还包括:在第二电容器电极的远离绝缘层的一侧形成与第二电容器电极直接接触的层间介电层;形成连接电极;在第二电压供应线和第一电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极的远离层间介电层的一侧形成平坦化层;在平坦化层的远离第一电压供应线的一侧形成延伸穿过平坦化层以连接至第一电压供应线的阴极接触焊盘;在平坦化层的远离连接电极的一侧形成延伸穿过平坦化层以连接至连接电极的阳极接触焊盘;以及,在阴极接触焊盘和阳极接触焊盘的远离衬底基板的一侧形成微发光二极管(微LED);其中,使用相同材料和相同掩膜板在相同层形成第一组中的所述至少一个晶体管的源电极和漏电极、数据线、第二电压供应线、第一电压供应线和连接电极;第二组包括输出晶体管;连接电极将输出晶体管的漏电极与阳极接触焊盘相连接;第一电压供应线和第二电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极形成为与层间介电层直接接触,并且形成在层间介电层的远离第二电容器电极的一侧;并且,平坦化层形成为在第一侧与阴极接触焊盘和阳极接触焊盘直接接触,并且形成为在与第一侧相对的第二侧与第二电压供应线和第一电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极直接接触;其中,形成微LED包括形成微LED前体单元;其中,形成微LED前体单元包括:形成第一类型掺杂半导体层;形成第二类型掺杂半导体层;形成连接第一类型掺杂半导体层和第二类型掺杂半导体层的量子阱层;形成与第一类型掺杂半导体层电连接的N焊盘;以及,形成与第二类型掺杂半导体层电连接的P焊盘;其中,所述方法还包括:将微LED前体单元转移至平坦化层的远离第一电压供应线和连接电极的一侧;以及,将N焊盘与阴极接触焊盘接合并且将P焊盘与阳极接触焊盘接合;其中,N焊盘与阴极接触焊盘直接接触,并且P焊盘与阳极接触焊盘直接接触。

附图说明

以下附图仅为根据所公开的各种实施例的用于示意性目的的示例,而不旨在限制本发明的范围。

图1是根据本公开的一些实施例中的阵列基板的平面图。

图2是示出根据本公开的一些实施例中的像素驱动电路的结构的电路示意图。

图3是根据本公开的一些实施例中的第二组中的晶体管之一的平面图。

图4是沿图3中A-A'线的截面图。

图5是根据本公开的一些实施例中的阵列基板的一部分的截面图。

图6是根据本公开的一些实施例中的第二组中的晶体管之一的平面图。

图7是沿图6中B-B'线的截面图。

图8是根据本公开的一些实施例中的阵列基板的一部分的截面图。

图9是根据本公开的一些实施例中的第二组中的晶体管的平面图。

图10是沿图9中C-C'线的截面图。

图11是根据本公开的一些实施例中的阵列基板的一部分的截面图。

图12是根据本公开的一些实施例中的阵列基板的一部分的截面图。

图13是根据本公开的一些实施例中的阵列基板的一部分的截面图。

图14是根据本公开的一些实施例中的阵列基板的一部分的截面图。

图15A至图15G示出了根据本公开的一些实施例中的制造阵列基板的方法。

具体实施方式

现在将参照以下实施例更具体地描述本公开。需注意,以下对一些实施例的描述仅针对示意和描述的目的而呈现于此。其不旨在是穷尽性的或者受限为所公开的确切形式。

本公开特别提供了阵列基板、显示设备和制造阵列基板的方法,其实质上消除了由于相关技术的限制和缺陷而导致的问题中的一个或多个。一方面,本公开提供了一种阵列基板。在一些实施例中,阵列基板包括:数据线;第一电压供应线;第二电压供应线;和像素驱动电路。在一些实施例中,像素驱动电路包括第一组的一个或多个晶体管和第二组的一个或多个晶体管。可选地,第一组中的至少一个晶体管的源电极和漏电极、数据线、第一电压供应线和第二电压供应线位于相同层。可选地,第二组中的至少一个晶体管的源电极和漏电极位于与第一电压供应线和第二电压供应线不同的层。

在一些实施例中,像素驱动电路还包括存储电容器。可选地,存储电容器包括第一电容器电极、第二电容器电极和位于第一电容器电极与第二电容器电极之间的绝缘层。可选地,第二组包括驱动晶体管。可选地,第一电容器电极连接至驱动晶体管的栅电极;并且第二电容器电极连接至电压电源。

如本文所用,术语“相同层”指的是在相同步骤中同时形成的各层之间的关系。在一个示例中,当第一组中的所述至少一个晶体管的源电极和漏电极、数据线、第二电压供应线、第一电压供应线作为在相同材料层中执行的相同构图工艺的一个或多个步骤的结果而形成时,它们位于相同层。在另一个示例中,可以通过同时执行形成第一组中的所述至少一个晶体管的源电极和漏电极的步骤、形成数据线的步骤、形成第二电压供应线的步骤和形成第一电压供应线的步骤而将第一组中的所述至少一个晶体管的源电极和漏电极、数据线、第二电压供应线、第一电压供应线形成在相同层。术语“相同层”不总是意味着层的厚度或层的高度在截面图中是相同的。

图1是根据本公开的一些实施例中的阵列基板的平面图。参照图1,阵列基板包括子像素Sp的阵列。每个子像素包括电组件,例如,发光元件。在一个示例中,由像素驱动电路PDC驱动发光元件。阵列基板包括栅线GL、数据线DL、第一电压供应线SL1(例如,低电压供应线Vss)和第二电压供应线SL2(例如,高电压供应线Vdd),它们中的每一个均与像素驱动电路PDC连接。像素驱动电路PDC驱动子像素Sp中的对应一个中的发光。

各种适当的像素驱动电路可以用于本阵列基板。适当驱动电路的示例包括3T1C、2T1C、4T1C、4T2C、5T2C、6T1C、7T1C、7T2C和8T2C。在一些实施例中,多个像素驱动电路中的对应一个是3T1C驱动电路。图2是示出根据本公开的一些实施例中的像素驱动电路的结构的电路示意图。参照图2,在一些实施例中,像素驱动电路包括电流调制子电路sc 1和持续时间调制子电路sc2。在一些实施例中,电流调制子电路sc1配置为基于输入至电流调制子电路sc 1的数据信号生成补偿电流信号,并且将补偿电流信号发送至持续时间调制子电路sc2。在一些实施例中,持续时间调制子电路sc2配置为从电流调制子电路sc 1接收补偿电流信号,并且基于补偿电流信号的时间积分来控制与持续时间调制子电路sc2连接的电组件。在一个示例中,持续时间调制子电路sc2配置为从电流调制子电路sc1接收补偿电流信号,并且基于补偿电流信号的时间积分来控制从发光元件LE发射的光的灰度值。图2示出了作为电流调制子电路sc1的6T1C电路。

在本阵列基板中可以使用各种合适的发光元件。适当发光元件的示例包括:有机发光二极管、量子点发光二极管和微发光二极管。可选地,发光元件是微发光二极管。可选地,发光元件是包括有机发光层的有机发光二极管。

在一些实施例中,电流调制子电路sc1包括:驱动晶体管Td;存储电容器Cst;第一晶体管T1,其具有与复位控制信号线Rst连接的栅电极、与复位信号线Vint连接的源电极以及与存储电容器Cst的第一电容器电极Ce1和驱动晶体管Td的栅电极连接的漏电极;第二晶体管T2,其具有与第一栅线GL1连接的栅电极、与数据线DL连接的源电极以及与驱动晶体管Td的源电极连接的漏电极;第三晶体管T3,其具有与第一栅线GL1连接的栅电极、与存储电容器Cst的第一电容器电极Ce1和驱动晶体管Td的栅电极连接的源电极以及与驱动晶体管Td的漏电极连接的漏电极;第四晶体管T4,其具有与发光控制信号线em连接的栅电极、与第二电压供应线SL2连接的源电极以及与驱动晶体管Td的源电极和第二晶体管T2的漏电极连接的漏电极;以及,第五晶体管T5,其具有与发光控制信号线em连接的栅电极、与驱动晶体管Td的漏电极和第三晶体管T3的漏电极连接的源电极以及与持续时间调制子电路sc2连接的漏电极。在一些实施例中,持续时间调制子电路sc2包括:输出晶体管Ts,其具有与第五晶体管T5的漏电极连接的源电极以及与连接电极连接的漏电极,所述连接电极转而连接发光元件LE的P焊盘;第六晶体管T6,其具有与第二栅线GL2连接的栅电极、与数据线DL连接的源电极以及与输出晶体管Ts的栅电极连接的漏电极;以及,电容器C,其具有与第六晶体管T6的漏电极和输出晶体管Ts的栅电极连接的第一电极以及配置为提供有公共电压Vcom的第二电极。

在一些实施例中,第一组的所述一个或多个晶体管是在像素驱动电路PDC的输出时段期间不导通的晶体管,在所述输出时段期间,像素驱动电路PDC向由像素驱动电路PDC驱动的电组件输出电信号。例如,当电组件是发光元件LE时,第一组的所述一个或多个晶体管是在像素驱动电路PDC的输出时段期间不导通的晶体管,在所述输出时段期间,像素驱动电路PDC向发光元件LE输出电信号。参照图2,在一个示例中,第一组的所述一个或多个晶体管包括第一晶体管T1、第二晶体管T2、第三晶体管T3和第六晶体管T6。

在一些实施例中,第二组的所述一个或多个晶体管是在像素驱动电路PDC的输出时段期间导通的晶体管,在所述输出时段期间,像素驱动电路PDC向由像素驱动电路PDC驱动的电组件输出电信号。例如,当电组件是发光元件LE时,第二组的所述一个或多个晶体管是在像素驱动电路PDC的输出时段期间导通的晶体管,在所述输出时段期间,像素驱动电路PDC向发光元件LE输出电信号。参照图2,在一个示例中,第二组的所述一个或多个晶体管包括第四晶体管T4、驱动晶体管Td、第五晶体管T5和输出晶体管Ts。

在一些实施例中,第一组中的所述一个或多个晶体管具有第一沟道尺寸,并且第二组中的所述一个或多个晶体管具有第二沟道尺寸,其中第二沟道尺寸大于第一沟道尺寸。如本文所用,术语“沟道尺寸”在本公开的上下文中指的是诸如晶体管的沟道宽度或者沟道长度或沟道面积之类的沟道尺寸。如本文所用,术语“沟道长度”旨在意指晶体管的沟道部分的尺寸,其中该尺寸表示源电极接触部分与漏电极接触部分之间的最小距离。从顶视图中看,沟道长度通常在与沟道-源极界面、沟道-漏极界面、沟道-源极/漏极界面等实质上垂直的方向上。可选地,沟道长度描述了沟道部分在与当沟道部分“导通(on)”时载流子流动的设计方向平行的方向上的尺寸。例如,沟道长度可以为从晶体管的一个源极/漏极区域到另一个的最短距离。如本文所用,术语“沟道宽度”旨在意指晶体管的沟道部分的尺寸,其中该尺寸表示在与沟道长度实质上垂直的方向上测得的尺寸。从顶视图中看,沟道宽度通常从一个沟道区域-场隔离区域界面到相对的沟道区域-场隔离区域界面延伸。可选地,沟道宽度描述了沟道部分在与当沟道部分“导通(on)”时载流子流动的设计方向垂直的方向上的尺寸。

在一些实施例中,当沟道尺寸是晶体管的沟道宽度或沟道长度时,第二沟道尺寸与第一沟道尺寸之比在2至100(例如,2至5、5至10、10至20、20至30、30至40、40至50、50至60、60至70、70至80、80至90、90至100、100至110、110至120、120至130、130至140、140至150、150至160、160至170、170至180、180至190、或190至200)的范围内。可选地,当沟道尺寸是晶体管的沟道宽度或沟道长度时,第二沟道尺寸与第一沟道尺寸之比在5至50的范围内。在一些实施例中,当沟道尺寸是晶体管的沟道面积时,第二沟道尺寸与第一沟道尺寸之比在5至500(例如,5至10、10至50、50至100、100至150、150至200、200至250、250至300、300至350、350至400、400至450、或450至500)的范围内。可选地,当沟道尺寸是晶体管的沟道面积时,第二沟道尺寸与第一沟道尺寸之比在20至250的范围内。

在一些实施例中,第一组的所述一个或多个晶体管中的对应一个的沟道宽度在2μm至50μm(例如,2μm至4μm、4μm至6μm、6μm至8μm、8μm至10μm、10μm至15μm、15μm至20μm、20μm至25μm、25μm至30μm、30μm至35μm、35μm至40μm、40μm至45μm、或45μm至50μm)的范围内。在一些实施例中,第一组的所述一个或多个晶体管中的对应一个的沟道长度在2μm至50μm(例如,2μm至4μm、4μm至6μm、6μm至8μm、8μm至10μm、10μm至15μm、15μm至20μm、20μm至25μm、25μm至30μm、30μm至35μm、35μm至40μm、40μm至45μm、或45μm至50μm)的范围内。

在一些实施例中,第二组的所述一个或多个晶体管中的对应一个的沟道宽度在50μm至500μm(例如,50μm至100μm、100μm至150μm、150μm至200μm、200μm至250μm、250μm至300μm、300μm至350μm、350μm至400μm、400μm至450μm、或450μm至500μm)的范围内。在一些实施例中,第二组的所述一个或多个晶体管中的对应一个的沟道长度在5μm至50μm(例如,5μm至10μm、10μm至15μm、15μm至20μm、20μm至25μm、25μm至30μm、30μm至35μm、35μm至40μm、40μm至45μm、或45μm至50μm)的范围内。

在一些实施例中,第一组的所述一个或多个晶体管中的对应一个的沟道宽度/沟道长度之比在0.5至2(例如,0.5至1、1至1.5、或1.5至2)的范围内。在一些实施例中,第二组的所述一个或多个晶体管中的对应一个的沟道宽度/沟道长度之比在2至50(例如,2至5、5至10、10至15、15至20、20至25、25至30、30至35、35至40、40至45、或45至50)的范围内。

在一些实施例中,第一组中的所述一个或多个晶体管具有第一沟道宽度/沟道长度之比,并且第二组中的所述一个或多个晶体管具有第二沟道宽度/沟道长度之比,其中第二沟道宽度/沟道长度之比大于第一沟道宽度/沟道长度之比。可选地,第二沟道宽度/沟道长度之比比第一沟道宽度/沟道长度之比大2至50(例如,2至5、5至10、10至15、15至20、20至25、25至30、30至35、35至40、40至45、或45至50)的范围内的因子。

在本公开的上下文中,第一组的所述一个或多个晶体管中的对应一个可以表示为Ty。在本公开的上下文中,第二组的所述一个或多个晶体管中的对应一个可以表示为Tx。

可选地,第二组中的所述一个或多个晶体管中的任一个的源电极和漏电极位于与第一电压供应线SL1和第二电压供应线SL2不同的层。可选地,第二组中的所述一个或多个晶体管中的全部的源电极和漏电极位于与第一电压供应线SL1和第二电压供应线SL2不同的层。

可选地,第一组中的所述一个或多个晶体管中的任一个的源电极和漏电极与第一电压供应线SL1和第二电压供应线SL2位于相同层。可选地,第一组中的所述一个或多个晶体管中的全部的源电极和漏电极与第一电压供应线SL1和第二电压供应线SL2位于相同层。

图3是根据本公开的一些实施例中的第二组中的晶体管的平面图。图4是沿图3中A-A'线的截面图。参照图3和图4,在一些实施例中,第二组的所述一个或多个晶体管中的一个晶体管Tx包括:衬底基板10;有源层ACTx,其位于衬底基板10上;栅绝缘层20,其位于有源层ACTx的远离衬底基板10的一侧;栅电极Gx,其位于栅绝缘层20的远离有源层ACTx的一侧;绝缘层30,其位于栅电极Gx的远离衬底基板10的一侧;层间介电层40,其位于绝缘层30的远离衬底基板10的一侧;源电极Sx和漏电极Dx,其位于层间介电层40的远离衬底基板10的一侧;以及平坦化层50,其位于源电极Sx和漏电极Dx的远离衬底基板10的一侧。可选地,漏电极Dx具有带拐角的U形状。在图4中,源电极Sx和漏电极Dx分别延伸穿过层间介电层40、绝缘层30和栅绝缘层20,以与有源层ACTx连接。

图5是根据本公开的一些实施例中的阵列基板的一部分的截面图。图5示出了阵列基板的具有晶体管Tx的部分。参照图5,该阵列基板包括:衬底基板10;晶体管Tx的有源层ACTx,其位于衬底基板10上;栅绝缘层20,其位于有源层ACTx的远离衬底基板10的一侧;晶体管Tx的栅电极Gx和存储电容器Cst的第一电容器电极Ce1,其位于栅绝缘层20的远离有源层ACTx的一侧;绝缘层30,其位于栅电极Gx和存储电容器Cst的第一电容器电极Ce1的远离衬底基板10的一侧;存储电容器Cst的第二电容器电极Ce2,其位于绝缘层30的远离衬底基板10的一侧;层间介电层40,其位于存储电容器Cst的第二电容器电极Ce2的远离衬底基板10的一侧;数据线DL、晶体管Tx的源电极Sx和漏电极Dx,其位于层间介电层40的远离衬底基板10的一侧;平坦化层50,其位于数据线DL、源电极Sx和漏电极Dx的远离衬底基板10的一侧;钝化层60,其位于平坦化层50的远离衬底基板10的一侧;第一电压供应线SL1、第二电压供应线SL2以及连接电极CE,其位于钝化层60的远离衬底基板10的一侧;第二平坦化层70,其位于第一电压供应线SL1、第二电压供应线SL2以及连接电极CE的远离衬底基板10的一侧;以及,阳极接触焊盘ACP和阴极接触焊盘CCP,其位于第二平坦化层70的远离衬底基板10的一侧。阳极接触焊盘ACP延伸穿过第二平坦化层70以连接至连接电极CE,连接电极CE延伸穿过钝化层60和平坦化层50以连接至晶体管Tx的漏电极Dx。阳极接触焊盘ACP和阴极接触焊盘CCP配置为分别与发光元件(诸如微发光二极管)的P焊盘和N焊盘接触。

为确保像素电流能够驱动像素,像素驱动电路中的晶体管,尤其是驱动晶体管,需要具有相对大的宽/长比(例如,晶体管的沟道宽度/沟道长度比),从而实现较强的驱动能力。例如,图3和图4示出了像素驱动电路中具有相对大的宽/长比的晶体管的示例。如图5所示,在具有数据线DL、源电极Sx和漏电极Dx的层中,晶体管占据子像素相对大的面积,导致未被占据的空间十分有限。因此,如果第一电压供应线SL1和第二电压供应线SL2被布置在与数据线DL、源电极Sx和漏电极Dx相同的层中,则第一电压供应线SL1和第二电压供应线SL2将必须制作得具有非常有限的线宽。然而,由于阵列基板(例如,具有微发光二极管的阵列基板)中需要使用的相对大的驱动电流,导致在第一电压供应线SL1(例如,低电压供应线Vss)中和在第二电压供应线SL2(例如,高电压供应线Vdd)中存在相对大的欧姆电阻压降。当第一电压供应线SL1和第二电压供应线SL2具有非常有限的线宽时,欧姆电阻压降问题变得尤其严重。

由于在具有数据线DL、源电极Sx和漏电极Dx的所述相同层中剩余的未被占据的空间十分有限,并且考虑到对增大第一电压供应线SL1和第二电压供应线SL2的线宽的需求,在一些实施例(如图5所示)中,本公开在一些实施例中将第一电压供应线SL1和第二电压供应线SL2布置在与数据线DL、源电极Sx和漏电极Dx不同的层中。如图5所示,第一电压供应线SL1、第二电压供应线SL2以及连接电极CE在与数据线DL、源电极Sx和漏电极Dx不同的层中并且位于钝化层60和平坦化层50的远离数据线DL、源电极Sx和漏电极Dx的一侧。因此,图5的阵列基板需要额外的掩膜板和与额外的掩膜板工艺相关联的额外的制造成本。此外,图5的阵列基板具有增大的厚度。

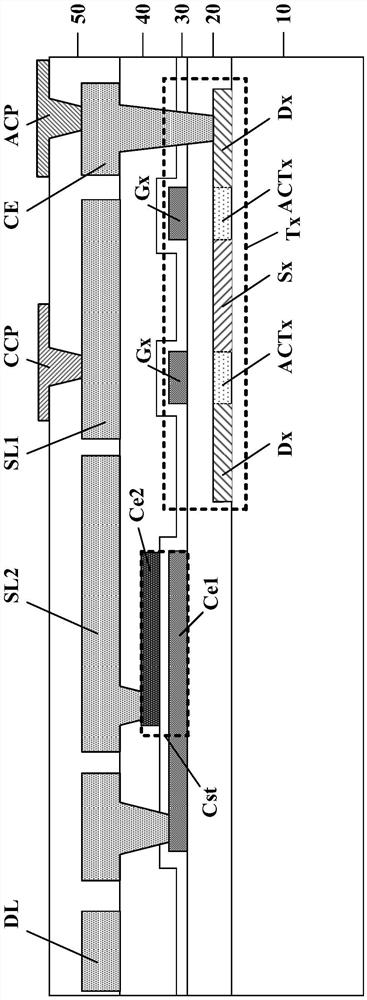

图6是根据本公开的一些实施例中的第二组中的晶体管的平面图。图7是沿图6中B-B'线的截面图。参照图6和图7,在一些实施例中,第二组的所述一个或多个晶体管中的一个晶体管Tx包括:衬底基板10;有源层ACTx,其位于衬底基板10上;栅绝缘层20,其位于有源层ACTx的远离衬底基板10的一侧;栅电极Gx,其位于栅绝缘层20的远离有源层ACTx的一侧;绝缘层30,其位于栅电极Gx的远离衬底基板10的一侧;源电极Sx和漏电极Dx,其位于绝缘层30的远离衬底基板10的一侧;以及层间介电层40,其位于源电极Sx和漏电极Dx的远离衬底基板10的一侧。可选地,漏电极Dx具有带拐角的U形状。在图6中,源电极Sx和漏电极Dx分别延伸穿过绝缘层30和栅绝缘层20,以与有源层ACTx连接。

图8是根据本公开的一些实施例中的阵列基板的一部分的截面图。图8示出了阵列基板的具有晶体管Tx的部分。参照图8,该阵列基板包括:衬底基板10;晶体管Tx的有源层ACTx,其位于衬底基板10上;栅绝缘层20,其位于有源层ACTx的远离衬底基板10的一侧;晶体管Tx的栅电极Gx和存储电容器Cst的第一电容器电极Ce1,其位于栅绝缘层20的远离有源层ACTx的一侧;绝缘层30,其位于栅电极Gx和存储电容器Cst的第一电容器电极Ce1的远离衬底基板10的一侧;存储电容器Cst的第二电容器电极Ce2、晶体管Tx的源电极Sx和漏电极Dx,其位于绝缘层30的远离衬底基板10的一侧;层间介电层40,其位于存储电容器Cst的第二电容器电极Ce2、晶体管Tx的源电极Sx和漏电极Dx的远离衬底基板10的一侧;数据线DL、第一电压供应线SL1、第二电压供应线SL2以及连接电极CE,其位于层间介电层40的远离衬底基板10的一侧;平坦化层50,其位于数据线DL、第一电压供应线SL1、第二电压供应线SL2以及连接电极CE的远离衬底基板10的一侧;以及,阳极接触焊盘ACP和阴极接触焊盘CCP,其位于平坦化层50的远离衬底基板10的一侧。阳极接触焊盘ACP延伸穿过平坦化层50以连接至连接电极CE,连接电极CE延伸穿过层间介电层40以连接至晶体管Tx的漏电极Dx。阳极接触焊盘ACP和阴极接触焊盘CCP配置为分别与发光元件(诸如微发光二极管)的P焊盘和N焊盘接触。在图8中,晶体管Tx(例如,第二组的所述至少一个或多个晶体管中的所述至少一个)的源电极Sx和漏电极Dx与第二电容器电极Ce2位于相同层。

图9是根据本公开的一些实施例中的第二组中的晶体管的平面图。图10是沿图9中C-C'线的截面图。参照图9和图10,在一些实施例中,第二组的所述一个或多个晶体管中的一个晶体管Tx包括:衬底基板10;有源层ACTx、源电极Sx和漏电极Dx,其位于衬底基板10上;栅绝缘层20,其位于有源层ACTx、源电极Sx和漏电极Dx的远离衬底基板10的一侧;栅电极Gx,其位于栅绝缘层20的远离有源层ACTx的一侧;绝缘层30,其位于栅电极Gx的远离衬底基板10的一侧;以及层间介电层40,其位于绝缘层30的远离衬底基板10的一侧。在一些实施例中,如图10所示,源电极Sx和漏电极Dx以及有源层ACTx是单个结构的各部分。在一些实施例中,第二组的所述一个或多个晶体管中的所述至少一个晶体管的源电极Sx和漏电极Dx与第二组中的所述一个或多个晶体管中的所述至少一个晶体管的有源层ACTx位于相同层并且由半导体材料制成。在一个示例中,首先在衬底基板10上沉积半导体材料层,并且随后对半导体材料层进行构图以形成与源电极Sx、漏电极Dx以及有源层ACTx相对应的第二半导体材料层。随后,在一个示例中,处理(例如,通过掺杂处理)第二半导体材料层的与源电极Sx和漏电极Dx相对应的区域,以使得它们更具导电性,从而形成源电极Sx、漏电极Dx以及有源层ACTx。

图11是根据本公开的一些实施例中的阵列基板的一部分的截面图。图11示出了阵列基板的具有晶体管Tx的部分。参照图11,该阵列基板包括:衬底基板10;晶体管Tx的有源层ACTx、源电极Sx和漏电极Dx,其位于衬底基板10上;栅绝缘层20,其位于有源层ACTx、源电极Sx和漏电极Dx的远离衬底基板10的一侧;晶体管Tx的栅电极Gx和存储电容器Cst的第一电容器电极Ce1,其位于栅绝缘层20的远离有源层ACTx的一侧;绝缘层30,其位于栅电极Gx和存储电容器Cst的第一电容器电极Ce1的远离衬底基板10的一侧;存储电容器Cst的第二电容器电极Ce2,其位于绝缘层30的远离衬底基板10的一侧;层间介电层40,其位于存储电容器Cst的第二电容器电极Ce2的远离衬底基板10的一侧;数据线DL、第一电压供应线SL1、第二电压供应线SL2以及连接电极CE,其位于层间介电层40的远离衬底基板10的一侧;平坦化层50,其位于数据线DL、第一电压供应线SL1、第二电压供应线SL2以及连接电极CE的远离衬底基板10的一侧;以及,阳极接触焊盘ACP和阴极接触焊盘CCP,其位于平坦化层50的远离衬底基板10的一侧。阳极接触焊盘ACP延伸穿过平坦化层50以连接至连接电极CE。连接电极CE延伸穿过层间介电层40、绝缘层30和栅绝缘层20,以与晶体管Tx的漏电极Dx连接。阳极接触焊盘ACP和阴极接触焊盘CCP配置为分别与发光元件(诸如微发光二极管)的P焊盘和N焊盘接触。

将图8和图11中的阵列基板与图5中的阵列基板比较,图8和图11的阵列基板将晶体管Tx的源电极Sx和漏电极Dx布置在与数据线DL不同的层中。因此,具有数据线DL的层具有足够空间来布置第一电压供应线SL1、第二电压供应线SL2以及连接电极CE。此外,第一电压供应线SL1和第二电压供应线SL2可以具有相对大的线宽以降低欧姆电阻压降。晶体管Tx的源电极Sx和漏电极Dx形成为与第二电容器电极CE2位于相同层(图8)或者与有源层ACTx位于相同层(图11),与图5中的阵列基板相比,无需额外的掩膜板,从而节约了制造成本。

图12是根据本公开的一些实施例中的阵列基板的一部分的截面图。图13是根据本公开的一些实施例中的阵列基板的一部分的截面图。参照图12和图13,在一些实施例中,阵列基板还包括诸如微发光二极管之类的发光元件LE。在一些实施例中,发光元件LE包括N焊盘CD和P焊盘AD。N焊盘CD与阴极接触焊盘CCP接合,并且P焊盘AD与阳极接触焊盘ACP接合。在一些实施例中,发光元件LE还包括:第一类型掺杂半导体层;量子阱层;以及,第二类型掺杂半导体层。

可选地,使用P掺杂半导体材料形成第一类型掺杂半导体层,并且使用N掺杂半导体材料形成第二类型掺杂半导体层。可选地,使用N掺杂半导体材料形成第一类型掺杂半导体层,并且使用P掺杂半导体材料形成第二类型掺杂半导体层。在一个示例中,P掺杂半导体材料包括p-GaN。在另一个示例中,N掺杂半导体材料包括N-GaN。可选地,量子阱层包括多量子阱(MQW)。在一个示例中,量子阱层包括具有多量子阱的单个层。在另一个示例中,量子阱层包括具有多量子阱的多个子层。可选地,通过金属有机化学气相沉积单独地形成第一类型掺杂半导体层、量子阱层和第二类型掺杂半导体层。

可选地,发光元件LE包括:第一类型掺杂半导体层;第二类型掺杂半导体层;量子阱层,其连接第一类型掺杂半导体层和第二类型掺杂半导体层;N焊盘CD,其与第一类型掺杂半导体层电连接;以及P焊盘AD,其与第二类型掺杂半导体层电连接。可选地,N焊盘CD与阴极接触焊盘CCP直接接触,并且P焊盘AD与阳极接触焊盘ACP直接接触。

参照图2、图5、图8、图11、图12和图13,在一些实施例中,存储电容器Cst包括第一电容器电极Ce1、第二电容器电极Ce2和位于第一电容器电极Ce1与第二电容器电极Ce2之间的绝缘层30。第一电容器电极Ce1连接至驱动晶体管Td的栅电极。第二电容器电极Ce2连接至电压电源。在一个示例中,电压电源是高电压电源,诸如第二电压供应线SL2(例如,高电压供应线Vdd)。

图14是根据本公开的一些实施例中的阵列基板的一部分的截面图。参照图14,在一些实施例中,第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线DL、第二电压供应线SL2和第一电压供应线SL1位于相同层。第二组的所述一个或多个晶体管中的所述至少一个晶体管的源电极Sx和漏电极Dx位于与第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy不同的层。

参照图2、图5、图8以及图11至图14,在一些实施例中,层间介电层40位于存储电容器Cst的第二电容器电极Ce2的远离绝缘层30的一侧,并且层间介电层40与存储电容器Cst的第二电容器电极Ce2直接接触。第二电压供应线SL2和第一电压供应线SL1、第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy以及数据线DL与层间介电层40直接接触,并且位于层间介电层40的远离存储电容器Cst的第二电容器电极Ce2的一侧。

参照图2、图5、图8以及图11至图14,在一些实施例中,第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线DL、第二电压供应线SL2、第一电压供应线SL1以及连接电极CE位于相同层。连接电极CE将第二组中的所述一个或多个晶体管中的一个的漏电极Dx与阳极接触焊盘ACP相连接。在一个示例中,参照图2,第二组中的所述一个或多个晶体管中的所述一个是输出晶体管Ts,并且连接电极CE将输出晶体管Ts的漏电极与阳极接触焊盘ACP相连接。

参照图2、图5、图8以及图11至图14,在一些实施例中,层间介电层40位于存储电容器Cst的第二电容器电极Ce2的远离绝缘层30的一侧,并且与存储电容器Cst的第二电容器电极Ce2直接接触。第二电压供应线SL2、第一电压供应线SL1、第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线SL以及连接电极CE与层间介电层40直接接触,并且位于层间介电层40的远离存储电容器Cst的第二电容器电极Ce2的一侧。

参照图2、图5、图8以及图11至图14,在一些实施例中,平坦化层50位于第二电压供应线SL2和第一电压供应线SL1、第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线DL以及连接电极CE的远离层间介电层40的一侧。阴极接触焊盘CCP位于平坦化层50的远离第一电压供应线SL1的一侧,并且延伸穿过平坦化层50以连接至第一电压供应线SL1。阳极接触焊盘ACP位于平坦化层50的远离连接电极CE的一侧,并且延伸穿过平坦化层50以连接至连接电极CE。平坦化层50在第一侧与阴极接触焊盘CCP和阳极接触焊盘ACP直接接触,并且在与第一侧相对的第二侧与第二电压供应线SL2、第一电压供应线SL1、第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线DL以及连接电极CE直接接触。

在一些实施例中,第四晶体管T4、第五晶体管T5、驱动晶体管Td和输出晶体管Ts中的任一个的源电极和漏电极位于与第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy不同的层。可选地,第四晶体管T4、第五晶体管T5、驱动晶体管Td和输出晶体管Ts中的全部的源电极和漏电极位于与第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy不同的层。可选地,第四晶体管T4、第五晶体管T5、驱动晶体管Td和输出晶体管Ts中的全部的源电极和漏电极位于相同层。

参照图2、图5、图8以及图11至图14,在一些实施例中,层间介电层40位于存储电容器Cst的第二电容器电极Ce2的远离绝缘层30的一侧,并且与存储电容器Cst的第二电容器电极Ce2直接接触。平坦化层50位于第二电压供应线SL2和第一电压供应线SL1、第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线DL以及连接电极CE的远离层间介电层40的一侧。阴极接触焊盘CCP位于平坦化层50的远离第一电压供应线SL1的一侧,并且延伸穿过平坦化层50以连接至第一电压供应线SL1。阳极接触焊盘ACP位于平坦化层50的远离连接电极CE的一侧,并且延伸穿过平坦化层50以连接至连接电极CE。第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线DL、第二电压供应线SL2、第一电压供应线SL1以及连接电极CE位于相同层。连接电极CE将第二组中的所述一个或多个晶体管中的一个的漏电极Dx与阳极接触焊盘ACP相连接。第二电压供应线SL2和第一电压供应线SL1、第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线SL以及连接电极CE与层间介电层40直接接触,并且位于层间介电层40的远离存储电容器Cst的第二电容器电极Ce2的一侧。平坦化层50在第一侧与阴极接触焊盘CCP和阳极接触焊盘ACP直接接触,并且在与第一侧相对的第二侧与第二电压供应线SL2和第一电压供应线SL1、第一组中的所述至少一个晶体管的源电极Sy和漏电极Dy、数据线DL以及连接电极CE直接接触。N焊盘CD与阴极接触焊盘CCP直接接触,并且P焊盘AD与阳极接触焊盘ACP直接接触。

参照图5、图8以及图11至图14,在一些实施例中,晶体管Tx是图2中的输出晶体管Ts

另一方面,本发明提供了一种制造阵列基板的方法。在一些实施例中,所述方法包括:形成数据线;形成第一电压供应线;形成第二电压供应线;以及形成像素驱动电路。在一些实施例中,形成像素驱动电路包括形成第一组的一个或多个晶体管和形成第二组的一个或多个晶体管。可选地,使用相同材料和相同掩膜板在相同层形成第一组中的至少一个晶体管的源电极和漏电极、数据线、第二电压供应线和第一电压供应线。可选地,第二组中的至少一个晶体管的源电极和漏电极形成在与第一电压供应线和第二电压供应线不同的层。

在一些实施例中,形成像素驱动电路还包括形成存储电容器。在一些实施例中,形成存储电容器包括形成第一电容器电极、形成第二电容器电极和形成位于第一电容器电极与第二电容器电极之间的绝缘层。可选地,第二组包括驱动晶体管。可选地,第一电容器电极连接至驱动晶体管的栅电极;可选地,第二电容器电极连接至电压电源。

在一些实施例中,所述方法还包括:形成阳极接触焊盘;形成阴极接触焊盘;以及形成将第二组中的一个或多个晶体管中的一个的漏电极与阳极接触焊盘相连接的连接电极。可选地,使用相同材料和相同掩膜板在相同层形成第一组中的所述至少一个晶体管的源电极和漏电极、数据线、第二电压供应线、第一电压供应线和连接电极。

可选地,使用相同材料和相同掩膜板在相同层形成第二组中的所述一个或多个晶体管中的所述至少一个晶体管的源电极和漏电极以及第二电容器电极。

可选地,使用相同半导体材料和相同掩膜板在相同层形成第二组中的所述一个或多个晶体管中的所述至少一个晶体管的源电极和漏电极以及第二组中的所述一个或多个晶体管中的所述至少一个晶体管的有源层。

在一些实施例中,所述方法还包括:在第二电容器电极的远离绝缘层的一侧形成与第二电容器电极直接接触的层间介电层;形成连接电极;在第二电压供应线和第一电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极的远离层间介电层的一侧形成平坦化层;在平坦化层的远离第一电压供应线的一侧形成延伸穿过平坦化层以连接至第一电压供应线的阴极接触焊盘;在平坦化层的远离连接电极的一侧形成延伸穿过平坦化层以连接至连接电极的阳极接触焊盘;以及,在阴极接触焊盘和阳极接触焊盘的远离衬底基板的一侧形成微发光二极管(微LED)。可选地,使用相同材料和相同掩膜板在相同层形成第一组中的所述至少一个晶体管的源电极和漏电极、数据线、第二电压供应线、第一电压供应线和连接电极。可选地,连接电极将第二组中的一个或多个晶体管中的一个的漏电极与阳极接触焊盘相连接。可选地,第二电压供应线和第一电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极形成为与层间介电层直接接触,并且形成在层间介电层的远离第二电容器电极的一侧。可选地,平坦化层形成为在第一侧与阴极接触焊盘和阳极接触焊盘直接接触,并且形成为在与第一侧相对的第二侧与第二电压供应线和第一电压供应线、第一组中的所述至少一个晶体管的源电极和漏电极、数据线以及连接电极直接接触。可选地,形成微LED包括形成微LED前体单元。可选地,形成微LED前体单元包括:形成第一类型掺杂半导体层;形成第二类型掺杂半导体层;形成连接第一类型掺杂半导体层和第二类型掺杂半导体层的量子阱层;形成与第一类型掺杂半导体层电连接的N焊盘;以及形成与第二类型掺杂半导体层电连接的P焊盘。可选地,所述方法还包括:将微LED前体单元转移至平坦化层的远离第一电压供应线和连接电极的一侧;将N焊盘与阴极接触焊盘接合并且将P焊盘与阳极接触焊盘接合。可选地,N焊盘与阴极接触焊盘直接接触,并且P焊盘与阳极接触焊盘直接接触。

图15A至图15G示出了根据本公开的一些实施例中的制造阵列基板的方法。参照图15A,在衬底基板10上形成晶体管Tx(第二组的所述一个或多个晶体管中的所述至少一个晶体管)的有源层ACTx。各种适当半导体材料和各种适当制造方法可以用于制作有源层。例如,可以通过等离子体增强化学气相沉积(PECVD)工艺在基板上沉积半导体材料。用于制作有源层的适当半导体材料的示例包括但不限于:金属氧化物(例如,ITO、IZTO、IGTO)、非晶硅、多晶硅等。

参照图15B,在有源层ACTx的远离衬底基板10的一侧形成栅绝缘层20;在栅绝缘层20的远离有源层ACTx的一侧形成晶体管Tx的栅电极Gx和存储电容器Cst的第一电容器电极Ce1。使用相同材料和相同掩膜板在相同层形成晶体管Tx的栅电极Gx和存储电容器Cst的第一电容器电极Ce 1。各种适当的电极材料和各种适当的制造方法可用于制作晶体管Tx的栅电极Gx和存储电容器Cst的第一电容器电极Ce1。例如,可以通过等离子体增强化学气相沉积(PECVD)工艺在基板上沉积电极材料并对其构图。用于制作晶体管Tx的栅电极Gx和存储电容器Cst的第一电容器电极Ce1的适当的电极材料的示例包括但不限于:铝、铜、钼、铬、铝铜合金、铜钼合金、钼铝合金、铝铬合金、铜铬合金、钼铬合金、铜钼铝合金等。

参照图15C,在栅电极Gx和存储电容器Cst的第一电容器电极Ce1的远离衬底基板10的一侧形成绝缘层30;在绝缘层30的远离衬底基板10的一侧形成存储电容器Cst的第二电容器电极Ce2、晶体管Tx的源电极Sx和漏电极Dx。使用相同材料和相同掩膜板在相同层形成存储电容器Cst的第二电容器电极Ce2、晶体管Tx的源电极Sx和漏电极Dx。各种适当的电极材料和各种适当的制造方法可用于制作存储电容器Cst的第二电容器电极Ce2、晶体管Tx的源电极Sx和漏电极Dx。例如,可以通过等离子体增强化学气相沉积(PECVD)工艺在基板上沉积电极材料并对其构图。用于制作存储电容器Cst的第二电容器电极Ce2、晶体管Tx的源电极Sx和漏电极Dx的适当的电极材料的示例包括但不限于:铝、铜、钼、铬、铝铜合金、铜钼合金、钼铝合金、铝铬合金、铜铬合金、钼铬合金、铜钼铝合金等。

参照图15D,在存储电容器Cst的第二电容器电极Ce2、晶体管Tx的源电极Sx和漏电极Dx的远离衬底基板10的一侧形成层间介电层40;在层间介电层40的远离衬底基板10的一侧形成数据线DL、第一电压供应线SL1、第二电压供应线SL2、连接电极CE、第一组的所述至少一个晶体管的源电极Sy和漏电极Dy。使用相同材料和相同掩膜板在相同层形成数据线DL、第一电压供应线SL1、第二电压供应线SL2、连接电极CE、第一组的所述至少一个晶体管的源电极Sy和漏电极Dy。连接电极CE形成为延伸穿过层间介电层40以连接至晶体管Tx的漏电极Dx。第二电压供应线SL2形成为延伸穿过层间介电层40以连接至存储电容器Cst的第二电容器电极Ce2。各种适当的电极材料和各种适当的制造方法可用于制作数据线DL、第一电压供应线SL1、第二电压供应线SL2、连接电极CE、第一组的所述至少一个晶体管的源电极Sy和漏电极Dy。例如,可以通过等离子体增强化学气相沉积(PECVD)工艺在基板上沉积电极材料并对其构图。用于制作数据线DL、第一电压供应线SL1、第二电压供应线SL2、连接电极CE、第一组的所述至少一个晶体管的源电极Sy和漏电极Dy的示例包括但不限于:铝、铜、钼、铬、铝铜合金、铜钼合金、钼铝合金、铝铬合金、铜铬合金、钼铬合金、铜钼铝合金等。

参照图15E,数据线DL、第一电压供应线SL1、第二电压供应线SL2、连接电极CE、第一组的所述至少一个晶体管的源电极Sy和漏电极Dy的远离衬底基板10的一侧形成平坦化层50;以及,在平坦化层50的远离衬底基板10的一侧形成阳极接触焊盘ACP和阴极接触焊盘CCP。阳极接触焊盘ACP形成为延伸穿过平坦化层50以连接至连接电极CE,阴极接触焊盘CCP形成为延伸穿过平坦化层50以连接至第一电压供应线SL1。各种适当的导电材料和各种适当的制造方法可以用于制作阳极接触焊盘ACP和阴极接触焊盘CCP。例如,可以通过等离子体增强化学气相沉积(PECVD)工艺在基板上沉积导电材料并对其构图。用于制作阳极接触焊盘ACP和阴极接触焊盘CCP的适当的导电材料的示例包括但不限于:各种金属、各种合金以及各种导电金属氧化物(例如,氧化铟锡)。

参照图15F,将微LED前体单元PLE转移到平坦化层50的远离第一电压供应线SL1和连接电极CE的一侧。随后将微LED前体单元PLE与阳极接触焊盘ACP和阴极接触焊盘CCP接合。例如,将微LED前体单元PLE的N焊盘CD与阴极接触焊盘CCP接合,并且将微LED前体单元PLE的P焊盘AD与阳极接触焊盘ACP接合。

参照图15G,在阵列基板上形成发光元件LE(例如,微LED)。发光元件LE的N焊盘CD与阴极接触焊盘CCP直接接触,并且发光元件的P焊盘AD与阳极接触焊盘ACP直接接触。

另一方面,本发明提供了一种显示设备,其包括本文所述的或通过本文所述方法制造的阵列基板以及与阵列基板连接的一个或多个集成电路。适当显示设备的示例包括但不限于:电子纸、移动电话、平板计算机、电视、监视器、笔记本计算机、数字相框、GPS等。可选地,所述显示设备还包括与显示面板连接的一个或多个集成电路。

出于示意和描述目的已示出对本发明实施例的上述描述。其并非旨在穷举或将本发明限制为所公开的确切形式或示例性实施例。因此,上述描述应当被认为是示意性的而非限制性的。显然,许多修改和变形对于本领域技术人员而言将是显而易见的。选择和描述这些实施例是为了解释本发明的原理和其最佳方式的实际应用,从而使得本领域技术人员能够理解本发明适用于特定用途或所构思的实施方式的各种实施例及各种变型。本发明的范围旨在由所附权利要求及其等同形式限定,其中除非另有说明,否则所有术语以其最宽的合理意义解释。因此,术语“发明”、“本发明”等不一定将权利范围限制为具体实施例,并且对本发明示例性实施例的参考不隐含对本发明的限制,并且不应推断出这种限制。本发明仅由随附权利要求的精神和范围限定。此外,这些权利要求可涉及使用跟随有名词或元素的“第一”、“第二”等术语。这种术语应当理解为一种命名方式而非意在对由这种命名方式修饰的元素的数量进行限制,除非给出具体数量。所描述的任何优点和益处不一定适用于本发明的全部实施例。应当认识到的是,本领域技术人员在不脱离随附权利要求所限定的本发明的范围的情况下可以对所描述的实施例进行变化。此外,本公开中没有元件和组件是意在贡献给公众的,无论该元件或组件是否明确地记载在随附权利要求中。

- 阵列基板、显示设备和制造阵列基板的方法

- 微发光二极管、阵列基板、显示设备和制造阵列基板的方法