双侧冷却的电子器件

文献发布时间:2023-06-19 13:46:35

背景技术

晶体管和封装电子器件的其它电路元件具有可随工作温度而变化的性能特性。各种电子器件封装类型,如四方扁平无引线(QFN)封装,可以包括暴露的裸片附接焊盘或其它暴露的散热焊盘,以通过封装器件的底部进行冷却。封装电子器件中的横向场效应晶体管(FET)却难以进行冷却。横向FET裸片的顶面具有带有晶体管电节点的焊盘。裸片的底侧有时在接地电位工作。裸片产生的热量通过底侧衬底散发到封装外部。功率密度的增加需要改善的排热功能,以便于切换应用(如DC-DC转换器)中晶体管的操作。通过在裸片和/或封装的底侧进行散热,会导致难以提高功率密度和/或提高宽带隙(WBG)晶体管(如用于在高频下切换高电压的GaN功率级FET)的能量效率。横向FET裸片的焊盘布置会限制热容量有限的焊线或焊料连接凸点在顶部的互连选择。一种QFN封装的冷却方案是通过带有散热孔的印刷电路板(PCB)将热量从裸片附接焊盘(DAP)散发至散热器,其中在散热器和PCB之间设有电隔离热界面材料(TIM)。然而,所述电隔离热界面材料通常是不良的热导体。

发明内容

描述了一种封装电子器件,其包括:裸片附接焊盘;第一和第二半导体裸片,所述第一和第二半导体裸片的第一侧连接至所述裸片附接焊盘的第一侧;衬底;以及封装结构,其包围所述半导体裸片和所述裸片附接焊盘和所述衬底的一部分。所述衬底包括陶瓷层、在所述陶瓷层的第一侧上形成的第一金属层,以及在所述陶瓷层的第二侧上形成的第二金属层。所述第二金属层连接至所述半导体裸片的所述第二侧。所述封装结构的第一侧暴露所述衬底的所述第一金属层的一部分,并且所述封装结构的第二侧暴露所述裸片附接焊盘的第二侧的一部分。

在另一方面,一种封装电子器件包括:封装结构,其包围第一半导体裸片和第二半导体裸片;裸片附接焊盘,其焊接至所述半导体裸片之一并所述沿封装结构的一侧暴露;以及衬底,其具有沿所述封装结构的另一侧暴露的第一金属层、焊接至所述半导体裸片的第二金属层,以及延伸于所述第一金属层和所述第二金属层之间并将其分隔开的隔离层。

一种描述的方法包括将第一和第二半导体裸片的第一侧附接至裸片附接焊盘的第一侧,将衬底一侧的金属层附接至所述半导体裸片的第二侧,以及形成包围所述半导体裸片的封装结构,其中所述封装结构包括暴露所述衬底一侧的第一金属层的第一侧和暴露所述裸片附接焊盘的一侧的第二侧。

附图说明

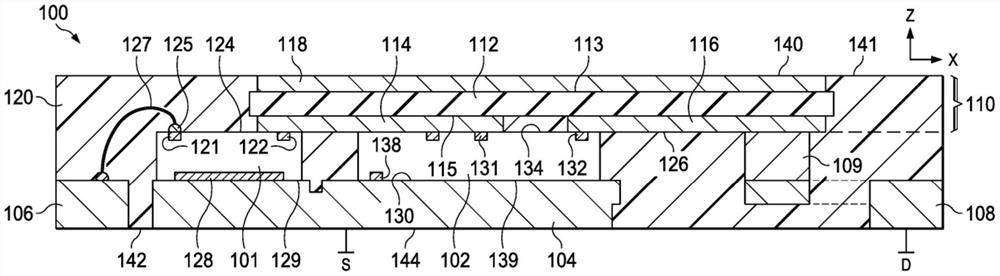

图1是沿图2和3中的线1-1截取的封装电子器件的截面侧视图。

图2是图1的封装电子器件的顶部透视图。

图3是图1和2的封装电子器件的底部透视图。

图4是一种用于制作封装电子器件的方法的流程图。

图5是沿图6和7中的线5-5截取的图1至3的封装电子器件的衬底的截面侧视图。

图6是图5和7的衬底的顶部透视图。

图7是图5和6的衬底的底部透视图。

图8是具有裸片附接焊盘和引线的引线框架的截面侧视图。

图9是设置在裸片附接焊盘第一侧上的第一和第二半导体裸片的截面侧视图。

图10是设置在引线框架的次引线一侧上的导电柱的截面侧视图。

图11是沿图12的线11-11截取的半导体裸片和引线框架的截面侧视图,示出了将半导体裸片焊接至裸片附接焊盘并将导电柱焊接至次引线的回流工艺。

图12是经图11的回流工艺处理后的半导体裸片和引线框架的顶部透视图。

图13是设置在图11和12的半导体裸片和导电柱上的图5至7的衬底的截面侧视图。

图14是沿图15的线14-14截取的截面侧视图,示出了将半导体裸片顶侧的触点焊接至衬底的图案化金属层的第二回流工艺。

图15是经图14的回流工艺处理后半导体裸片和衬底的顶部透视图。

图16是经引线接合工艺处理后,焊接至半导体裸片和导电柱的顶侧的衬底的截面侧视图。

图17是经模制工艺处理以形成封装结构后,焊接至半导体裸片和导电柱的顶侧的衬底的截面侧视图。

图18是另一示例性封装电子器件的截面侧视图。

具体实施方式

在附图中,相同的参考数字始终指代相同的元件,并且各种特征不一定按比例绘制。此外,术语“耦合(couple或couples)”包括间接或直接的电或机械连接或其组合。例如,如果第一器件耦合到或与第二器件耦合,则该连接可以是通过直接电连接,或通过经由一或多个中间器件和连接件的间接电连接。

图1至3示出了提供顶侧和底侧排热路径的示例性封装电子器件100,其可以与横向FET和其它电路元件结合使用。图1示出了沿图2和3中的线1-1截取的封装电子器件100的截面图,图2示出了封装电子器件100的顶部透视图,图3示出了封装电子器件100的底部透视图。示例性封装电子器件100包括第一半导体裸片101和第二半导体裸片102。在另一个实例中,封装电子器件100中包括多于两个的半导体裸片。

在一个实例中,封装电子器件100由起始引线框架结构构成,并且具有裸片附接焊盘104和称为引线的一或多个最终分离的引线结构。在一个实例中,封装电子器件100是使用具有裸片附接焊盘104和一或多根引线的主引线框架结构以及以下参考图11和12所示的次引线框架结构构成。图1中的封装电子器件100包括最初包括在主引线框架结构中的裸片附接焊盘104的引线106,以及最初为次引线框架结构的一部分的次引线108。封装电子器件100包括连接(例如焊接)至引线108的导电柱109。

在一个实例中,裸片附接焊盘104、引线106和108以及导电柱109是导电金属,如铜。在另一个实例中,结构104、106、108和/或109可以是不同的导电金属,如铝。在一个实例中,起始主引线框架包括随后在模制之前分离的所示裸片附接焊盘104和引线106,第二引线框架结构包括引线108。在另一个实例中,导电结构104、106和108是设置在如胶带之类的载体上的单独结构,随后进行裸片附接处理和其它制造过程以创造封装电子器件100。

封装电子器件100包括具有隔离层112(如陶瓷层)的多层衬底110,所述隔离层延伸于下金属层和上金属层之间并将其分隔开。隔离层112是电绝缘体。隔离层112包括上部第一侧113。下金属层包括连接至隔离层112的下部第二侧115的第一导电部114,以及连接至第二侧115的第二导电部116。在图1至3的实例中,第一部分114与第二部分116电隔离。

示例性衬底110还包括沿隔离层112的上部第一侧113的一部分延伸的上部金属层118(在本文中有时称为第一金属层)。隔离层112不包括导电通孔,并且将第一和第二金属层彼此电隔离,使得上部第一金属层118与下部金属层114、116(在本文中有时称为第二金属层)电隔离。在一个实例中,第一和第二金属层包括铜。在其它实施方式中,可以使用不同的导电金属,如铝,或者可以使用导电金属材料的组合。

在一个实例中,第一金属层118和图案化的第二金属层114、116是使用一或多种合适的金属化材料和工艺在起始隔离层衬底112(例如,陶瓷材料)上形成的,所述金属化材料和工艺如直接敷铜法(DBC)、活性金属钎焊(AMB)、绝缘金属衬底(IMS)加工、直接敷铝法(DBA)等。下部金属层114和116的金属衬底特征可以根据裸片布置通过蚀刻、电镀或印刷技术进行图案化。导电金属层114、116和118可以是或包括任何适合的导电材料,如Cu、Ni、Pd、Ag、Au。在一个实例中,隔离层112的厚度(例如,沿图1中的Z方向)为100μm或更多以及约300μm或更少,第一金属层118的厚度为50μm或更多以及100μm或更少,第二金属层114、116的厚度为50μm或更多以及100μm或更少。

封装电子器件100还包括封装结构120,其包围第一半导体裸片101和第二半导体裸片102的侧面。此外,封装结构120包围裸片附接焊盘104的一部分、引线106和108的一部分以及衬底110的一部分。在一个实例中,封装结构120是模制材料,如塑料。在另一个实例中,可以使用陶瓷封装材料。封装结构120暴露引线106和108的底部以及裸片附接焊盘104的底部,例如以将这些特征焊接至主印刷电路板(PCB,未示出)。此外,在所示实例中,引线106、108的侧部是暴露的,这一点并非在所有可能实施方式中有严格要求。如图2和3另外示出,示例性封装电子器件100是在四侧具有器件引线的QFN型封装。

再次参考图1,第一半导体裸片101包括在第一半导体裸片101的上侧124或沿所述上侧的第一触点121和第二触点122。触点121和122是导电特征,如沿半导体裸片101的一侧124的外表面暴露的铜或铝裸片焊盘。在一个实例中,触点121和122为焊料125或包括所述焊料,如焊料凸块,以便于制备期间的焊接操作。第一半导体裸片101的第二触点122沿衬底110的下侧126焊接至第二金属层的第一部分114。在图1所示的横截面中,第一触点121通过焊线127焊接至第一引线106。在一个实例中,封装电子器件100的其它引线(未示出)焊接至相应的第一和/或第二半导体裸片101、102的触点。该实例中的第一半导体裸片101包括在第一半导体裸片101的下侧129上的导电触点128。第一半导体裸片101的下侧129在本文中有时被称为第一侧,并且第一半导体裸片101的上侧124在本文中有时被称为第一半导体裸片101的第二侧。例如,通过将导电触点128焊接至裸片附接焊盘104的上部第一侧130,使得第一侧129连接至裸片附接焊盘104的第一侧130。

第二半导体裸片102包括在上侧134或沿所述上侧延伸的第一触点131和第二触点132。第二半导体裸片102还包括连接(例如,通过焊接)至裸片附接焊盘104的第一侧130的触点138。触点138在第二半导体裸片102的下侧139上或沿所述下侧延伸。第二半导体裸片102的下侧139在本文中有时被称为第一侧,第二半导体裸片102的上侧134在本文中有时被称为第二半导体裸片102的第二侧。在图1至3的实例中,第二金属层的第一部分114焊接至第一半导体裸片101的触点122,第一部分114还焊接至第二半导体裸片102的触点131。此外,第二金属层的第二部分116焊接至第二半导体裸片102的触点132。

多层衬底110具有由第一金属层118的暴露部分形成的上部第一侧140。完整的封装电子器件100具有上部第一侧141和下部第二侧142。如图1和2所示,衬底110的第一侧140的暴露部分为半导体裸片101和/或102中的一者或两者中或由其产生的热量提供上部排热路径。如图1和3所示,裸片附接焊盘104的下部第二侧144沿封装电子器件100的第二侧142暴露,从而为半导体裸片101和/或102中的一者或两者中或由其产生的热量提供第二(下部)排热路径。衬底110的下侧126在本文中有时被称为衬底110的第二侧。在图1至3的实例中,裸片附接焊盘104的第一侧130焊接至第一半导体裸片101的触点128和第二半导体裸片102的触点138。

如图1所示,第一金属层118形成于示例性隔离层112的第一侧113,第二金属层114、116形成于隔离层112的第二侧115。在一个实例中,第二金属层114、116是图案化的金属(如铜)层,第一和第二部分114和116的特征是被设计为与第一和第二半导体裸片101、102的特定触点互连。在所示实例中,第二部分116也连接(例如,焊接)至导电柱109,以将第二半导体裸片102的触点132电连接至引线108。

如下文中结合图4至15进一步描述的,裸片101和102以及衬底110可以单独制造并与引线框架一同引入封装工艺,以制成具有顶侧互连和由第一金属层118形成的顶侧暴露焊盘的封装电子器件100。通过相应的第一和第二半导体裸片101和102的上部第二侧124和134,衬底110提供良好的散热路径,作为顶侧冷却路径。此外,暴露的第一金属层118与第二金属层114、116电隔离。这种电隔离提供了隔离散热焊盘,所述隔离散热焊盘有助于将外部散热器(未示出)连接(例如,胶合)至第一金属层118的第一侧140,从而在散热器和第一金属层118之间无需电隔离热界面材料(TIM)。在一个实例中,衬底110焊接或以其它方式附接至第一和第二半导体裸片101和102的相应第二侧124、134以制作电接触和热接触两者。相应的第一和第二半导体裸片101、102的下部第一侧29和139连接(例如,焊接)至下方的导电裸片附接焊盘104,从而与其制作电接触和热接触两者。

如下所述,通过引线接合一或多个触点(例如,触点121),以用于其余的I/O引脚或其它所需的与主机PCB和/或裸片之间的电连接。示例性器件100包括在四个侧外部可使用的引线,这一点并非在所有可能实施方式中有严格要求。在一个实例中,封装电子器件100模制成QFN封装形状,如图1至3所示。在其它实例中,可以提供其它完成的封装形状,其具有底部和顶侧散热路径,从而便于将热排至下方的主机PCB以及顶侧环境或附接的散热器。在一种实施方式中,封装电子器件100的第二半导体裸片102包括高电压晶体管(例如,氮化镓(GaN)FET),其漏极端子连接至触点132(例如,在图1中标记为“D”),其源极端子连接至触点131(例如,在图1中标记为“S”)。

第二金属层的第一部分114将晶体管源极端子电连接至第一半导体裸片101的触点122。在本实例中,第一半导体裸片101包括栅极驱动器电路以控制第二半导体裸片102的晶体管操作。第一半导体裸片101为第二侧124上的触点122与下部第一侧129上的触点128之间提供电连接。此外,第二半导体裸片102为上部第二侧134上的触点131与下部第一侧139上的触点138之间提供电连接。在本实例中,裸片附接焊盘104电连接至晶体管源极端子,并且裸片附接焊盘104的下部第二侧144可以焊接至主机PCB(未示出)的接地或其它参考电压连接。除了电源连接之外,裸片附接焊盘104还用作导热散热焊盘,以使热量从半导体裸片101和102的各自下部第一侧129和139去除并进入下方的主机PCB结构。此外,在本实例中,衬底110的第二金属层的第二部分116提供从晶体管漏极端子(例如,第二半导体裸片102的触点132)通过导电柱109至引线108的电连接。这种电连接使得通过将引线108焊接至对应的PCB焊盘(未示出)而将晶体管漏极端子连接至主机PCB。

在一种应用中,晶体管漏极端子可以相对于接地或源极端子的其它参考电压连接至高电压信号。第一金属层118沿封装结构120的第一侧141暴露。隔离层112在第一金属层118与第二金属层114、116之间延伸并将其分隔开以提供电隔离。衬底110的第一和第二金属层的电隔离有利于防止向第一金属层118施加高电压,并且导电散热器结构可以焊接或以其它方式附接至衬底110的上部第一侧140而无需电隔离热界面材料。在本实例中,第二金属层114、116焊接至第一半导体裸片101的触点122和第二半导体裸片102的触点131和132。以此方式,示例性衬底110促进热传递,使热量通过衬底110,并(图1)向上到达封装电子器件100的环境或任何附接的散热器(未示出),从而从相应的第一和第二半导体裸片101和102的上部第二侧124和134去除。图1至3的实例中的封装结构120包围第一半导体裸片101和第二半导体裸片102,以及裸片附接焊盘104、衬底110的一部分和器件引线106、108的一部分。

现在参考图4至17,图4示出了一种用于制作封装电子器件的方法400,图5至15示出了根据方法400进行制备处理的示例性封装电子器件100。在图4的实例中,在401处提供下侧具有图案化金属且上侧具有隔离金属的陶瓷衬底。图5至7示出了如上文结合图1所示的衬底110的实例,所述衬底在图4的401处提供。在一个实例中,衬底110是单独制造的,例如,由陶瓷或其它隔离衬底112制成。在一个实施方式中,在401处使用DBC、AMB、IMS和DBA处理中的一或多种在隔离层112上形成第一金属层118和图案化的第二金属层114、116。在一个实例中,在如图4所示的工艺400中,衬底110提供为输入组件。在另一个可能的实施方式中,方法400包括衬底110的制备。图6示出了衬底110的示例性顶部透视图,其中沿衬底110的上侧140,在隔离层112的上部第一侧113上形成大体均匀的第一金属层118。图5示出了沿图6和7的线5-5截取的衬底110的截面侧视图。在本实例中,图7示出了沿衬底110的下部第二侧126,在隔离层112的下部第二侧115上形成的第二金属层的第一部分114和第二部分116的示例性图案化铜构造。

方法400在图4的402处继续,其中施加焊料以选择裸片附接焊盘和任何所包括的次引线的上侧的一部分。图8示出了一个实例,其中执行焊料沉积工艺800,以将焊料802施加到裸片附接焊盘104的上部第一侧130和次引线108的顶侧的特定部分。在一个实例中,通过丝网印刷工艺800在402处使用焊接掩模(未示出)施加焊料。在另一个实例中,通过印刷工艺800在402处施加焊料。

另外在404处,方法400继续,其中将第一和第二半导体裸片放置在裸片附接焊盘上。图9示出了一个实例,其中执行裸片附接工艺900,以将相应的第一和第二半导体裸片101和102的下部第一侧129和139附接至裸片附接焊盘104的上部第一侧130。在一个实例中,裸片附接工艺900包括操作自动拾取和放置机器(未示出),以将半导体裸片101和102定位在裸片附接焊盘的第一侧130的预定位置处,如图10进一步所示。在图4的405处,方法400还包括将一或多个导电柱(例如,铜)放置在次引线上。图10示出了一个实例,其中执行导电柱放置工艺1000,以将导电柱109放置在次引线108上侧的预定位置处。可以使用任何合适的放置工艺1000,如使用合适的机器(未示出)的自动拾取和放置工艺。如下文结合图16所述,在另一个实施方式中,可以从方法400中省略405处的铜柱放置。

方法400在图4的406处继续,其中通过回流焊料将半导体裸片触点焊接至裸片附接焊盘并将任何所包括的导电柱焊接至次引线的上部。图11和12示出了一个实例,其中在图11中执行热回流工艺1100,通过回流预先放置的焊料以便将相应第一和第二裸片101和102的下侧129和139上的触点焊接至裸片附接焊盘104的第一侧130,并将一或多个铜柱109焊接至次引线108的上部,如图12所示。在一个实例中,多个铜柱109焊接至具有多个相关次引线108的次引线框架部分,如图8所示。

方法400在图4的408和410处继续,其中将衬底110附接至半导体裸片和任何所包括的导电柱。在408处,方法400包括将陶瓷衬底的下侧放置在第一和第二半导体裸片以及任何所包括的导电柱的上侧。图13示出了一个实例,其中执行放置工艺1300以将衬底110的第二侧126的第二金属层114、116放置到第一半导体裸片101的第二侧124和第二半导体裸片102的第二侧134。在一个实例中,导电柱109的顶侧提供有焊料125,并且第一和第二半导体裸片101和102包括焊料凸块125,其形成在相应的上部第二侧124和134的相应触点121、122、131和132上,如图13所示。在另一个实例中,在衬底放置之前执行丝网印刷、印刷或其它焊料施加处理以施加焊料125,如图13所示。在本实例中,放置工艺1300还将第二部分116的下侧126的一部分放置到导电柱109的顶表面上,如图14所示。

再次参考图14和15,方法400在图4的410处继续,其中回流焊料以将衬底的第二金属层与半导体裸片和导电柱联合。图14示出了一个实例,其中执行热回流工艺1400,通过回流焊料125以将第二金属层的下部第二侧126联合至相应半导体裸片101和102的触点122、131和132。工艺1400还将第二金属层的第二部分116焊接至导电柱109的顶侧,从而形成如图5所示的部分完成器件100。

方法400在图4的412处继续,其中进行引线接合。图16示出了一个实例,其中执行引线接合工艺1600,以将一或多个接合线127附接至预先指定的触点和/或引线之间。图16的示例性截面图示出了一个示例性接合线127,其第一端焊接至第一半导体裸片101的触点121,其第二和焊接至引线106。在一个示例中,引线接合工艺1600在裸片101和102的触点之间、裸片中的一个和引线之间、或其组合之间创造多个接合线连接。在上述的一个实例中,第一半导体裸片101包括驱动电路,其具有焊接至封装电子器件100的相应引线的多个触点,以将驱动电路与外部主机电路(未示出)接口连接,并且某些实施方式可包括多于两个的半导体裸片,其具有相应的接合线连接(未示出),以连接至任何包括的附加半导体裸片的关联触点,或连接至所述关联触点之间。

方法400在图4的414处继续,其中进行模制以形成封装结构。图17示出了一个实例,其中执行模制工艺1700以形成包围第一半导体裸片101和第二半导体裸片102的示例性模制封装结构120。在一个实例中,封装结构120包括:第一侧141,其暴露衬底110的第一侧140的第一金属层118;以及下部第二侧142,其暴露裸片附接焊盘104的第二侧144。如上所述,图1和17中所得的封装电子器件100提供顶侧和底侧冷却路径,以便于各种不同半导体电路类型(包括半导体裸片101和102中一者或两者的转换电源和相关功率晶体管)的功率密度和能量效率的提高。

图18示出了另一个示例性封装电子器件1800的截面侧视图,其包括如上文结合图1的器件100所述的特征。与封装电子器件100不同,图18的封装电子器件1800不包括上述引线108或导电柱109。相反,器件1800的漏极连接由成形的夹引线1708形成,其延伸至封装电子器件1800的底侧142,并且包括有角度的一部分,所述一部分直接焊接至衬底110的第二金属层的第二部分116。示例性封装电子器件1800可以使用上文图4的示例性方法400来制备,其中省略405处铜柱的放置。

示例性封装电子器件100和1800,以及示例性方法400提供了便于封装器件单向封装冷却(例如,顶侧和底侧冷却)的解决方案,所述封装器件包括横向FET或其它半导体裸片,所述半导体裸片在裸片顶侧具有多节点的触点或焊盘布置。所述概念采用便于紧凑双侧冷却的隔离衬底结构110,并且所示技术可以结合用于裸片附接的标准引线框架和用于顶侧互连的绝缘衬底使用。所示实例示出了具有最终标准QFN封装形式的封装电子器件100、1800的实施方式。通过双侧冷却改进热管理有助于降低晶体管结温,可以提高器件可靠性,并有助于增加功率密度。双侧冷却技术将晶体管的热阻网络分成两个并联路径,并且结到环境热阻(即,R

上述实例仅是对说明书的各个方面的几种可能的实施方式的说明,其中本领域的其他技术人员在阅读和理解本说明书和附图后将得出等效的改变和/或修改。在权利要求的范围内,可以对所述实例进行修改,并且其它实施方式也是可能的。

- 双侧冷却的电子器件

- 具有多侧感应器冷却的功率电子器件组件