CUP通孔重叠修正方法

文献发布时间:2023-06-19 11:49:09

技术领域

本发明涉及半导体集成电路设计领域,特别是指一种CUP通孔重叠修正方法。

背景技术

集成电路(芯片)在封装时会使用金属焊线连接焊垫(电路中的输入输出端口)到外部的封装结构的引脚上。在一定的工艺条件下,输入输出端口的物理版图设计直接影响到封装的成品率和可靠性。由于CUP(CIRCUIT UNDER PAD,焊垫下电路器件)类型的输入输出端口的芯片在焊垫区下面有电路器件存在,一些金属层次被用来连接器件,使得用作CUP焊垫区的金属比非CUP 焊垫区的少几层金属,同时在连接焊线和探针这些用作CUP 焊垫区的金属也起着保护下面电路的作用。因此,在CUP 类型的设计中,焊垫区的结构设计既要满足普通焊垫的功能,又要保护使下面的电路不受损害,而且下面的电路又给焊垫区的可靠性和稳定性有一定的影响,其设计更加复杂。

在CUP 焊垫区的窗口及周围区域,至少有顶层金属、顶层通孔和次一层金属。顶层金属和次一层金属通过顶层通孔连接起来构成基本的完全连接的贯通焊垫区的金属结构。

由于CUP结构在焊垫下有电路器件(作为输入输出结构)存在,所以封装时很可能造成外部应力通过焊垫传导到下面的电路,破坏了这个输入输出接口电路,因此造成整个芯片失效。

对于CUP区域应力传导很重要的原因就是相邻的通孔层重叠,如图1所示,即上下层通孔在垂直投影面重叠。通孔区域对于应力的传导比周围介质层要强很多。在大多数CUP结构物理版图中,通孔区域又是不能缺少的。在工艺要求的CUP设计规则中,相邻两层的通孔是不能重叠的,那就需要有一个好的方法去调整不同层通孔的放置使其不会重叠,即将两层通孔的位置错开放置,如图2所示。

发明内容

本发明所要解决的技术问题是提供一种CUP通孔重叠修正方法,使上下层的通孔的排布不重叠。

为解决上述问题,本发明实现了一种在CUP区域物理版图中相邻层通孔重叠的修正方法。这种方法不同于传统的仅靠手动调整的方法,而是在满足设计规则情况下选择最优化的排布方式,实现了自动化修正,从而解决了一些CUP区域版图修改问题。

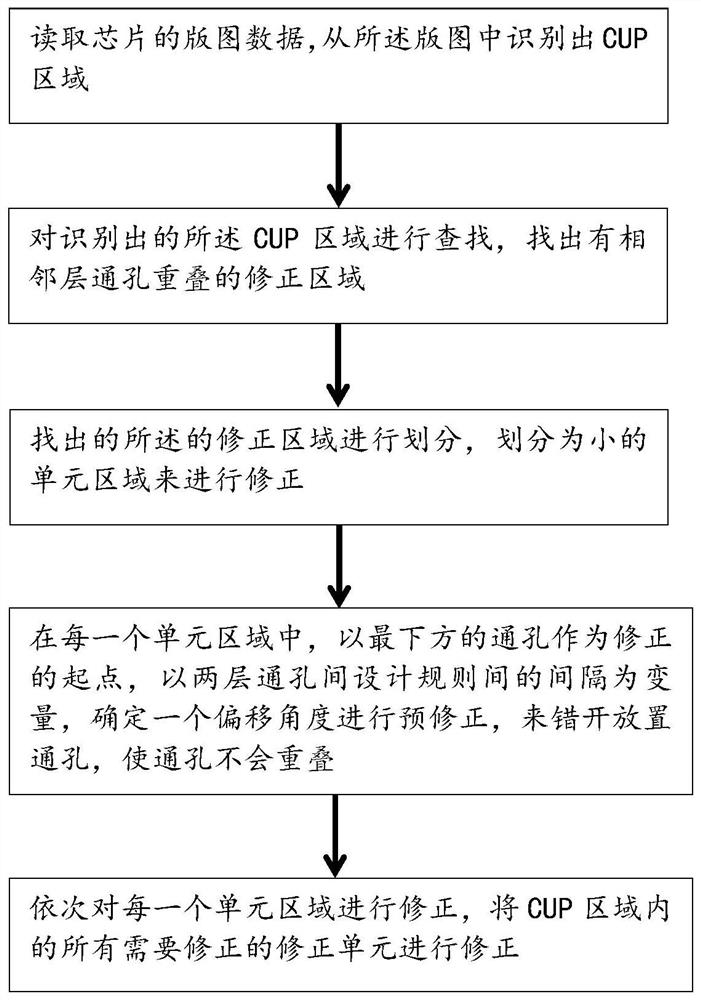

本发明所述的CUP通孔重叠修正方法,包含如下的处理步骤:

步骤一,读取芯片的版图数据,从所述版图中识别出CUP区域;

步骤二,对识别出的所述CUP区域进行查找,找出有相邻层通孔重叠的修正区域;

步骤三,将所述步骤二中找出的所述的修正区域进行划分,划分为小的单元区域来进行修正;

步骤四,在每一个单元区域中,以最下方的通孔作为修正的起点,以两层通孔间设计规则间的间隔为变量,来错开放置通孔,使通孔不会重叠;

步骤五,依次对每一个单元区域进行修正,将CUP区域内的所有需要修正的单元区域进行修正。

进一步地改进是,所述的CUP区域是芯片内为引出封装时的引线而制作的焊垫区,所述焊垫区包含有连接电路的通孔,在通孔下方包含有电路。

进一步地改进是,所述的在修正单元范围内,确定一个角度为一个偏置量,逐步修正添加通孔;各个角度的偏移量通过不同层间通孔的偏移量来实现。

进一步地改进是,所述的角度是以实际情况来确定的,以实现添加的通孔数量达到最大化。

进一步地改进是,所述的角度包含0 °、45 °、90 °、135 °、180 °;比较哪种角度允许添加的通孔最多,就选择该角度。这个只是假定值,实际可以根据情况调整这个值。

进一步地改进是,所述步骤四中,在修正时,以两层通孔间设计规则间的间隔为变量,所述间隔是选择通孔间设计规则中最大的间隔来作为变量。

进一步地改进是,通过尽可能多的通孔数量来降低层间连接电阻,提高通孔的电流能力。

本发明通过对CUP区域具有相邻层重叠通孔的区域提取出来并划分为小的修正单元来进行处理,以最下方的通孔为修正起点,以相邻两层通孔间设计规则间隔较大的值为变量,错开放置通孔,消除通孔重叠的状态,实现自动化的最优化通孔排布,改善了CUP区域的封装时的应力问题。

附图说明

图1 是CUP区域的相邻层具有重叠通孔的剖面示意图。

图2 是CUP区域的相邻层通孔错开放置不重叠的剖面示意图。

图3 是CUP区域的相邻层通孔重叠且具有45°偏移角的示意图。

图4 是CUP区域的相邻层通孔具有45°偏移角的示意图。

图5 是CUP区域的相邻层通孔重叠且具有0°偏移角的示意图。

图6 是某一芯片版图识别出CUP区域的示意图。

图7 是对识别出的CUP区域提取出具有相邻层重叠通孔的示意图。

图8 是对图7所示的进一步划分为小的修正单元的示意图。

图9 是某一修正单元内对重叠区域重新排列的示意图。

图10 是某一修正单元内以最左下角的通孔为参考点,偏移角度为0°时的修正示意图。

图11 是某一修正单元内以最左下角的通孔为参考点,偏移角度为45°时的修正示意图。

图12 是某一修正单元内以最左下角的通孔为参考点,偏移角度为90°时的修正示意图。

图13 是本发明方法步骤示意图。

具体实施方式

下面将结合附图,对本发明中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在不做出创造性劳动的前提下所获得的所有其它实施例,都属于本发明保护的范围。

本发明所述的一种CUP通孔重叠修正方法, 包含如下的步骤:

步骤一,读取芯片的版图数据,从所述版图中识别出CUP区域。

步骤二,对识别出的所述CUP区域进行查找,找出有相邻层通孔重叠的修正区域。

步骤三,将所述步骤二中找出的所述的修正区域进行划分,划分为小的单元区域来进行修正。

步骤四,在每一个单元区域中,以最下方的通孔作为修正的起点,以两层通孔间设计规则间的间隔为变量,来错开放置通孔,使通孔不会重叠。

在修正单元区域中(0-180°)范围内,以每45°(这个只是假定值,实际可以根据情况调整这个值)为一个偏置量,往上来修正添加通孔。以0 °、45 °、90 °、135 °、180 °常见的角度来说,如图3、图4、图5所示。以这五种情况修正的通孔排布,比较哪种角度情况下允许添加通孔是最多的,就选择那种方案修正。一般情况下,认为连接通孔越多,电阻越小,电流能力越强。

各个角度的偏移量通过不同层间通孔的偏移量来实现,如45 °对于在不同层都为0.4*0.4um的通孔,可以将下层通孔相对于上层通孔,向右上移动0.4um实现,其他情况类似。

步骤五,依次对每一个单元区域进行修正,将CUP区域内的所有需要修正的单元区域进行修正。

在某一实施例中,如图6所示,是读取一幅芯片的版图并从芯片的版图中识别出的CUP区域,该区域包含大量的通孔(图中的小方格),分布在版图中的不同区域。实际上这些通孔分布在版图中不同的层次,在某些地方形成了重叠,由于透视效果以及黑白图片显示的问题,有些地方可能不能清晰地展现,在此特别说明。所识别出的CUP区域包含的通孔中,有存在上下层重叠的通孔,也有不重叠彼此错开的通孔,需要对它们进行区分。

如图7所示,对识别的CUP区域继续进行查找,区分出该区域中有相邻层通孔重叠的区域。再将这些有相邻层通孔重叠的区域进行进一步地划分,分成一个个小的修正单元来进行处理。如图8所示。

假设某一个修正单元中需要修正的通孔为VIA1和VIA2,通孔的尺寸都是0.2*0.2um,通孔间的间距为0.23um,重叠区域为1.1*1.35um。

在重叠区域内,以VIA1的3X3阵列为基础,将重叠的VIA2通孔重新排列。由于通孔间间距都为0.23um(即最大间距也是0.23um),通孔尺寸为0.2um。同层通孔的间隔尺寸(最大VIA尺寸 +最大VIA间距) 为0.43 um,如图9所示。

以下方最靠左通孔VIA1为参考点,偏移量角度为0°,添加不重叠的VIA2通孔。即只有X轴偏移+0.2um,VIA2在重叠区域内尺寸为0.43um添加,如图10所示。

同样,以左下角VIA1孔为参考点,偏移量角度为45°时,添加不重叠的VIA2通孔。即X轴偏移+0.2um,Y轴偏移+0.2um,VIA2在重叠区域内尺寸为0.43um添加,如图11所示。

以左下角VIA1孔为参考点,当偏移量角度为90°时,添加不重叠的VIA2通孔, 即Y轴偏移+0.2um VIA2在重叠区域内尺寸为0.43um添加,如图12所示。

以左下角VIA1孔为参考点,当偏移量角度为135°或180 °时,添加不重叠的VIA2通孔, 即X轴偏移为-0.2um。由于这些添加区域在重叠区域以外,所以无法添加VIA2。

通过比较这五种偏移量修正情况(0 °、45 °、90 °、135 °、180 ° ),发现在90 °情况下,修正后VIA1和VIA2不重叠并且通孔数量最多,即选取该方案进行修正。

在整个CUP区域范围,对所有修正单元内的重叠的通孔采用上述的修正方案即90°的方案进行修正,完成整个CUP区域的通孔修正,这样整个CUP区域的相邻层通孔都消除了重叠的情况,并且通孔的数量达到了最大化,能降低整个通孔连接的电阻,提高电流能力。

以上仅为本发明的优选实施例,并不用于限定本发明。对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- CUP通孔重叠修正方法

- 一种基于相邻片间重叠像元数偏差统计的偏流角修正方法