用于具有多区段使能信号电压域的行解码器的设备和方法

文献发布时间:2024-04-18 19:44:28

技术领域

本公开大体上涉及半导体装置,且更具体地说,涉及半导体存储器装置。

背景技术

具体地说,本公开涉及易失性存储器,例如动态随机存取存储器(DRAM)。存储器可具有数个存储器单元,其中的每一个存储信息位(例如,作为物理信号,如电容性电荷)。存储器单元可组织成阵列,其中每一存储器单元在行(例如,字线)与列(例如,位线)的相交点处。行地址和列地址可用于指定一或多个存储器单元。行解码器接收行地址且激活行(例如,通过将电压提供到与行地址相关联的字线)。随着存储器装置的大小减小,可能需要减小诸如行解码器之类的组件的大小。

发明内容

本公开的一方面涉及一种设备,其包括:区段使能信号驱动器,其经配置以接收预区段使能信号,且在第一电压域中提供第一区段使能信号且在第二电压域中提供第二区段使能信号;区段使能电路,其经配置以在所述第一电压域中提供具有基于所述第一区段使能信号和所述第二区段使能信号的电平的多字线驱动器信号。

本公开的另一方面涉及一种行解码器,其包括:第一晶体管,其具有耦合到第一信号的第一栅极,其中第一电压表示有效第一信号且接地电压表示无效第一信号,其中所述第一晶体管经配置以响应于所述无效第一信号而将所述第一电压耦合到节点;以及第二晶体管,其具有耦合到第二信号的第二栅极,其中第二电压表示有效第二信号且所述接地电压表示无效第二信号,其中所述第二晶体管经配置以响应于所述有效第二信号而将所述接地电压耦合到所述节点,其中基于所述节点的电压产生字线驱动器信号。

本公开的又一方面涉及一种方法,其包括:将行地址解码为区段预使能信号;基于所述区段预使能信号在第一电压域中产生第一区段使能信号;基于所述区段预使能信号在第二电压域中产生第二区段使能信号;以及基于所述第一区段使能信号和所述第二区段使能信号提供多字线驱动器信号。

附图说明

图1为根据本公开的实施例的半导体装置的框图。

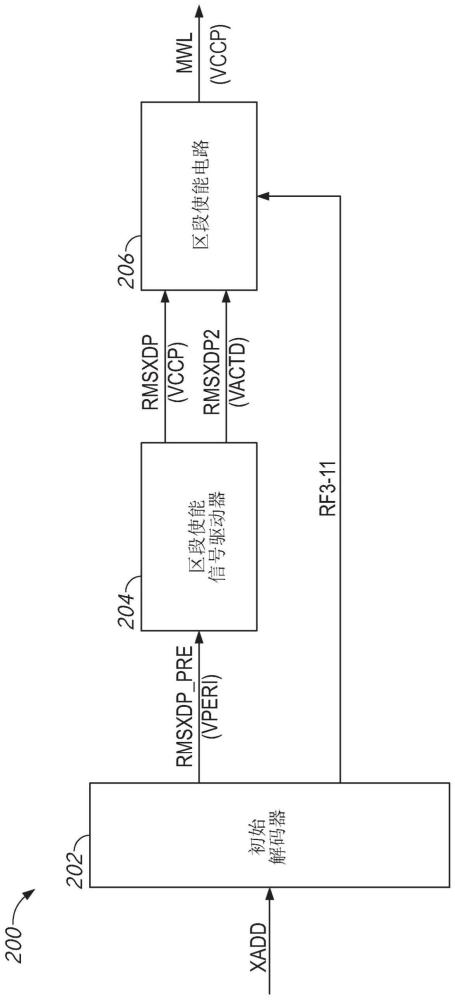

图2为根据本公开的一些实施例的行解码器的一部分的框图。

图3为根据本公开的一些实施例的区段使能电路的示意图。

图4为根据本公开的一些实施例的区段使能信号驱动器的示意图。

图5为根据本公开的一些实施例的方法的流程图。

具体实施方式

某些实施例的以下描述在本质上仅为示例性的,并且绝不意图限制本公开的范围或其应用或用途。在对本发明的系统和方法的实施例的以下详细描述中,参考形成本文的一部分的附图,且借助于说明方式展示其中可实践所描述的系统和方法的特定实施例。足够详细地描述这些实施例,以使所属领域的技术人员能够实践本发明所公开的系统和方法,且应理解,可利用其它实施例,且在不脱离本公开的精神和范围的情况下可进行结构和逻辑改变。此外,为了清晰起见,当所属领域的技术人员清楚某些特征时将不再论述其详细描述,以免混淆本公开的实施例的描述。因此,以下详细描述不应以限制性的意义来理解,且本公开的范围仅由所附权利要求书来限定。

行解码器可在不同电压域中操作。如本文所使用,不同电压域可指给定信号在其下操作的电压范围。由于存储器中的信号可通常为二进制的,因此在第一电压域中操作的信号指示第一电压指示逻辑高的信号,而在第二电压域中操作的信号使用第二电压来指示逻辑高。在一些实施例中,不同电压域可使用共同电压来表示逻辑低(例如,接地电压)。

行解码器可能需要转换不同电压域之间的信号。举例来说,存储器阵列可在VCCP电压域中操作,而由行解码器接收到的信号可在VPERI电压域中操作,其中VPERI为比VCCP低的电压。行解码器可接收行地址且对所述行地址的不同区段进行解码以激活控制信号。举例来说,行地址可为多位信号,且一组位可指定一组特定区段中的一者,而另一组位可指定所述区段内的字线。行地址中指定区段的部分可被称为区段地址。区段地址可解码为VPERI域中的预区段使能信号,其可用于产生VCCP域中的区段使能信号。区段使能电路可使用区段使能信号来激活字线驱动器信号MWL。区段使能电路可使用电压VACTD(其在VCCP与VPERI之间)和缓冲晶体管以在VCCP域与VPERI域之间耦合。通过移除对额外缓冲晶体管的需要来减小行解码器的大小可为有用的。

本公开涉及用于具有多区段使能信号电压域的行解码器的设备、系统和方法。区段使能信号驱动器接收预区段使能信号,且在第一电压域(例如,VCCP)中提供第一区段使能信号且在第二电压域(例如,VACTD)中提供第二区段使能信号。预区段使能信号可在第三域(例如,VPERI)中。字线驱动器信号提供于第一电压域中,所述信号具有基于第一区段使能信号和第二区段使能信号的电平。由于区段使能信号被划分成两个,其中的一者在中间电压域中,因此在接收区段使能信号的晶体管与耦合到不同电压域中的信号的晶体管之间可能不需要额外的缓冲晶体管。这可帮助减小行解码器的大小。

举例来说,第一区段使能信号可耦合到第一晶体管的栅极,且第二区段使能信号可耦合到第二晶体管。第一晶体管可为p型晶体管,其在第一区段使能信号为逻辑低时将电压VCCP耦合到信号线,且第二晶体管可为n型晶体管,其在第二区段使能信号为逻辑高时且在第二晶体管由经解码行地址信号激活时将接地电压耦合到信号线。可反转沿着信号线的电压以提供多字线驱动器信号。

图1为根据本公开的实施例的半导体装置的框图。半导体装置100可为半导体存储器装置,例如集成在单个半导体芯片上的DRAM装置。

半导体装置100包含存储器阵列118。存储器阵列118展示为包含多个存储器组。在图1的实施例中,存储器阵列118展示为包含八个存储器组BANK0到BANK7。在其它实施例的存储器阵列118中可能包含更多或更少的组。每一存储器组包含多个字线WL、多个位线BL和/BL以及布置在所述多个字线WL与所述多个位线BL和/BL的相交点处的多个存储器单元MC。字线WL的选择由行解码器108执行,并且位线BL和/BL的选择由列解码器110执行。在图1的实施例中,行解码器108包含用于每一存储器组的相应行解码器,且列解码器110包含用于每一存储器组的相应列解码器。位线BL和/BL耦合到相应感测放大器(SAMP)。来自位线BL或/BL的读取数据由感测放大器SAMP放大,且经由互补本地数据线(LIOT/B)、传送门(TG)和互补主数据线(MIOT/B)传送到读取/写入放大器120。相反地,从读取/写入放大器120输出的写入数据经由互补主数据线MIOT/B、传送门TG以及互补本地数据线LIOT/B传送到感测放大器SAMP,且写入在耦合到位线BL或/BL的存储器单元MC中。

半导体装置100可采用多个外部端子,其包含:耦合到命令和地址总线以接收命令和地址以及CS信号的命令和地址(C/A)端子;用于接收时钟CK和/CK的时钟端子;用于提供数据的数据端子DQ;以及用于接收电源电势VDD、VSS、VDDQ和VSSQ的电源端子。

时钟端子供应有提供到输入电路112的外部时钟CK和/CK。外部时钟可为互补的。输入电路112基于CK和/CK时钟产生内部时钟ICLK。将ICLK时钟提供到命令解码器106且提供到内部时钟产生器114。内部时钟产生器114基于ICLK时钟提供各种内部时钟LCLK。LCLK时钟可用于各种内部电路的定时操作。将内部数据时钟LCLK提供到输入/输出电路122,以对包含于输入/输出电路122中的电路的操作进行定时,例如提供到数据接收器以对写入数据的接收进行定时。

C/A端子可供应有存储器地址。经由命令/地址输入电路102将供应给C/A端子的存储器地址传送到地址解码器104。地址解码器104接收地址,且将经解码行地址XADD供应到行解码器108并将经解码列地址YADD供应到列解码器110。地址解码器104还可供应经解码组地址BADD,其可指示含有经解码行地址XADD和列地址YADD的存储器阵列118的组。C/A端子可供应有命令。命令的实例包含用于控制各种操作的定时的定时命令、用于存取存储器的存取命令,例如用于执行读取操作的读取命令和用于执行写入操作的写入命令,以及其它命令和操作。存取命令可与用以指示待存取的存储器单元的一或多个行地址XADD、列地址YADD和组地址BADD相关联。

命令可作为内部命令信号经由命令/地址输入电路102提供到命令解码器106。命令解码器106包含对内部命令信号进行解码以产生各种内部信号的电路和用于执行操作的命令。举例来说,命令解码器106可提供用以选择字线的行命令信号和用以选择位线的列命令信号。

装置100可接收作为读取命令的存取命令。当接收到读取命令且随读取命令及时供应组地址、行地址和列地址时,从存储器阵列118中对应于行地址和列地址的存储器单元读取读取数据。读取命令由命令解码器106接收,所述命令解码器提供内部命令,使得来自存储器阵列118的读取数据被提供到读取/写入放大器120。读取数据经由输入/输出电路122从数据端子DQ输出到外部。

装置100可接收作为写入命令的存取命令。当接收到写入命令且随写入命令及时供应组地址、行地址和列地址时,将供应到数据端子DQ的写入数据写入到存储器阵列118中对应于行地址和列地址的存储器单元。写入命令由命令解码器106接收,所述命令解码器提供内部命令以使得写入数据由输入/输出电路122中的数据接收器接收。还可将写入时钟提供到外部时钟端子,以对通过输入/输出电路122的数据接收器对写入数据的接收进行定时。写入数据经由输入/输出电路122供应到读取/写入放大器120,并且通过读取/写入放大器120供应到存储器阵列118以供写入到存储器单元MC中。

作为刷新模式的一部分,装置100还可接收使其实行一或多个刷新操作的命令。在一些实施例中,刷新模式命令可在外部发布到存储器装置100。在一些实施例中,刷新模式命令可以通过装置的组件周期性地产生。在一些实施例中,当外部信号指示刷新进入命令时,还可激活刷新信号AREF。刷新信号AREF可用于在刷新模式期间控制刷新操作的定时。信号AREF可以在刷新模式期间以周期性定时产生。因此,刷新操作可自动地继续。刷新模式退出命令(其可来自外部控制器和/或可在内部产生)可使得刷新信号AREF的周期性激活停止,并且可使得装置100返回到空闲状态和/或恢复其它操作。

刷新信号AREF被供应到刷新控制电路116。刷新控制电路116将刷新行地址RXADD供应到行解码器108,所述行解码器可刷新由刷新行地址RXADD指示的一或多个字线WL。在一些实施例中,刷新地址RXADD可表示单个字线。在一些实施例中,刷新地址RXADD可以表示多个字线,其可以由行解码器108顺序地或同时地刷新。刷新控制电路116可控制刷新操作的定时,且可产生和提供刷新地址RXADD。可控制刷新控制电路116以改变刷新地址RXADD的细节(例如,如何计算刷新地址、刷新地址的定时、由地址表示的字线的数目),或可基于内部逻辑进行操作。

电源端子供应有电源电势VDD和VSS。将电源电势VDD和VSS供应到内部电压产生器电路124。内部电压产生器电路124基于供应到电源端子的电源电势VDD和VSS产生诸如VCCP、VPERI、VACTD之类的各种内部电势和其它内部电压。不同电压电势可在存储器的不同区域中有用。举例来说,电压VCCP可为比VDD高的电压,且可用于操作存储器阵列118的存储器单元和行解码器108的某些信号。电压VPERI可具有与VDD类似的电压,且可适用于遍及阵列118外部的存储器的信号。电压VACTD可为可用于行解码器108的中间电压(例如,在VCCP与VPERI之间)。不同电压可用于建立不同电压域。举例来说,每一电压可表示对应电压域中的高逻辑电平(例如,VCCP表示VCCP域中的逻辑高等)。电压域可共享表示逻辑低的共同电压,例如VSS。

还向电源端子供应电源电势VDDQ和VSSQ。电源电势VDDQ和VSSQ被供应到输入/输出电路122。在本公开的实施例中,供应到电源端子的电源电势VDDQ和VSSQ可为与供应到电源端子的电源电势VDD和VSS相同的电势。在本公开的另一实施例中,供应到电源端子的电源电势VDDQ和VSSQ可为与供应到电源端子的电源电势VDD和VSS不同的电势。供应到电源端子的电源电势VDDQ和VSSQ用于输入/输出电路122,使得由输入/输出电路122产生的电源噪声不会传播到其它电路块。

图2为根据本公开的一些实施例的行解码器的一部分的框图。在一些实施例中,行解码器部分200可表示图1的行解码器108的一部分。行解码器部分200包含初始解码器202,所述初始解码器接收行地址XADD且提供处于VPERI电压域中的预区段使能信号RMSXDP_PRE。初始解码器202还基于地址XADD(此处标记为RF3-11)提供其它经解码信号(例如,基于原始行地址XADD的位3到11的信号)。行解码器部分200包含区段使能信号驱动器,所述区段使能信号驱动器接收RMSXDP_PRE且提供两个行使能信号RMSXDP(在VCCP电压域中)和RMSXDP2(在VACTD电压域中)。区段使能电路206接收RMSXDP和RMSXDP2且提供多字线驱动器信号MWL。区段使能电路206可由经解码信号RF3-11中的一或多者激活。

行解码器部分200包含一组初始解码器202,其表示行解码器的组件,所述组件在区段使能信号驱动器204的‘上游’。初始解码器202接收行地址XADD,所述行地址XADD可为多位信号。行地址的不同部分(例如,不同组的位)可指示存储器阵列的组织内的分级结构的不同层级。举例来说,XADD<12:15>可表示区段地址且可用于产生区段预使能信号RMSXDP_PRE。类似地,行地址XADD的其它部分可激活其它信号,此处统称为RF3-11。在RF3-11内可存在可激活解码器200的不同层级的若干个别信号(如本文中更详细描述)。举例来说,可存在多个区段使能电路206,且信号RF3-11的组合可激活如由行地址XADD指定的区段使能电路206中的一者。

预区段使能信号RMSXDP_PRE可在VPERI电压域中,其中电压VPERI表示逻辑高(例如,有效信号),且接地电压(例如,VSS)表示逻辑低(例如,无效信号)。虽然仅展示单个RMSXDP_PRE信号,但可存在多个RMSXDP_PRE信号,且初始解码器202可基于行地址XADD的值而选择激活哪一个(或多个)(例如,设置成VPERI)。

区段使能信号驱动器接收信号RMSXDP_PRE且产生区段使能信号RMSXDP和RMSXDP2,其中的每一个在不同电压域中,且在不同于RMSXDP_PRE的电压域中。可存在数个区段使能驱动器204,其各自与不同RMSXDP_PRE信号相关联,此处仅展示单个区段使能信号驱动器204。信号RMSXDP在VCCP域中,其中电压VCCP表示逻辑高且接地电压(例如,VSS)表示逻辑低。信号RMSXDP2在VACTD域中,其中电压VACTD表示逻辑高且接地电压(例如,VSS)表示逻辑低。电压VPERI、VCCP和VACTD可彼此不同。电压VCCP可为用于存储器阵列中的电压,且可高于用于存储器阵列外部的存储器的区中的电压VPERI。电压VACTD可为VCCP与VPERI之间的中间电压。信号RMSXDP和RMSXDP2可具有相同逻辑电平。举例来说,如果信号RMSXDP为有效的(例如,在VCCP下),那么信号RMSXDP2也为有效的(例如,在VACTD下)。类似地,如果信号RMSXDP为无效的(例如,在VSS下),那么信号RMSXDP也为无效的(例如,在VSS下)。

将区段使能信号RMSXDP和RMSXDP2提供到区段使能电路206。可存在若干区段使能电路206,其中的每一个产生不同多字线驱动器信号MWL。MWL信号又激活可激活字线的字线驱动器。一或多个区段使能电路206可由经解码地址信号RF3-11激活。当有效区段使能电路206接收到处于有效状态(例如,均在高逻辑电平下)的区段使能信号RMSXDP和RMSXDP2时,所述区段使能电路206在有效电平下提供其MWL信号。

图3为根据本公开的一些实施例的区段使能电路的示意图。在一些实施例中,区段使能电路300可为图1的行解码器108的一部分和/或可实施图2的区段使能电路206。

区段使能电路300在MWL产生器电路310处接收区段使能信号RMSXDP和RMSXDP2,其在信号RMSXDP和RMSXDP2为无效的且MWL产生器电路310为有效的时在有效电平下提供MWL信号。MWL产生器电路310展示为堆叠式方框以表示存在多个MWL产生器电路310,其中的每一个可被激活以提供相应的MWL信号。MWL产生器电路310可由经解码地址信号RF345、RF678和RF91011(例如,图2的RF3-11)激活。虽然相对于本公开论述信号的某些布置(例如,RF347、RF678和RF91011),但这些仅为实例,且可在其它实例实施例中使用行地址的其它信号和位模式。

基于经解码行地址XADD,信号RF345、RF678和RF91011为经解码地址信号。举例来说,一或多个信号RF345由行地址的第3位、第4位和第5位激活。类似地,RF678可基于XADD<6:8>而处于有效状态,且RF91011可基于XADD<9:11>而处于有效状态。信号RF678和RF91011指定多个MWL产生器310,而信号RF345可指定要激活的那些指定MWL产生器310中所选择的一者。举例来说,区段使能电路300包含晶体管302和304。晶体管302具有耦合到多个MWL产生器电路310的漏极和耦合到晶体管304的漏极的源极,所述晶体管304具有耦合到接地电压(例如,VSS)的源极。晶体管302的栅极耦合到RF678,且晶体管304的栅极耦合到RF91011。晶体管302和304可为n型晶体管。因此,当耦合到此MWL驱动器310的RF678和RF91011信号均为有效的时,MWL驱动器(连同由RF678和RF91011的那些值激活的任何其它者)耦合到地面。MWL产生器电路310包含晶体管316,其具有耦合到晶体管314的源极的漏极、耦合到晶体管302的漏极的源极以及耦合到RF345的栅极。晶体管316可为n型晶体管。信号RF345可特定于此MWL产生器电路310。因此,当RF345(连同RF678和RF91011)为有效的时,晶体管316将晶体管314耦合到地面,从而激活MWL产生器电路310。信号RF345可具备所指定的定时以控制MWL产生器310的激活,作为存取操作的部分。

MWL产生器电路310包含晶体管312,其具有耦合到电压VCCP的源极、耦合到节点330的漏极以及耦合到RMSXDP的栅极。晶体管312可为p型晶体管。MWL产生器电路310还包含晶体管314,其具有耦合到节点330的漏极、耦合到晶体管316的漏极的源极以及耦合到RMSXDP2的栅极。晶体管314可为n型晶体管。因此,晶体管312和314可稍微类似于反相器电路而起作用,其中节点330作为输出。然而,晶体管312和314耦合到在有效时具有不同电压的单独输入RMSXDP和RMSXDP2,但由于它们共享逻辑电平,因此这两者同时为有效的。这是因为晶体管316上的栅极电压(例如,当RF345处于有效状态时)为VPERI,其为比VCCP(当RMSXDP处于有效状态时,晶体管312上的栅极电压)低的电压。晶体管314上的VACTD的栅极电压(例如,当RMSXDP2处于有效状态时)可充当中间物以提高VCCP域中的信号(例如,RMSXDP)与VPERI域中的信号(例如,RF345、RF678和RF91011)之间的连接的可靠性。

节点330携载作为RMSXDP和RMSXDP2的逻辑反的信号。类似于RMSXDP,节点330上的信号在VCCP域中。晶体管320和322充当反相器且在节点334上提供信号,所述信号为节点330上的信号的逻辑反(例如,节点334上的信号与RMSXDP和RMSXDP2的逻辑电平匹配)。晶体管320具有耦合到控制信号CP的源极、耦合到节点334的漏极以及耦合到节点330的栅极。晶体管320可为p型晶体管。晶体管322具有耦合到接地电压的源极、耦合到节点334的漏极以及耦合到节点330的栅极。晶体管322可为n型晶体管。因此,当信号CP为有效的时,晶体管320和322可充当反相器。可在RF345变为有效之后的一段时间在有效电平(例如,VCCP)下提供信号CP,以控制MWL产生器310的定时。

晶体管318具有耦合到第二控制信号CP2的源极、耦合到节点330的漏极以及耦合到节点334的栅极。晶体管318可为p型晶体管。当节点334上的信号为无效的(例如,RMSXDP和RMSXDP2也为无效的)时,晶体管318为有效的,且控制信号CP2的电压耦合到节点330。这可用于驱动节点330上的电压。

节点334上的信号由晶体管324和326反转,以在充当MWL信号的节点336上提供输出电压。晶体管324具有耦合到VCCPRdec(其可为内部VCCP电压)的源极、耦合到节点336的漏极以及耦合到节点334的栅极。晶体管324可为p型晶体管。晶体管326具有耦合到控制信号CN的源极、耦合到节点336的漏极以及耦合到节点334的栅极。晶体管326可为n型晶体管。晶体管324和326可一起充当反相器,使得沿着节点336的信号MWL具有来自节点334的反转逻辑电平(例如,信号MWL为RMSXDP和RMSXDP2的逻辑反)。信号CN可为用于管理提供信号MWL的定时的控制信号。

以此方式,被激活到区段使能信号的晶体管314的节点直接耦合(例如,不具有中间晶体管)到晶体管316的节点,所述节点由VPERI电压域中的信号(RF345)激活。由于晶体管314耦合到在VCCP与VPERI之间的不同的中间电压域中的区段使能信号,因此与由VCCP操作的晶体管的节点直接耦合到由VPERI操作的晶体管的节点的情况相比,可存在提高的可靠性。

图4为根据本公开的一些实施例的区段使能信号驱动器的示意图。在一些实施例中,驱动器400可包含于图1的行解码器108和/或图2的驱动器204的实施中。驱动器400接收预区段使能信号RMSXDP_PRE且提供信号RMSXDP和RMSXDP2。驱动器400包含:电平移位器402,其将PRSXDP_PRE从VPERI域转换到VCCP域;反相器404和406,其提供RMSXDP;以及晶体管410和412,其提供RMSXDP2。

电平移位器402具有耦合到RMSXDP_PRE的输入和耦合到节点408的输出。电平移位器402接收VPERI电压域中的信号(RMSXDP_PRE),且将信号提供到节点408,所述信号具有与RMSXDP_PRE相同的逻辑电平但在VCCP域中。节点408耦合到反相器404的输入,所述反相器具有耦合到反相器406的输入的输出。反相器406提供信号RMSXDP。由于在节点508与信号RMSXDP之间存在串联的两个反相器404和406,因此信号RMSXDP具有与节点408相同的逻辑电平(例如,与RMSXDP_PRE相同的电平)。反相器404和406可在VCCP域中操作。

驱动器400包含:晶体管410,其具有耦合到电压VACTD的源极、耦合到携载RMSXDP2的节点的漏极以及耦合到节点408(例如,RMSXDP_PRE,但在VCCP域中)的栅极;以及晶体管412,其具有耦合到RMSXDP2的源极、耦合到接地电压(例如,VSS)的漏极以及耦合到由反相器404提供的信号的栅极(例如,在VCCP域中的RMSXDP_PRE的反相)。晶体管410和412均可为n型晶体管。因此,当RMSXCDP_PRE为有效的(例如,在VPERI下)时,那么将电压VCCP(由于电平移位器402)施加到晶体管410的栅极,从而将电压VACTD耦合到RMSXDP2。当RMSXDP_PRE为无效的(例如,在接地电压VSS下)时,那么将VCCP的电压(由于反相器404)施加到晶体管412的栅极,从而将RMSXDP2耦合到接地电压(例如,VSS)。

图5为根据本公开的一些实施例的方法的流程图。在一些实施例中,方法500可由图1到4中描述的设备或系统中的一或多者实施。

方法500包含框510,其描述将行地址解码为区段预使能信号。行地址可为存储器阵列(例如,图1的118)上的存取操作的部分。行地址可具有对应于存储器阵列中的分级结构的不同层级的不同部分。方法500可包含基于行地址的区段地址部分产生预使能信号。

方法500包含框520,其描述在第一电压域中产生第一区段使能信号。第一区段使能信号(例如,RDMSXP)可使用第一电压(例如,VCCP)来表示逻辑高(例如,有效第一区段使能信号),且使用接地电压(例如,VSS)来表示逻辑低(例如,无效第一区段使能信号)。方法500包含当预使能信号为有效时产生有效第一区段使能信号,且当预使能信号为无效时产生无效第一区段使能信号。

所述方法包含框530,其描述在第二电压域中产生第二区段使能信号。第二区段使能信号(例如,RDMSXP2)可使用第二电压(例如,VACTD)来表示逻辑高(例如,有效第二区段使能信号),且使用接地电压(例如,VSS)来表示逻辑低(例如,无效第二区段使能信号)。方法500包含当预使能信号为有效时产生有效第二区段使能信号,且当预使能信号为无效时产生无效第二区段使能信号。

第一区段使能信号和第二区段使能信号可由区段使能信号驱动器电路(例如,图2的204)产生。预使能信号可在第三电压域(例如,VPERI域)中,其中第三电压(例如,VPERI)表示有效预使能信号,且接地电压(例如,VSS)表示无效预使能信号。电压VACTD可在电压VPERI与VCCP之间。

方法500包含框540,其描述基于第一区段使能信号和第二区段使能信号提供多字线信号。区段使能电路(例如,206)可提供多字线信号MWL。方法500可包含在第一区段使能信号和第二区段使能信号为有效时在无效电平下提供MWL信号,且在第一区段使能信号和第二区段使能信号为无效时在有效电平下提供MWL信号。MWL信号可在第一电压域(例如,VCCP域)中。

方法500可包含响应于MWL信号而激活至少一个字线(例如,在图1的存储器阵列118中)。方法500可包含:将行地址解码为经解码地址信号(例如,图2的RF3-11);响应于经解码地址信号而激活所选择的区段使能电路;以及当所选择的区段使能电路为有效的时,用所选择的区段使能电路提供多字线驱动器信号。

当然,应了解,本文中所描述的实例、实施例或过程中的任一者可与一或多个其它实例、实施例和/或过程组合或分开和/或在根据本发明系统、装置和方法的单独装置或装置部分当中执行。

最后,上文的论述意图仅为说明性的,且不应解释为将所附权利要求书限于任何特定实施例或实施例群组。因此,虽然已参考示例性实施例详细地描述了本发明系统,但还应了解,在不脱离如所附权利要求书中阐述的本发明系统的更广和预期精神和范围的情况下,所属领域的技术人员可设计许多修改和替代实施例。因此,说明书和附图应以说明性方式看待,且不旨在限制所附权利要求书的范围。