一种存储芯片的测试系统及测试方法

文献发布时间:2024-04-18 19:48:15

技术领域

本发明涉及静态存储技术领域,特别涉及一种存储芯片的测试系统及测试方法。

背景技术

存储芯片是嵌入式系统芯片的概念在存储行业的具体应用。无论是系统芯片还是存储芯片,都是通过在单一芯片中嵌入软件,以实现多功能、高性能以及对多种协议、多种硬件和不同应用的支持。存储芯片广泛应用于计算机、移动设备、物联网等领域,用于存储各种数据,如操作系统、应用程序、音乐、视频、照片等。

目前存储芯片的兼容性能较差,会发生存储系统运行异常的情况。因此,存在待改进之处。

发明内容

本发明的目的在于提供一种存储芯片的测试系统及测试方法,用于解决现有技术中存在存储芯片的兼容性能较差的问题。

为解决上述技术问题,本发明是通过以下技术方案实现的:

本发明提出一种存储芯片的测试系统,包括:

通用串口总线模块,用以与主机之间进行数据传输;

存储模块,用以存储所述主机写入的测试系统映像文件;

内存模块,用以运行所述测试系统映像文件中的测试程序;

多个芯片测试座,用以安装待测芯片;

中央处理模块,用以调节所述芯片测试座周围的环境温度,调节所述待测芯片输入时钟信号的延迟值,并向所述待测芯片写入测试数据,收集所述待测芯片上的响应数据,以检测所述待测芯片的兼容性能;以及

电源模块,用以对所述芯片测试座和所述中央处理模块供电。

在本发明的一个实施例中,所述中央处理模块用以将所述时钟信号的一个周期划分为多个时钟区间,并以不同的时钟区间作为所述时钟信号的延迟值,向所述待测芯片写入测试数据。

在本发明的一个实施例中,所述中央处理模块用以将一个时钟区间作为单位延迟值,在所述时钟信号每增加一个单位延迟值后,向所述待测芯片写入测试数据。

在本发明的一个实施例中,所述中央处理模块用以将所述芯片测试座周围的环境温度设定为多个区间,并在多个区间的环境温度下向所述待测芯片写入测试数据。

在本发明的一个实施例中,所述中央处理模块用以判断所述响应数据与所述时钟信号是否具有时间上的同步性,并基于判断结果,比较所述待测芯片的兼容性能。

在本发明的一个实施例中,在所述响应数据与所述时钟信号具有时间上的同步性时,所述中央处理模块将所述响应数据表示为正常数据,在所述响应数据与所述时钟信号不具有时间上的同步性时,所述中央处理模块将所述响应数据表示为异常数据。

在本发明的一个实施例中,在不同的环境温度下,当所述正常数据关联延迟值的时钟区间占时钟信号一个周期的60%以上,且不同的环境温度对应所述正常数据的重合度超过90%以上时,所述中央处理模块判定所述待测芯片兼容性能处于第一状态。

在本发明的一个实施例中,在不同的环境温度下,当所述正常数据关联延迟值的时钟区间占时钟信号一个周期的50%~60%,且不同的环境温度对应所述正常数据的重合度超过90%以上时,所述中央处理模块判定所述待测芯片兼容性能处于第二状态。

在本发明的一个实施例中,在不同的环境温度下,当所述正常数据关联延迟值的时钟区间占时钟信号一个周期的50%以下,且在相邻延迟值的时钟区间内,所述正常数据和所述异常数据之间交叉出现时,所述中央处理模块判定所述待测芯片兼容性能处于第三状态。

本发明还提出一种存储芯片的测试方法,包括:

通过通用串口总线模块,接收主机传输的数据;

获取所述主机写入的测试系统映像文件,存储至存储模块上,并在内存模块上运行所述测试系统映像文件中的测试程序;

将待测芯片安装在多个芯片测试座上;

通过电源模块,对所述芯片测试座和中央处理模块进行供电;以及

通过所述中央处理模块,调节所述芯片测试座周围的环境温度,调节所述待测芯片输入时钟信号的延迟值,并向所述待测芯片写入测试数据,收集所述待测芯片上的响应数据,以检测所述待测芯片的兼容性能。

如上所述,本发明提供了一种存储芯片的测试系统及测试方法,可快速高效的筛选出兼容性能良好的存储芯片。

当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

附图说明

为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

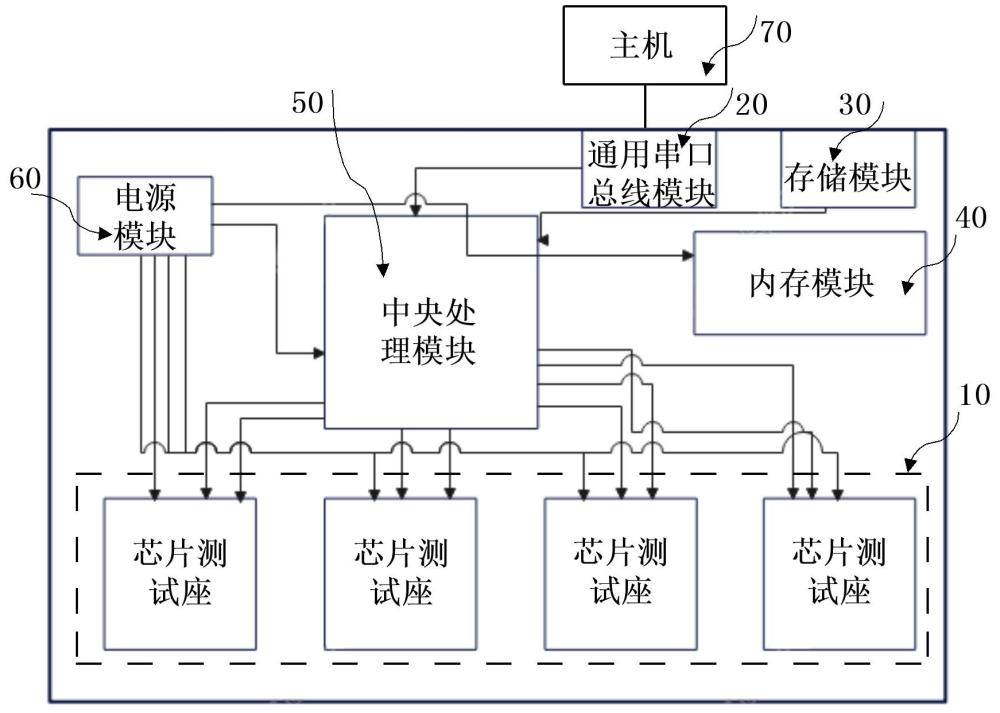

图1为本发明一实施例中存储芯片的测试系统的结构示意图。

图2为本发明一实施例中存储芯片的测试系统中时钟信号的示意图。

图3为本发明一实施例中存储芯片的测试系统中响应数据的示意图。

图4为本发明一实施例中存储芯片的测试方法的步骤示意图。

图5为本发明一实施例中图4中步骤S30的步骤示意图。

图6为本发明一实施例中图4中步骤S50的步骤示意图。

图中:10、芯片测试座;20、通用串口总线模块;30、存储模块;40、内存模块;50、中央处理模块;60、电源模块;70、主机。

具体实施方式

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其它优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。还应当理解,本发明实施例中使用的术语是为了描述特定的具体实施方案,而不是为了限制本发明的保护范围。下列实施例中未注明具体条件的试验方法,通常按照常规条件,或者按照各制造商所建议的条件。

须知,本说明书所附图式所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供熟悉此技术的人士了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容所能涵盖的范围内。同时,本说明书中所引用的如“上”、“下”、“左”、“右”、“中间”及“一”等的用语,亦仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当亦视为本发明可实施的范畴。

请参阅图1至图6,本发明提出一种存储芯片的测试系统,可对eMMC(EmbeddedMulti Media Card,嵌入式多媒体卡)、SSD(Solid State Disk,固态硬盘)、UFS(UniveralFlash Storage,通用闪存存储器)等存储芯片的兼容性能进行检测。本发明在不同存储芯片适配终端产品的PCB(Printed Circuit Board,印制电路板)时,可在不同的环境条件下,快速高效的筛选出兼容性能良好的存储芯片。下面通过具体的实施例进行详细的描述。

请参阅图1,在本发明的一个实施例中,本发明可提出一种存储芯片的测试系统,可包括芯片测试座10、通用串口总线模块20、存储模块30、内存模块40、中央处理模块50和电源模块60。芯片测试座10上可安装待测芯片,待测芯片可为eMMC、SSD或者UFS等存储芯片。芯片测试座10的数量可为多个,多个芯片测试座10上可安装不同的待测芯片。可将芯片测试座10放入温箱中,温箱中的环境温度可进行调节。在多个芯片测试座10上安装一批次相同型号的待测芯片时,可挑选出一批次中兼容性能强的待测芯片。在多个芯片测试座10上安装不同批次相同型号的待测芯片时,可挑选出兼容性能最强的一个批次的待测芯片。在多个芯片测试座10上安装不同型号的待测芯片时,可挑选出兼容性能最强的一个型号的待测型号。通用串口总线模块(USB,Universal Serial Bus)20作为测试系统的输入、输出接口,可接收主机70输入的数据,也可向主机70发送数据。在主机70向通用串口总线模块20传输测试系统映像文件(OS Image)后,通用串口总线模块20可将测试系统映像文件传输并保存在存储模块30上。存储模块30可为SD(存储)卡。内存模块30可运行测试系统映像文件中的测试程序。内存模块30可为DRAM(Dynamic Random Access Memory,动态随机存取存储器)。中央处理模块(CPU,Central Processing Unit)50可对温箱内芯片测试座10所处的环境温度进行调节。中央处理模块50还可对待测芯片输入时钟信号(clock)的延迟值进行调节。中央处理模块50向待测芯片写入测试数据,收集待测芯片上的响应数据,响应数据是待测芯片对测试数据进行处理所生成的。中央处理模块50通过对响应数据进行统计,以检测待测芯片的兼容性能,兼容性能可指待测芯片在不同运行环境下的稳定性。可将响应数据上传至主机10中,由主机10统计生成报表,对比出不同待测芯片的兼容性能。

请参阅图1和图2,在本发明的一个实施例中,中央处理模块50可调整输入待测芯片时钟信号的延迟值,以在不同延迟值的时钟信号下,对待测芯片的兼容性能进行检测。中央处理模块50可将时钟信号的一个周期划分为多个时钟区间,并将不同的时钟区间作为延迟值,向待测芯片写入测试数据。中央处理模块50还可将一个时钟区间作为单位延迟值,在时钟信号每增加一个单位延迟值后,向待测芯片写入测试数据。例如,如图2所示,可将时钟信号中一个周期的高电平划分为64个时钟区间,可记为T1~T64。T1~T64表示为具有相应延迟值的时钟区间。以一个时钟区间作为单位延迟值,在时钟信号对应的T1~T64共64个延迟值时,中央处理模块50分别向待测芯片写入测试数据,并记录待测芯片上的响应数据。将一个具有延迟值的时钟信号输入至待测芯片,当中央处理模块50向待测芯片输入的测试数据写入通过时,待测芯片上生成正常的响应数据,可记为正常数据。当中央处理模块50向待测芯片输入的测试数据写入失败时,待测芯片上生成异常的响应数据,或者不生产响应数据,可记为异常数据。即响应数据与时钟信号具有关于时间上的同步性时,表明测试数据写入通过,响应数据记为正常数据。响应数据与时钟信号不具有关于时间上的同步性时,表明测试数据写入失败,响应数据记为异常数据。

请参阅图1、图2,在本发明的一个实施例中,中央处理模块50可对温箱中芯片测试座10周围的环境温度进行控制调节,中央处理模块50可将芯片测试座10周围的环境温度调节为高温、常温和低温等多个区间,并在多个区间的环境温度下向待测芯片写入测试数据,以检测待测芯片在不同环境温度下的兼容性能。其中,高温状态可大于等于105℃,常温状态可在20℃~30℃的范围,低温状态可小于等于-40℃。

请参阅图1、图2和图3,在本发明的一个实施例中,中央控制模块50可记录待测芯片的响应数据,并在不同的环境温度、不同延迟值的时钟信号下,统计不同待测芯片的响应数据。如图3所示,可将正常的响应数据记为0,将异常的响应数据记为1。高温环境可设为105℃,常温环境可设为25℃,低温环境可设为-40℃。对于待测芯片中的第一芯片,在高温、常温和低温等不同的环境温度下,标记为0的正常数据关联延迟值的时钟区间占时钟信号一个周期的60%以上,并且不同环境温度关联标记为0的正常数据彼此的重合度超过90%以上时,中央处理模块50可判定待测芯片的兼容性能处于第一状态。对于待测芯片中的第二芯片,在高温、常温和低温等不同的环境温度下,标记为0的正常数据关联延迟值的时钟区间占时钟信号一个周期的50%~60%,并且不同环境温度关联标记为0的正常数据彼此的重合度超过90%以上时,中央处理模块50可判定待测芯片的兼容性能处于第二状态。对于待测芯片中的第三芯片,在高温、常温和低温等不同的环境温度下,标记为0的正常数据关联延迟值的时钟区间占时钟信号一个周期的50%以下,并且在相邻延迟值的时钟区间内,正常数据和异常数据之间相互交叉出现时,中央处理模块50可判定待测芯片的兼容性能处于第三状态。第一状态的兼容性能大于第二状态的兼容性能,第二状态的兼容性能大于第三状态的兼容性能。当待测芯片的兼容性能处于第一状态时,可表示该待测芯片的兼容性能良好。当待测芯片的兼容性能处于第二状态时,可表示该待测芯片的兼容性能一般。当待测芯片的兼容性能处于第三状态时,可表示该待测芯片的兼容性能较差。

请参阅图4,在本发明的一个实施例中,本发明可提出一种存储芯片的测试方法,可包括以下的步骤。

步骤S10、计算机通过通用串口总线模块与多通道功能筛选子板连接。

步骤S20、计算机烧录多通道功能筛选子板的操作系统映像文件到存储模块。

步骤S30、将待测芯片安装在多个芯片测试座上。

步骤S40、多通道功能筛选子板上电,中央处理模块运行程序,在默认参数下初始化多个待测芯片,并挂载附属分区。

步骤S50、通过中央处理模块,调节芯片测试座周围的环境温度,调节待测芯片输入时钟信号的延迟值,并向待测芯片写入测试数据,收集待测芯片上反应的响应数据,以检测待测芯片的兼容性能。

步骤S10、计算机通过通用串口总线模块与多通道功能筛选子板连接。

在本发明的一个实施例中,可将存储芯片的测试系统中的多个芯片测试座10、通用串口总线模块20、存储模块30、内存模块40、中央处理模块50和电源模块60设置到一个电路板上,形成一个多通道功能筛选子板。主机70可为计算机(PC,personal computer)、手机(cell phone)和平板电脑(Pad,portable android device)等。当主机70为计算机时,计算机可与通用串口总线模块20插接,以实现与多通道功能筛选子板的连接。

步骤S20、计算机烧录多通道功能筛选子板的操作系统映像文件到存储模块。

在本发明的一个实施例中,计算机可烧录多通道功能筛选子板的操作系统映像文件(OS image)到存储模块20中。在内存模块30上,可运行测试系统映像文件中的测试程序。

步骤S30、将待测芯片安装在多个芯片测试座上。

在本发明的一个实施例中,在多通道功能筛选子板未通电的状态下,在多个芯片测试座10上安装不同的待测芯片。可将芯片安装座10设置于温箱中,以便于将待测芯片的测试环境温度进行调节。通过将待测芯片设置在芯片测试座10上,可用以解决现有存储芯片兼容能力需要焊接到终端产品上直接测试缺乏的通用性。通过在芯片测试座10上对待测芯片进行安装、拆卸,可提高对待测芯片兼容性能进行检测的效率。

步骤S40、多通道功能筛选子板上电,中央处理模块运行程序,在默认参数下初始化多个待测芯片,并挂载附属分区。

在本发明的一个实施例中,电源模块60与芯片测试座10、中央处理模块50电连接,以实现对多通道筛选子板进行上电。中央处理模块50控制内存模块30运行测试程序,在默认参数下初始化四个待测芯片,并可挂载附属分区。

步骤S50、通过中央处理模块,调节芯片测试座周围的环境温度,调节待测芯片输入时钟信号的延迟值,并向待测芯片写入测试数据,收集待测芯片上的响应数据,以检测待测芯片的兼容性能。

在本发明的一个实施例中,中央处理模块50作为存储芯片的测试系统的运算和控制核心,是数据处理、程序运行的最终执行单元。中央处理模块50可用以调节芯片测试座10周围的环境温度,中央处理模块50可调节待测芯片输入时钟信号的延迟值。中央处理模块50还可向待测芯片写入测试数据,并收集待测芯片上的响应数据。通过测试数据、输入的时钟信号和响应数据的比较,中央处理模块50可用以检测出待测芯片的兼容性能。本发明操作简单,多个芯片测试座10可测试多个不同类型的待测芯片,可自动化收集数据,统计分析能力强。本发明可在不同延迟值的时钟信号和不同环境温度下,对多个待测芯片的兼容性能进行快速、全面、精确的分析。

请参阅图5,在本发明的一个实施例中,步骤S30可包括步骤S310和步骤S320。步骤S310可表示为多通道功能筛选子板断电后,在多个芯片测试座10中分别放入不同的待测芯片。步骤S320可表示为多通道功能筛选子板放置在温箱中,测试环境温度可调节为高温、常温、低温的状态。

请参阅图6,在本发明的一个实施例中,步骤S50可包括步骤S510、步骤S520、步骤S530、步骤S540和步骤S550。其中步骤S510可表示为中央处理模块50调整待测芯片时钟信号的一个时钟区间为单位的延迟值,可写入测试数据到多个待测芯片中,测试数据可为大于1M(MB,兆)的数据量。步骤S520可表示为中央处理模块50按顺序读取待测芯片中的响应数据,并测试数据、输入的时钟信号和响应数据进行比较后,判断测试数据是否正确写入到待测芯片中。在步骤S520中,当判断结果为测试数据正确写入到待测芯片中,可进行步骤S530。步骤S530可表示为记录当前数据写入通过时,时钟信号设置的延迟值,并可通过通用串口总线回传至计算机中。在步骤S520中,当判断结果为测试数据没有正确写入到待测芯片中,可进行步骤S540。步骤S540可表示为记录当前数据写入失败时,时钟信号设置的延迟值,并可通过通用串口总线回传至计算机中。步骤S550可表示为计算机生成报表,并可以对比出多个待测芯片兼容性能的相关数值,例如为图3中多个待测芯片兼容性能的相关数值。

本发明提出一种存储芯片的测试系统及测试方法,本发明的操作简单,复用性强,可在不同的测试环境中,快速检测出多个存储产品的兼容性能,提高了测试效率。

以上公开的本发明实施例只是用于帮助阐述本发明。实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施方式。显然,根据本说明书的内容,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地理解和利用本发明。本发明仅受权利要求书及其全部范围和等效物的限制。