读出定时生成电路及半导体存储装置

文献发布时间:2024-04-18 19:48:15

相关申请的交叉引用

本申请享有以日本专利申请2022-48991号(申请日:2022年3月24日)为基础申请的优先权。本申请通过参照该基础申请而包含基础申请的全部内容。

技术领域

实施方式涉及读出定时(sense timing)生成电路及半导体存储装置。

背景技术

在半导体存储装置中,在数据读出时位线成为足以对读出放大器的输出进行确定的电位后,将读出放大器活性化。此时,设定读出放大器被活性化的定时(下面,称为读出定时),以便对在读出放大器中使用的晶体管的特性波动进行吸收,能够可靠地判定读出信号的电平。

另外,读出信号的电位的变化根据周围温度等的温度而不同,若将读出放大器被活性化的定时(下面,称为读出定时)设为相同,则在存储器单元的值为“0”的情况下,温度越高,则读出裕度(读出的信号的电平与判定用的基准信号的电平之差)变得越少,在存储器单元的值为“1”的情况下,温度越低,则数据读出裕度变得越少。

发明内容

本发明提供能够生成读出定时的读出定时生成电路及半导体存储装置,在该读出定时能够减少由温度造成的影响,增大读出裕度并进行可靠性高的动作。

实施方式的读出定时生成电路基于从输入端子输入的时钟信号,从输出端子输出使读出放大器为使能状态的读出放大器使能信号,读出定时生成电路具有:延迟电路部,具有延迟量伴随温度上升而变少的温度特性,且具有温度特性不同的多个种类的多个延迟电路,延迟电路部使时钟信号延迟而作为读出放大器使能信号进行输出;以及连接切换部,对从输入端子至输出端子的延迟电路部中的多个延迟电路的连接状态进行切换。

附图说明

图1是实施方式所涉及的半导体存储装置的概要结构的说明图。

图2是读出放大器电路的主要部分结构例的说明图。

图3是读出定时生成电路的一个例子的说明图。

图4A及图4B是延迟电路的结构例的说明图。

图5是现有的问题点的说明图。

图6是实施方式的动作说明图。

具体实施方式

以下参照附图,对实施方式的半导体存储装置详细地进行说明。

此外,本发明不由这些实施方式限定。

接下来,作为半导体装置的一个例子,对NOR型闪存详细地进行说明。

图1是实施方式所涉及的半导体存储装置的概要结构的说明图。

半导体装置10构成为NOR型闪存,如图1所示,具有存储器单元阵列11、行译码器12、列译码器13、参考电位生成电路14、读出放大器电路15、数据输出电路16及控制电路17。

存储器单元阵列11具有配置为棋盘的网格状的多个存储器单元MC。

另外,存储器单元阵列具有多个字线WL、多个源极线SL和多个位线BL。

在图1中,为了容易理解,仅将处于选择状态的存储器单元MC显示出一个,仅显示出与该存储器单元相对应的字线WL、源极线SL及位线BL。

在这里,存储器单元MC具有存储器单元晶体管TR,该存储器单元晶体管TR的源极端子与源极线SL连接、栅极端子与字线WL连接、漏极端子与位线BL连接。

行译码器12在控制电路17的控制下,将与读出对象的存储器单元MC相对应的字线WL设为使能状态。

列译码器13在控制电路17的控制下,将与读出对象的存储器单元MC相对应的源极线SL及位线BL设为使能状态。

参考电位生成电路14生成参考电位并对读出放大器电路15供给。

读出放大器电路15将在规定的定时处于选择状态的存储器单元MC所对应的位线的电位与参考电位进行比较,对存储器单元MC的数据进行判定,将判定结果输出至数据输出电路16。

数据输出电路16基于读出放大器电路15的输出,将读出数据DOUT进行输出。

控制电路17基于来自未图示的主机装置(例如,MPU)的时钟信号CLK、指令数据CMD及地址数据ADD,对行译码器12、列译码器13及读出放大器电路15进行控制,以便进行数据相对于对应的存储器单元MC的写入、读出或者删除。

图2是读出放大器电路的主要部分结构例的说明图。

接下来,对读出放大器电路15的结构进行说明。

读出放大器电路15与位线BL相对应,具有多个读出放大器151和多个读出定时生成电路152。

在该情况下,读出定时生成电路152也能够在多个读出放大器151中共用。

读出放大器151向非反相输入端子输入来自各模块BLK的源极线SL的输入信号IN,向反相输入端子输入基准电压Vref,在来自读出定时生成电路152的读出放大器使能信号SAE为使能状态的情况下,在输入信号IN为基准电压Vref以上的高电压的情况下,将“H”电平的输出信号OUT进行输出。

另外,在来自读出定时生成电路152的读出放大器使能信号SAE为使能状态的情况下,在输入信号IN为小于基准电压Vref的电压的情况下,将“L”电平的输出信号OUT进行输出。

在这里,对读出定时生成电路152的结构例进行说明。

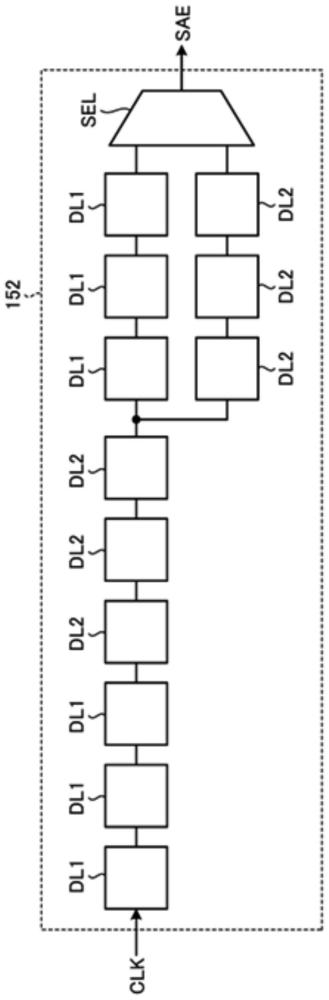

图3是读出定时生成电路的一个例子的说明图。

读出定时生成电路152具有多个(在图3的例子中为6个)第1延迟电路DL1、多个(在图3的例子中为6个)第2延迟电路DL2和选择器SEL。

在这里,第1延迟电路DL1和第2延迟电路DL2如后面详述那样,温度特性及延迟时间不同。

读出定时生成电路152更详细地说,在输入端设置有供时钟信号CLK输入的串联连接的3个第1延迟电路DL1。

在该3个第1延迟电路DL1的后级设置有3个第2延迟电路DL2。

这6个延迟电路作为串联连接多个延迟电路而成的串联连接部而发挥功能。

并且,在该3个第2延迟电路DL2的后级,将串联连接的3个第1延迟电路DL1和串联连接的3个第2延迟电路DL2并联连接。

这6个延迟电路与前述串联部连接,作为并联连接部发挥功能,该并联连接部是延迟电路进行了多个系统(在图3的例子中为2个系统)连接而成的。

而且,在并联连接部的后级,连接有作为连接切换部而发挥功能的选择器SEL,在选择器SEL的各输入端子连接有各系统,将任一个输入端子的输入信号作为读出放大器使能信号SAE进行输出。

在以上的说明中,作为连接切换部而发挥功能的选择器SEL与并联连接部的后级连接,但也能够设为,将并联连接部的各系统的输出端共用连接,将作为连接切换部的选择器SEL设置于串联连接部与并联连接部之间。

或者,也能够构成为,将连接切换部连接在并联连接部的后级,并且在连接切换部的后级连接串联连接部。

在这里,对第1延迟电路DL1及第2延迟电路DL2的结构例详细地进行说明。

图4A及图4B是延迟电路的结构例的说明图。

图4A是第1延迟电路DL1的电路结构的一个例子的说明图。

图4B是第2延迟电路DL2的电路结构的一个例子的说明图。

在图中,对相同的部分标注同一附图标记。

第1延迟电路DL1若大致区分,则如图4A所示,具有:第1逆变器INV1,能够对驱动力进行调整,且具有负的温度系数(负的温度特性);第2逆变器INV21,输入端子与第1逆变器INV1的输出端子连接,且具有正的温度系数(正的温度特性);以及第2逆变器INV22,输入端子与第2逆变器INV21的输出端子连接,且具有正的温度系数(正的温度特性)。

在该情况下,正的温度特性是指温度越高,则延迟时间变得越长,负的温度特性是指温度越低,则延迟时间变得越长。

另外,第2逆变器INV21和第2逆变器INV22为同一结构,具有同一温度特性。

第1逆变器INV1具有:P沟道MOS晶体管P11,栅极端子与输入端子连接,漏极端子与输出端子连接;以及P沟道MOS晶体管P12,漏极端子与P沟道MOS晶体管P11的源极端子连接,栅极端子被输入驱动力控制信号IREF_P,源极端子与高电位侧电源VDD连接。

并且,第1逆变器INV1具有:N沟道MOS晶体管N11,栅极端子与第1延迟电路DL1的输入端子连接,漏极端子与输出端子连接;以及N沟道MOS晶体管N12,漏极端子与N沟道MOS晶体管N11的源极端子连接,栅极端子被输入驱动力控制信号IREF_N,源极端子与低电位侧电源VSS连接。

第2逆变器INV21具有:P沟道MOS晶体管P21,栅极端子与第1逆变器INV1的输出端子连接,源极端子与高电位侧电源VDD连接,漏极端子与输出端子连接;以及N沟道MOS晶体管N21,栅极端子与输入端子连接,漏极端子与第1延迟电路DL1的输出端子连接,源极端子与低电位侧电源VSS连接。

同样地,第2逆变器INV22具有:P沟道MOS晶体管P21,栅极端子与第2逆变器INV22的输入端子连接,源极端子与高电位侧电源VDD连接,漏极端子与输出端子连接;以及N沟道MOS晶体管N21,栅极端子与输入端子连接,漏极端子与第1延迟电路DL1的输出端子连接,源极端子与低电位侧电源VSS连接。

第2延迟电路DL2若大致区分,则如图4B所示,具有:第1逆变器INV11,能够对驱动力进行调整,且具有负的温度系数(负的温度特性);第1逆变器INV12,输入端子与第1逆变器INV12的输出端子连接,能够对驱动力进行调整,且具有负的温度系数(负的温度特性);以及第2逆变器INV2,输入端子与第1逆变器INV12的输出端子连接,且具有正的温度系数(正的温度特性)。

在该情况下,第1逆变器INV11和第1逆变器INV12为同一结构,具有同一温度特性。

第1逆变器INV11具有:P沟道MOS晶体管P11,栅极端子与第2延迟电路DL2的输入端子连接,漏极端子与输出端子连接;以及P沟道MOS晶体管P12,漏极端子与P沟道MOS晶体管P11的源极端子连接,栅极端子被输入驱动力控制信号IREF_P,源极端子与高电位侧电源VDD连接。

并且,第1逆变器INV11具有:N沟道MOS晶体管N11,栅极端子与第2延迟电路DL2的输入端子连接,漏极端子与输出端子连接;以及N沟道MOS晶体管N12,漏极端子与N沟道MOS晶体管N11的源极端子连接,栅极端子被输入驱动力控制信号IREF_N,源极端子与低电位侧电源VSS连接。

第1逆变器INV12具有:P沟道MOS晶体管P11,栅极端子与第1逆变器INV11的输出端子连接,漏极端子与第1逆变器INV12的输出端子连接;以及P沟道MOS晶体管P12,漏极端子与P沟道MOS晶体管P11的源极端子连接,栅极端子被输入驱动力控制信号IREF_P,源极端子与高电位侧电源VDD连接。

并且,第1逆变器INV12具有:N沟道MOS晶体管N11,栅极端子与第1逆变器INV11的输出端子连接,漏极端子与输出端子连接;以及N沟道MOS晶体管N12,漏极端子与N沟道MOS晶体管N11的源极端子连接,栅极端子被输入驱动力控制信号IREF_N,源极端子与低电位侧电源VSS连接。

第2逆变器INV2具有:P沟道MOS晶体管P21,栅极端子与第1逆变器INV12的输出端子连接,源极端子与高电位侧电源VDD连接,漏极端子与输出端子连接;以及N沟道MOS晶体管N21,栅极端子与第1逆变器INV12的输出端子连接,漏极端子与第1延迟电路DL1的输出端子连接,源极端子与低电位侧电源VSS连接。

在本实施方式中,第1延迟电路DL1及第2延迟电路DL2成为都具有负的温度系数的延迟电路,但第2延迟电路DL2成为负的温度系数比第1延迟电路DL1大的延迟电路。

即,若将第1延迟电路DL1的温度系数设为P1,将第2延迟电路DL2的温度系数设为P2,则成为0>P1>P2。

换言之,在温度以一定量升高的情况下,第1延迟电路DL1的延迟量的减少比第2延迟电路DL2的延迟量的减少变少。

因此,作为构成读出定时生成电路152的延迟电路,在大量使用第2延迟电路DL2的情况下,与大量使用第1延迟电路DL1的情况相比较,相对于温度上升,延迟量的减少变得更大,即,更早转换为读出放大器使能状态。

在以上的说明中,对第1逆变器INV1、INV11、INV12具有负的温度系数(负的温度特性),第2逆变器INV2、INV21、INV22具有正的温度系数(正的温度特性)的情况进行了说明,但也可以相反。

在该情况下,当然第1延迟电路DL1的温度特性和第2延迟电路DL2的温度特性成为相反的状态。

接下来,对实施方式的动作进行说明。

首先,在实施方式的动作之前,对现有的问题点进行说明。

图5是现有的问题点的说明图。

现有的读出定时生成电路的读出放大器放大器使能信号的输出定时被设为恒定。

另外,在宽温度范围(例如,-40~175℃)对应的闪存中进行读出的情况下,根据在存储器单元中储存的值及温度,读出电压的变动状态不同。

更更详细地说,在构成存储器单元MC的存储器单元晶体管TR的阈值电压Vth高的状态的情况下,即使字线WL成为“H”电平,存储器单元晶体管TR仍保持截止状态不变,位线BL的电位大致仍保持电源电位不变。

但是,由于存储器单元晶体管TR的泄漏电流,位线BL的电位稍稍地逐渐降低。

一般来说,存储器单元晶体管TR的泄漏电流存在越成为高温则越增加的倾向。因此,越成为高温,则如图5所示,将存储器单元MC中所储存的值=0读出的情况下的位线BL的电位的降低变得越快。

因此,动作温度范围越成为更高温,则相对于参考电位Vref的数据读出裕度MG0越有可能变得不充分,读出的数据有可能出现错误。

另一方面,在构成存储器单元MC的存储器单元晶体管TR的阈值电压Vth低的状态的情况下,若字线WL成为高电平,则存储器单元晶体管TR成为导通状态,从位线BL向源极线SL的导通电流流动,位线BL的电位逐渐地降低。

一般来说,存储器单元晶体管TR的导通电流存在越成为低温则越减小的倾向,因此越成为低温,如图5所示将存储器单元MC中所储存的值=1读出的情况下位线BL的电位的降低变得越慢。

因此,动作温度范围越成为更低温,则相对于参考电位Vref的数据读出裕度MG1越有可能变得不充分,读出的数据有可能出现错误。

接下来,再次参照图3对实施方式的动作进行说明。

在读出定时生成电路152中,选择器SEL预先对构成并联连接部的3个串联连接而成的第1延迟电路DL1或者构成并联连接部的3个串联连接而成的第2延迟电路DL2的任一方进行选择。

因此,在选择器SEL中,在预先对构成并联连接部的上列的3个串联连接而成的第1延迟电路DL1进行选择的情况下,读出定时生成电路152实际成为6个第1延迟电路DL1及3个第2延迟电路DL2串联连接的结构。

在选择器SEL中,在预先对构成并联连接部的下列的3个串联连接的第2延迟电路DL2进行选择的情况下,读出定时生成电路152实际成为3个第1延迟电路DL1及6个第2延迟电路DL2串联连接的结构。

图6是实施方式的动作说明图。

在该情况下,在对上列的3个串联连接的第1延迟电路DL1或者下列的3个串联连接的第2延迟电路DL2进行选择的情况的任意情况下,温度系数为负,因此如图6所示,在读出定时生成电路152中输出的读出放大器使能信号SAE成为使能的定时,在规定的高温的情况和规定的低温的情况下变得不同。

例如,在高温的情况下,成为读出放大器使能信号SAE(HT)所示的定时,在低温的情况下,成为读出放大器使能信号SAE(LT)所示的定时。

因此,在将存储器单元中所储存的值=0读出的情况下,如图6的信号波形HT0所示,即使在温度高且在构成读出对象的存储器单元的晶体管的漏极-源极间流动的电流所引起的读出电压的降低大的情况下,在读出放大器使能信号SAE成为使能状态的读出放大器使能信号SAE(HT)定时,也能够将从基准电压Vref起的数据读出裕度MGH确保得充分大,读出的数据不会出现错误。

另外,在将存储器单元MC中所储存的值=1读出的情况下,如图6的信号波形LT1所示,即使温度低且在构成读出对象的存储器单元MC的存储器单元晶体管TR的漏极-源极间流动的电流所引起的读出电压的降低变小,如图6所示,也能够将从基准电压Vref起的数据读出裕度MGL确保得充分大,读出的数据不会出现错误。

但是,在温度特性在负值上过于大的情况下,在将高温时的存储器单元中所储存的值=1读出的情况下,数据读出裕度MGH1减少,读出的数据有可能出现错误。

因此,在本实施方式中,通过适当地设定选择器SEL,来对适当的温度特性的延迟电路进行选择,以便数据读出裕度MGH1不低于数据读出裕度MGL1。

换言之,以将存储器单元MC中所储存的值=1读出的情况下的温度特性与延迟电路的温度特性一致的方式来设定选择器SEL,由此能够使得数据读出裕度MGH1不低于数据读出裕度MGL1。

如以上的说明那样,根据本实施方式,与周围温度相应地,在温度变高的情况下,使读出放大器使能信号SAE成为使能状态的定时快速地移位,在温度降低的情况下,使读出放大器使能信号SAE成为使能状态的定时缓慢地移位,并且能够通过选择器对定时的移位量进行选择,因此能够使实际的读出定时生成电路152的动作变得更适当。

在以上的说明中,对作为并联连接部而设置2个系统的延迟电路组的情况进行了说明,但也能够设置3个系统以上的延迟电路组。

在以上的说明中,构成为作为连接切换部而设置选择器并可选择地对任意的系统进行切换,但也能够以如下方式构成:将构成并联连接部的多个系统的延迟电路组的输入端子共用连接,并且将输出端子共用连接,以仅某一个系统的延迟电路组维持连接状态的方式,将其他延迟电路组的信号传送电路上的保险丝切断或者通过激光而物理性地切断延迟电路组。

对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示出的,并不是要对发明的范围进行限定。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围,能够进行各种省略、置换、变更。这些实施方式以及其变形包含于发明的范围及主旨,并且包含于权利要求书所记载的发明和其等同的范围。