电路板及其制作方法与电子装置

文献发布时间:2023-06-19 18:53:06

技术领域

本发明涉及一种基板结构及其制作方法,尤其涉及一种电路板及其制作方法与采用此电路板的电子装置。

背景技术

在现有电路板中,同轴穿孔(coaxial via)的设计在内部导体层与外部导体层之间需要有一层或一层以上的绝缘层来作阻绝,其中形成绝缘层的方式是通过压合增层的方式来达成。因此在同轴穿孔的两端会有阻抗不匹配且会出现电磁干扰(electromagneticinterference,EMI)屏蔽缺口,进而影响高频信号完整性。此外,在同轴穿孔的设计中,信号路径的两端分别接地路径的两端位于不同平面上,且无法减少噪音干扰。

发明内容

本发明是针对一种电路板,其具有良好的信号回路,可具有较佳的信号完整性。

本发明还针对一种电路板的制作方法,用以制作上述的电路板。

根据本发明的实施例,电路板包括第一介电材料、第二介电材料、第三介电材料、第一外部线路层、第二外部线路层、多个导电结构以及导通孔结构。第二介电材料位于第一介电材料与第三介电材料之间,且第一介电材料的介电常数不同于第二介电材料的介电常数以及第三介电材料的介电常数。第一外部线路层配置于第一介电材料上。第二外部线路层配置于第三介电材料上。导通孔结构至少贯穿第一介电材料与第二介电材料,且电性连接至第一外部线路层与第二外部线路层而定义出信号路径。导电结构彼此电性连接且围绕第一介电材料、第二介电材料以及第三介电材料。导电结构电性连接第一外部线路层与第二外部线路层而定义出接地路径。接地路径环绕信号路径。

在根据本发明的实施例的电路板中,上述的导电结构包括多个第一导电柱、多个第二导电柱、第一线路层、第二线路层以及导电连接层。第一导电柱围绕第一介电材料,而第二导电柱围绕第三介电材料。导电连接层连接第一线路层与第二线路层且围绕第二介电材料。

在根据本发明的实施例的电路板中,上述的电路板还包括第一基材、第二基材以及第三基材。第一基材包括第一基底、第一介电材料以及第一导电柱。第一介电材料以及第一导电柱贯穿第一基底,且第一导电柱位于第一基底与第一介电材料之间。第二基材包括第二基底、第二介电材料、第一线路层、第二线路层以及导电连接层。第二基底具有彼此相对的第一表面与第二表面以及开口,且开口贯穿第二基底。第一线路层与第二线路层分别位于第一表面与第二表面上。导电连接层覆盖开口的内壁且电性连接第一线路层与第二线路层。第二介电材料填满开口。第三基材包括第三基底、第三介电材料以及第二导电柱。第三介电材料以及第二导电柱贯穿第三基底,且第二导电柱位于第三基底与第三介电材料之间。

在根据本发明的实施例的电路板中,上述的第一外部线路层包括第一信号线路与第一接地线路。第二外部线路层包括第二信号线路与第二接地线路。第一信号线路、导通孔结构以及第二信号线路定义出信号路径。第一接地线路、第一导电柱、第一线路层、导电连接层、第二线路层、第二导电柱以及第二接地线路定义出接地路径。

在根据本发明的实施例的电路板中,上述的导通孔结构包括贯孔以及导电材料层。贯孔贯穿第一介电材料、第二介电材料以及第三介电材料。导电材料层覆盖贯孔的内壁且电性连接第一外部线路层与第二外部线路层。

在根据本发明的实施例的电路板中,上述的导通孔结构还包括介电层,填满贯孔。介电层彼此相对的上表面与下表面分别切齐于第一外部线路层的顶表面与第二外部线路层的底表面。

在根据本发明的实施例的电路板中,上述的导通孔结构还包括介电层,填满贯孔。第一外部线路层与第二外部线路层分别覆盖介电层彼此相对的上表面与下表面。

在根据本发明的实施例的电路板中,上述的第一基底的介电常数与第三基底的介电常数分别高于3.6,而第一基底的介电损耗与第三基底的介电损耗分别低于0.02。

在根据本发明的实施例的电路板中,上述的导电结构包括多个第一导电柱、多个第二导电柱、第一线路层、第二线路层、第三线路层以及导电连接层。第一导电柱围绕第一介电材料,而第二导电柱围绕第三介电材料。第二线路层位于第一线路层与第三线路层之间,而导电连接层连接第一线路层、第二线路层以及第三线路层且围绕第二介电材料。

在根据本发明的实施例的电路板中,上述的电路板还包括第一基材以及第二基材。第一基材包括第一基底、第一介电材料以及第一导电柱。第一介电材料以及第一导电柱贯穿第一基底,且第一导电柱位于第一基底与第一介电材料之间。第二基材包括第二基底、第三基底、第二介电材料、第三介电材料、第一线路层、第二线路层、第三线路层、导电连接层、第二导电柱以及开口。第二基底具有彼此相对的第一表面与第二表面。第一线路层与第二线路层分别位于第一表面与第二表面上。第三基底与第三介电材料位于第二基底的第二表面上。第三线路层位于第三基底与第三介电材料上。第二导电柱电性连接第二线路层与第三线路层。开口贯穿第二基底与第三介电材料。导电连接层覆盖开口的内壁且电性连接第一线路层、第二线路层及第三线路层。第二介电材料填满开口。

在根据本发明的实施例的电路板中,上述的第一外部线路层包括第一信号线路与第一接地线路。第二外部线路层包括第二信号线路与第二接地线路。第一信号线路、导通孔结构以及第二信号线路定义出信号路径。第一接地线路、第一导电柱、第一线路层、导电连接层以及第二接地线路定义出接地路径。

在根据本发明的实施例的电路板中,上述的导通孔结构包括贯孔以及导电材料层。贯孔贯穿第一介电材料以及第二介电材料。导电材料层覆盖贯孔的内壁且电性连接第一外部线路层与第二外部线路层。

在根据本发明的实施例的电路板中,上述的导通孔结构还包括介电层,填满贯孔。介电层彼此相对的上表面与下表面分别切齐于第一外部线路层的顶表面与第二外部线路层的底表面。

在根据本发明的实施例的电路板中,上述的介电层的介电常数高于3.6,且介电层的介电损耗低于0.05。

在根据本发明的实施例的电路板中,上述的导通孔结构还包括介电层,填满贯孔。第一外部线路层与第二外部线路层分别覆盖介电层彼此相对的上表面与下表面。

在根据本发明的实施例的电路板中,上述的介电层的介电常数高于3.6,且介电层的介电损耗低于0.05。

在根据本发明的实施例的电路板中,上述的导电结构包括多个第一导电柱、多个导通孔、第一线路层、第二线路层、第三线路层以及导电连接层。第一导电柱围绕第一介电材料,而导通孔贯穿第三介电材料。第二线路层位于第一线路层与第三线路层之间。导电连接层连接第一线路层、第二线路层以及第三线路层且围绕第二介电材料。

在根据本发明的实施例的电路板中,上述的电路板还包括第一基材以及第二基材。第一基材包括第一基底、第一介电材料以及第一导电柱。第一介电材料以及第一导电柱贯穿第一基底,且第一导电柱位于第一基底与第一介电材料之间。第二基材包括第二基底、第二介电材料、第三介电材料、第一线路层、第二线路层、第三线路层、导电连接层、导通孔以及开口。第二基底具有彼此相对的第一表面与第二表面。第一线路层与第二线路层分别位于第一表面与第二表面上。第三介电材料位于第二基底的第二表面上。第三线路层位于第三介电材料上。导通孔电性连接第二线路层与第三线路层。开口贯穿第二基底与第三介电材料。导电连接层覆盖开口的内壁且电性连接第一线路层、第二线路层及第三线路层。第二介电材料填满开口。

在根据本发明的实施例的电路板中,上述的第一外部线路层包括第一信号线路与第一接地线路。第二外部线路层包括第二信号线路与第二接地线路。第一信号线路、导通孔结构以及第二信号线路定义出信号路径。第一接地线路、第一导电柱、第一线路层、导电连接层以及第二接地线路定义出接地路径。

在根据本发明的实施例的电路板中,上述的导通孔结构包括贯孔以及导电材料层。贯孔贯穿第一介电材料以及第二介电材料。导电材料层覆盖贯孔的内壁且电性连接第一外部线路层与第二外部线路层。

在根据本发明的实施例的电路板中,上述的导通孔结构还包括介电层,填满贯孔。介电层彼此相对的上表面与下表面分别切齐于第一外部线路层的顶表面与第二外部线路层的底表面。

在根据本发明的实施例的电路板中,上述的导通孔结构还包括介电层,填满贯孔。第一外部线路层与第二外部线路层分别覆盖介电层彼此相对的上表面与下表面。

在根据本发明的实施例的电路板中,上述的第一介电材料的介电损耗与第三介电材料的介电损耗(Dissipation Factor,Df)分别大于0且小于0.006,而第二介电材料的介电损耗大于0且小于0.008。

根据本发明的实施例,电路板的制作方法包括以下步骤。形成多个导电结构以围绕第一介电材料、第二介电材料以及第三介电材料。压合第一介电材料、第二介电材料以及第三介电材料。第二介电材料位于第一介电材料与第三介电材料之间,且第一介电材料的介电常数不同于第二介电材料的介电常数以及第三介电材料的介电常数。导电结构彼此电性连接。形成导通孔结构以至少贯穿第一介电材料与第二介电材料。形成第一外部线路层与第二外部线路层分别于第一介电材料上与第三介电材料上。第一外部线路层、第二外部线路层以及导通孔结构电性连接而定义出信号路径。导电结构电性连接第一外部线路层与第二外部线路层而定义出接地路径,其中接地路径环绕信号路径。

在根据本发明的实施例的电路板的制作方法中,上述的导电结构包括多个第一导电柱、多个第二导电柱、第一线路层、第二线路层以及导电连接层。第一导电柱围绕第一介电材料,而第二导电柱围绕第三介电材料。导电连接层连接第一线路层与第二线路层且围绕第二介电材料。

在根据本发明的实施例的电路板的制作方法中,上述形成导电结构以围绕第一介电材料、第二介电材料以及第三介电材料的步骤包括:提供第一基材。第一基材包括第一基底、第一介电材料以及第一导电柱。第一介电材料以及第一导电柱贯穿第一基底,且第一导电柱位于第一基底与第一介电材料之间。提供第二基材。第二基材包括第二基底、第二介电材料、第一线路层、第二线路层以及导电连接层。第二基底具有彼此相对的第一表面与第二表面以及开口,其中开口贯穿第二基底。第一线路层与第二线路层分别位于第一表面与第二表面上。导电连接层覆盖开口的内壁且电性连接第一线路层与第二线路层。第二介电材料填满开口。提供第三基材。第三基材包括第三基底、第三介电材料以及第二导电柱。第三介电材料以及第二导电柱贯穿第三基底,且第二导电柱位于第三基底与第三介电材料之间。

在根据本发明的实施例的电路板的制作方法中,上述形成导通孔结构以至少贯穿第一介电材料与第二介电材料的步骤包括:形成贯孔,以贯穿第一介电材料、第二介电材料以及第三介电材料。形成导电材料层,以覆盖贯孔的内壁。

在根据本发明的实施例的电路板的制作方法中,上述形成第一外部线路层与第二外部线路层分别于第一介电材料上与第三介电材料上的步骤包括:压合第一介电材料、第二介电材料以及第三介电材料时,同时分别压合第一金属层与第二金属层于第一基材与第三基材上。形成导电材料层时,导电材料层还延伸覆盖于第一金属层与第二金属层上。图案化导电材料层、第一金属层以及第二金属层,而形成第一外部线路层与第二外部线路层。

在根据本发明的实施例的电路板的制作方法中,上述的电路板的制作方法还包括:形成导电材料层之后,且于图案化导电材料层、第一金属层以及第二金属层之前,填充介电层于贯孔内。介电层填满贯孔,且介电层彼此相对的上表面与下表面分别切齐于导电材料层的顶表面与底表面。

在根据本发明的实施例的电路板的制作方法中,上述的电路板的制作方法还包括:于填充介电层于贯孔内之后,且于图案化导电材料层、第一金属层以及第二金属层之前,形成罩盖层于导电材料层上。罩盖层覆盖导电材料层以及介电层的上表面与下表面。图案化罩盖层、导电材料层、第一金属层以及第二金属层,而形成第一外部线路层以及第二外部线路层。

在根据本发明的实施例的电路板的制作方法中,上述的导电结构包括多个第一导电柱、多个第二导电柱、第一线路层、第二线路层、第三线路层以及导电连接层。第一导电柱围绕第一介电材料,而第二导电柱围绕第三介电材料。第二线路层位于第一线路层与第三线路层之间。导电连接层连接第一线路层、第二线路层以及第三线路层且围绕第二介电材料。

在根据本发明的实施例的电路板的制作方法中,上述形成导电结构以围绕第一介电材料、第二介电材料以及第三介电材料的步骤包括:形成第一基材。第一基材包括第一基底、第一介电材料以及第一导电柱。第一介电材料以及第一导电柱贯穿第一基底,且第一导电柱位于第一基底与第一介电材料之间。提供第二基材。第二基材包括第二基底、第三基底、第二介电材料、第三介电材料、第一线路层、第二线路层、第三线路层、导电连接层、第二导电柱以及开口。第二基底具有彼此相对的第一表面与第二表面。第一线路层与第二线路层分别位于第一表面与第二表面上。第三基底与第三介电材料位于第二基底的第二表面上,而第三线路层位于第三基底与第三介电材料上。第二导电柱电性连接第二线路层与第三线路层。开口贯穿第二基底与第三介电材料。导电连接层覆盖开口的内壁且电性连接第一线路层、第二线路层及第三线路层。第二介电材料填满开口。

在根据本发明的实施例的电路板的制作方法中,上述形成导通孔结构以至少贯穿第一介电材料与第二介电材料的步骤包括:形成贯孔,以贯穿第一介电材料以及第二介电材料。形成导电材料层,以覆盖贯孔的内壁。

在根据本发明的实施例的电路板的制作方法中,上述形成第一外部线路层与第二外部线路层分别于第一介电材料上与第三介电材料上的步骤包括:压合第一介电材料、第二介电材料以及第三介电材料时,同时压合金属层于第一基材上。形成导电材料层时,导电材料层还延伸覆盖于金属层与第三线路层上。图案化导电材料层以及金属层,而形成第一外部线路层与第二外部线路层。

在根据本发明的实施例的电路板的制作方法中,上述的电路板的制作方法,还包括:形成导电材料层之后,且于图案化导电材料层与金属层之前,填充介电层于贯孔内。介电层填满贯孔,且介电层彼此相对的上表面与下表面分别切齐于导电材料层的顶表面与底表面。

在根据本发明的实施例的电路板的制作方法中,上述的电路板的制作方法,还包括:于填充介电层于贯孔内之后,且于图案化导电材料层与金属层之前,形成罩盖层于导电材料层上。罩盖层覆盖导电材料层以及介电层的上表面与下表面。图案化罩盖层、导电材料层以及金属层,而形成第一外部线路层以及第二外部线路层。

在根据本发明的实施例的电路板的制作方法中,上述的导电结构包括多个第一导电柱、多个导通孔、第一线路层、第二线路层、第三线路层以及导电连接层。第一导电柱围绕第一介电材料,而导通孔贯穿第三介电材料。第二线路层位于第一线路层与第三线路层之间。导电连接层连接第一线路层、第二线路层以及第三线路层且围绕第二介电材料。

在根据本发明的实施例的电路板的制作方法中,上述形成导电结构以围绕第一介电材料、第二介电材料以及第三介电材料的步骤包括:形成第一基材。第一基材包括第一基底、第一介电材料以及第一导电柱。第一介电材料以及第一导电柱贯穿第一基底,且第一导电柱位于第一基底与第一介电材料之间。形成第二基材。第二基材包括第二基底、第二介电材料、第三介电材料、第一线路层、第二线路层、第三线路层、导电连接层、导通孔以及开口。第二基底具有彼此相对的第一表面与第二表面。第一线路层与第二线路层分别位于第一表面与第二表面上。第三介电材料位于第二基底的第二表面上,而第三线路层位于第三介电材料上。导通孔电性连接第二线路层与第三线路层。开口贯穿第二基底与第三介电材料。导电连接层覆盖开口的内壁且电性连接第一线路层、第二线路层及第三线路层。第二介电材料填满开口。

在根据本发明的实施例的电路板的制作方法中,上述形成导通孔结构以至少贯穿第一介电材料与第二介电材料的步骤包括:形成贯孔,以贯穿第一介电材料以及第二介电材料。形成导电材料层,以覆盖贯孔的内壁。

在根据本发明的实施例的电路板的制作方法中,上述形成第一外部线路层与第二外部线路层分别于第一介电材料上与第三介电材料上的步骤包括:压合第一介电材料、第二介电材料以及第三介电材料时,同时压合金属层于第一基材上。形成导电材料层时,导电材料层还延伸覆盖于金属层与第三线路层上。图案化导电材料层以及金属层,而形成第一外部线路层与第二外部线路层。

在根据本发明的实施例的电路板的制作方法中,上述的电路板的制作方法,还包括:形成导电材料层之后,且于图案化导电材料层与金属层之前,填充介电层于贯孔内。介电层填满贯孔,且介电层彼此相对的上表面与下表面分别切齐于导电材料层的顶表面与底表面。

在根据本发明的实施例的电路板的制作方法中,上述的电路板的制作方法,还包括:于填充介电层于贯孔内之后,且于图案化导电材料层与金属层之前,形成罩盖层于导电材料层上。罩盖层覆盖导电材料层以及介电层的上表面与下表面。图案化罩盖层、导电材料层以及金属层,而形成第一外部线路层以及第二外部线路层。

根据本发明的实施例,电子装置包括电路板以及电子元件。电路板包括第一介电材料、第二介电材料、第三介电材料、第一外部线路层、第二外部线路层、多个导电结构以及导通孔结构。第二介电材料位于第一介电材料与第三介电材料之间,且第一介电材料的介电常数不同于第二介电材料的介电常数以及第三介电材料的介电常数。第一外部线路层配置于第一介电材料上。第二外部线路层配置于第三介电材料上。导通孔结构至少贯穿第一介电材料与第二介电材料,且电性连接至第一外部线路层与第二外部线路层而定义出信号路径。导电结构彼此电性连接且围绕第一介电材料、第二介电材料以及第三介电材料。导电结构电性连接第一外部线路层与第二外部线路层而定义出接地路径。接地路径环绕信号路径。电子元件电性连接电路板。

基于上述,在本发明的电路板的设计中,导通孔结构电性连接至第一外部线路层与第二外部线路层而定义出信号路径,而导电结构彼此电性连接且电性连接第一外部线路层与第二外部线路层而定义出接地路径,其中接地路径环绕信号路径。藉此,可形成良好的高频高速信号回路,且后续在积体电路与天线的应用上,亦可解决同一平面信号干扰的问题,可降低信号能量损失及减少噪音干扰,进而可提升信号传输可靠度。此外,本发明的导通孔结构至少贯穿第一介电材料与第二介电材料,意即在导电通孔结构的周围设置不同介电常数的介电材料,可提高信号传输速率与减少信号传输损失。

附图说明

图1A至图1E是依照本发明的一实施例的一种电路板的制作方法的剖面示意图;

图1F是图1E的电路板的俯视示意图;

图2A至图2B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图;

图3A至图3B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图;

图4A至图4K是依照本发明的另一实施例的另一种电路板的制作方法的剖面示意图;

图5A至图5B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图;

图6A至图6B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图;

图7A至图7L是依照本发明的另一实施例的另一种电路板的制作方法的剖面示意图;

图8A至图8B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图;

图9A至图9B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图;

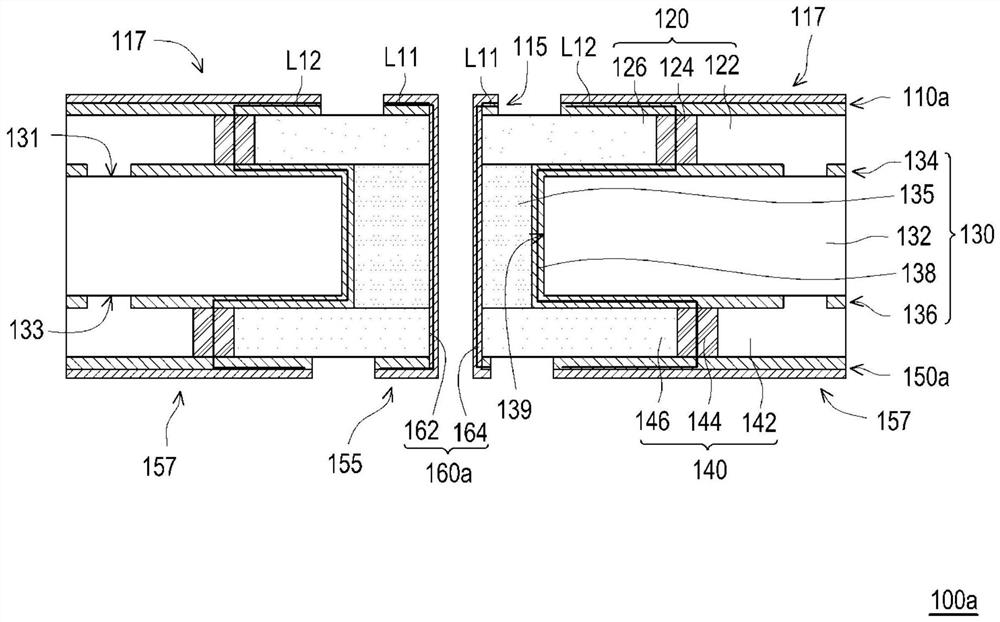

图10A至10C是依照本发明的多个实施例的多种电子装置的剖面示意图。

附图标记说明

10a、10b、10c:电子装置;

100a、100b、100c、200a、200b、200c、300a、300b、300c:电路板;

110:第一金属层;

110a、110b、110c、210a、210b、210c、310a、310b、310c:第一外部线路层;

115、215、315:第一信号线路;

117、217、317:第一接地线路;

120、220、320:第一基材;

122、222、322:第一基底;

124、224、324:第一导电柱;

126、226、326:第一介电材料;

130、230、330:第二基材;

131、S3、S7:第一表面;

132、231、331:第二基底;

133、S4、S8:第二表面;

134、232、332:第一线路层;

135、237、337:第二介电材料;

136、234、334:第二线路层;

138、235、335:导电连接层;

139、H、H’:开口;

140:第三基材;

142、233:第三基底;

144、238:第二导电柱;

146、239、333:第三介电材料;

150:第二金属层;

150a、150b、150c、250a、250b、250c、350a、350b、350c:第二外部线路层;

155、255、355:第二信号线路;

157、257、35:第二接地线路;

160a、240a、240b、340a、340b:导通孔结构;

162、242、342:贯孔;

163、164、243、244、343、344:导电材料层;

166、246、346:介电层;

170、260、360:罩盖层;

236、336:第三线路层;

338:导通孔;

400:电子元件;

410:接垫;

500:连接件;

F1、F3、F5:上表面;

F2、F4、F6:下表面;

L11、L21、L31:信号路径;

L12、L22、L32:接地路径;

M1、M2、M3、M4、M5、M6、210、310:金属层;

S1、S5、S9:顶表面;

S2、S6、S10:底表面;

T:通孔。

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

图1A至图1E是依照本发明的一实施例的一种电路板的制作方法的剖面示意图。图1F是图1E的电路板的俯视示意图。关于本实施例的电路板的制作方法,首先,请参考图1A,提供第一金属层110、第一基材120、第二基材130、第三基材140以及第二金属层150。第一基材120包括第一基底122、第一导电柱124以及第一介电材料126。第一介电材料126以及第一导电柱124贯穿第一基底122,且第一导电柱124位于第一基底122与第一介电材料126之间,其中第一导电柱124围绕第一介电材料126。提供第一基材120的步骤包括先提供第一基底122,其中第一基底122于此时处于B阶段状态,意即尚未完全固化。第一基底122的材质例如是环氧数酯(Epoxy)、铁氟龙(PTFE)、聚苯醚(Polyphenylene Ether,PPE)、聚酰亚胺(Polyimide,PI)、BT树脂(Bismaleimide Triazine,BT)、酚醛树脂(Phenolic Novolac,PN)、碳氢化合物(Hydrocarbon),但不以此为限。接着,可于第一基底122的相对两侧贴附离型膜,其中离型膜的材质如是聚酯聚合物(PET)。接着,对第一基底122进行外型切割(routing),而形成通孔。接着,填入第一介电材料126于通孔内,此时第一介电材料126的相对两侧分别对齐于离型膜。接着,对第一介电材料126进行钻孔程序,而形成通孔,其中钻孔程序例如是雷射钻孔或机械钻孔或冲压(punching),但不以此为限。最后,以印刷(printing)或注入(injection)的方式,于通孔内填充导电胶材,而形成围绕第一介电材料126的第一导电柱124。之后,移除贴附在第一基底122相对两侧的离型膜,而使第一导电柱124与第一介电材料126的相对两表面分别突出于第一基底122的相对两表面,而完成第一基材120的制作。

再者,第二基材130包括第二基底132、第二介电材料135、第一线路层134、第二线路层136以及导电连接层138。第二基底132具有彼此相对的第一表面131与第二表面133以及开口139,其中开口139贯穿第二基底132。第一线路层134与第二线路层136分别位于第一表面131与第二表面133上。导电连接层138覆盖开口139的内壁且电性连接第一线路层134与第二线路层136。第二介电材料135填满开口139,且导电连接层138围绕第二介电材料135。第三基材140包括第三基底142、第二导电柱144以及第三介电材料146。第三介电材料146以及第二导电柱144贯穿第三基底142,且第二导电柱144位于第三基底142与第三介电材料146之间,其中第二导电柱144围绕第三介电材料146。此处,第三基材140的制作方法与第一基材120的制作方法相同,请参考上述第一基材120的制作方法,于此不再赘述。须说明的是,上述的第一导电柱124、第二导电柱144、第一线路层134、第二线路层136以及导电连接层138可视为多个导电结构,而至此已形成围绕第一介电材料126、第二介电材料135以及第三介电材料146的多个导电结构。此处,第一金属层110、第一基材120、第二基材130、第三基材140以及第二金属层150可视为复合式印刷电路板(composite PCB),其中第一金属层110与第二金属层150例如是铜箔层,但不以此为限。

接着,请参考图1B,进行热压合程序,以压合第一金属层110、第一基材120、第二基材130、第三基材140以及第二金属层150。由于是采用热压合的制程,因此此时的第一基材120的第一基底122以及第三基材140的第三基底142会由原来的B阶段状态转变成C阶段状态,意即呈现完全固化状态,而使第一金属层110、第二基材130以及第二金属层150连接至第一基材120与第三基材150上。此时,第二介电材料135位于第一介电材料126与第三介电材料146之间。较佳地,第一介电材料126的介电常数不同于第二介电材料135的介电常数以及第三介电材料146的介电常数。导电结构(即第一导电柱124、第一线路层134、导电连接层138、第二线路层136及第二导电柱144)彼此电性连接且连接至第一金属层110与第二金属层150。

进一步来说,在本实施例中,第一基底122与第三基底142可以使用一般介电材料,其中第一基底122的介电常数与第三基底142的介电常数可分别高于3.6,而第一基底122的介电损耗(Df)与第三基底142的介电损耗则分别低于0.02,藉此提供适当的阻抗匹配。再者,第一介电材料126的介电常数与第三介电材料146的介电常数,较佳地,分别低于3.2,且第一介电材料126的介电损耗(Df)与第三介电材料146的介电损耗分别大于0且小于0.006,藉此除了提供适当的绝缘性与阻抗匹配外,还能降低介电耗损。此外,第二介电材料135的介电常数低于3.4,而第二介电材料135的介电损耗(Df)则大于0且小于0.008,以提供适当的绝缘性与阻抗匹配外,还可降低介电耗损。至此,已完成压合第一介电材料126、第二介电材料135以及第三介电材料146的步骤。

接着,请参考图1C,形成贯孔162,以贯穿第一介电材料126、第二介电材料135以及第三介电材料146。接着,请参考图1D,形成导电材料层163,以覆盖贯孔162的内壁,其中导电材料层163还延伸覆盖于第一金属层110与第二金属层150上。

之后,请同时参考图1D与图1E,图案化导电材料层163、第一金属层110以及第二金属层150,而形成于第一基材120上的第一外部线路层110a、形成于第三基材140上的第二外部线路层150a以及形成贯穿第一介电材料126、第二介电材料135以及第三介电材料146的导通孔结构160a。第一外部线路层110a形成于第一基材120的第一基底122、第一导电柱124以及第一介电材料126上,且电性连接第一导电柱124与导通孔结构160a。第二外部线路层150a形成于第三基材140的第三基底142、第二导电柱144以及第三介电材料146上,且电性连接第二导电柱144与导通孔结构160a。特别地,第一外部线路层110a、第二外部线路层150a以及导通孔结构160a电性连接而定义出信号路径L11。导电结构电性连接第一外部线路层110a与第二外部线路层150a而定义出接地路径L12,其中接地路径L12环绕信号路径L11。至此,已完成电路板100a的制作。

在结构上,请同时参考图1E以及图1F,本实施例的电路板100a包括第一介电材料126、第二介电材料135、第三介电材料146、第一外部线路层110a、第二外部线路层150a、多个导电结构以及导通孔结构160a。第二介电材料135位于第一介电材料126与第三介电材料146之间,且第一介电材料126的介电常数不同于第二介电材料135的介电常数以及第三介电材料146的介电常数。第一外部线路层110a配置于第一介电材料126上。第二外部线路层150a配置于第三介电材料146上。导通孔结构160a贯穿第一介电材料126、第二介电材料135以及第三介电材料146,且电性连接至第一外部线路层110a与第二外部线路层150a而定义出信号路径L11。导通孔结构160a包括贯孔162以及导电材料层164。贯孔162贯穿第一介电材料126、第二介电材料135以及第三介电材料146。导电材料层164覆盖贯孔162的内壁且电性连接第一外部线路层110a与第二外部线路层150a。导电结构包括第一导电柱124、第二导电柱144、第一线路层134、第二线路层136以及导电连接层138,其中导电结构彼此电性连接且围绕第一介电材料126、第二介电材料135以及第三介电材料146。导电结构电性连接第一外部线路层110a与第二外部线路层150a而定义出接地路径L12。接地路径L12环绕信号路径L11。

详细来说,本实施例的电路板100a还包括第一基材120、第二基材130以及第三基材140。第一基材120包括第一基底122、第一介电材料126以及第一导电柱124。第一介电材料126以及第一导电柱124贯穿第一基底122,且第一导电柱124位于第一基底122与第一介电材料126之间,其中第一导电柱124围绕第一介电材料126。第二基材130包括第二基底132、第二介电材料135、第一线路层134、第二线路层136以及导电连接层138。第二基底132具有彼此相对的第一表面131与第二表面133以及开口139,且开口139贯穿第二基底132。第一线路层134与第二线路层136分别位于第一表面131与第二表面133上。导电连接层138覆盖开口139的内壁且电性连接第一线路层134与第二线路层136。第二介电材料135填满开口139,且导电连接层138围绕第二介电材料135。第三基材140包括第三基底142、第三介电材料146以及第二导电柱144。第三介电材料146以及第二导电柱144贯穿第三基底142,且第二导电柱144位于第三基底142与第三介电材料146之间,其中第二导电柱144围绕第三介电材料146。

此外,本实施例的第一外部线路层110a包括第一信号线路115与第一接地线路117。第二外部线路层150a包括第二信号线路155与第二接地线路157。第一信号线路115、导通孔结构160a以及第二信号线路155定义出信号路径L11。第一接地线路117、第一导电柱124、第一线路层134、导电连接层138、第二线路层136、第二导电柱144以及第二接地线路157定义出接地路径L12。由于信号路径L11被接地路径L12所环绕且呈封闭性包围,因此可形成良好的高频高速回路。此外,信号路径L11的两侧分别接地路径L12的两侧位于同一平面上,且由于本实施例的电路板100a具有第一导电柱124及第二导电柱144的设置可将屏蔽缺口补起来,而形成完整的屏蔽,可有效的降低信号能量损失及减少噪音干扰,进而可提升信号传输可靠度。

简言之,本实施例由第一信号线路115、导通孔结构160a以及第二信号线路155所定义出信号路径L11被由第一接地线路117、第一导电柱124、第一线路层134、导电连接层138、第二线路层136、第二导电柱144以及第二接地线路157所定义出接地路径L12环绕包围住。意即,可传输5G等高频高速信号的信号路径L11的周围设置封闭性佳的接地路径L12,藉此可形成良好的高频高速回路,而使得本实施例的电路板100a可具有较佳的信号完整性。此处,所述的高频是指频率大于1GHz;而所述的高速是指资料传输的速度大于100Mbps。再者,一般皆知,高频电路讲求的是传输信号的速度与品质,而影响这两项的主要因素是传输材料的电气特性,即材料介电常数(Dk)与介电损耗(Df)。通过降低基材的介电常数和介电损耗,可有效地缩短信号延迟(Signal Propagation Delay Time),并可提高信号传输速率与减少信号传输损失(Signal Transmission Loss)。

由于本实施例仅在贯孔162的周围设置价格较昂贵的第一介电材料126、第二介电材料135以及第三介电材料146,相较于以往整个基材都采用此介电材料而言,本实施例可有效的可减少介电材料的使用量,可有效地降低成本,并可提高信号传输速率与减少信号传输损失。再者,本实施例所提供的第一基材120、第二基材130以及第三基材140为线路板完成品,而第一金属层110与第二金属层150则属于半成品,且以压合的方式将第一金属层110、第一基材120、第二基材130、第三基材140及第二金属层150整合在一起。导通孔结构160a、第二基材130的导电连接层138及第二介电材料135定义出同轴穿孔(coaxial via),其中第二介电材料135位于导通孔结构160a与导电连接层138之间。相较于现有技术中以压合绝缘层的增层法方式来阻绝同轴穿孔的内部导体层与外部导体层而言,本实施例的电路板100a的制作方法可避免产生阻抗不匹配而影响高频信号的完整性的问题。此外,由于本实施例不是采用压合绝缘层的增层法来增加电路板的层数,因此不会采用导通孔的叠孔设计来导通相邻的结构层。因此,本实施例的电路板100a的制作方法除了可以克服导通孔的能量损耗之外,还可以避免叠孔的热应力可靠度不佳的问题。

在此必须说明的是,下述实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参照前述实施例,下述实施例不再重复赘述。

图2A至图2B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图。请同时参考图1D以及图2A,本实施例的电路板的制作方法与上述的电路板的制作方法相似,两者差异在于:在图1D形成导电材料层163的步骤之后,请参考图2A,进行塞孔(plugging)程序,填充介电层166于贯孔162内,其中介电层166填满贯孔162。较佳地,介电层166彼此相对的上表面F1与下表面F2分别切齐于导电材料层163的顶表面S1与底表面S2。若介电层166高于导电材料层153的顶表面S1与底表面S2,则可选择性地通过研磨的方式,而使介电层166的上表面F1与下表面F2分别切齐于导电材料层163的顶表面S1与底表面S2,藉此维持较佳的平整度。此处,介电层166的材质例如是树脂,可视为塞孔剂,或者是,介电常数高于3.6且介电损耗低于0.05的介电材料。

之后,请同时参考图2A与图2B,进行微影程序,以图案化导电材料层163、第一金属层110以及第二金属层150,而形成第一外部线路层110b与第二外部线路层150b。第一外部线路层110b位于第一基材120的第一基底122上且具有顶表面S1,而第二外部线路层150b位于第三基材140的第三基底142上且具有底表面S2。介电层166彼此相对的上表面F1与下表面F2分别切齐于第一外部线路层110b的顶表面S1与第二外部线路层150b的底表面S2。此处,导通孔结构160b包括贯孔162、导电材料层164以及位于贯孔162内的介电层166。至此,已完成电路板100b的制作。

图3A至图3B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图。请同时参考图2A以及图3A,本实施例的电路板的制作方法与上述的电路板的制作方法相似,两者差异在于:在图2A填充介电层166于贯孔162内的步骤之后,请参考图3A,形成罩盖层170于导电材料层163上。罩盖层170覆盖导电材料层163以及介电层166的上表面F1与下表面F2。此处,罩盖层155的材质例如是铜,但不以此为限。之后,请同时参考图3A与图3B,进行微影程序,以图案化罩盖层170、导电材料层163、第一金属层110以及第二金属层150,而形成第一外部线路层110c以及第二外部线路层150c。第一外部线路层110c与第二外部线路层150c分别覆盖介电层166彼此相对的上表面F1与下表面F2。至此,已完成电路板100c的制作。

图4A至图4K是依照本发明的另一实施例的另一种电路板的制作方法的剖面示意图。先同时参考图1A以及图4G,本实施例的电路板的制作方法与上述的电路板的制作方法相似,两者差异在于:本实施例没有上述的第三基材140,且第二基材230也不同于上述的第二基材130。

详细来说,请先参考图4A,提供第二基底231、金属层M1、第二线路层234、第三基底233、第二导电柱238、第三介电材料239及金属层M2。金属层M1与第二线路层234分别位于第二基底231的相对两侧,其中金属层M1例如是铜箔层,而第二线路层234暴露出第二基底231的部分表面。第三介电材料239贯穿第三基底233,而第二导电柱238贯穿第三介电材料239,其中第二导电柱238与第三介电材料239彼此相对的两表面分别突出于第三基底233相对两表面。第三基底233位于第二基底231与金属层M2之间,其中第三基底233于此时处于B阶段状态,意即尚未完全固化。此处,第三基底233、第二导电柱238以及第三介电材料239的制作方法与上述图1A中的第三基材140的形成方法相同,于此不再赘述。

接着,请参考图4B,进行热压合程序,以压合第二基底231、第三基底233以及金属层M2。由于是采用热压合的制程,因此此时的第三基底233会由原来的B阶段状态转变成C阶段状态,意即呈现完全固化状态,而使第二基底231、第二线路层234以及金属层M2连接至第三基底233上。此时,第二线路层234通过第二导电柱238电性连接金属层M2。

接着,请参考图4C,形成开口H,以贯穿金属层M1、第二基底231、第二线路层234、第三基底233、第三介电材料239以及金属层M2。接着,请参考图4D,形成金属层M3以覆盖开口H的内壁以及金属层M1与金属层M2上。接着,请参考图4E,填充第二介电材料237于开口H内,其中第二介电材料237彼此相对的两表面分别切齐金属层M3。接着,请同时参考图4E与图4F,通过微影制程,以图案化金属层M1、M2、M3,而形成位于第二基底231上的第一线路层232、位于第三基底233上的第三线路层236以及连接第一线路层232及第三线路层236的导电连接层235。至此,已完成第二基材230的制作。

接着,请参考图4G,提供金属层210、第一基材220以及第二基材230。金属层210例如是铜箔层,但不以此为限。第一基材220包括第一基底222、第一介电材料226以及第一导电柱224。第一介电材料226以及第一导电柱224贯穿第一基底222,且第一导电柱224位于第一基底222与第一介电材料226之间,其中第一导电柱224围绕第一介电材料226。此处,第一基材220的形成方式与图1A中的第一基材120的形成方式相同,于此不再赘述。第二基材230包括第二基底231、第三基底233、第二介电材料237、第三介电材料239、第一线路层232、第二线路层234、第三线路层236、导电连接层235、第二导电柱238以及开口H。第二基底231具有彼此相对的第一表面S3与第二表面S4。第一线路层232与第二线路层234分别位于第一表面S3与第二表面S4上,其中第二线路层234位于第一线路层232与第三线路层236之间。第三基底233与第三介电材料239位于第二基底231的第二表面S4上,而第三线路层236位于第三基底233与第三介电材料239上。第二导电柱238电性连接第二线路层234与第三线路层236,其中第二导电柱238围绕第三介电材料239。开口H贯穿第二基底231与第三介电材料239。导电连接层235覆盖开口H的内壁且电性连接第一线路层232、第二线路层234及第三线路层236。第二介电材料237填满开口H,且导电连接层235围绕第二介电材料237。须说明的是,上述的第一导电柱224、第二导电柱238、第一线路层232、第二线路层234、第三线路层236以及导电连接层235可视为多个导电结构,而至此已形成围绕第一介电材料226、第二介电材料237以及第三介电材料239的多个导电结构。此处,金属层210、第一基材220以及第二基材230可视为复合式印刷电路板。

接着,请参考图4H,进行热压合程序,以压合金属层210、第一基材220以及第二基材230。由于是采用热压合的制程,因此此时的第一基材220的第一基底222会由原来的B阶段状态转变成C阶段状态,意即呈现完全固化状态,而使金属层210以及第二基材230连接至第一基材220上。

接着,请参考图4I,形成贯孔242,以贯穿金属层210、第一介电材料226以及第二介电材料237。接着,请参考图4J,形成导电材料层243,以覆盖贯孔242的内壁,其中导电材料层243还延伸覆盖于金属层210与第三线路层236上。

之后,请同时参考图4J与图4K,图案化导电材料层243以及金属层210,而形成于第一基材220上的第一外部线路层210a以及形成于第二基材230上的第二外部线路层250a以及形成贯穿第一介电材料226以及第二介电材料237的导通孔结构240a。第一外部线路层210a形成于第一基材220的第一基底222、第一导电柱224以及第一介电材料226上,且电性连接第一导电柱224与导通孔结构240a。第二外部线路层250a形成于第二基材230的第三线路层236上,且电性连接第三线路层236与导通孔结构240a。特别地,第一外部线路层210a包括第一信号线路215与第一接地线路217。第二外部线路层250a包括第二信号线路255与第二接地线路257。第一信号线路215、导通孔结构240a以及第二信号线路255定义出信号路径L21。第一接地线路217、第一导电柱224、第一线路层232、导电连接层235以及第二接地线路257定义出接地路径L22,其中接地路径L22环绕信号路径L21。至此,已完成电路板200a的制作。

在结构上,请同时参考图1E与图4K,本实施例的电路板200a与上述的电路板100a相似,两者差异在于:在本实施例中,电路板200a无上述的第三基材140,且导通孔结构240a的贯孔242贯穿第一基材220的第一介电材料226以及第二基材230的第二介电材料237,而导通孔结构240a的导电材料层244覆盖贯孔242的内壁且电性连接第一外部线路层210a与第二外部线路层250a。详细来说,电路板200a包括第一外部线路层210a、第一基材220、第二基材230、导通孔结构240a以及第二外部线路层250a。第一基材220包括第一基底222、第一介电材料226以及第一导电柱224。第一介电材料226以及第一导电柱224贯穿第一基底222,且第一导电柱224位于第一基底222与第一介电材料226之间,其中第一导电柱222围绕第一介电材料226。第二基材230包括第二基底231、第三基底233、第二介电材料237、第三介电材料239、第一线路层232、第二线路层234、第三线路层236、导电连接层235、第二导电柱238以及开口H。第二基底231具有彼此相对的第一表面S3与第二表面S4。第一线路层232与第二线路层234分别位于第一表面S3与第二表面S4上。第三基底233与第三介电材料239位于第二基底231的第二表面S4上。第三线路层236位于第三基底233与第三介电材料239上,且第二线路层234位于第一线路层232与第三线路层236之间。第二导电柱238电性连接第二线路层234与第三线路层236,其中第二导电柱238围绕第三介电材料239。开口H贯穿第二基底231与第三介电材料239。导电连接层235覆盖开口H的内壁且电性连接第一线路层232、第二线路层234及第三线路层236。第二介电材料237填满开口H,且导电连接层235围绕第二介电材料237。此处,导电结构包括第一导电柱222、第二导电柱238、第一线路层232、第二线路层234、第三线路层236以及导电连接层235。

简言之,本实施例由第一信号线路215、导通孔结构240a以及第二信号线路255所定义出的信号路径L21被由第一接地线路217、第一导电柱224、第一线路层232、导电连接层235以及第二接地线路257所定义出的接地路径L22环绕包围住。意即,可传输5G等高频高速信号的信号路径L21的周围设置封闭性佳的接地路径L22,藉此可形成良好的高频高速回路,而使得本实施例的电路板200a可具有较佳的信号完整性。此外,导通孔结构240a、第二基材230的导电连接层235及第二介电材料237定义出同轴穿孔(coaxial via),其中第二介电材料237位于导通孔结构240a与导电连接层235之间。相较于现有技术中以压合绝缘层的增层法方式来阻绝同轴穿孔的内部导体层与外部导体层而言,本实施例的电路板200a的制作方法可避免产生阻抗不匹配而影响高频信号的完整性的问题。

图5A至图5B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图。请同时参考图4J以及图5A,本实施例的电路板的制作方法与上述的电路板的制作方法相似,两者差异在于:在4J形成导电材料层243的步骤之后,请参考图5A,进行塞孔(plugging)程序,填充介电层246于贯孔242内,其中介电层246填满贯孔242。较佳地,介电层246彼此相对的上表面F3与下表面F4分别切齐于导电材料层243的顶表面S5与底表面S6。若介电层246高于导电材料层243的顶表面S5与底表面S6,则可选择性地通过研磨的方式,而使介电层246的上表面F3与下表面F4分别切齐于导电材料层243的顶表面S5与底表面S6。此处,介电层246的材质例如是树脂,可视为塞孔剂,或者是,介电常数高于3.6且介电损耗低于0.05的介电材料。

之后,请同时参考图5A与图5B,进行微影程序,以图案化导电材料层243以及金属层210,而形成第一外部线路层210b与第二外部线路层250b。第一外部线路层210b位于第一基材220的第一基底222上且具有顶表面S5,而第二外部线路层250b位于第二基材230的第三线路层236上且具有底表面S6。介电层246彼此相对的上表面F3与下表面F4分别切齐于第一外部线路层210b的顶表面S5与第二外部线路层250b的底表面S6。此处,导通孔结构240b包括贯孔242、导电材料层244以及位于贯孔242内的介电层246。至此,已完成电路板200b的制作。

图6A至图6B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图。请同时参考图5A以及图6A,本实施例的电路板的制作方法与上述的电路板的制作方法相似,两者差异在于:在图5A填充介电层246于贯孔242内的步骤之后,请参考图6A,形成罩盖层260于导电材料层243上。罩盖层260覆盖导电材料层243以及介电层246的上表面F3与下表面F4。此处,罩盖层260的材质例如是铜,但不以此为限。之后,请同时参考图6A与图6B,进行微影程序,以图案化罩盖层260、导电材料层243以及金属层210,而形成第一外部线路层210c以及第二外部线路层250c。第一外部线路层210c与第二外部线路层250c分别覆盖介电层246彼此相对的上表面F3与下表面F4。至此,已完成电路板200c的制作。

图7A至图7L是依照本发明的另一实施例的另一种电路板的制作方法的剖面示意图。先同时参考图1A以及图7H,本实施例的电路板的制作方法与上述的电路板的制作方法相似,两者差异在于:本实施例没有上述的第三基材140,且第二基材330也不同于上述的第二基材130。

详细来说,请先参考图7A,提供第二基底331、金属层M4、第二线路层334、第三介电材料333以及金属层M5。金属层M4与第二线路层334分别位于第二基底331的相对两侧,其中第二线路层334暴露出第二基底331的部分表面。金属层M5配置于第三介电材料333上,且完全覆盖第三介电材料333的一侧表面。第三介电材料333位于第二基底331与金属层M5之间,其中第三介电材料333于此时处于B阶段状态,意即尚未完全固化。接着,请参考图7B,进行热压合程序,以压合第二基底331以及第三介电材料333。由于是采用热压合的制程,因此此时的第三介电材料333会由原来的B阶段状态转变成C阶段状态,意即呈现完全固化状态,而使第二基底331、第二线路层334以及金属层M5连接至第三介电材料333上。

接着,请参考图7C,形成开口H’,以贯穿金属层M4、第二基底331、第二线路层334、第三介电材料333以及金属层M5。接着,请参考图7D,形成通孔T以贯穿金属层M5及第三介电材料333而暴露出部分第二线路层334。接着,请参考图7E,形成金属层M6以覆盖开口H’的内壁、金属层M4与金属层M5上,且填满通孔T。接着,请参考图7F,填充第二介电材料337于开口H’内,其中第二介电材料337彼此相对的两表面分别切齐金属层M6。接着,请同时参考图7F与图7G,通过微影制程,以图案化金属层M4、M5、M6,而形成位于第二基底331上的第一线路层332、位于第三介电材料333上的第三线路层336、连接第一线路层332及第三线路层336的导电连接层335以及连接第二线路层334与第三线路层336的导通孔338。至此,已完成第二基材330的制作。

接着,请参考图7H,提供金属层310、第一基材320以及第二基材330。第一基材320包括第一基底322、第一介电材料326以及第一导电柱324。第一介电材料326以及第一导电柱324贯穿第一基底322,且第一导电柱324位于第一基底322与第一介电材料326之间,其中第一导电柱324围绕第一介电材料326。此处,第一基材320的形成方式与图1A中的第一基材120的形成方式相同,于此不再赘述。第二基材330包括第二基底331、第二介电材料337、第三介电材料333、第一线路层332、第二线路层334、第三线路层336、导电连接层335、导通孔338以及开口H’。第二基底331具有彼此相对的第一表面S7与第二表面S8。第一线路层332与第二线路层334分别位于第一表面S7与第二表面S8上。第二线路层334位于第一线路层332与第三线路层336之间。第三介电材料333位于第二基底331的第二表面S8上,而第三线路层336位于第三介电材料333上。导通孔338贯穿第三介电材料333且电性连接第二线路层334与第三线路层336。开口H’贯穿第二基底331与第三介电材料333。导电连接层335覆盖开口H’的内壁且电性连接第一线路层332、第二线路层334及第三线路层336。第二介电材料337填满开口H’,且导电连接层335围绕第二介电材料333。须说明的是,上述的第一导电柱324、导通孔338、第一线路层332、第二线路层334、第三线路层336以及导电连接层335可视为多个导电结构,而至此已形成围绕第一介电材料326、第二介电材料337以及第三介电材料333的多个导电结构。此处,提供金属层310、第一基材320以及第二基材330可视为复合式印刷电路板。

接着,请参考图7I,进行热压合程序,以压合金属层310、第一基材320以及第二基材330。由于是采用热压合的制程,因此此时的第一基材320的第一基底322会由原来的B阶段状态转变成C阶段状态,意即呈现完全固化状态,而使金属层310以及第二基材330连接至第一基材320上。

接着,请参考图7J,形成贯孔242,以贯穿金属层310、第一介电材料326以及第二介电材料337。接着,请参考图7K,形成导电材料层343,以覆盖贯孔342的内壁,其中导电材料层343还延伸覆盖于金属层310与第三线路层336上。

之后,请同时参考图7K与图7L,图案化导电材料层343以及金属层310,而形成于第一基材320上的第一外部线路层310a以及形成于第二基材330上的第二外部线路层350a以及形成贯穿第一介电材料326以及第二介电材料337的导通孔结构340a。第一外部线路层310a形成于第一基材320的第一基底322、第一导电柱324以及第一介电材料326上,且电性连接第一导电柱324与导通孔结构340a。第二外部线路层350a形成于第二基材330的第三线路层336上,且电性连接第三线路层336与导通孔结构340a。特别地,第一外部线路层310a包括第一信号线路315与第一接地线路317。第二外部线路层350a包括第二信号线路355与第二接地线路357。第一信号线路315、导通孔结构340a以及第二信号线路355定义出信号路径L31。第一接地线路317、第一导电柱324、第一线路层332、导电连接层335以及第二接地线路357定义出接地路径L32,其中接地路径L32环绕信号路径L31。至此,已完成电路板300a的制作。

在结构上,请同时参考图1E与图7L,本实施例的电路板300a与上述的电路板100a相似,两者差异在于:在本实施例中,电路板300a无上述的第三基材140,且导通孔结构340a的贯孔342贯穿第一基材320的第一介电材料326以及第二基材330的第二介电材料337,而导通孔结构340a的导电材料层344覆盖贯孔342的内壁且电性连接第一外部线路层310a与第二外部线路层350a。详细来说,电路板300a包括第一外部线路层310a、第一基材320、第二基材330、导通孔结构340a以及第二外部线路层350a。第一基材320包括第一基底322、第一介电材料326以及第一导电柱324。第一介电材料326以及第一导电柱324贯穿第一基底322,且第一导电柱324位于第一基底322与第一介电材料326之间,其中第一导电柱324围绕第一介电材料326。第二基材330包括第二基底331、第二介电材料337、第三介电材料333、第一线路层332、第二线路层334、第三线路层336、导电连接层335、导通孔338以及开口H’。第二基底331具有彼此相对的第一表面S7与第二表面S8。第一线路层332与第二线路层334分别位于第一表面S7与第二表面S8上。第二线路层334位于第一线路层332与第三线路层336之间。第三介电材料333位于第二基底331的第二表面S8上。第三线路层336位于第三介电材料333上。导通孔338贯穿第三介电材料333且电性连接第二线路层334与第三线路层336。开口H’贯穿第二基底331与第三介电材料333。导电连接层335覆盖开口H’的内壁且电性连接第一线路层332、第二线路层334及第三线路层336。第二介电材料337填满开口H’,且导电连接层335围绕第二介电材料337。此处,导电结构包括第一导电柱324、导通孔338、第一线路层332、第二线路层334、第三线路层336以及导电连接层335。

简言之,本实施例由第一信号线路315、导通孔结构340a以及第二信号线路355所定义出的信号路径L31被由第一接地线路317、第一导电柱324、第一线路层332、导电连接层335以及第二接地线路357所定义出的接地路径L32环绕包围住。意即,可传输5G等高频高速信号的信号路径L31的周围设置封闭性佳的接地路径L32,藉此可形成良好的高频高速回路,而使得本实施例的电路板300a可具有较佳的信号完整性。此外,导通孔结构340a、第二基材330的导电连接层335及第二介电材料337定义出同轴穿孔(coaxial via),其中第二介电材料337位于导通孔结构340a与导电连接层335之间。相较于现有技术中以压合绝缘层的增层法方式来阻绝同轴穿孔的内部导体层与外部导体层而言,本实施例的电路板300a的制作方法可避免产生阻抗不匹配而影响高频信号的完整性的问题。

图8A至图8B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图。请同时参考图7K以及图8A,本实施例的电路板的制作方法与上述的电路板的制作方法相似,两者差异在于:在7K形成导电材料层343的步骤之后,请参考图8A,进行塞孔(plugging)程序,填充介电层346于贯孔342内,其中介电层346填满贯孔342。较佳地,介电层346彼此相对的上表面F5与下表面F6分别切齐于导电材料层343的顶表面S9与底表面S10。若介电层346高于导电材料层343的顶表面S9与底表面S10,则可选择性地通过研磨的方式,而使介电层346的上表面F5与下表面F6分别切齐于导电材料层343的顶表面S9与底表面S10。此处,介电层346的材质例如是树脂,可视为塞孔剂,或者是,介电常数高于3.6且介电损耗低于0.05的介电材料,藉此提供绝缘性与适当的阻抗匹配。

之后,请同时参考图8A与图8B,进行微影程序,以图案化导电材料层343以及金属层310,而形成第一外部线路层310b与第二外部线路层350b。第一外部线路层310b位于第一基材320的第一基底322上且具有顶表面S9,而第二外部线路层350b位于第二基材330的第三线路层336上且具有底表面S10。介电层346彼此相对的上表面F5与下表面F6分别切齐于第一外部线路层310b的顶表面S9与第二外部线路层350b的底表面S10。此处,导通孔结构340b包括贯孔342、导电材料层344以及位于贯孔342内的介电层346。至此,已完成电路板300b的制作。

图9A至图9B是依照本发明的另一实施例的另一种电路板的制作方法的局部步骤的剖面示意图。请同时参考图8A以及图9A,本实施例的电路板的制作方法与上述的电路板的制作方法相似,两者差异在于:在图8A填充介电层346于贯孔342内的步骤之后,请参考图9A,形成罩盖层360于导电材料层343上。罩盖层360覆盖导电材料层343以及介电层346的上表面F5与下表面F6。此处,罩盖层360的材质例如是铜,但不以此为限。之后,请同时参考图9A与图9B,进行微影程序,以图案化罩盖层360、导电材料层343以及金属层310,而形成第一外部线路层310c以及第二外部线路层350c。第一外部线路层310c与第二外部线路层350c分别覆盖介电层346彼此相对的上表面F5与下表面F6。至此,已完成电路板300c的制作。

图10A至10C是依照本发明的多个实施例的多种电子装置的剖面示意图。请先参考图10A,在本实施例中,电子装置10a包括上述例如是图3B的电路板100c以及电子元件400,其中电子元件400电性连接电路板100c,且电子元件400包括多个接垫410。此外,本实施例的电子装置10a还包括多个连接件500,配置于电路板100c的第二外部线路层150c与电子元件400的接垫410之间,其中电子元件400通过连接件500与电路板100c电性连接。此处,连接件500例如是焊球,但不以此为限。在应用上,可在电路板100c相对于电子元件400的另一侧上设置天线结构,并使天线结构与电路板100c的第一外部线路层110c电性连接。在积体电路与天线的应用上,本实施例的电路板100c可解决同一平面信号干扰的问题,可降低信号能量损失及减少噪音干扰,进而可提升信号传输可靠度。

接着,请参考图10B,在本实施例中,电子装置10b包括上述例如是图6B的电路板200c以及电子元件400,其中电子元件400电性连接电路板200c,且电子元件400包括多个接垫410。此外,本实施例的电子装置10b还包括多个连接件500,配置于电路板200c的第二外部线路层250c与电子元件400的接垫410之间,其中电子元件400通过连接件500与电路板200c电性连接。此处,连接件500例如是焊球,但不以此为限。在应用上,可在电路板200c相对于电子元件400的另一侧上设置天线结构,并使天线结构与电路板200c的第一外部线路层210c电性连接。在积体电路与天线的应用上,本实施例的电路板200c可解决同一平面信号干扰的问题,可降低信号能量损失及减少噪音干扰,进而可提升信号传输可靠度。

最后,请参考图10C,在本实施例中,电子装置10c包括上述例如是图9B的电路板300c以及电子元件400,其中电子元件400电性连接电路板300c,且电子元件400包括多个接垫410。此外,本实施例的电子装置10c还包括多个连接件500,配置于电路板300c的第二外部线路层350c与电子元件400的接垫410之间,其中电子元件400通过连接件500与电路板300c电性连接。此处,连接件500例如是焊球,但不以此为限。在应用上,可在电路板300c相对于电子元件400的另一侧上设置天线结构,并使天线结构与电路板300c的第一外部线路层310c电性连接。在积体电路与天线的应用上,本实施例的电路板300c可解决同一平面信号干扰的问题,可降低信号能量损失及减少噪音干扰,进而可提升信号传输可靠度。

综上所述,在本发明的电路板的设计中,导通孔结构电性连接至第一外部线路层与第二外部线路层而定义出信号路径,而导电结构彼此电性连接且电性连接第一外部线路层与第二外部线路层而定义出接地路径,其中接地路径环绕信号路径。藉此,可形成良好的高频高速信号回路,且后续在积体电路与天线的应用上,亦可解决同一平面信号干扰的问题,可降低信号能量损失及减少噪音干扰,进而可提升信号传输可靠度。此外,本发明的导通孔结构至少贯穿第一介电材料与第二介电材料,意即在导电通孔结构的周围设置不同介电常数的介电材料,可提高信号传输速率与减少信号传输损失。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 一种电路板结构、制作方法及电子设备

- 一种电子设备电路板测试装置

- 盖板、显示装置、电子设备及盖板的制作方法

- 壳体、该壳体的制作方法及具有该壳体的电子装置

- 电路板、电路板的制作方法、电路板调试装置及电子设备

- 电路板的制作方法、电路板及电子装置