公共源极平面网格阵列封装

文献发布时间:2023-06-19 10:19:37

技术领域

本发明主要涉及一种半导体封装及其制造方法。更确切地说,本发明涉及一种用于公共源极结构,具有平面网格阵列封装的半导体。

背景技术

在蜂窝电话充电应用中,具有公共源极配置的双向半导体开关通常由集成电路控制器控制,以提供过压保护。常规技术使用双沟道横向双扩散金属氧化物半导体晶体管(LDMOS)结构来提供用于外部电连接的交替漏极接触图案。尽管常规的横向器件技术提供了在单个芯片上集成两个LDMOS的便利,但是由于沟道是横向形成的,因此占用了很大的半导体面积。本发明使用具有三个分离的金属层的第一垂直双扩散金属氧化物半导体场效应晶体管(VDMOSFET)芯片、第二VDMOSFET芯片以及具有三个单独金属层的平面网格阵列,以实现用于外部电连接的交替的漏极接触图案。由于垂直器件的沟道是垂直形成的,因此可以缩小两个芯片总的半导体面积。

在本发明中,两个N-通道VDMOSFET芯片以及一个三层平面网格阵列衬底是共同封装在一个单独的封装中的。第一层是用于晶片接合。第二层是用于漏极走线布线。第三层是用于外部电路连接。

发明内容

本发明提出了一种半导体封装,包括一个平面网格阵列衬底、一个第一VDMOSFET芯片、一个第二VDMOSFET芯片以及一个模塑封装。平面网格阵列衬底包括一个第一金属层、一个第二金属层、一个第三金属层、多个通孔以及树脂。在半导体封装结构底面上的一系列漏极焊盘构成一个交替的漏极接触模块。

本发明还提出了一种半导体封装的制备方法。该方法包括以下步骤:制备一个平面网格阵列衬底;在平面网格阵列衬底上安装一个第一VDMOSFET芯片以及一个第二VDMOSFET芯片;使用引线接合工艺;形成一个模塑封装;并且进行切单工艺。

附图说明

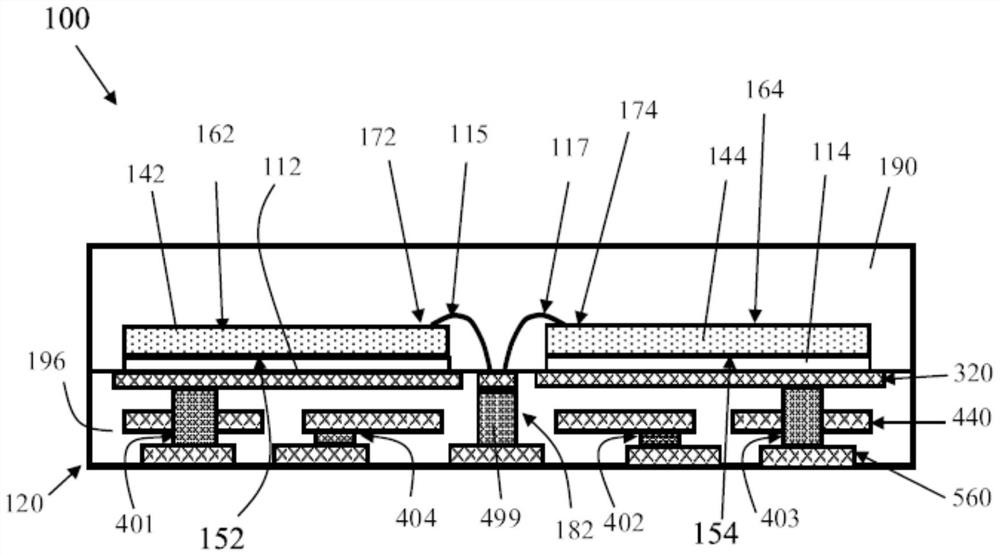

图1A和图1B表示在本发明的示例中,一种半导体封装的剖面图。

图2表示在本发明的示例中,一种具有公共源极结构的电路。

图3表示在本发明的示例中,一种平面网格阵列衬底的第一金属层的俯视图。

图4表示在本发明的示例中,一种平面网格阵列衬底的第二金属层的俯视图。

图5表示在本发明的示例中,一种平面网格阵列衬底的第三金属层的俯视图。

图6表示在本发明的示例中,一种功率半导体封装制备工艺的流程图。

图7、8、9和10表示在本发明的示例中,半导体封装的制备工艺步骤的剖面图。

具体实施方式

在本发明的示例中,图1A表示半导体封装100沿图3中的AA’线的剖面图,图1B表示半导体封装100沿图3中的BB’线的剖面图。半导体封装100包括一个平面网格阵列衬底120、一个第一VDMOSFET芯片142、一个第二VDMOSFET芯片144以及一个模塑封装190。平面网格阵列衬底120包括一个第一金属层320、一个第二金属层440、一个第三金属层560、多个通孔182以及树脂196。树脂196封装了第一金属层320的绝大部分、第二金属层440、第三金属层560的绝大部分以及多个通孔182的绝大部分。模塑封装190封装了第一VDMOSFET芯片142以及第二VDMOSFET芯片144。模塑封装190的底面直接连接到树脂196的顶面上。

在本发明的示例中,第一金属层320的顶面是共面的。第一金属层320的底面是共面的。第二金属层440的顶面是共面的。第二金属层440的底面是共面的。第三金属层560的顶面是共面的。第三金属层560的底面是共面的。第二金属层440位于第一金属层320和第三金属层560之间。在本发明的示例中,第一金属层320与第二金属层440被一部分树脂196分开。第二金属层440与第三金属层560被另一部分树脂196分开。

第一VDMOSFET芯片142包括一个漏极电极152,位于第一VDMOSFET芯片142的底面上。第一VDMOSFET芯片142还包括一个源极电极162以及一个栅极电极172,位于第一VDMOSFT芯片142的顶面上。第二VDMOSFET芯片144包括一个漏极电极154,位于第二VDMOSFET芯片144的底面上。第二VDMOSFET芯片144还包括一个源极电极164以及一个栅极电极174,位于第二VDMOSFET芯片144的顶面上。

图2表示在本发明的示例中,具有公共源极结构的电路200。第一VDMOSFET芯片242和第二VDMOSFET芯片244具有一个公共源极结构。

图3表示在本发明的示例中,平面网格阵列衬底120的第一金属层320的俯视图。第一金属层320包括一个第一金属焊盘352、一个第二金属焊盘354、一个源极焊盘357以及一个栅极焊盘369。参见图1和图3,第一VDMOSFET芯片142的漏极电极152通过第一导电黏合剂112,连接到第一金属层320的第一金属焊盘352上。第二VDMOSFET芯片144的漏极电极154通过第二导电黏合剂114,连接到第一金属层320的第二金属焊盘354上。在一个示例中,第一导电黏合剂112和第二导电黏合剂114都是由一种焊锡膏材料制成。在另一个示例中,第一导电黏合剂112和第二导电黏合剂114都是由一种动力冶金材料制成。在另一个示例中,第一导电黏合剂112和第二导电黏合剂114都是由一种弹性体材料制成。在另一个示例中,第一导电黏合剂112和第二导电黏合剂114都是由一种环氧材料制成。

在本发明的示例中,第一金属焊盘352是一个矩形结构。第二栅极焊盘354是一个矩形结构。源极焊盘357是一个矩形结构。栅极焊盘369是一个矩形结构。

参见图1A、图1B和图3,第一VDMOSFET芯片142的源极电极162通过接合引线111,电子地并机械地连接到第一金属层320的源极焊盘357上。第一VDMOSFET芯片142的栅极电极172通过接合引线115,电子地并机械地连接到第一金属层320的栅极焊盘369上。第二VDMOSFET芯片144的源极电极164通过接合引线113,电子地并机械地连接到第一金属层320的源极焊盘357上。第二VDMOSFET芯片144的栅极电极174通过接合引线117,电子地并机械地连接到第一金属层320的栅极焊盘369上。

图4表示在本发明的示例中,平面网格阵列衬底120的第二金属层440的俯视图。第二层包括第一个字母U型焊盘452以及第二个字母U型焊盘454。第一个字母U型焊盘452包括第一个支脚452A、第二个支脚452B以及第三个支脚452C。第一个支脚452A垂直于第二个支脚452B。第二个支脚452B垂直于第三个支脚452C。第一个支脚454A垂直于第二个支脚454B。第二个支脚454B垂直于第三个支脚454C。第二个字母U型焊盘454的第三个支脚454C,位于第一个字母U型焊盘452的第一个支脚452A和第一个字母U型焊盘452的第三个支脚452C之间。第一个字母U型焊盘452的第三个支脚452C,位于第二个字母U型焊盘454的第一个支脚454A和第二个字母U型焊盘454的第三个支脚454C之间。

在本发明的示例中,第一个字母U型焊盘452的第三个支脚452C的长度,小于第一个字母U型焊盘452的第一个支脚452A的长度,这是因为第一个字母U型焊盘452的第三个支脚452C位于第二个字母U型焊盘454的开口中。第二个字母U型焊盘454的第三个支脚454C的长度,小于第二个字母U型焊盘454的第一个支脚454A的长度,这是因为第二个字母U型焊盘454的第三个支脚454C位于第一个U型焊盘452的开口中。

一个或多个源极通孔497位于第一个字母U型焊盘452的第三个支脚452C和第二个字母U型焊盘454的第三个支脚454C之间。一个或多个栅极通孔499位于第一个字母U型焊盘452的第三个支脚452C和第二个字母U型焊盘454的第三个支脚454C之间。

在本发明的示例中,多个第一通孔401被均匀地隔开,沿第一个字母U型焊盘452的第一个支脚452A分布。多个第二通孔402被均匀地隔开,沿第一个字母U型焊盘452的第三个支脚452C分布。多个第三通孔403被均匀地隔开,沿第二个字母U型焊盘454的第一个支脚454A分布。多个第四通孔404被均匀地隔开,沿第二个字母U型焊盘454的第三个支脚454A分布。在本发明的示例中,没有通孔沿第一个字母U型焊盘452的第二个支脚452B分布。在本发明的示例中,没有通孔沿第二个字母U型焊盘454的第二个支脚454B分布。

在本发明的示例中,第二金属层440组成二阶旋转对称。第一个字母U型焊盘452和第二个字母U型焊盘454(包括多个通孔,用于接收多个第一通孔401、多个第二通孔402、多个第三通孔403以及多个第四通孔404),组成二阶旋转对称。在本发明的示例中,第一个字母U型焊盘452和第二个字母U型焊盘454具有相同的尺寸(相同的表面积以及相同的厚度)。

参见图3、图4和图5,第一金属层320的源极焊盘357以及第三金属层560的源极焊盘597,通过一个或多个源极通孔497相连接。第一金属层320的栅极焊盘369以及第三金属层560的栅极焊盘599,通过一个或多个栅极通孔499相连接。

在本发明的示例中,第三金属层560的源极焊盘597的底面为圆形结构。第三金属层560的栅极焊盘599的底面为圆形结构。

图5表示在本发明的示例中,平面网格阵列衬底120的第三金属层560的仰视图。图5也是半导体封装100的仰视图。第三金属层560包括源极焊盘597、栅极焊盘599、用于连接到第一VDMOSFET 142的漏极电极152(到D1)的第一个漏极焊盘552、用于连接到第二VDMOSFET 144的漏极电极154(到D2)的第二个漏极焊盘554、用于连接到第一VDMOSFET142的漏极电极152(到D1)的第三个漏极焊盘556、以及用于连接到第二VDMOSFET 144的漏极电极154(到D2)的第四个漏极焊盘558。在本发明的示例中,“到D1”和“到D2”遵循交替模式,“到D1”然后是“到D2”,然后是“到D1”,然后是“到D2”。

第二个漏极焊盘554位于第一个漏极焊盘552和第三个漏极焊盘556之间。第三个漏极焊盘556位于第二个漏极焊盘554和第四个漏极焊盘558之间。第三金属层560的源极焊盘597位于第二个漏极焊盘554和第三个漏极焊盘556之间。第三金属层的栅极焊盘599位于第二个漏极焊盘554和第三个漏极焊盘556之间。

在本发明的示例中,第一个漏极焊盘552、第二个漏极焊盘554、第三个漏极焊盘556以及第四个漏极焊盘558具有相同的尺寸(一个相同的表面积以及一个相同的厚度)。第一个漏极焊盘552、第二个漏极焊盘554、第三个漏极焊盘556以及第四个漏极焊盘558中每个漏极焊盘的顶面都是由一个矩形结构512构成,在矩形结构的两个相对端分别具有两个半圆516和518。

参见图1A、图1B、图3、图4和图5,第一金属层320的第一金属焊盘352、第二金属层440的第一个字母U型焊盘452、以及第三金属层560的第一个漏极焊盘552,都通过多个第一通孔401连接起来。第二金属层440的第一个字母U型焊盘452以及第三金属层560的第三个漏极焊盘556,都通过多个第二通孔402连接起来。第一金属层320的第二个金属焊盘354、第二金属层440的第二个字母U型焊盘454以及第三金属层560的第四个漏极焊盘558,都通过多个第三通孔403连接起来。第二金属层440的第二个字母U型焊盘454以及第三金属层560的第二个漏极焊盘554,都通过多个第四通孔404连接起来。

在本发明的示例中,多个第一通孔401垂直于第一金属层320。多个第一通孔401垂直于第二金属层440。多个第一通孔401垂直于第三金属层560。多个第二通孔402垂直于第一金属层320。多个第三通孔403垂直于第一金属层320。多个第四通孔404垂直于第一金属层320。

在本发明的示例中,第一金属层320、第二金属层440以及第三金属层560都是由铜材料制成的。树脂196是由FR4材料或聚酰亚胺材料制成的。多个通孔182为含有铜的导电材料。

图6表示在本发明的示例中,一种功率半导体封装的制备工艺600的流程图。工艺600从区块602开始。为了简便,图10中虚线的右侧(与实线中相应的左侧结构相同)在图7、图8和图9中并没有表示出来。

在区块602中,参见图7,提出了一种平面网格阵列衬底120。平面网格阵列衬底120包括一个第一金属层320、一个第二金属层440、一个第三金属层560、多个通孔182以及树脂196。区块602之后是区块604。

在区块604中,参见图8,第一VDMOSFET芯片142通过第一个导电黏合剂112,连接到第一金属层320中图3所示的第一金属焊盘352上。第二VDMOSFET芯片144通过第二个导电黏合剂114,连接到第一金属层320中图3所示的第二个金属焊盘354上。区块604之后是区块606。

在区块606中,参见图1A、图1B、图3、图4、图5和图9,进行引线接合工艺。第一VDMOSFET芯片142的源极电极162通过接合引线111,电子地并机械地连接到第一金属层320的源极焊盘357上。第一VDMOSFET芯片142的栅极电极172通过接合引线115,电子地并机械地连接到第一金属层320的栅极焊盘369上。第二VDMOSFET芯片144的源极电极164通过接合引线113,电子地并机械地连接到第一金属层320的源极焊盘357上。第二VDMOSFET芯片144的栅极电极174通过接合引线117,电子地并机械地连接到第一金属层320的栅极焊盘369上。在一个示例中,引线接合工艺可以用夹片连接工艺代替。在另一个示例中,引线接合工艺可以用铝带连接工艺代替。区块606之后是区块608。

在区块608中,参见图1A,形成一个模塑封装190。模塑封装190封装了第一VDMOSFET芯片142以及第二VDMOSFET芯片144。模塑封装190的底面直接连接到树脂196的顶面上。区块608之后是区块610。

在区块610中,参见图10,沿1030线进行切单工艺。半导体封装1000与相邻的半导体封装1002(如图中虚线所示)分开。虽然图10中仅表示出了两个半导体封装。但是在同一个切单工艺中分开的半导体封装的数量可以有所不同。在一个示例中,条带尺寸为100毫米乘300毫米。每个半导体封装的尺寸为2毫米乘2毫米。

本领域的普通技术人员可以理解,本发明公开的实施例的修改是可能存在的。例如,多个通孔182的总数可以有所不同。本领域普通技术人员还可以想到其他修改,并且所有这样的修改被认为属于本发明的范围之内,如同权利要求所限定的那样。

- 公共源极平面网格阵列封装

- 源极驱动器、源极驱动器阵列、具有此阵列的驱动电路及显示器