半导体存储器装置和半导体存储器装置的制造方法

文献发布时间:2023-06-19 10:55:46

本申请要求于2019年11月1日在韩国知识产权局提交的韩国专利申请号10-2019-0138550的优先权,其全部公开内容通过引用并入本文。

技术领域

各个实施例一般地涉及半导体存储器装置和半导体存储器装置的制造方法,并且更具体地涉及三维半导体存储器装置和三维半导体存储器装置的制造方法。

背景技术

半导体存储器装置可以包括存储器单元阵列和耦合到存储器单元阵列的外围电路。存储器单元阵列可以包括多个存储器单元阵列,并且外围电路可以被配置为操作外围电路的各种操作。

多个存储器单元可以以三维布置,以便制造三维半导体存储器装置。在三维半导体存储器装置中,存储器单元的栅电极可以耦合到堆叠在衬底之上的多个字线。堆叠在彼此之上的字线的数目可以增加,以增加三维半导体存储器装置的集成度。然而,随着所堆叠的字线的数目增加,制造过程的稳定性和结构稳定性可能劣化。

发明内容

根据本公开的一个实施例,一种半导体存储器装置可以包括:第一堆叠,包括彼此分离的并且被堆叠在衬底上以形成下部阶梯式结构的下部导电图案;支撑柱,穿过第一堆叠并且包括绝缘层;第二堆叠,包括彼此分离的并且被堆叠在第一堆叠上的上部导电图案,上部导电图案包括与下部阶梯式结构和支撑柱不重叠的上部阶梯式结构;沟道结构,穿过第二堆叠和第一堆叠;以及存储器层,包围沟道结构的侧壁。

根据本公开的一个实施例,一种半导体存储器装置可以包括:衬底,包括第一区域和第二区域;第一半导体图案和第二半导体图案,与第一区域重叠并且在与衬底的上表面平行的平面上彼此分离;第一堆叠,包括被分离地堆叠在第一半导体图案和第二半导体图案上以形成下部阶梯式结构的下部导电图案;第一绝缘柱,穿过第一堆叠并且延伸到第一半导体图案中;第二绝缘柱,穿过第一堆叠并且延伸到第二半导体图案中;第二堆叠,包括被分离地堆叠在第一堆叠上的上部导电图案,上部导电图案包括不与下部阶梯式结构以及第一绝缘柱和第二绝缘柱重叠的上部阶梯式结构;沟道结构,穿过第二堆叠和第一堆叠并且延伸到第一半导体图案中;以及存储器层,包围沟道结构的侧壁。

根据本公开的一个实施例,一种制造半导体存储器装置的方法可以包括:在具有下部结构的衬底上形成第一堆叠体;形成穿过第一堆叠体的第一牺牲柱和第二牺牲柱;在第一堆叠体上形成第二堆叠体,以覆盖第一牺牲柱和第二牺牲柱;通过蚀刻第二堆叠体和第一堆叠体以暴露第二牺牲柱来形成阶梯式结构;去除第二牺牲柱;以及形成绝缘层,绝缘层填充第二牺牲柱被去除的区域,并且延伸以覆盖阶梯式结构,其中第一堆叠体和第二堆叠体中的每一个包括彼此交替堆叠的层间绝缘层和牺牲层。

根据本公开的一个实施例,一种制造半导体存储器装置的方法可以包括:在包括下部结构的衬底上形成第一堆叠体;形成穿过第一堆叠体的牺牲柱和支撑柱;在第一堆叠体上形成第二堆叠体,以覆盖牺牲柱和支撑柱;通过蚀刻第二堆叠体和第一堆叠体以暴露支撑柱来形成阶梯式结构;以及形成延伸以覆盖支撑柱和阶梯式结构的绝缘层。

附图说明

图1是根据本公开的实施例的半导体存储器装置的示意图;

图2是图示根据本公开的实施例的半导体存储器装置与单元阵列区域和接触区域重叠的一部分的图;

图3A和图3B是沿图2的线I-I’和II-II’截取的截面图;

图4是根据本公开的实施例的半导体存储器装置的虚设堆叠体的截面图;

图5A是图示根据本公开的实施例的存储器串的图,并且图5B是图示根据本公开的实施例的存储器层的图;

图6是图示根据本公开的实施例的包括下部结构的衬底的图;

图7是图示根据本公开的实施例的制造半导体存储器装置的方法的示意图;

图8A和图8B是图示图7所示的步骤ST1A的实施例的截面图;

图9A、图9B和图9C是图示图7所示的步骤ST3A的实施例的截面图;

图10是图示图7所示的步骤ST5A的实施例的截面图;

图11A和图11B是图示图7所示的步骤ST7A的实施例的截面图;

图12A和图12B是图示图7所示的步骤ST9A的实施例的截面图;

图13A、图13B、图13C、图13D、图13E、图13F、图13G、

图13H和图13I是图示图7所示的步骤ST11A的实施例的截面图;

图14A、图14B和图14C是图示图7所示的步骤ST13A的实施例的截面图;

图15A、图15B、图15C和图15D是图示形成沟道连接图案的过程的截面图;

图16A和图16B是图示形成位线接触插塞、栅极接触插塞、第一上部接触插塞和第二上部接触插塞的过程的截面图;

图17A是图示图7所示的步骤ST7A之后执行的清洗过程的截面图,并且图17B是图示由清洗过程之后执行的后续过程制造的半导体存储器装置的截面图;

图18是图示根据本公开的实施例的制造半导体存储器装置的方法的示意流程图;

图19A、图19B、图19C、图19D和图19E是与根据图18的制造方法的过程相对应的结构的截面图;

图20A、图20B和图20C是图示根据本公开的实施例的制造半导体存储器装置的方法的截面图;

图21是图示根据本公开的实施例的存储器系统的配置的框图;

图22是图示根据本公开的实施例的计算系统的配置的框图。

具体实施方式

本文所公开的具体结构或功能描述仅是例示性的,以用于描述根据本公开的概念的实施例的目的。实施例可以以各种形式实现,并且不应被解释为限于在本文中阐述的特定实施例。

以上术语用于区分一个部件与另一部件,例如,在不脱离根据本公开的概念的范围的情况下,第一部件可以被称为第二部件,并且类似地,第二部件可以被称为第一部件。

本公开的各种实施例提供了能够改进制造过程的稳定性和结构稳定性的半导体存储器装置。

图1是根据本公开的实施例的半导体存储器装置的示意图。

参考图1,半导体存储器装置可以包括布置在图6所示的衬底201上的外围电路和存储器单元阵列,衬底201包括第一区域A1和第二区域A2。第一区域A1可以被限定为与构成存储器单元阵列的栅极堆叠结构GST重叠的区域。第二区域A2可以被限定为不与栅极堆叠结构GST重叠的区域。

尽管未在图1中示出,但是外围电路可以包括行解码器、页缓冲器、控制电路等。行解码器、页缓冲器和控制电路可以包括晶体管TR。外围电路中包括的晶体管TR之中的第一组晶体管可以布置在衬底的第二区域A2上。外围电路中包括的晶体管TR之中的第二组晶体管可以布置在衬底的第一区域A1上,并且与栅极堆叠结构GST重叠。晶体管TR中的每一个的栅电极213可以布置在衬底中限定的有源区ACT上。用作晶体管TR中的每一个的源极和漏极的结JN(如图6所示)可以形成在栅电极213两侧的有源区ACT中。

栅极堆叠结构GST可以通过缝隙SI彼此间隔开。栅极堆叠结构GST中的每一个可以包括单元阵列区域CAR和接触区域CTA。接触区域CTA可以从单元阵列区域CAR延伸。根据一个实施例,栅极堆叠结构GST中的每一个可以包括至少两个单元阵列区域CAR和布置在相邻单元阵列区域CAR之间的接触区域CTA。然而,本公开不限于此。在一个实施例中,栅极堆叠结构GST中的每一个的接触区域CTA可以布置在对应的栅极堆叠结构的边缘处。

接触区域CTA可以包括第一连接区域CA1和第二连接区域CA2。如图2所示,第一连接区域CA1可以与栅极接触插塞GCT重叠。如图2所示,第二连接区域CA2可以与第一接触插塞PCT1重叠。

单元阵列区域CAR可以包括如图5A所示的多个字线WL和如图5A所示的选择线SSL1、SSL2、DSL1和DSL2,其耦合到存储器串。存储器串可以耦合到布置在栅极堆叠结构GST之上的位线BL。

在一个实施例中,第二区域A2上布置的晶体管TR可以与位于与栅极堆叠结构GST相同层级的虚设堆叠体重叠。在一个实施例中,可以省略虚设堆叠体。

图2是图示根据本公开的实施例的半导体存储器装置与单元阵列区域CAR和接触区域CTA重叠的一部分的图。

参考图2,栅极堆叠结构GTS可以由上部绝缘层99覆盖。与单元阵列区域CAR重叠的上部绝缘层99和栅极堆叠结构GST可以被沟道结构CH穿透。栅极堆叠结构GST可以在第一方向D1和第二方向D2上延伸。沟道结构CH可以在与第一方向D1和第二方向D2上延伸的平面正交的第三方向D3上延伸。根据一个实施例,第一方向D1、第二方向D2和第三方向D3可以分别对应于x轴、y轴和z轴。

沟道结构CH中每一个的侧壁可以被存储器层81包围。沟道结构CH可以以矩阵格式布置在与沟道结构CH相对应的栅极堆叠结构GST中。本公开不限于此。在一个实施例中,沟道结构CH可以形成之字形。沟道结构CH中的每一个可以具有各种截面形状,诸如圆形、椭圆形、多边形和矩形。

沟道结构CH可以布置在栅极堆叠结构GST中形成的上部缝隙USI的两侧处。上部缝隙USI和缝隙SI可以在第一方向D1和第三方向D3上延伸。

与接触区域CTA重叠的上部绝缘层99和栅极堆叠结构GST可以被栅极接触插塞GCT和第一接触插塞PCT1穿透。第一支撑柱SP1可以布置在与接触区域CTA重叠的栅极堆叠结构GST中。与接触区域CTA重叠的上部绝缘层99和栅极堆叠结构GST可以被第二支撑柱SP2穿透。

栅极接触插塞GCT、第一支撑柱SP1、第二支撑柱SP2和第一接触插塞PCT1可以具有各种截面形状,诸如圆形、椭圆形、多边形和正方形。栅极接触插塞GCT、第一支撑柱SP1、第二支撑柱SP2和第一接触插塞PCT1的布置不限于图2并且可以进行各种更改。在第一方向D1和第二方向D2上延伸的平面中,第一支撑柱SP1、第二支撑柱SP2和第一接触插塞PCT1中的每一个可以具有比沟道结构CH中的每一个更大的面积。

第一接触插塞PCT1中每一个的侧壁可以被第一绝缘结构IS1包围。第一接触插塞PCT1中的每一个可以通过第一绝缘结构IS1与栅极堆叠结构GST绝缘。

第一支撑柱SP1可以具有比第二支撑柱SP2更简化的结构。根据一个实施例,第一支撑柱SP1中的每一个可以包括单个绝缘材料,并且第二支撑柱SP2中的每一个可以包括与沟道结构CH中的每一个相同的材料。第二支撑柱SP2可以在第三方向D3上延伸,以比第一支撑柱SP1更长。第二支撑柱SP2中每一个的侧壁可以被第一虚设存储器层81d1包围。第一虚设存储器层81d1可以包括与存储器层81相同的材料。

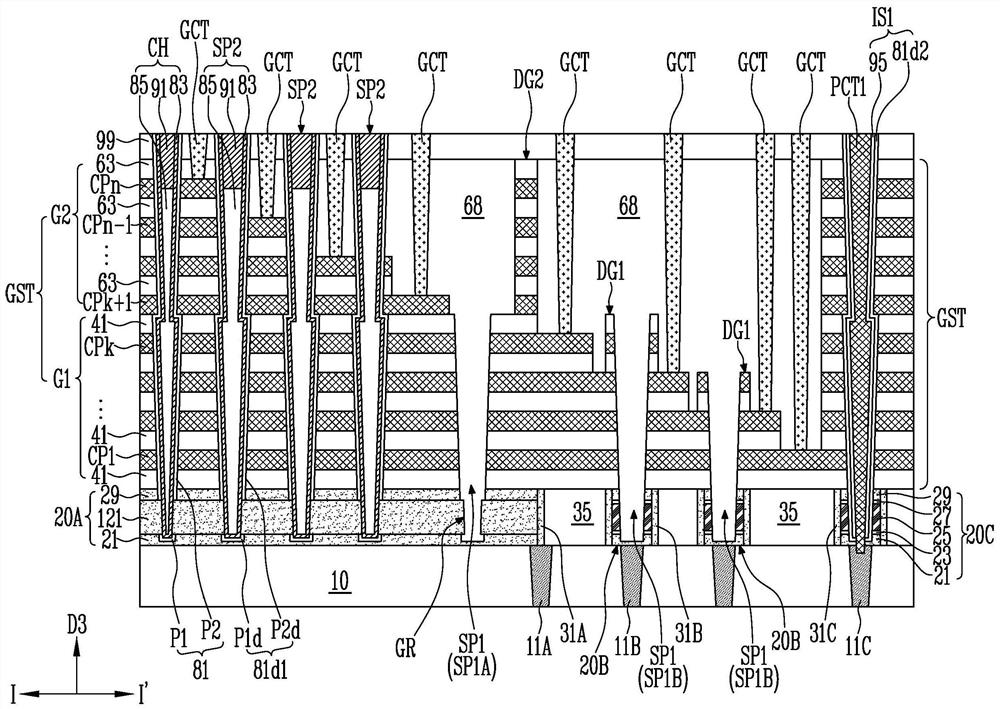

图3A和图3B是沿图2的线I-I’和II-II’截取的截面图。

参考图3A和图3B,栅极堆叠结构GST中的每一个可以包括彼此交替堆叠的层间绝缘层41和63以及导电图案CP1至CPn,其中n是自然数。导电图案CP1至CPn可以通过在导电图案CP1至CPn之间插入的层间绝缘层41和63在第三方向D3上彼此间隔开并且堆叠在彼此之上。导电图案CP1至CPn可以包括各种导电材料,诸如掺杂的半导体层、金属层和导电金属氮化物。导电图案CP1至CPn中的每一个可以包括导电材料或两个类型的导电材料。层间绝缘层41和63中的每一个可以包括氧化硅层。

栅极堆叠结构GST可以通过缝隙SI彼此间隔开。穿过栅极堆叠结构GST中每一个的顶部的上部缝隙USI可以在第三方向D3上比缝隙SI短。根据一个实施例,上部缝隙USI可以足够深,以穿过导电图案CP1至CPn之中位于最上层处的至少第n导电图案CPn。本公开不限于此。在一个实施例中,上部缝隙USI可以穿过依次布置在第n导电图案CPn下方的一个或多个层。导电图案(例如,被上部缝隙USI穿透的第n导电图案和第(n-1)导电图案)可以由选择线分离。如图5A所示,用作字线WL的导电图案可以不被上部缝隙USI穿透。

栅极堆叠结构GST中每一个的侧壁可以由覆盖缝隙SI侧壁的侧壁绝缘层125保护。每个栅极堆叠结构GST可以包括第一堆叠G1和在第一堆叠G1上堆叠的第二堆叠G2。导电图案CP1至CPn可以包括下部导电图案CP1至CPk和上部导电图案CPk+1至CPn,其中k是小于n的自然数。层间绝缘层41和63可以包括第一层间绝缘层41和第二层间绝缘层63。第一堆叠G1可以包括彼此交替堆叠的第一层间绝缘层41和下部导电图案CP1至CPk,并且第二堆叠G2可以包括彼此交替堆叠的上部导电图案CPk+1至CPn和第二层间绝缘层63。

下部导电图案CP1至CPk可以在第三方向D3上彼此分离并且堆叠在彼此上,以形成下部阶梯式结构,并且上部导电图案CPK+1至CPn可以在第三方向D3上彼此分离并且堆叠在彼此上,以形成上部阶梯式结构。下部阶梯式结构和上部阶梯式结构可以与如图2所示的接触区域CTA重叠。下部阶梯式结构可以被第一支撑柱SP1穿透。具有上部阶梯式结构的第二堆叠G2可以不与下部阶梯式结构重叠,以使得第一支撑柱SP1开放。

第一支撑柱SP1中的每一个可以穿过第一堆叠G1并且包括绝缘层68。绝缘层68可以延伸以覆盖第一堆叠G1的下部阶梯式结构和第二堆叠G2的上部阶梯式结构。换言之,第一支撑柱可以是由绝缘层68的一部分形成的绝缘柱。第一支撑柱SP1可以被下部导电图案CP1至CPk中的至少一个包围。

沟道结构CH中的每一个可以穿过第一堆叠G1和第二堆叠G2,并且通过存储器层81来与下部导电图案CP1至CPk和上部导电图案CPk+1至CPn中的每一个分离。第二支撑柱SP2中的每一个可以穿过第一堆叠G1和第二堆叠G2,并且通过第一虚设存储器层81d1来与下部导电图案CP1至CPk和上部导电图案CPk+1至CPn中的每一个分离。

第二支撑柱SP2中的每一个可以包括与沟道结构CH中的每一个相同的材料。根据一个实施例,沟道结构CH和第二支撑柱SP2中的每一个可以包括沟道层83、芯绝缘图案85和覆盖图案91。沟道层83可以形成在存储器层81或第一虚设存储器层81d1上,并且可以包括半导体材料。在一个实施例中,沟道层83可以包括硅。沟道结构CH中每一个的沟道层83可以用作存储器串的沟道。芯绝缘图案85和覆盖图案91可以填充沟道层83的中心区域。芯绝缘图案85可以包括氧化物。覆盖图案91可以布置在芯绝缘图案85上并且包括由沟道层83的顶端包围的侧壁。覆盖图案91可以包括掺杂的半导体层,包括n型杂质和p型杂质中的至少一个。根据一个实施例,可以省略芯绝缘图案85,并且沟道层83可以填充存储器层81或第一虚设存储器层81d1的中心区域。

第一接触插塞PCT1可以穿过第二堆叠G2和第一堆叠G1。包围第一接触插塞PCT1中的每一个的第一绝缘结构IS1可以包括第二虚设存储器层81d2,第二虚设存储器层81d2包括与存储器层81相同的材料。换言之,第二虚设存储器层81d2可以包围对应的第一接触插塞PCT1的侧壁并且在第一接触插塞PCT1和栅极堆叠结构GST之间延伸。第一绝缘结构IS1可以进一步包括布置在第二虚设存储器层81d2和对应的第一接触插塞PCT1之间的氧化物层95。

沟道结构CH、第二支撑柱SP2和第一接触插塞PCT1可以形成在穿过栅极堆叠结构GST的孔中。每个孔可以被配置为使得穿过第一堆叠G1的下部孔和穿过第二堆叠G2的上部孔彼此耦合。与形成穿过第一堆叠G1和第二堆叠G2的长孔的蚀刻过程相比,形成下部孔和上部孔中的每一个的蚀刻过程可以更容易制造。因此,本公开可以增加制造过程的稳定性。

下部导电图案CP1至CPk和上部导电图案CPk+1至CPn可以耦合到栅极接触插塞GCT。栅极接触插塞GCT可以耦合到形成下部阶梯式结构的下部导电图案CP1至CPk中的一些以及形成上部阶梯式结构的上部导电图案CPk+1至CPn中的一些。栅极接触插塞GCT可以在第三方向D3上延伸。

第一虚设栅极堆叠结构DGl和第二虚设栅极堆叠结构DG2可以与第一堆叠Gl的下部阶梯式结构重叠。第一虚设栅极堆叠结构DG1中的每一个可以被布置在与第一堆叠G1的下部导电图案CP1至CPk和第一层间绝缘层41中的一些相同的层级中。第一虚设栅极堆叠结构DG1中的每一个可以被第一支撑柱SP1穿透。第二虚设栅极堆叠结构DG2可以包括与第二堆叠G2的第二层间绝缘层63和上部导电图案CPk+1至CPn相同的材料,并且可以布置在与第二堆叠G2相同的层级中。

由下部阶梯式结构和上部阶梯式结构限定的梯级可以由绝缘层68减轻。绝缘层68和栅极堆叠结构GTS可以由上部绝缘层99覆盖。沟道结构CH、第二支撑柱SP2、栅极接触插塞GCT和第一接触插塞PCT1可以延伸穿过上部绝缘层99。

栅极堆叠结构GST可以布置在由间隙填充绝缘层35分离的半导体图案20A至20C上。半导体图案20A至20C可以包括与第一堆叠G1重叠的第一半导体图案20A、第二半导体图案20B和第三半导体图案图20C。

在一个实施例中,第一半导体图案20A至第三半导体图案20C中的每一个可以包括第一半导体层21以及与第一半导体层21重叠的第二半导体层29。在一个实施例中,第二半导体层29可以被省略。第一半导体图案20A可以包括设置在第一半导体层21和第二半导体层29之间的沟道连接图案121。第二半导体图案20B和第三半导体图案20C中的每一个可以包括设置在第一半导体层21和第二半导体层29之间的牺牲堆叠。牺牲堆叠可以包括依次堆叠在第一半导体层21上的第一保护层23、牺牲层25和第二保护层27。

第一半导体层21和沟道连接图案121中的每一个可以包括n型或p型杂质。根据一个实施例,对于使用栅极感应的漏极泄漏(GIDL)电流执行擦除操作的GIDL擦除方法,沟道连接图案121和第一半导体层21可以包括n型杂质。根据一个实施例,对于通过提供孔来执行擦除操作的阱擦除方法,沟道连接图案121和第一半导体层21可以包括p型杂质。第二半导体层29可以是未掺杂的半导体层,或者可以是包括与第一半导体层21和沟道连接图案121相同类型的杂质的掺杂半导体层。

牺牲层25可以包括具有与第一保护层23和第二保护层27不同的蚀刻速率的材料,从而实现选择性蚀刻。在一个实施例中,牺牲层25可以包括未掺杂的硅层。第一保护层23和第二保护层27中的每一个可以包括氧化物层。

第一半导体图案20A可以延伸以与缝隙SI和沟道结构CH重叠。第一半导体图案20A可以延伸以与第二支撑柱SP2重叠。

沟道结构CH和第二支撑柱SP2可以延伸到第一半导体图案20A中。根据一个实施例,沟道结构CH和第二支撑柱SP2可以延伸到第一半导体图案20A的第一半导体层21中。以这种方式,第一半导体图案20A的第一半导体层21可以包围沟道结构CH中每一个的下部、第二支撑柱SP2中每一个的下部、存储器层81的下部以及第一虚设存储器层81d1的下部。

存储器层81可以被沟道连接图案121穿透,以被分离为第一存储器图案Pl和第二存储器图案P2。第一存储器图案P1可以布置在对应的沟道结构CH和第一半导体图案20A的第一半导体层21之间。第二存储器图案P2可以布置在对应的沟道结构CH和栅极堆叠结构GST之间。第一虚设存储器层81d1可以被沟道连接图案121穿透,以被分离为第一虚设图案P1d和第二虚设图案P2d。第一虚设图案P1d可以布置在对应的第二支撑柱SP2与第一半导体图案20A的第一半导体层21之间。第二虚设图案P2d可以布置在对应的第二支撑柱SP2和栅极堆叠结构GST之间。沟道连接图案121可以延伸以包围沟道结构CH和第二支撑柱SP2,并且穿透存储器层81和第一虚设存储器层81d1以接触沟道结构CH中的每一个的沟道层83和第二支撑柱SP2。

第一支撑柱SP1可以分别包括与第一半导体图案20A重叠的至少一个绝缘柱SP1A和与第二半导体图案20B重叠的第二绝缘柱SP1B。

第一绝缘柱SP1A可以穿过第二半导体层29和第一半导体图案20A的沟道连接图案121,并且可以延伸到第一半导体图案20A的第一半导体层21中。由沟道连接图案121包围的第一绝缘柱SP1A的侧壁可以包括凹槽GR,沟道连接图案121插入到凹槽GR中。

第二半导体图案20B可以彼此间隔开。第二半导体图案20B可以与第一半导体图案20A分离。第二半导体图案20B可以布置在第一堆叠G1的下部阶梯式结构下方。第二绝缘柱SP1B中的每一个可以穿透对应的第二半导体图案20B的第二半导体层29、第二保护层27、牺牲层25和第一保护层23,并且可以延伸到对应的第二半导体图案20B的第一半导体层21中。半导体图案20B中的每一个可以具有比与其对应的第二绝缘柱SP1B更大的宽度。

第三半导体图案20C可以与第一半导体图案20A和第二半导体图案20B间隔开,并且可以被第一接触插塞PCTl穿透。第三半导体图案20C可以具有比第一接触插塞PCT1更大的宽度。第三半导体图案20C的第一半导体层21、第一保护层23、牺牲层25、第二保护层27和第二半导体层29可以包围第一接触插塞PCT1。第一接触插塞PCT1可以穿透第一绝缘结构IS1并且延伸得比第一绝缘结构IS1更长。

第一垂直掺杂半导体图案31A可以形成在第一半导体图案20A的侧壁上,第二垂直掺杂半导体图案31B可以形成在第二半导体图案20B中每一个的侧壁上,并且第三垂直掺杂半导体图案31C可以形成在第三半导体图案20C的侧壁上。第一垂直掺杂半导体图案31A至第三垂直掺杂半导体图案31C可以包括n型或p型杂质。根据一个实施例,第一垂直掺杂半导体图案31A至第三垂直掺杂半导体图案31C可以包括与第一半导体层21相同类型的杂质。

第一半导体图案20A至第三半导体图案20C可以布置在被下部接触插塞11A、11B和11C穿透的下部绝缘层10上。下部接触插塞11A、11B和11C可以包括第一下部接触插塞11A、第二下部接触插塞11B和第三下部接触插塞11C。第一下部接触插塞11A可以被耦合到第一半导体图案20A,第二下部接触插塞11B可以被分别耦合到第二半导体图案20B,并且第三下部接触插塞11C可以被耦合到第三半导体图案20C。

第一半导体图案20A和第一垂直掺杂半导体图案31A可以与第一下部接触插塞11A重叠。第二半导体图案20B中的每一个可以与对应的第二下部接触插塞11B重叠。第三半导体图案20C和第一接触插塞PCT1可以与第三下部接触插塞11C重叠。第一接触插塞PCT1可以穿过第三半导体图案20C以接触第三下部接触插塞11C。

图4是根据本公开的实施例的半导体存储器装置的虚设堆叠体DST的截面图。虚设堆叠体DST可以与如图1所示的第二区域A2重叠。

参考图4,参考图3A和图3B描述的下部绝缘层10和间隙填充绝缘层35可以延伸以与如图1所示的第二区域A2重叠。

穿过下部绝缘层10的下部接触插塞可以进一步包括与如图1所示的第二区域A2重叠的第四下部接触插塞11D。通过间隙填充绝缘层35彼此分离的半导体图案可以进一步包括与第四下部接触插塞11D重叠的第四半导体图案20D。

第四半导体图案20D可以包括与如图3A所示的第二半导体图案20B和第三半导体图案20C相同的材料。换言之,第四半导体图案20D可以包括顺序地堆叠在彼此上的第一半导体层21、第一保护层23、牺牲层25、第二保护层27和第二半导体层29。第四半导体图案20D可以与第四下部接触插塞11D重叠。第四垂直掺杂半导体图案31D可以形成在第四半导体图案20D的侧壁上。第四垂直掺杂半导体图案31D可以包括与第一半导体层21相同类型的杂质。

第四半导体图案20D和第四垂直掺杂半导体图案31D可以被虚设堆叠体DST覆盖。虚设堆叠体DST可以包括在第四半导体图案20D和第四垂直掺杂半导体图案31D上交替堆叠的虚设层间绝缘层41d和63d以及牺牲层43和61。虚设层间绝缘层41d和63d可以包括与参考图3A和图3B描述的层间绝缘层41和63相同的材料,并且可以位于与层间绝缘层41和63相同的层级中。牺牲层43和61可以布置在与参考图3A和图3B描述的导电图案CP1至CPn相同的层级处。牺牲层43和61可以包括具有与虚设层间绝缘层41d和63d不同的蚀刻速率的材料,以实现选择性蚀刻。在一个实施例中,牺牲层43和61中的每一个可以包括氮化物层。

虚设堆叠体DST和第四半导体图案20D可以被第二接触插塞PCT2穿透。第二接触插塞PCT2可以延伸以接触第四下部接触插塞11D。

第二接触插塞PCT2的侧壁可以被第二绝缘结构IS2包围。第二绝缘结构IS2可以包括与参考图3A描述的第一绝缘结构IS1相同的材料。根据一个实施例,第二绝缘结构IS2可以包括具有与如图3A和图3B所示的存储器层81相同的材料的第三虚设存储器层81d3、以及布置在第三虚设存储器层81d3和第二接触插塞PCT2之间的氧化物层95。第三虚设存储器层81d3和氧化物层95可以延伸穿过虚设堆叠体DST。

如参考图3A至图3B所述的上部绝缘层99可以延伸以覆盖虚设堆叠体DST并且被第二接触插塞PCT2和第二绝缘结构IS2穿透。第四半导体图案20D可以具有比第二接触插塞PCT2更大的宽度。

如图3A、图3B和图4所示的第一下部接触插塞11A至第四下部接触插塞11D以及第一接触插塞PCT1和第二接触插塞PCT2可以包括能够传递电信号的各种导电材料。

图5A是图示根据本公开的实施例的存储器串的图,并且图5B是图示根据本公开的实施例的存储器层的图。

参考图5A,存储器串可以耦合到多个字线WL和选择线SSL1、SSL2、DSL1和DSL2。选择线SSL1、SSL2、DSL1和DSL2可以包括源极选择线SSL1和SSL2的至少一个层以及漏极选择线DSL1和DSL2的至少一个层。源极选择线SSL1和SSL2可以耦合至源极选择晶体管的栅电极。漏极选择线DSL1和DSL2可以耦合到漏极选择晶体管的栅电极。字线WL可以耦合到存储器单元的栅电极。

源极选择线SSL1和SSL2、字线WL和漏极选择线DSL1和DSL2可以包括参考图3A和图3B所述的导电图案CP1至CPn。与第一半导体图案20A相邻设置的第一导电图案CP1或依次堆叠并与第一半导体图案20A相邻设置的至少两个导电图案可以用作源极选择线。在一个实施例中,源极选择线SSL1和SSL2可以包括由第一导电图案CP1形成的第一选择线SSL1和由第二导电图案CP2形成的第二选择线SSL2。位于距第一半导体图案20A最远的第n导电图案CPn或第n导电图案CPn和依次布置在第n导电图案CPn下方的至少一个导电图案层可以用作漏极选择线。在一个实施例中,漏极选择线DSL1和DSL2可以包括由第n导电图案CPn形成的第一漏极选择线DSL1和由第(n-1)导电图案CPn-1(位于第n导电图案CPn下方)形成的第二漏极选择线DSL2。设置在彼此相邻的第二漏极选择线DSL2与第二源极选择线SSL2之间的导电图案可以用作字线WL。

根据上述结构,漏极选择晶体管可以形成在漏极选择线DSL1和DSL2中的每一个与沟道结构CH之间的交叉处。源极选择晶体管可以形成在源极选择线SSL1和SSL2中的每一个与沟道结构CH之间的交叉处。存储器单元可以形成在字线WL和沟道结构CH之间的交叉处。存储器单元可以通过沟道结构CH的沟道层83串联耦合在源极选择晶体管和漏极选择晶体管之间。源极选择晶体管可以通过沟道层83耦合到第一半导体图案20A的沟道连接图案121。沟道结构CH的覆盖图案91可以用作漏极选择晶体管的结。

存储器层81的第一存储器图案Pl可以在第一半导体图案20A的第一半导体层21和沟道结构CH之间延伸。存储器层81的第二存储器图案P2可以在第一半导体图案20A的第二半导体层29和沟道结构CH之间延伸。如图5B所示,存储器层81的第一存储器图案P1和第二存储器图案P2中的每一个可以包括隧道绝缘层TI、数据存储层DL和阻挡绝缘层BI。

图5B是图示包围沟道层83的存储器层81的截面图。

参考图5B,存储器层81的中心区域可以填充有沟道层83、芯绝缘图案85和覆盖图案91。存储器层81的隧道绝缘层TI可以包围沟道层83,存储器层81的数据存储层DL的可以包围隧道绝缘层TI,并且存储器层81的阻挡绝缘层BI可以包围数据存储层DL。

数据存储层DL可以包括能够使用Fowler-Nordheim隧穿来存储变化的数据的材料层。数据存储层DL可以包括各种材料。在一个实施例中,电荷陷阱层可以包括氮化物层以用作电荷陷阱层。本公开不限于此。在一个实施例中,数据存储层DL可以包括相变材料、纳米点等。阻挡绝缘层BI可以包括能够阻挡电荷的氧化物层。隧道绝缘层可以包括能够进行电荷隧穿的氧化硅层。

如图3A所示的第一虚设存储器层81d1和第二虚设存储器层81d2以及如图4所示的第三虚设存储器层81d3可以分别包括与如上所述的隧道绝缘层TI、数据存储层DL和阻挡绝缘层BI相同的材料层。

图6是图示根据本公开的实施例的包括下部结构LS的衬底201的图。

参考图6,衬底201可以是半导体层。例如,衬底201可以是体硅衬底、绝缘体上硅衬底、锗衬底、绝缘体上锗衬底、硅锗衬底或通过选择性外延生长方法形成的外延层。

下部结构LS可以包括形成在衬底201中的隔离层203、外围电路的晶体管TR、放电杂质区域DCI、互连结构221以及参考图3A和图4所述的第一下部接触插塞11A至第四下部接触插塞11D。参考图3A和图4所述的第一半导体图案20A至第四半导体图案20D可以位于下部结构LS上,或者可以在与衬底201的顶表面平行的平面中彼此分离。

隔离层203可以在衬底201中划分有源区域ACT1和ACT2。有源区域ACT1和ACT2可以包括第一有源区域ACT1和第二有源区域ACT2。晶体管TR可以布置在第一有源区域ACT1上,并且放电杂质区域DCI可以布置在第二有源区域ACT2中。

互连结构221可以连接到晶体管TR和放电杂质区域DCI。放电杂质区域DCI和晶体管TR可以由绝缘层堆叠体220覆盖,绝缘层堆叠体220具有堆叠在彼此上的两个或更多个绝缘层。互连结构221可以穿过绝缘层堆叠体220。

第一半导体图案20A可以通过与第一半导体图案20A连接的第一下部接触插塞11A以及与第一下部接触插塞11A相对应的互连结构221来连接到放电杂质区域DCI。半导体图案20B中的每一个可以通过与半导体图案20B中的每一个连接的第二下部接触插塞11B以及与第二下部接触插塞11B相对应的互连结构221来连接到放电杂质区域DCI。可以提供放电杂质区域DCI以便使第一半导体图案20A和第二半导体图案20B中累积的电荷放电。

晶体管TR中的每一个可以包括栅极绝缘层211、栅电极213和结JN。晶体管TR中每一个的栅极绝缘层211和栅电极213可以堆叠在与其对应的第一有源区域ACT1上。可以通过将n型或p型杂质注入到栅电极213的两侧上突出的第一有源区域ACT1中来形成晶体管TR中每一个的结JN。

第一接触插塞PCT1可以通过与第一接触插塞PCT1连接的第三下部接触插塞11C以及与第三下部接触插塞11C相对应的互连结构221来连接到与第一接触插塞PCT1相对应的晶体管TR。第二接触插塞PCT2可以通过与第二接触插塞PCT2连接的第四下部接触插塞11D以及与第四下部接触插塞11D相对应的互连结构221来连接到与第二接触插塞PCT2相对应的晶体管TR。

图7是图示根据本公开的实施例的制造半导体存储器装置的方法的示意性流程图。

参考图7,制造半导体存储器装置的方法可以包括:形成预备结构的步骤ST1A;形成被牺牲柱穿透的第一堆叠体的步骤ST3A;形成第二堆叠体的步骤ST5A;形成阶梯式结构的步骤ST7A;形成第一支撑柱的步骤ST9A;形成第二支撑柱和接触插塞的步骤ST11A;以及形成导电图案的步骤ST13A。

步骤ST1A可以在形成包括以上参考图6所述的下部结构LS的衬底201之后执行。换言之,预备结构可以形成在包括如上面参考图6所述的下部结构LS的衬底201上。

在下文中,参考图8A和图8B、图9A至图9C、图10、图11A和图11B、图12A和图12B、图13A至图13I、图14A至图14C、图15A至图15D以及图16A和图16B来描述根据一个实施例的制造半导体存储器装置的方法。下面的图是图示根据制造过程在如图1所示的衬底的第一区域A1和第二区域A2上形成的结构的截面图。根据制造过程在第一区域A1上形成的结构的截面图是沿图2的线I-I’或II-II’截取的。

图8A和图8B是图示图7所示的步骤ST1A的一个实施例的截面图。步骤ST1A可以包括形成半导体图案320A1至320D和形成垂直掺杂半导体图案331A至331D。

参考图8A,形成半导体图案320A1至320D可以包括在包括下部结构300的衬底上依次堆叠第一半导体层321、牺牲堆叠体305和第二半导体层329,以及蚀刻第一半导体层321、牺牲堆叠体305和第二半导体层329。

下部结构300可以包括被第一下部接触插塞311A至第四下部接触插塞311D穿透的下部绝缘层301。如上面参考图6所述,第一下部接触插塞311A至第四下部接触插塞311D可以分别对应于第一下部接触插塞11A至第四下部接触插塞11D。尽管下部结构300示出了如参考图6所述的下部结构LS的一部分,但是半导体图案320A1至320D可以形成在包括如图6所示的下部结构LS的衬底201上。

半导体图案320A1至320D可以包括与第一下部接触插塞311A重叠的预备第一半导体图案320A1、与第二下部接触插塞311B重叠的第二半导体图案320B、与第三下部接触插塞311C重叠的第三半导体图案320C以及与第四下部接触插塞311D重叠的第四半导体图案320D。预备第一半导体图案320A1的边缘可以与第一下部接触插塞311A重叠。第二半导体图案320B中的每一个可以具有比对应的第二下部接触插塞311B更大的宽度,并且在对应的第二下部接触插塞311B的两侧上突出。第三半导体图案320C可以具有比第三下部接触插塞311C更大的宽度,并且在第三下部接触插塞311C的两侧上突出。第四半导体图案320D可以具有比第四下部接触插塞311D更大的宽度,并且在第四下部接触插塞311D的两侧上突出。预备第一半导体图案320A1、第二半导体图案320B和第三半导体图案320C可以布置在如参考图1所述的衬底的第一区域A1上。第四半导体图案320D可以布置在衬底的第二区域A2上。

第一半导体层321可以包括n型或p型杂质。牺牲堆叠体305可以包括顺序堆叠在彼此上的第一保护层323、牺牲层325和第二保护层327。牺牲层325可以包括具有与第一保护层323和第二保护层327不同的蚀刻速率的材料,以实现选择性蚀刻。第一保护层323和第二保护层327可以包括能够在蚀刻牺牲层325时保护第一半导体层321和第二半导体层329的材料。在一个实施例中,牺牲层325可以包括未掺杂的硅层。第一保护层323和第二保护层327中的每一个可以包括氧化物层。第二半导体层329可以包括未掺杂的半导体层或包括与第一半导体层321相同的杂质的掺杂半导体层。在一个实施例中,第一保护层323、第二保护层327和第二半导体层329中的至少一个可以省略。

参考图8B,步骤ST1A可以包括在预备第一半导体图案320A1和第二半导体图案320B至第四半导体图案320D的侧壁上形成垂直掺杂的半导体图案331A至331D。垂直掺杂的半导体图案331A至331D可以包括在预备第一半导体图案320A1的侧壁上形成的第一垂直掺杂的半导体图案331A、在第二半导体图案320B中每一个的侧壁上形成的第二垂直掺杂的半导体图案331B、在第三半导体图案320C的侧壁上形成的第三垂直掺杂的半导体图案331C以及在第四半导体图案320D的侧壁上形成的第四垂直掺杂的半导体图案331D。第一垂直掺杂的半导体图案331A至第四垂直掺杂的半导体图案331D可以包括与如图8A所述的第一半导体层321相同的杂质。

步骤ST1A可以包括利用间隙填充绝缘层335填充预备第一半导体图案320A1、第二半导体图案320B、第三半导体图案320C和第四半导体图案320D之间的间隙。

通过参考图8A和图8B描述的上述过程,可以在下部结构300上提供预备结果,预备结构包括通过间隙填充绝缘层335彼此分离的预备半导体图案320A1和第二半导体图案320B至第四半导体图案320D。

图9A至图9C是图示图7所示的步骤ST3A的实施例的截面图。

参考图9A,步骤ST3A可以包括在预备结构上形成第一堆叠体340。第一堆叠体340可以包括彼此交替堆叠的第一层间绝缘层341和第一牺牲层343。第一层间绝缘层341和第一牺牲层343可以延伸以与预备第一半导体图案320A1和第二半导体图案320B至第四半导体图案320D重叠。

第一层间绝缘层341中的每一个可以包括第一材料层,并且第一牺牲层343中的每一个可以包括第二材料层。第二材料层可以包括具有与第一材料层不同的蚀刻速率的绝缘材料,以允许选择性蚀刻。在一个实施例中,第一材料层可以包括氧化物层,第二材料层可以包括氮化物层。

参考图9B,步骤ST3A可以包括形成穿过第一堆叠体340的下部孔351A至351F。下部孔351A至351F可以同时形成。在形成下部孔351A至351F的蚀刻过程期间,预备第一半导体图案320A1和第二半导体图案320B至第四半导体图案320D中的每一个可以用作蚀刻停止层。

下部孔351A至351F可以包括第一下部孔351A、第二下部孔351B、第三下部孔351C、第四下部孔351D、第五下部孔351E和第六下部孔351F。

第一下部孔351A至第三下部孔351C可以与预备第一半导体图案320A1重叠。第二下部孔351B可以布置在第一下部孔351A和第三下部孔351C之间。第三下部孔351C可以被布置为比第一下部孔351A更靠近预备第一半导体图案320A1的边缘。第一下部孔351A至第三下部孔351C中的每一个可以穿过第一堆叠体340并延伸到预备第一半导体图案320A1中。

第四下部孔351D至第六下部孔351F可以与第二半导体图案320B至第四半导体图案320D重叠。第四下部孔351D至第六下部孔351F可以与第一堆叠体340重叠并且延伸到第二半导体图案320B至第四半导体图案320D中。

第一下部孔351A至第六下部孔351F中的每一个可以穿过第二半导体层329、第二保护层327、牺牲层325和第一保护层323,并且可以延伸到第一半导体层321中。第一下部孔351A至第六下部孔351F中的每一个可以具有比对应的半导体图案小的宽度。

参考图9C,步骤ST3A可以包括利用第一牺牲柱353A至第六牺牲柱353F分别填充如图9B所示的第一下部孔351A至第六下部孔351F。第一牺牲柱353A至第六牺牲柱353F可以包括具有与参考图9A所述的第一材料层和第二材料层不同的蚀刻速率的材料。根据一个实施例,第一牺牲柱353A至第六牺牲柱353F可以包括诸如钨的金属。

图10是图示图7所示的步骤ST5A的实施例的截面图。

参考图10,步骤ST5A可以包括形成第二堆叠体360,第二堆叠体360延伸以覆盖第一堆叠体340上的第一牺牲柱353A至第六牺牲柱353F。第二堆叠体360可以包括彼此交替堆叠的第二层间绝缘层363和第二层间绝缘层361。第二层间绝缘层361中的每一个可以包括如参考图9A所述的第一材料层,并且第二牺牲层363中的每一个可以包括如以上参考图9A所述的第二材料层。

图11A和图11B是图示图7所示的步骤ST7A的实施例的截面图。

参考图11A,步骤ST7A可以包括通过蚀刻第二堆叠体360来形成上部阶梯式结构USW1和USW2。上部阶梯式结构USW1和USW2可以包括与第二牺牲柱353B重叠的第一上部阶梯式结构USW1以及与第四牺牲柱353D重叠的第二上部阶梯式结构USW2。

第二堆叠体360的第二牺牲层363可以包括最下层L、最上层T和布置在最上层T和最下层L之间的一个或多个中间层M。形成第一上部阶梯式结构USW1和第二上部阶梯式结构USW2的蚀刻过程可以被控制,使得最下层L、中间层M和最上层T可以保留,同时分别与第一牺牲柱353A、第五牺牲柱353E和第六牺牲柱353F重叠。形成第一上部阶梯式结构USW1和第二上部阶梯式结构USW2的蚀刻过程可以被控制,以便暴露第三牺牲柱353C。

根据实施例的上部阶梯式结构USW1和USW2可以是在第二堆叠体360中具有彼此不同的深度的第一上部阶梯式结构USW1和第二部上部阶梯式结构USW2。在一个实施例中,第一上部阶梯式结构USW1的梯级可以包括最下层L、中间层M和最上层T,并且第二上部阶梯式结构USW2的相应梯级可以包括堆叠在最下层L上的中间层M和最上层T。

尽管未示出,但是在一个实施例中,上部阶梯式结构USW1和USW2可以包括具有相同深度的第一上部阶梯式结构USW1和第二上部阶梯式结构USW2。

当蚀刻第二堆叠体360时用作蚀刻阻挡层的掩模图案的形状、用于蚀刻第二堆叠体360的蚀刻过程的数目以及第二堆叠体360的蚀刻量可以根据目标第一上部阶梯式结构USW1和第二上部阶梯式结构USW2的结构变化。

参考图11B,步骤ST7A可以包括在第一堆叠体340上形成下部阶梯式结构LSW。可以通过蚀刻第一堆叠体340来形成下部阶梯式结构LSW,使得如图11A所示的第二上部阶梯式结构USW2可以被转录到第一堆叠体320上,并且第四牺牲柱353D可以被暴露。下部阶梯式结构LSW可以包围第四牺牲柱353D。

在形成下部阶梯式结构LSW时,可以形成第一虚设堆叠体DST1和第二虚设堆叠体DST2。第一虚设堆叠体DST1可以布置在第一上部阶梯式结构USW1和下部阶梯式结构LSW之间并且设置在第一堆叠体340上。第二虚设堆叠体DST2可以布置在下部阶梯式结构LSW上并且包围第四牺牲柱353D。

第一堆叠体340的第一牺牲层343可以包括最下层L’、最上层T’和布置在最上层T’和最下层L’之间的一个或多个中间层M’。形成下部阶梯式结构LSW的蚀刻过程可以被控制,使得最下层L’、中间层M’和最上层T’可以保留,同时分别包围第一牺牲柱353A、第二牺牲柱353B、第五牺牲柱353E和第六牺牲柱353F。形成下部阶梯式结构LSW的蚀刻过程可以被控制,以便维持第一上部阶梯式结构USW1。下部阶梯式结构LSW的梯级可以包括布置在最下层L’上的中间层M’和最上层T’。

当蚀刻第一堆叠体340时用作蚀刻阻挡层的掩模图案的形状、用于蚀刻第一堆叠体340的蚀刻过程的数目以及第一堆叠体340的蚀刻量可以根据目标下部阶梯式结构LSW而变化。

通过参考图11A和图11B描述的上述过程,可以在第一堆叠体340和第二堆叠体360中的每一个上形成阶梯式结构,并且可以暴露第三牺牲柱353C和第四牺牲柱353D。根据一个实施例,在第二堆叠体360形成在第一堆叠体340上之后,可以将第二堆叠体360上形成的第二上部阶梯式结构USW2转录到第一堆叠体340上,从而形成下部阶梯式结构LSW。结果,根据本公开的一个实施例,可以简化下部阶梯式结构LSW的蚀刻过程。

图12A和图12B是图示图7中所示的步骤ST9A的实施例的截面图。

参考图12A,步骤ST9A可以包括去除如图11B所示的第三牺牲柱353C和第四牺牲柱353D。结果,第三下部孔351C和第四下部孔351D可以被开放。

参考图12B,步骤ST9A可包括形成绝缘层355,绝缘层355填充如图12A所示的第三下部孔351C和第四下部孔351D并且覆盖第一上部阶梯式结构USW1和下部阶梯式结构LSW。绝缘层355的填充第三下部孔351C和第四下部孔351D的各部分可以被限定为第一支撑柱355SP_A和355SP_B。第一绝缘柱355SP_A可以与第一半导体图案320A1重叠,并且第二绝缘柱355SP_B可以与第二半导体图案320B重叠。

图13A至图13I是图示图7中所示的步骤ST11A的实施例的截面图。

参考图13A,步骤ST11A可以包括蚀刻第二堆叠体360,以便形成第一上部孔373A、第二上部孔373B、第三上部孔373C和第四上部孔373D,其分别暴露第一牺牲柱353A、第二牺牲柱353B、第五牺牲柱353E和第六牺牲柱353F。第一上部孔373A可以耦合至第一下部孔351A,第二上部孔373B可以耦合至第二下部孔351B,第三上部孔373C可以耦合至第五下部孔351E,并且第四上部孔373D可以耦合到第六下部孔351F。

蚀刻第二堆叠体360的过程可以包括在第二堆叠体360上形成包括多个开口的掩模图案371,以及使用掩模图案371作为蚀刻阻挡层来执行蚀刻过程。在使用掩模图案371作为蚀刻阻挡层的蚀刻过程期间,可以蚀刻与第二牺牲柱353B重叠的绝缘层355。

参考图13B,步骤ST11A可以包括通过第一上部孔373A、第二上部孔373B、第三上部孔373C和第四上部孔373D来分别去除第一牺牲柱353A、第二牺牲柱353B、第五牺牲柱353E和第六牺牲柱353F。结果,第一孔H1至第四孔H4可以被开放。

第一孔H1可以通过将如图13A所示的第一上部孔373A和第一下部孔351A连接来被限定,并且可以暴露预备第一半导体图案320A1的第一半导体层321。第二孔H2可以通过将如图13A所示的第二上部孔373B和第二下部孔351B彼此连接来被限定,并且可以暴露预备第一半导体图案320A1的第一半导体层321。第三孔H3可以通过将如图13A所示的第三上部孔373C和第五下部孔351E彼此连接来被限定,并且可以暴露第三半导体图案320C的第一半导体层321。第四孔H4可以通过将如图13A所示的第四上部孔373D和第六下部孔351F彼此连接来被限定,并且可以暴露第四半导体图案320D的第一半导体层321。

参考图13C,步骤ST11A可以包括在第一孔H1至第四孔H4中的每个孔的表面上形成存储器层381,在存储器层381上形成沟道层383,以及利用芯绝缘层385来填充沟道层383的中心区域。

存储器层381可以通过如以上参考图5B所述依次堆叠阻挡绝缘层BI、数据存储层DL和隧道绝缘层TI来形成。存储器层381可以同时形成在第一孔H1至第四孔H4的表面上。

沟道层383可以在存储器层381上具有各种结构。根据一个实施例,沟道层383可以保形地形成在存储器层381上,芯绝缘层385可以通过利用可流动材料层来填充第一孔H1至第四孔H4的中心区域(没有被沟道层383填充)并且将可流动材料层固化而形成。可流动材料层可以包括聚硅氮烷(PSZ)。

参考图13D,步骤ST11A可以包括去除如图13C所示的芯绝缘层385的上端,使得中空部分HP可以被限定在沟道层383的中心区域的上端中。结果,芯绝缘图案385P可以形成在第一孔H1至第四孔H4中的每一个中,使得芯绝缘图案385p可以将与芯绝缘图案385P相对应的沟道层383的上端开放。

参考图13E,步骤ST11A可以包括形成掺杂半导体层391L以填充如图13D所示的中空部分HP。掺杂半导体层391L可以包括n型杂质或p型杂质中的至少一个。

参考图13F,步骤ST11A可以包括去除掺杂半导体层391L的一部分、以及第三孔H3和第四孔H4中的每一个中包括的芯绝缘图案385P和沟道层383,以便暴露第三孔H3和第四孔H4中的每一个中形成的存储器层381。尽管未在图13F中示出,但是可以通过使用与第一孔H1和第二孔H2重叠并且暴露第三孔H3和第四孔H4的掩模图案(未示出)作为蚀刻阻挡层的蚀刻过程来去除掺杂半导体层391L的该部分。当去除第三孔H3和第四孔H4中的每一个中布置的芯绝缘图案385P和沟道层383时,可以将剩余的掺杂半导体层391L用作蚀刻阻挡层。

参考图13G,步骤ST11A可以包括在通过第三孔H3和第四孔H4暴露的存储器层381上形成氧化物层395。氧化物层395可以形成以补充存储器层381的绝缘特性。根据一个实施例,可以省略形成氧化物层395的过程。

参考图13H,步骤ST11A可以包括形成第一开口OP1和第二开口OP2,第一开口OP1和第二开口OP2分别耦合至第三孔H3和第四孔H4,并且穿过存储器层和氧化物层。在下文中,分别保留在第三孔H3和第四孔H4中的每一个中的存储器层和氧化物层将分别被称为虚设存储器层381P和氧化物层图案395P。

第一开口OP1可以穿过第三半导体图案320C的第一半导体层321,以便暴露第三下部接触插塞311C。第二开口OP2可以穿过第四半导体图案320D的第一半导体层321,以便暴露第四下部接触插塞311D。

参考图13I,步骤ST11A可以包括沟道结构380A、第二支撑柱380B、第一接触插塞397A和第二接触插塞397B。形成沟道结构380A、第二支撑柱380B、第一接触插塞397A和第二接触插塞397B可以包括利用导电材料来填充第三孔H3和第四孔H4以及第一开口OP1和第二开口OP2,以及将导电材料和如图13H所示的掺杂半导体层391L平坦化。导电材料可以包括能够传递电信号的各种材料。掺杂半导体层391L可以保留为覆盖图案391。

通过以上参考图13A至图13I描述的过程,沟道结构380A可以形成在第一孔H1中,第二支撑柱380B可以形成在第二孔H2中,第一接触插塞397A可以填充第三孔H3和第一开口OP1,并且第二接触插塞397B可以填充第四孔H4和第二开口OP2。沟道结构380A和第二支撑柱380B中的每一个可以包括沟道层383、芯绝缘图案385P和覆盖图案391。第一接触插塞397A可以接触第三下部接触插塞311C,并且第二接触插塞397B可以接触第四下部接触插塞311D。

尽管在图13A至图13I中未示出,但是在一个实施例中,可以省略覆盖图案391和芯绝缘图案385P,并且沟道结构380A和第二支撑柱380B中的每一个可以包括填充存储器层381的中心区域的沟道层383。

根据本公开的实施例,包围第一接触插塞397A和第二接触插塞397B中的每一个的虚设存储器层381P可以使用形成存储器层381的过程来形成。虚设存储器层381P可以用作用于使第一接触插塞397A和第二接触插塞397B绝缘的绝缘结构。

图14A至图14C是图示图7所示的步骤ST13A的实施例的截面图。

参考图14A,在执行步骤ST13A之前,如图13I所示的掩模图案371可以被去除,并且掩模图案371被去除的区域可以被填充有第一上部绝缘层399。第一上部绝缘层399可以包围如图13I所示的沟道结构380A、第二支撑柱380B、第一接触插塞397A和第二接触插塞397B中的每一个的上端。在形成第一上部绝缘层399之后,可以形成上部缝隙,可以形成填充上部缝隙的隔离层401,并且可以在第一上部绝缘层399上形成第二上部绝缘层411。第二上部绝缘层411可以延伸以包围如图13I所示的沟道结构380A、第二支撑柱380B、第一接触插塞397A和第二接触插塞397B。上部缝隙可以对应于如图2和图3B所示的上部缝隙USI。

步骤ST13A可以包括形成穿过第二上部绝缘层411、第一上部绝缘层399、第二堆叠体360和第一堆叠体340的缝隙413。缝隙413可以与预备第一半导体图案302A1重叠。预备第一半导体图案302A1的第二半导体层329可以通过缝隙413的底表面被暴露。

参考图14B,步骤ST13A可以包括通过缝隙413选择性地去除第一牺牲层343和第二牺牲层363。缝隙413可以与如图1所示的衬底的第一区域A1重叠,并且衬底的第二区域A2可以与第一区域A1和缝隙413分离。可以选择性地去除第一牺牲层343和第二牺牲层363,使得第一牺牲层343和第二牺牲层363中的每一个的一部分可以保留在第二区域A2中,并且第一牺牲层343和第二牺牲层363中的每一个与第一区域A1重叠的另一部分可以被去除。

在下文中,第一牺牲层343和第二牺牲层363被去除的区域可以被称为栅极区域431。可以在第一层间绝缘层341和第二层间绝缘层361之间限定栅极区域431。

保留在第二区域A2中的第一牺牲层343和第二牺牲层363以及与其重叠的第一层间绝缘层341和第二层间绝缘层361可以形成第三虚设堆叠体DST3。第三虚设堆叠体DST3可以对应于如图4所示的虚设堆叠体DST。

参考图14C,步骤ST13A可以包括在如图14B所示的栅极区域431中形成导电图案433。

可以通过形成沿栅极区域431的表面延伸的阻挡金属层、形成足够厚以填充阻挡金属层上的栅极区域431的导电层、以及蚀刻阻挡金属层和导电层以将其与导电图案433分离来形成导电图案433。结果,可以形成包括第一层间绝缘层341和第二层间绝缘层361以及导电图案433的栅极堆叠结构430。

参考图14A至图14C使用上述过程形成的栅极堆叠结构430可以延伸以包围沟道结构380A、第一支撑柱355SP_A和355SP_B、第二支撑柱380B和第一接触插塞397A。如图16A所示,第一接触插塞397A可以通过虚设存储器层381P来与栅极堆叠结构430的导电图案433绝缘。因此,根据实施例,可以在不形成用于阻挡围绕第一接触插塞397A形成导电图案433的阻挡结构的情况下,确保半导体存储器装置的操作性能。因此,根据本公开的实施例,可以防止由阻挡结构的制造过程引起的难度水平和过程失败的增加。

通过以上参考图14A至图14C所述的过程,尽管第一牺牲层343和第二牺牲层363被导电图案433代替,但是沟道结构380A、第一支撑柱355SP_A和355SP_B、第二支撑柱380B以及第一接触插塞397A可以用作支撑件。

通过以上参考图14A至图14C所述的过程,如图13I所示的第一虚设结构DST1和第二虚设结构DST2的与缝隙413相邻的第一牺牲层343和第二牺牲层363可以由导电图案433代替。结果,如图16A所示,可以限定第一虚设栅极堆叠结构430D1和第二虚设栅极堆叠结构430D2。

在下文中,可以参考图15A至图15D以及图16A和图16B来描述在步骤ST13A之后执行的后续过程。

图15A至图15D是图示形成沟道连接图案421的过程的截面图。

参考图15A,可以在缝隙413的侧壁上形成侧壁绝缘层415,以保护栅极堆叠结构430。

随后,可以蚀刻第二半导体层329,使得缝隙413可以延伸到预备第一半导体图案320A1的牺牲层325中。以这种方式,预备第一半导体图案320A1的第二半导体层329可以被缝隙413穿透,并且牺牲层325可以通过缝隙413的底表面被暴露。与缝隙413不重叠的如图13I所示的第二半导体图案320B和第三半导体图案320C以及第四半导体图案320D可以保留而不被蚀刻。

参考图15B,如图15A所示的预备第一半导体图案302A1的牺牲层325可以被去除,以通过缝隙413暴露存储器层381。第一半导体层321和第二半导体层329可以由第一保护层323和第二保护层327保护。

参考图15C,通过去除如图15B所示的存储器层381的暴露区域,可以将存储器层381分离为第一存储器图案381P1和第二存储器图案381P2,并且可以暴露沟道结构380A的侧壁。在去除存储器层381的蚀刻过程中,如图15B所示的预备第一半导体图案320Al的第一保护层323和第二保护层327被去除,使得预备第一半导体图案320A1的第一半导体层321和第二半导体层329可以被暴露。

在下文中,在第一半导体层321和第二半导体层329之间布置的并且在第一存储器图案381P1和第二存储器图案381P2之间延伸的空间可以被限定为水平空间417。水平空间可以形成为暴露沟道结构380A的沟道层383。

在水平空间417的蚀刻过程期间,包围第二支撑柱380B的存储器层可以被分离为如图16A所示的第一虚设图案381P1d和第二虚设图案381P2d。在形成水平空间417的蚀刻过程中,如图16A所示,可以在第一绝缘柱355SP_A的侧壁中形成凹槽355GR。

参考图15D,如图15C所示的水平空间417可以利用沟道连接图案421来填充。沟道连接图案421可以接触第一半导体层321和第二半导体层329以及沟道层383。沟道连接图案421可以包括n型杂质或p型杂质。

沟道连接图案421可以通过使用第一半导体层321和第二半导体层329中的至少一个作为种子层进行选择性生长(例如,选择性外延生长(SEG))来形成。在一个实施例中,可以使用诸如化学气相沉积(CVD)的非选择性方法来形成沟道连接图案421。

通过参考图15A至图15D描述的过程,可以形成包括第一半导体层321、第二半导体层329和沟道连接图案421的第一半导体图案320A2。

沟道连接图案421可以在第一存储器图案381P1和第二存储器图案381P2之间延伸,并且在第一虚设图案381P1d和第二虚设图案381P2d之间延伸,以接触如图16A所示的第二支撑柱380B的沟道层383。如图16A所示,沟道连接图案421可以延伸以填充第一绝缘柱355SP_A的凹槽355GR。

尽管未在图15D中示出,在形成填充缝隙413的绝缘材料或导电材料之后,可以执行平坦化过程。通过平坦化过程,第二上部绝缘层结构411的上表面可以被暴露。

图16A和图16B是图示形成位线接触插塞453、栅极接触插塞455、第一上部接触插塞457和第二上部接触插塞459的过程的截面图。

参考图16A,可以在第一上部绝缘层399上形成第三上部绝缘层451。第三上部绝缘层451可以延伸以覆盖沟道结构380A、第二支撑柱380B、第一接触插塞397A和第二接触插塞397B。

参考图16B,可以形成穿过第三上部绝缘层451、第一上部绝缘层399和绝缘层355中的至少一个的位线接触插塞453、栅极接触插塞455、第一上部接触插塞457和第二上部接触插塞459。

位线接触插塞453可以穿过第三上部绝缘层451,以接触沟道结构380A。栅极接触插塞455可以穿过与阶梯式结构重叠的第一上部绝缘层399和绝缘层355,以分别接触栅极堆叠结构430的导电图案433。第二上部接触插塞457可以穿过第三上部绝缘层451,以接触第一接触插塞397A。第二上部绝缘层459可以穿过第三上部绝缘层451,以接触第二接触插塞397B。

下文中,可以执行形成如图1所示的位线BL的过程。位线BL可以耦合到位线接触插塞453。

图17A是图示在图7所示的步骤ST7A之后执行的清洗过程的截面图,并且图17B是图示通过在清洗过程之后执行的后续过程制造的半导体存储器装置的截面图。

参考图17A,可以在执行参考图8A和图8B描述的步骤ST1A、参考图9A至图9C描述的步骤ST3A、参考图10描述的步骤ST5A以及参考图11A和图11B描述的步骤ST7A之后形成清洗过程。通过清洗过程,可以去除第一堆叠体340的第一牺牲层343中每一个的一部分和第二堆叠体360的第二牺牲层363中的每一个的一部分。

在下文中,如以上参考图12A描述,如图11B所示的第三牺牲柱353C和第四牺牲柱353D可以被去除。

通过上述清洗过程以及去除第三牺牲柱和第四牺牲柱的过程,参考图11B描述的第二虚设堆叠体DST2可以从第一堆叠体340的下部阶梯式结构LSW’去除。另外,凹凸可以形成在第一堆叠体340上保留的第一虚设堆叠体DST1’的侧壁上。另外,凹凸可以形成在与第三半导体图案320C重叠的第一堆叠体340和第二堆叠体360中的每一个的侧壁上。形成下部阶梯式结构LSW’的梯级的第一层间绝缘层341可以与布置在第一层间绝缘层341上的第一牺牲层相比朝向侧部保持更长。形成第一上部阶梯式结构USW1’的梯级的第二层间绝缘层361可以与布置在第二层间绝缘层361上的第二牺牲层363相比朝向侧部保持更长。

参考图17B,通过参考图12B描述的过程,可以形成延伸以覆盖第一上部阶梯式结构USW1’和下部阶梯式结构LSW’的绝缘层355。以与参考图12B描述的相同的方式,绝缘层355的部分可以被限定为第一支撑柱355SP_A和355S_B。

随后,可以依次执行参考图13A至图13I描述的步骤ST11A、参考图14A至图14C描述的步骤ST13A以及参考图15A至图15D描述的形成沟道连接图案421。因此,可以形成包括如图17A所示的第一上部阶梯式结构USW1’和下部阶梯式结构LSW’的并且具有不平坦的侧壁的栅极堆叠结构430’。另外,可以形成具有如图17A所示的凹凸的虚设栅极堆叠结构430D’。

通过参考图13A至13I描述的步骤ST11A以及参考图14A至图14C描述的步骤ST13A,栅极堆叠结构430’可以包括包围沟道结构380A的导电图案433、第一支撑柱355SP_A和355SP_B、第二支撑柱380B以及第一接触插塞397A。

随后,通过以上参考图16A和图16B描述的过程,可以形成位线接触插塞453、栅极接触插塞455、栅极接触插塞455和第一上部接触插塞457。

图18是图示根据本公开的实施例的制造半导体存储器装置的方法的示意性流程图。

参考图18,制造半导体存储器装置的方法可以包括:形成预备结构的步骤ST1B、形成被牺牲柱和第一支撑柱穿透的第一堆叠体的步骤ST3B、形成第二堆叠体的步骤ST5B、形成阶梯式结构的步骤ST7B、形成沟道结构、第二支撑柱和接触插塞的步骤ST9B、以及形成导电图案的步骤ST11B。

步骤ST1B可以在形成如上参考图6所述的包括下部结构LS的衬底201之后执行。换言之,预备结构可以形成在如以上参考图6所述的包括下部结构LS的衬底201上。

图19A至图19E是与根据图18的制造方法的过程相对应的结构的截面图。图19A至图19E是图示在以上参考图1描述的衬底的第一区域A1上形成的与制造过程相对应的结构的截面图。图示根据制造过程形成在第一区域A1上的结构的截面图沿图2的线I-I’被截取。

参考图19A,步骤ST1B可以包括形成半导体图案520A1至520C以及形成垂直掺杂的半导体图案531A至531C。半导体图案520A1至520C和垂直掺杂的半导体图案531A至531C可以形成在包括下部结构500的衬底上。

下部结构500可以包括被第一下部接触插塞511A至第三下部接触插塞511C穿透的下部绝缘层501。如以上参考图6所述,第一下部接触插塞511A至第三下部接触插塞511C可以分别对应于第一下部接触插塞11A至第三下部接触插塞11C。尽管下部结构500示出了参考图6所述的下部结构LS的一部分,但是半导体图案520A1至520C可以形成在包括如图6所示的下部结构LS的衬底201上。

半导体图案520A1至520C中的每一个可以包括顺序堆叠在彼此上的第一半导体层521、牺牲堆叠体505和第二半导体层529。半导体图案520A1至520C可以包括与第一下部接触插塞511A重叠的预备第一半导体图案520A1、与第二下部接触插塞511B重叠的第二半导体图案520B以及与第三下部接触插塞511C重叠的第三半导体图案520C。

牺牲堆叠体505的第一半导体层521、第一保护层523、牺牲层525和第二保护层527以及第二半导体层529可以包括分别与以上参考图8A所述的牺牲堆叠体305的第一半导体层321、第一保护层323、牺牲层325和第二保护层327以及第二半导体层329相同的材料。

以与参考图8B描述的相同的方式,步骤ST1B可以包括形成垂直掺杂的半导体图案531A至531C,以及利用间隙填充绝缘层535来填充半导体图案520A1至520C之间的空间。

随后,步骤ST3B可以使用与以上参考图9A至图9C描述的相同的过程和材料来执行。在步骤ST3B处,可以形成包括彼此交替堆叠的第一层间绝缘层541和第一牺牲层543的第一堆叠体540,并且可以利用第一牺牲柱553A至第五牺牲柱553E来分别填充穿过第一堆叠体540的第一下部孔551A至第五下部孔551E。

第一下部孔551A、填充第一下部孔551A的第一牺牲柱553A、第二下部孔551B、填充第二下部孔551B的第二牺牲柱553B、第三下部孔551C和填充第三下部孔551C的第三牺牲柱553C可以与预备第一半导体图案520A1重叠。第一下部孔551A至第三下部孔551C的布置可以与如图9B所示的第一下部孔351A至第三下部孔351C的布置相同。第一下部孔551A、填充第一下部孔551A的第一牺牲柱553A、第二下部孔551B、填充第二下部孔551B的第二牺牲柱553B、第三下部孔551C以及填充第三下部孔551C的第三牺牲柱553C可以穿过第一堆叠体540、第二半导体层529和牺牲堆叠体505,并且可以延伸到第一半导体层521中。

第四下部孔551D和填充第四下部孔551D的第四牺牲柱553D中的每一个可以与对应的第二半导体图案520B重叠,可以穿过第一堆叠体540、第二半导体层529和牺牲层堆叠体505,并且可以延伸到第一半导体层521中。第五下部孔551E和填充第五下部孔551E的第五牺牲柱553E中的每一个可以与对应的第三半导体图案520C重叠,可以穿过第一堆叠体540、第二半导体层529和牺牲堆叠体505,并且可以延伸到第一半导体层521中。

步骤ST3B可以包括形成包括开口的掩模图案557,第一堆叠体540上的第三牺牲柱553C和第四牺牲柱553D通过开口被开放。掩模图案557可以覆盖第一牺牲柱553A、第二牺牲柱553B和第五牺牲柱553E。

参考图19B,步骤ST3B可以包括通过使用掩模图案557作为蚀刻阻挡层的蚀刻过程,通过去除图19A所示的第三牺牲柱553C和第四牺牲柱553D来使得第三下部孔551C和第四下部孔551D开放。

参考图19C,步骤ST3B可以包括去除如图19B所示的掩模图案557,以及在第三下部孔551C和第四下部孔551D中分别形成第一支撑柱559A和559B。第一支撑柱559A和559B中的每一个可以包括绝缘材料。第一支撑柱559A和559B可以包括第一绝缘柱559A和第二绝缘柱559B。第一绝缘柱559A可以填充第三下部孔551C,第二绝缘柱559B可以分别填充第四下部孔551D。第一绝缘柱559A可以与预备第一半导体图案520A1重叠,并且第二绝缘柱559B可以分别与第二半导体图案520B重叠。

参考图19D,步骤ST5B可以包括在第一堆叠体540上形成第二堆叠体560,第一堆叠体540被第一牺牲柱553A和第二牺牲柱553B、第一支撑柱559A和559B以及第五牺牲柱553E穿透。

第二堆叠体560可以包括第二牺牲层563和第二层间绝缘层561,其延伸以覆盖第一牺牲柱553A和第二牺牲柱553B、第一支撑柱559A和559B以及第五牺牲柱553E并且彼此交替堆叠。第二牺牲层563可以包括与第一牺牲层543相同的材料,并且第二层间绝缘层561可以包括与第一层间绝缘层541相同的材料。

随后,通过步骤ST7B,可以在第二堆叠体560上形成上部阶梯式结构,并且可以在第一堆叠体540上形成下部阶梯式结构。步骤ST7B可以使用如上参考图11A和图11B所述的过程来形成或以上参考图17A所述的过程来形成。

参考图19E,在步骤ST7B之后,可以形成覆盖阶梯式结构的绝缘层555。可以通过绝缘层555来减轻由阶梯式结构引起的层级差。

随后,通过步骤ST9B,可以形成沟道结构580A、第二支撑柱580B和接触插塞597。步骤ST9B可以以与以上参考图13A至图13I描述的步骤ST11A相同的方式来执行。

在步骤ST9B处形成的沟道结构580A和第二支撑柱580B可以形成在穿过如图19D所示的第一堆叠体540和第二堆叠体560的孔中,并且与预备第一半导体图案520A1重叠。在步骤ST9B处,沟道结构580A和第二支撑柱580B中的每一个可以形成在存储器层581上,存储器层581形成在对应孔的表面上。沟道结构580A和第二支撑柱580B中的每一个可以包括如以上参考图3A和图3B所述的沟道层583、芯绝缘图案585和覆盖图案591。

在步骤ST9B处形成的接触插塞597可以形成在穿过如图19D所示的第一堆叠体540和第二堆叠体560的孔中,并且与第三半导体图案520C重叠。接触插塞597可以穿过对应孔的表面上形成的虚设存储器层581P和氧化物层595,并且穿过第三半导体图案520C以接触第三下部接触插塞511C。

随后,如图14A所示,可以形成包围沟道结构580A、第二支撑柱580B和接触插塞597的第一上部绝缘层599。

随后,在步骤ST11B处,如图19D所示的第一牺牲层543和第二牺牲层563可以被导电图案633代替,使得可以形成包围沟道结构580A、第一支撑柱559A和559B、第二支撑柱580B和接触插塞597的栅极堆叠结构630。在形成导电图案633时,可以在栅极堆叠结构630的阶梯式结构上形成虚设栅极堆叠结构630D。步骤ST11B可以以与参考图14A至图14C描述的步骤ST13A相同的方式来执行。

随后,使用以上参考图15A至图15D描述的过程,如图19D所示的预备第一半导体图案520A1的牺牲堆叠体505可以被沟道连接图案621代替。结果,可以限定耦合到沟道结构580A的第一半导体图案520A2。

通过沟道连接图案621,包围沟道结构580A的存储器层581可以被分离为第一存储器图案585P1和第二存储器图案581P2。通过沟道连接图案621,包围第二支撑柱580B的存储器层581可以被分离为第一虚设图案581P1d和第二虚设图案581P2。当形成沟道连接图案621时,可以在第一绝缘柱559A的侧壁上形成凹槽559GR,并且沟道连接图案621可以延伸以填充凹槽559GR。

随后,通过以上参考图16A和图16B描述的过程,可以形成上部绝缘层651、位线接触插塞653、栅极接触插塞655和上部接触插塞657。

图20A至图20C是图示根据本公开的实施例的制造半导体存储器装置的方法的截面图。图20A至图20C是图示以上参考图1描述的衬底的第一区域A1上形成的与制造过程相对应的结构的截面图。图示根据制造过程形成在第一区域A1上的结构的截面图沿图2的线I-I’被截取。在下文中,将省略重复配置的详细描述。

参考图20A,可以使用如上参考图8A和图8B描述的过程来形成与第一下部接触插塞711A至第三下部接触插塞711C重叠的半导体图案720A1至720C。半导体图案720A1至720C可以包括耦合至第一下部接触插塞711A的预备第一半导体图案720A1、分别耦合至第二下部接触插塞711B的第二半导体图案720B以及耦合至第三下部接触插塞711C的第三半导体图案720C。

随后,可以形成包围沟道结构780A、第一支撑柱755A和755B、第二支撑柱780B和预备插塞780的阶梯式堆叠体SWS。

阶梯式堆叠体SWS可以包括第一堆叠体740和第二堆叠体760。第一堆叠体740可以延伸以与半导体图案720A1至720C重叠并且具有下部阶梯式结构。第一堆叠体740可以包括彼此交替堆叠的第一层间绝缘层741和第一牺牲层743。第二堆叠体760可以包括在第一堆叠体740上彼此交替堆叠的第二牺牲层763和第二层间绝缘层761。第二堆叠体760可以延伸以与预备第一半导体图案720A1重叠并且具有上部阶梯式结构。

沟道结构780A、第二支撑柱780B和预备插塞780C可以形成在穿过第一堆叠体740和第二堆叠体760的孔中。沟道结构780A和第二支撑柱780B可以与预备第一半导体图案720A1重叠并且延伸到预备第一半导体图案720A1中。预备插塞780C可以与第三半导体图案720C重叠并且延伸到第三下部半导体图案720C中。沟道结构780A、第二支撑柱780B和预备插塞780C中的每一个可以布置在对应孔的表面上形成的存储器层781上。沟道结构780A、第二支撑柱780B和预备插塞780C中的每一个可以包括沟道层783、芯绝缘图案785和覆盖图案791。沟道层783、芯绝缘图案785和覆盖图案791可以分别包括与以上参考图3A和图3B所述的沟道层83、芯绝缘图案85和覆盖图案91相同的材料。

第一支撑柱755A和755B可以从覆盖阶梯式堆叠结构SWS的上部阶梯式结构和下部阶梯式结构的绝缘层755延伸,或者可以与绝缘层755分离地形成。第一支撑柱755A和755B可以穿过第一堆叠体740。第一支撑柱755A和755B可以包括第一绝缘柱755A和第二绝缘柱755B。第一绝缘柱755A可以与预备第一半导体图案720A1重叠并且延伸到预备第一半导体图案720A1中。第二绝缘柱755B可以分别与第二半导体图案720B重叠,并且延伸到第二半导体图案720B中。

在执行参考图9A至图9C、图10、图11A和图11B、图12A和图12B以及图13A至图13E的上述过程之后,包围沟道结构780A、第一支撑柱755A和755B、第二支撑柱780B和预备插塞780C的阶梯式堆叠体SWS可以通过平坦化掺杂的半导体层291L以暴露如图13E所述的掩模图案371来形成。随后,掩模图案371可以被第一上部绝缘层799代替。结果,沟道结构780A、第二支撑柱780B和预备插塞780C的上端可以被第一上部绝缘层799包围。

参考图20B,可以形成接触孔HC,通过接触孔HC暴露第三下部接触插塞711C。形成接触孔HC的过程可以包括去除预备插塞780C以暴露如图20A所示的存储器层781,在存储器层781上沉积氧化物层795,以及形成穿过氧化物层795和存储器层781的开口,以暴露第三下部接触插塞711C。在下文中,保留在接触孔HC周围的存储器层被称为虚设存储器层781P。

参考图20C,在与如图20B所示的第一牺牲层743和第二牺牲层763可以被导电图案833G代替的同时,如图20B所示的接触孔HC可以利用接触插塞833CT来被填充。

第一牺牲层743和第二牺牲层763可以被导电图案833G代替,使得可以形成包围沟道结构780A、第一支撑柱755A和755B、第二支撑柱780B和接触插塞833CT的栅极堆叠体830。可以以与以上参考图14A至图14C描述的步骤ST13A相同的方式来执行利用导电图案833G代替第一牺牲层743和第二牺牲层763的过程。

通过利用在形成导电图案833G时提供的导电材料填充如图20B所示的接触孔HC,接触插塞833CT可以与导电图案833G同时形成。根据该实施例,接触插塞833CT和导电图案833G可以包括相同的导电材料。

然后可以执行包括参考图15A至图15D描述的过程以及参考图16A和图16B描述的过程的后续过程。

图21是图示根据本公开的实施例的存储器系统1100的配置的框图。

参考图21,存储器系统1100可以包括存储器装置1120和存储器控制器1110。

存储器装置1120可以是由多个闪存芯片组成的多芯片封装。存储器装置1120可以包括:包括下部阶梯式结构的第一堆叠;穿过第一堆叠并且包括绝缘层的支撑柱;使得下部阶梯式结构和支撑柱开放并且包括上部阶梯式结构的第二堆叠;以及穿过第一堆叠和第二堆叠的沟道结构。

存储器控制器1110可以被配置为控制存储器装置1120,并且包括静态随机存取存储器(SRAM)1111、中央处理单元(CPU)1112、主机接口1113、纠错块1114和存储器接口1115。SRAM 1111可以用作CPU 1112的操作存储器,CPU 1112可以执行用于存储器控制器1110的数据交换的控制操作,并且主机接口1113可以包括主机访问存储器系统1100的数据交换协议。另外,纠错块1114可以检测并纠正从存储器装置1120读取的数据中包括的错误,并且存储器接口1115可以执行与存储器装置1120的对接。存储器控制器1110还可以包括用于存储代码数据以与主机对接的只读存储器(ROM)。

具有上述配置的存储器系统1100可以是固态驱动器(SSD)或其中存储器装置1120和存储器控制器1110被组合的存储器卡。例如,当存储器系统1100是SSD时,存储器控制器1110可以通过接口协议(包括通用串行总线(USB)、多媒体卡(MMC)、外围部件快速互连(PCI-E)、串行高级技术附件(SATA)、并行高级技术附件(PATA)、小型计算机小型接口(SCSI)、增强型小型磁盘接口(ESDI)和集成驱动电子装置(IDE))中的一个来与外部装置(例如,主机)通信。

图22是图示根据本公开的实施例的计算系统1200的配置的框图。

参考图22,计算系统1200可以包括电耦合到系统总线1260的CPU 1220、随机存取存储器(RAM)1230、用户接口1240、调制解调器1250和存储器系统1210。另外,当计算系统1200是移动装置时,可以进一步包括用于向计算系统1200提供操作电压的电池,还可以包括应用芯片组、图像处理器、移动DRAM等。

存储器系统1210可以包括存储器装置1212和存储器控制器1211。存储器装置1212可以包括:包括下部阶梯式结构的第一堆叠、穿过第一堆叠并且包括绝缘层的支撑柱、使得下部阶梯式结构和支撑柱开放并且包括上部阶梯式结构的第二堆叠、以及穿过第一堆叠和第二堆叠的沟道结构。

根据本公开,具有下部阶梯式结构的第一堆叠体的结构稳定性和制造过程的稳定性可以通过穿透第一堆叠体的柱结构来改进。

根据本公开,在第一堆叠体上形成第二堆叠体之后,可以分别形成第一堆叠体的阶梯式结构和第二堆叠体的阶梯式结构,使得用于形成阶梯式结构的过程可以被简化。

- 半导体存储器装置和半导体存储器装置的制造方法

- 半导体存储器装置和半导体存储器装置的制造方法