减轻功率放大器耦合压控振荡器所引起干扰的系统和方法

文献发布时间:2023-06-19 11:17:41

技术领域

本发明总体上涉及通信系统,并且更具体地说涉及减轻由功率放大器谐波耦合到发射器的压控振荡器中引起的干扰的系统和方法。

背景技术

通信装置的发射器可包含具有压控振荡器(VCO)的频率合成器或锁相环(PLL)以及包含功率放大器(PA)的功率部分。在本记载中,频率合成器可以是射频(RF)合成器,尽管本文所描述的实施例不限于RF配置。VCO的频率通常除以整数因子N以产生PA的发射频率。PA到VCO的“拉动”可以是由于涉及PA和VCO的电感的磁耦合而出现的,无论是实际的无源电感器还是相应区段的载流供应回路,尤其是在PA以高功率电平发射时。PA到VCO的耦合可能对发射器的基本操作有害。其可能会影响频率合成器本身的控制电压以使其超出变容器的线性范围,从而导致发射器中的调制误差,并且可能进一步导致PLL的稳定性问题。其还可通过影响VCO相位噪声而诱导相位噪声降级,从而潜在地恶化发射并违反发射频谱掩码。另外,相位噪声降级还可能影响用于发射器的带内误差向量幅度(EVM)。在采用基于窄带的PLL的合成器的发射器中,此降级可以很显著,这通常是满足相位噪声规格的优选设计选择。

可通过在PA与VCO之间采用较高的频率间隔来减轻由PA到VCO的耦合所引起的干扰,但这会导致VCO和本地振荡器(LO)链中的较高电流消耗。来自片上PA的输出功率可被降低,但是将需要外部前端模块以显著的额外费用和电路板面积/占用面积来实现期望的功率电平。可采用宽带合成器,但是这种合成器由于较高的相位噪声而增加不期望的发射。可在VCO中使用磁差电感器,但这种电感器消耗明显更高的硅面积。电感-电容或基于L-C的VCO可由环形振荡器来代替,所述环形振荡器通常对耦合效应不太敏感。然而,环形振荡器遭受较高的相位噪声。PA区段和VCO区段也可在空间上分离,以最小化耦合;然而,这种空间分离的增加在使用具有更精细几何工艺的先进的半导体制造技术的收发器中通常是不可行的。先进的制造技术对最小化硅面积、降低成本和降低电流消耗为有利的。

发明内容

根据本记载的一个实施例的一种发射器包含:频率合成器,所述频率合成器包含提供振荡信号的压控振荡器;可编程延迟电路,所述可编程延迟电路延迟所述振荡信号以提供经延迟振荡信号;功率放大器,所述功率放大器被配置成使用所述经延迟振荡信号来发射信号;以及延迟控制器,所述延迟控制器用延迟时间对所述延迟电路进行编程,所述延迟时间减少由从所述功率放大器到所述压控振荡器的耦合所引起的干扰。

所述延迟电路可被数字地编程以选择整数个延迟步长,其中延迟步长的总数和每个延迟步长的持续时间基于所述振荡信号针对多个操作振荡频率中的每个操作振荡频率的周期来确定。所述延迟控制器可对所述延迟电路进行编程,以减少所述压控振荡器的作为延迟变化的函数的控制电压变化。另外或在替代性方案中,所述延迟控制器可对所述延迟电路进行编程,以减少在所述发射器的输出处的作为延迟变化的函数的相位噪声降级。

所述延迟控制器可基于在所述压控振荡器与所述功率放大器之间的传播延迟以及所述压控振荡器的频率来调整所述延迟电路。所述延迟控制器可基于检测到的操作温度来调整所述延迟电路。所述延迟控制器可将校准值与信道频率偏移和温度偏移组合,以确定用于对所述延迟电路进行编程的延迟选择值。

所述延迟控制器可包含存储器,所述存储器基于检测到的温度来存储多个温度偏移;以及组合器,所述组合器将校准值与所选温度偏移和频率偏移组合以提供用于对所述延迟电路进行编程的延迟选择值。所述存储器可存储多个校准值,每个校准值由一个或多个发射频带中的对应一个发射频带来确定,其中校准值基于所选发射频带来选择。

所述发射器可包含处理电路系统,所述处理电路系统基于在所述压控振荡器与所述功率放大器之间的经校准传播延迟以及在信道频率与用于确定所述经校准传播延迟的校准频率之间的频率差,来计算并提供所述频率偏移。所述处理电路系统可基于检测到的温度以从所述温度偏移中进行选择。所述温度偏移可基于测量跨相对于校准温度的可适用操作温度范围的延迟和增量延迟步长来确定。

根据本记载的一个实施例的一种减轻在发射器中由从功率放大器到压控振荡器的耦合所引起的干扰的方法包含:由包含所述压控振荡器的频率合成器生成振荡信号;以及将所述振荡信号延迟一定量,所述一定量在功率放大器使用经延迟振荡信号进行发射时,减少由从所述功率放大器到所述压控振荡器的耦合所引起的干扰。

所述方法可包含选择整数个延迟步长,其中延迟步长的总数和每个延迟步长的持续时间基于所述振荡信号针对多个操作振荡频率中的每个操作振荡频率的周期来确定。所述方法可包含延迟以减少所述压控振荡器的作为延迟变化的函数的控制电压变化。所述方法可包含延迟以减少在所述发射器的输出处的作为延迟变化的函数的相位噪声降级。

所述方法可包含基于在所述压控振荡器与所述功率放大器之间的传播延迟以及所述压控振荡器的频率进行延迟。所述方法可包含基于检测到的操作温度进行延迟。所述方法可包含将校准值与信道频率偏移和温度偏移组合。所述方法可包含基于指示检测到的温度的温度值来选择温度偏移;基于在校准频率下的在所述压控振荡器与所述功率放大器之间的传播延迟以及在所述校准频率与信道频率之间的差来计算频率偏移;以及将所述温度偏移和所述频率偏移与校准值组合。

附图说明

本发明通过举例的方式示出并且不受附图限制,在附图中,相似附图标记指示类似元件。附图中的元件是为了简单和清楚起见而示出的并且不一定按比例绘制。

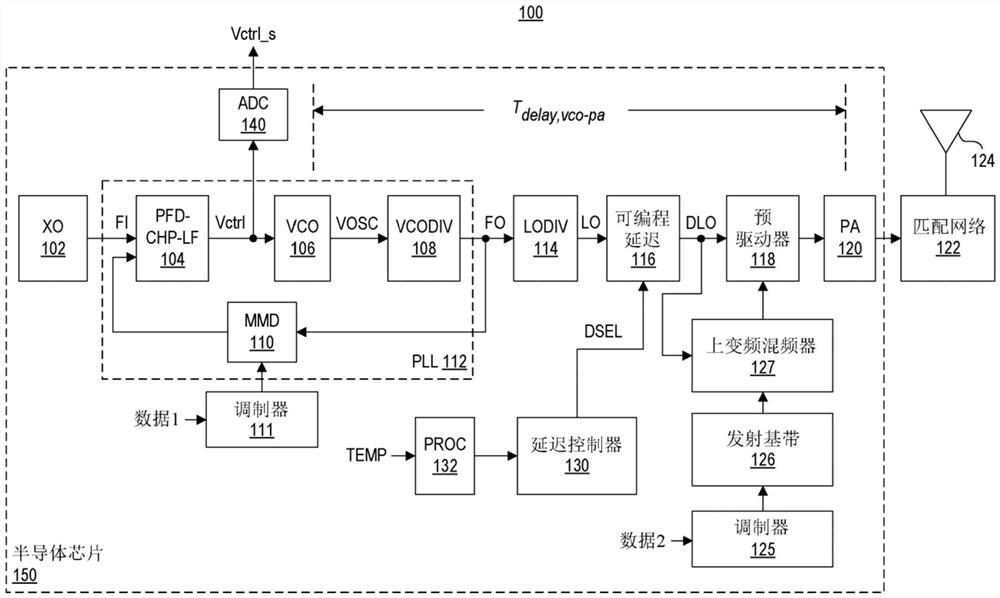

图1是根据本记载的一个实施例的包含可编程延迟电路的发射器电路的简化框图,所述可编程延迟电路减轻由从PA到VCO的耦合所引起的干扰。

图2是展示根据本记载的一个实施例的存在于图1的PA与VCO之间的磁耦合的形象示意图。

图3示出根据本记载的一个实施例的在从0到2π的全周期(或ΔC的全周期)内绘制值ΔG、ΔC、开环中的Δf

图4包含根据本记载的一个实施例的绘制开环中的Δf

图5是根据本记载的一个实施例所实施的图1的延迟电路的简化框图。

图6是根据本记载的一个实施例所实施的延迟单元的示意图,其可用作图5的延迟单元中的一个或多个延迟单元。

图7是绘制根据图5和6的实施例所配置的图1的延迟电路的DSEL<2:0>信号的每个设置的DLO信号对时间的一个周期的幅度的图解图。

图8是根据本记载的一个实施例的2个VCO周期内的开环中的Δf

图9是展示根据本记载的一个实施例的对于915MHz发射器,在约5.49GHz下操作的VCO的从-40℃到135℃的温度补偿的表格。

图10是根据本记载的一个实施例的与处理电路系统所介接的图1的延迟控制器的简化框图。

图11是展示根据本记载的一个实施例的用于确定要存储在图10的温度偏移存储器中的温度偏移的表征过程的流程图。

图12是根据本记载的一个实施例的图1的发射器电路的校准程序的流程图。

图13是展示图1的发射器电路的正常操作的流程图,所述正常操作用于更新图10的延迟控制器的校准值和偏移值,以在每次发射之前更新由图1的延迟电路实施的延迟。

具体实施方式

在发射器中功率放大器(PA)与压控振荡器(VCO)之间的磁耦合引起的干扰可能对发射操作有害。侵扰者PA中的谐波电流通过某个增益和相位因子连接到受害者VCO电流(即VCO L-C储能电路中的瞬时电流)。在发射本地振荡器(LO)链中VCO与PA之间的延迟通过相位因子影响在PA到VCO之间的耦合。其调制VCO L-C储能电路并在有效的储能电路电容中产生偏移,从而影响RF合成器中的瞬时频率和所得的反馈控制电压。所述耦合取决于VCO与PA之间的延迟,其中过零点以每半个VCO周期周期性地出现。在过零点附近,由于在高增益区域中将PA注入到VCO中,相位噪声降级变得严重。降级在过零点处达到最大值,并且当操作因延迟而远离过零点时对称地改善。相关的行为是在VOSC信号的过零点附近的电路噪声注入使VCO的相位噪声降级。

通过在发射LO链中的VCO与PA之间采用延迟电路,延迟可被调整而使耦合以足够裕度远离过零区域来减轻噪声放大。延迟电路不影响PA的输出功率或效率。传感器可以是PLL的控制电压对延迟响应的导数,从而利用辅助模数转换器(ADC)实现快速的片上校准。对于具有基于L-C的数控振荡器(DCO)的数字PLL,来自数字滤波器的数字词可被直接监测。也可通过使用外部信号分析器或接收器来测量相位噪声降级对天线端口处的编程延迟并最小化灵敏度,以确定延迟。当放置在开环波形中的Δf

图1是根据本记载的一个实施例的包含可编程延迟电路116的发射器电路100的简化框图,所述可编程延迟电路减轻由PA到VCO的耦合所引起的干扰。晶体振荡器(XO)102向相位频率检测器和电荷泵低通滤波器(PFD-CHP-LF)104的第一输入提供振荡输入频率信号FI。PFD-CHP-LF 104向电感器-电容器L-C VCO 106的输入提供控制电压V

FO被提供给LO分频器(LODIV)114的输入,所述LO分频器的输出向延迟电路116的输入提供LO信号。延迟电路116的输出向预驱动器电路118的输入提供经延迟的LO信号DLO,所述预驱动器电路的输出耦合到PA 120的输入。PA 120的输出耦合到匹配网络122的输入,所述匹配网络的输出通过天线端口提供给天线124。XO 102、PLL 112、LODIV 114、延迟电路116、预驱动器电路118和PA 120可集成在如所示出的半导体芯片150上,尽管XO 102的物理晶体可以是片外的并耦合到片上驱动器电路。匹配网络122和天线124被示出为片外地提供,如安装到印刷电路板(PCB)等(未示出)。然而,匹配网络122或天线122或两者均可在半导体芯片150上,这取决于操作频率和其它设计考虑。

第一调制器111接收第一数据DATA1,并将输出提供给MMD 110的输入。第一调制器111可用于仅适用于恒定包络调制方案的基于直接环内调制的发射器。第二调制器125接收第二数据DATA2,并且所述第二调制器的输出提供给发射基带电路126的输入,所述发射基带电路的输出提供给上变频混频器127的输入。发射基带电路126可包含数模转换和滤波功能。上变频混频器127接收DLO,并将输出提供给预驱动器电路118。第二调制器125可用于采用幅度调制方案、可变包络调制方案和/或恒定包络调制方案的线性上变频发射器。如所示出,第一调制器111和第二调制器125、发射基带电路126和上变频混频器127也可设置在半导体芯片150上。

在发射器电路100的一般操作中,由XO 102、PLL 112、LODIV 114和延迟电路116产生的DLO信号被预驱动器电路118(对于使用第一调制器111的方案)或被上变频混频器127直接使用,并且然后被预驱动器电路118(对于使用第二调制器125的方案)和PA 120使用,以输出RF信号,所述RF信号通过匹配网络122所提供以用于由天线124进行发射。匹配网络122在PA 120的输出与天线124之间提供阻抗匹配,以最大化功率发射效率。

发射器电路100通常表示在RF频率下操作的RF发射器,所述RF频率包含亚千兆赫(sub-GHz)、2.4GHz或5GHz,例如,Zigbee、Z波、Wi-Fi、蓝牙(包含蓝牙低能量或BLE)、蜂窝3G、4G-LTE(长期演进)等。对于一些配置,半导体芯片150的PA 120的输出功率可高达20分贝-毫瓦(dBm)。发射器电路100可支持各种调制方案,如恒定包络二进制相移键控(BPSK)、频移键控(FSK)、最小频移键控(MSK)、高斯MSK(GMSK)、偏移正交相移键控(O-QPSK)和/或可变包络方案,如QPSK、正交振幅调制(QAM)和正交频分复用(OFDM)。

常规的发射器电路不包含延迟电路116,使得在现有技术的配置中,LO信号通常直接提供给预驱动器电路118或上变频混频器127。如本文进一步描述的,磁耦合可发生在PA120与VCO 106的电感之间,无论是实际的无源电感器还是相应节段的载流回路,特别是当PA 120以高功率电平发射时。VCODIV 108和LODIV 114将VCO的频率除以因子N。当PA 120的第N个谐波耦合到VCO 106中时,PA到VCO的耦合可能对发射器电路100的基本操作有害。其可以影响V

所述耦合取决于从VCO 106到PA 120的VCO-PA延迟,示出为T

另外,耦合也受到操作温度的影响。特定设计的一批半导体芯片的采样可被表征以确定在可适用的操作温度范围内对温度的相对灵敏度。这用于对温度偏移存储器1004(图10)进行编程。处理电路系统132通过TEMP值来监测温度,并转换成用于选择温度偏移的选择值,以进一步微调延迟。TEMP值可由片上温度传感器(未示出)来提供,或可从测量环境温度的片外温度传感器(未示出)来导出。

有各种方法可用于校准发射器电路100的温度和频率。在一个实施例中,在校准操作期间监测V

图2是展示根据本记载的一个实施例的存在于PA 120与VCO 106之间的磁耦合的形象示意图。针对VCO 106的PA 120供应电流或输出电流耦合机制被建模为具有电感L

示出VCO 106的等效模型,其中电压源206由具有电容ΔC的电容器210和具有电导ΔG的电阻器212代替,所述电容器和所述电阻器与电感器204和电容器208并联耦合。用基尔霍夫电流定律(Kirchhoff's Current Law)(KCL)求解ΔC和ΔG,ΔC=-(M/L)α·cos(φ

图3示出根据本记载的一个实施例的在从0到2π的全周期(或ΔC的全周期)内绘制值ΔG、ΔC、Δf

已经确定,在过零点(如ZC1和ZC2)附近,由于在高增益区域中将噪声注入到VCO中,相位噪声降级变得严重。降级在过零点处达到最大值并且当操作通过延迟而移动远离过零点时对称地改善。以此方式,期望调整延迟电路116的延迟以避免ZC1和ZC2,并且尽可能实际上接近MAX。

图4包含根据本记载的一个实施例的绘制开环中的Δf

如图4所示出,对于开环中Δf

延迟电路116被设计为相对于VOSC信号的周期T

图5是根据本记载的一个实施例实施的延迟电路116的简化框图。LO信号被提供给差分(DIFF)电路502的输入,所述差分电路将单端LO信号转换成差分信号INN0/INP0。应当注意,对于已经以差分形式提供LO信号的一些配置,可不提供DIFF电路502。DSEL信号被示出为3位数字值DSEL<2:0>以实现从0(000b)到7(111b)的8种不同延迟设置的分辨率,其中“b”表示二进制值。DSEL<2:0>被提供给解码器504的相应的输入,所述解码器将DSEL<2:0>转换成一位有效(one-hot)选择值SEL_P<7:0>和一位(one-low)无效选择值SEL_N<7:0>。作为实例,对于DSEL<2:0>=001b,SEL_P<7:0>=00000001b和SEL_N<7:0>=11111110b。

如所示出,延迟电路116进一步包含一系列的8个延迟单元D7、D6、D5、D4、D3、D2、D1和D0(D7-D0)。每个延迟单元D7-D0包含一对输入I0和I1、选择输入SEL0、使能输入EN和输出O。延迟单元D7的I0输入、I1输入、SEL0输入和EN输入是INN0、VDD、SEL_P<7>和SEL_N<6>,并且延迟单元D7的输出O提供信号OP7(其中VDD表示逻辑高电平或逻辑1)。延迟单元D6的I0输入、I1输入、SEL0输入和EN输入是INP0、OP7、SEL_P<6>和SEL_N<5>,并且延迟单元D6的输出O提供信号OP6。延迟单元D5的I0输入、I1输入、SEL0输入和EN输入是INN0、OP6、SEL_P<5>和SEL_N<4>,并且延迟单元D5的输出O提供信号OP5。延迟单元D4的I0输入、I1输入、SEL0输入和EN输入是INP0、OP5、SEL_P<4>和SEL_N<3>,并且延迟单元D4的输出O提供信号OP4。延迟单元D3的I0输入、I1输入、SEL0输入和EN输入是INN0、OP4、SEL_P<3>和SEL_N<2>,并且延迟单元D3的输出O提供信号OP3。延迟单元D2的I0输入、I1输入、SEL0输入和EN输入是INP0、OP3、SEL_P<2>和SEL_N<1>,并且延迟单元D2的输出O提供信号OP2。延迟单元D1的I0输入、I1输入、SEL0输入和EN输入是INN0、OP2、SEL_P<1>和SEL_N<0>,并且延迟单元D1的输出O提供信号OP1。延迟单元D0的I0输入、I1输入、SEL0输入和EN输入是INP0、OP1、SEL_P<0>和VDD,并且将延迟单元D0的输出O耦合到反相器506的输入,所述反相器的输出提供经延迟LO信号DLO。

现在简要描述图5所示出的延迟电路116的操作。应当注意,延迟单元D7到D1中的每个延迟单元的输出被提供给相继的延迟单元的输入之一,以形成延迟单元的菊链,被称为延迟链。二进制值DSEL<2:0>标识延迟单元D7-D0中被激活的一个延迟单元,其中剩余的较高编号的延迟单元被有效地去激活,并且剩余的较低编号的延迟单元形成延迟链,以将经延迟信号从被激活的延迟单元向下传播到最后一个延迟单元D0。例如,二进制值DSEL<2:0>=111b激活延迟单元D7,并使剩余的延迟单元D6-D0能够进入到延迟链中,以将信号延迟总共7个延迟步长。二进制值DSEL<2:0>=100b激活延迟单元D4,去激活延迟单元D7-D5,并使剩余的延迟单元D3-D0能够进入到延迟链中,以将信号延迟总共4个延迟步长。二进制值DSEL<2:0>=000b仅激活最后一个延迟单元D0以实现最小延迟。

图6是根据本记载的一个实施例实施的延迟单元600的示意图,其可用作延迟单元D7-D0中的任何一个且高达所有延迟单元。I0输入和SEL0输入被提供给2输入布尔(Boolean)与非门602的相应输入,所述2输入布尔与非门的输出耦合到3输入布尔与非门(NAND)604中的一个输入。I1输入和EN输入被提供给与非门604的另外2个输入,所述与非门的输出提供延迟单元600的O输出。延迟单元D7-D0中的每个延迟单元可根据延迟单元600来配置。在一个实施例中,延迟单元600的延迟大约为17ps,因此使用总共7个延迟步长,实现了119ps的总延迟,这适合于在5GHz范围内使用VCO操作的大多数发射器电路。可针对任何发射器电路配置来调整延迟步长的数量和每个延迟单元的延迟。

图7是绘制根据图5和6的实施例所配置的延迟电路116的DSEL<2:0>信号的每个设置的DLO信号对时间的一个周期的幅度的简化图解图。第一曲线图针对DSEL<2:0>=000b、第二曲线图针对DSEL<2:0>=001b,依此类推,直到针对DSEL<2:0>=111b的最后的曲线图。在每个曲线图之间的延迟是延迟步长,直到从第一曲线图到最后的曲线图的全延迟。例如,延迟步长可以是17ps,直到总延迟为119ps。

图8是根据本记载的一个实施例的2个VCO周期(0到2T

沿着开环波形中的Δf

对于此配置,在25℃的室温下的未补偿操作位于区域A内的中心,使得接近室温的补偿是不必要的。因此,温度补偿意指增加零延迟,使得“补偿”操作是相同的,并且因此落在点802上。第四点814对应于在约-25℃的低温下的补偿操作,其在区域A内约在相位因子T

在更具体的实施例中,对于915MHz发射器(其频率划分因子N为6),VCO频率为约5.49GHz,使得T

图9是展示根据本记载的一个实施例的对于915MHz发射器,在约5.49GHz下操作的VCO的从-40℃到135℃的温度补偿的表格900。温度(TEMP以℃为单位)示出在相差10℃的子范围内,从-40℃到-35℃的5℃极度低温子范围除外。VCO-PA传播延迟T

传播延迟T

图10是根据本记载的一个实施例的与处理电路系统132介接的延迟控制器130的简化框图。延迟控制器130包含校准偏移存储器1002、温度偏移存储器1004和组合器1006。尽管校准偏移存储器1002和温度偏移存储器1004被示出为两个独立的存储器,但是已存储的信息可存储在同一存储器内。校准偏移存储器1002存储至少一个校准偏移,所述至少一个校准偏移包含用于每个可适用的操作频带的一个校准偏移。如所示出,示出用于第一频带的第一校准偏移CAL_FB1,直到用于最后频带的最后校准偏移CAL_FBM,其中M是0或更大的任何合适的整数。作为实例,可对800MHz的频带(例如,868MHz)执行一次Zigbee发射器的校准以提供CAL_FB1,并且再次对900MHz的频带(例如,915MHz)执行所述Zigbee发射器的校准,以提供第二校准偏移CAL_FB2(未示出)。根据可适用的操作频带数量,可存储任何数量的校准偏移值。例如,应当注意,对于2.4GHz Wi-Fi,可能仅需要1个校准偏移,如在落在2400MHz与2480MHz之间的总体操作频带的中间的2440MHz下执行的一个校准。

处理电路系统132确定适用于发射的频带,并向校准偏移存储器1002输出FBAND值。校准偏移存储器1002选择对应的校准偏移值,并将所选校准偏移值作为值CAL输出到组合器1006的一个输入。应当注意,如果仅确定一个校准偏移,例如Wi-Fi,则唯一的校准偏移值可被编程为CAL,并且处理电路系统132不需要提供FBAND值。

温度偏移存储器1004存储一组温度偏移值,每个温度偏移值对应于总体温度操作范围内的温度子范围。如图9所示出,例如,用于对未补偿传播延迟T

在一个实施例中,温度偏移存储器1004被存储为查找表(LUT)。处理电路系统132接收指示实际温度的TEMP值,并将对应的温度选择值T_SEL输出到温度偏移存储器1004。温度偏移存储器1004将所选温度偏移作为温度偏移值T_OFF输出到组合器1006的另一个输入。对于LUT配置,T_SEL可以是索引值。

如本文进一步描述的,针对一个或多个频带中的每个频带内的特定频率来确定校准偏移值中的每个校准偏移值。仍然,每个频带可包含具有对应的信道频率的多个信道,使得信道频率偏移FQ_OFF被确定在任何给定时间内用于调整在经校准值与实际发射频率之间的频率差。频率的调整是确定性的,使得处理电路系统132不是针对每个信道存储单独的频率调整值,而是基于在确定CAL值的频率与任何给定时间的实际发射频率之间的差来计算频率调整值FQ_OFF。因此,FQ_OFF值被计算并输出到组合器1006的另一个输入。

作为处理电路系统132如何可确定信道频率偏移FQ_OFF的实例,假设对于具有从VCO到PA的传播延迟T

调整后传播延迟T'

例如,如果发射器的未补偿传播延迟T

可针对930MHz执行类似的计算,其中ΔT

组合器1006将CAL值、T_OFF值、和FQ_OFF值组合在一起(如通过在此实例中相加,尽管可设想替代性的数学函数),并执行模函数(CAL+T_OFF+FQ_OFF)%D以确定所提供给延迟电路的延迟选择值。当延迟电路被配置为图5所示出的具有多达D=8个不同的延迟步长(包含0)的延迟电路116时,则模函数是(CAL+T_OFF+FQ_OFF)%8,并且延迟选择值DSEL<2:0>的范围为0到7。以此方式,延迟电路116由延迟控制器130编程,以在所选的频率和温度下针对特定配置(CAL值)进行校准,以补偿温度差,并补偿频率差。应当注意,偏移值中的一个或多个偏移值可以是负值。模函数确保增加的延迟值始终为正。

图11是展示根据本记载的一个实施例的用于确定要存储在温度偏移存储器1004中的温度偏移的表征过程的流程图。在第一框1102处,测试设备跨代表一批半导体芯片的所选一组半导体芯片的整个可适用操作温度范围来测量相对延迟。应当注意,不是给定批次中的每个芯片都可被表征;相反,仅所选子集被表征以代表整批相同类型的芯片。在下一个框1104处,温度偏移被编程到温度偏移存储器1004中,并且操作完成。

应当注意,表征不同于校准,这将在本文中进一步描述。相反,编程到温度偏移存储器1004中的温度偏移可相对于所选温度值,如35℃的中间温度值或任何其它合适的代表性温度值。室温或接近室温的代表性温度有利于测试。假设校准将在代表性温度下执行,使得每隔一个温度子范围的温度偏移是相对于代表性温度值。换言之,温度偏移是相对于代表性的中间温度值来进行,所述中间温度值是在校准程序期间进行校准。

图12是根据本记载的一个实施例的发射器电路100的校准程序的流程图。在第一框1202处,发射器电路100的PA 120在最大功率下、代表性温度值或中间温度值处(例如,25℃或35℃或任何其它合适的温度水平下)以及第一频带内的中间频率水平下操作。例如,对于800MHz频带,所选频率可以是868MHz;对于900MHz频带,所选频率可以是915MHz;并且对于2.4GHz,所选频率可以是2440MHz。

在下一个框1204处,在监测V

在下一个框1210处,询问是否应该校准另一个频带。如果是,则操作循环回到框1202,以重复确定下一个频带的CAL_FB值的整个程序,然后将所述CAL_FB值存储到校准偏移存储器1002中。当不存在要测试的另外频带时,或如果仅存在如在框1210处所确定的一个频带(例如,2.4GHz下的Wi-Fi),则操作完成。以此方式,存储到校准偏移存储器1002中的每个CAL_FB针对在可适用频带内的中间频率值和在中间温度值处来校准发射器电路100。

图13是展示发射器电路100的正常操作的流程图,所述正常操作用于更新延迟控制器130的校准值和偏移值,以在每次发射之前更新由延迟电路116实施的延迟。在第一框1302处,询问发射器电路100是否将要发射,这被称为PRE-TX。如果否,则操作循环回并等待下一次发射。当发射器电路100将要发射时,操作前进到框1304,其中处理电路系统132更新经提供给校准偏移存储器1002的FBAND值,以选择对应的CAL_FB值作为CAL偏移(例如,CAL_FB1、...、CAL_FBM中所选的一个)。如果仅存在一个可适用的FBAND和对应的CAL_FB值,则其被提供为CAL,并且此步骤可被省略。在下一个框1306处,处理电路系统132以用于校准的可适用频带的中间频率和适用于发射的所选频道为基础,计算如先前所描述的频率偏移值FQ_OFF。

在下一个框1308处,处理电路系统132读取TEMP值,并且然后确定并更新经提供给温度偏移存储器1004的温度选择值T_SEL,以输出对应的温度偏移值T_OFF。在温度偏移存储器1004未被实施为LUT的替代性实施例中,处理电路系统132简单地寻址被提供为T_OFF值的对应的温度偏移。在下一个框1310处,操作循环直到当前分组发射操作完成,并且然后操作循环回到框1302以等待下一次发射。

应当注意,滞后可由处理电路系统132(如在处理器的固件中编程或并入有限状态机等)或延迟控制器130在温度值的连续子范围之间实施,以避免在2个连续温度子范围之间跳跃。在一个实施例中,可在从一个子范围转变到另一个子范围之前配置小的重叠,并且相同的重叠或类似的重叠应用在相反的方向上。例如,当温度仅在TEMP指示25.5℃的时候上升时,操作可从15℃子范围转变到25℃子范围,但是当温度仅在TEMP指示14.5℃的时候下降时,操作可转变回15℃子范围。

已经呈现本描述以使本领域普通技术人员能够在特定应用和对应要求的背景下制造和使用本发明。然而,本发明并不旨在局限于本文所示出和描述的特定实施例,而是符合与本文所记载的原理和新颖特征一致的最宽范围。许多其它版本和变化是可能的和预期的。本领域技术人员应该理解,他们可容易地使用所记载的概念和具体实施例作为设计或修改其它结构的基础,以提供与本发明相同的目的,而不脱离本发明的精神和范围。

- 减轻功率放大器耦合压控振荡器所引起干扰的系统和方法

- 家庭网络传输线路的干扰减轻装置、干扰减轻方法及通信系统