半导体封装防磁结构

文献发布时间:2023-06-19 11:42:32

技术领域

本发明是关于一种半导体封装结构,特别是关于一种半导体封装防磁结构。

背景技术

小尺寸的集成电路封装单元一般是以成批方式建构于单一个矩阵式基底上;此矩阵式基底是预先定义出多个封装区域,其中每一个封装区域即用以建构一个封装单元。于完成封装胶体制程之后,接着即可进行一分割程序(singulation process),用以将矩阵式基底上所建构的封装单元总合结构体分割成个别的封装单元。以此种方式制造的封装单元例如包括薄型球栅数组式(Thin&Fine Ball Grid Array,TFBGA)封装单元、四边形平面无导脚式(Quad Flat No-lead,QFN)封装单元等等。

电磁干扰是一种电磁现象,一些电器、电子设备工作时所产生的电磁波,容易对周围的其他电气、电子设备形成电磁干扰,引发故障或者影响信号的传输。而且,过度的电磁干扰会形成电磁污染,危害周遭人们的身体健康。随着设备与结构的演进,要达到能够正常工作而不会相互发生电磁干扰造成性能改变和设备损坏的这种相互兼容的状态越来越难。为了使整体达到电磁兼容,必须以整体的电磁环境为依据,要求每个用电设备不产生超过一定限度的电磁发射,同时又要求用电设备本身要具备一定的抗干扰能力。只有对每一个用电设备都作出这两个方面的约束和改进,才能保证整体达到完全兼容。

发明内容

根据现有技术中所披露的问题,本发明半导体封装防磁结构的设计,可以防止电磁波以及增加整体封装结构的电性。

本发明的主要目的在于提供一种可以防止电磁波及增加整体封装结构的电性的半导体封装防磁结构。

根据上述目的,本发明提供一种半导体封装防磁结构,其特征在于,包含:基板、第一芯片、第一导线、胶层、第二芯片、金属薄膜与第二导线,其中基板还具有上表面和下表面以及多个贯穿上表面及下表面的电连接结构,同时在上表面及下表面之间具有一个窗口。另外,第一芯片设有主动面及背面,第一芯片的主动面朝下设置在基板的上表面上,而且第一芯片的部分主动面还暴露于窗口中,暴露于窗口的部分主动面与基板的电连接结构电性连接,同时第一导线通过暴露于窗口的部分将第一芯片的主动面与基板的下表面电性连接。接着,胶层设置于第一芯片的背面上,然后第二芯片设置在胶层上,藉由胶层使第二芯片固定在第一芯片的背面上。金属薄膜设置于第二芯片上,以及第二导线同时电性连接金属薄膜的上表面及基板的上表面上。

根据上述目的,本发明另外又提供一种半导体封装防磁结构,其特征在于,包含:基板、第一芯片、第一导线、胶层、第二芯片、金属薄膜、第二导线与封装结构,其中基板还具有上表面和下表面以及多个贯穿上表面及下表面的电连接结构。另外,第一芯片设有主动面及背面,第一芯片的背面朝下设置在基板的上表面上,而且第一芯片的主动面上还具有多个焊垫,同时第一导线分别电性连接第一芯片的主动面上的多个焊垫及基板的上表面。接着,胶层设置于第一芯片的主动面上且包覆第一导线,然后第二芯片设置在胶层上,接下来金属薄膜设置于第二芯片上,再来是第二导线同时电性连接金属薄膜的上表面及基板的上表面上。而封装结构设置在基板的上表面并且包覆了基板的部分上表面、金属薄膜与第二导线。

附图说明

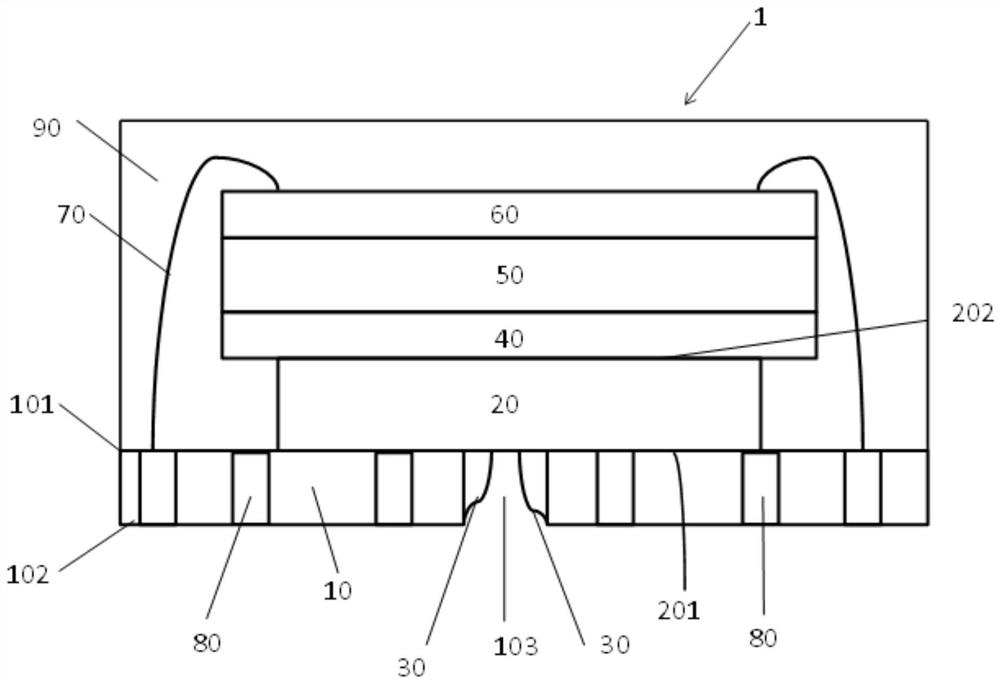

图1是根据本发明所披露的技术,表示半导体封装防磁结构的第一实施例示意图;

图2是根据本发明所披露的技术,表示半导体封装防磁结构的第二实施例示意图;

图3是根据本发明所披露的技术,表示半导体封装防磁结构的第三实施例示意图;

图4是根据本发明所披露的技术,表示半导体封装防磁结构的第四实施例示意图;

图5是根据本发明所披露的技术,表示半导体封装防磁结构的第五实施例示意图;

具体实施方式

为了使本发明的目的、技术特征及优点,能更为相关技术领域人员所了解,并得以实施本发明,在此配合所附的图式、具体阐明本发明的技术特征与实施方式,并列举较佳实施例进一步说明。以下文中所对照的图式,为表达与本发明特征有关的示意,并未亦不需要依据实际情形完整绘制。而关于本案实施方式的说明中涉及本领域技术人员所熟知的技术内容,亦不再加以陈述。

请参考图1,图1为半导体封装防磁结构的第一实施例示意图。如图1所示,本发明的半导体封装防磁结构1包含基板10、第一芯片20、第一导线30、胶层40、第二芯片50、金属薄膜60与第二导线70,其中基板10还具有上表面101和下表面102以及多个贯穿上表面101及下表面102的电连接结构80,同时在上表面101及下表面102之间具有一个窗口103。要说明的是,在基板10内的多个电连接结构80是利用内联机制程(interconnection process)来形成,其形成方式和电连接结构的功能与现有技术相同,也并非本发明的主要技术特征,故不多加陈述。另外,第一芯片20具有主动面201及背面202,且于主动面201上设有多个焊垫(未在图中表示)第一芯片20的主动面201朝下以覆晶(flip-chip)方式设置在基板10的上表面101上,而且第一芯片20的部分主动面201还暴露于窗口103中,暴露于窗口103的部分主动面201与基板10的电连接结构80彼此电性连接,同时第一导线30通过暴露于窗口103的部分将第一芯片20的主动面201与基板10的下表面102电性连接,具体来说是将第一导线30的一端连接于第一芯片20的主动面201上的焊垫(未在图中表示),而第一导线30的另一端则是经过窗口103连接于基板10的下表面102。接着,胶层40设置于第一芯片20的背面202上,然后第二芯片50设置在胶层40上,藉由胶层40使第二芯片50固定在第一芯片20的背面202上。金属薄膜60设置于第二芯片50上,以及第二导线70同时电性连接金属薄膜60的上表面及基板10的上表面101上。

接下来请继续参考图1,在另一实施例中,本发明的半导体封装防磁结构1包含基板10、第一芯片20、第一导线30、胶层40、第二芯片50、金属薄膜60、第二导线70与封装结构90,其中基板10还具有上表面101和下表面102以及多个贯穿上表面101及下表面102的电连接结构80,同时在上表面101及下表面102之间具有一个窗口103。另外,第一芯片20是一种功能芯片,其具有主动面201及背面202,第一芯片20的主动面201以覆晶方式朝下设置在基板10的上表面101上,而且第一芯片20的部分主动面201还暴露于窗口103中,暴露于窗口103的部分主动面201与基板10的电连接结构80电性连接,同时第一导线30通过暴露于窗口103的部分将第一芯片20的主动面201与基板10的下表面102电性连接,另外基板10的下表面102上还具有多个电性连接结构,其中基板10的下表面102上的电性连接结构为锡球(solder ball)或是晶圆凸块(solder bump)。接着,胶层40设置于第一芯片20的背面202上,然后第二芯片50设置在胶层40上,藉由胶层40使第二芯片50固定在第一芯片20的背面202上,其中第二芯片50的尺寸可以大于、小于或是等于第一芯片20的尺寸,以及第二芯片50可以是半导体裸片及硅芯片。金属薄膜60设置于第二芯片50上,以及第二导线70分别电性连接于金属薄膜60的上表面及基板10的上表面101上。而封装结构90包覆了基板10的部分上表面101、第二导线70、金属薄膜60、在窗口103内的第一导线30及暴露于窗口103的基板10的下表面102,在本发明中利用第二芯片50及其上方的金属薄膜60增加整体半导体封装防磁结构1的电性并且可以防止电磁波的干扰以提高半导体封装防磁结构1的工作效率。

再来请参考图2,图2为本发明的半导体封装防磁结构的第二实施例示意图。如图2所示,本发明的半导体封装防磁结构2包含基板12、第一芯片22、第一导线32、胶层42、第二芯片52、金属薄膜62、第二导线72与封装结构90,其中基板12还具有上表面121和下表面122以及多个贯穿上表面121及下表面122的电连接结构82。另外,第一芯片22具有主动面221及背面222,第一芯片22以主动面221朝上以背面222朝下的方式设置在基板12的上表面121上,而且第一芯片22的主动面221上还具有多个焊垫(未在图中表示),同时第一导线32分别电性连接第一芯片22的主动面221上的多个焊垫(未在图中表示)及基板12的上表面121。接着,胶层42设置于第一芯片22的主动面221上且包覆第一导线32,然后第二芯片52设置在胶层42上,接下来金属薄膜62设置于第二芯片52上,再来是第二导线72同时电性连接金属薄膜62的上表面及基板12的上表面121上。而封装结构90设置在基板12的上表面121并且包覆了基板12的部分上表面121、金属薄膜62与第二导线72。

接下来请继续参考图2,在另一实施例中,本发明的半导体封装防磁结构2包含基板12、第一芯片22、第一导线32、胶层42、第二芯片52、金属薄膜62、第二导线72与封装结构90,其中基板12还具有上表面121和下表面122以及多个贯穿上表面121及下表面122的电连接结构82。另外,第一芯片22是一种功能芯片,其具有主动面221及背面222,第一芯片22的背面222朝下设置在基板12的上表面121上,而且第一芯片22的主动面221上还具有多个焊垫(未在图中表示),同时第一导线32分别电性连接第一芯片22的主动面221上的多个焊垫(未在图中表示)及基板12的上表面121,另外基板12的下表面122上还具有多个电性连接结构(未在图中表示),其中基板12的下表面122上的电性连接结构为锡球(solder ball)或是晶圆凸块(solder bump)。接着,胶层42设置于第一芯片22的主动面221上且包覆第一导线32,然后第二芯片52设置在胶层42上,接下来金属薄膜62设置于第二芯片52上,其中第二芯片52的尺寸可以大于、小于或是等于第一芯片22的尺寸,以及第二芯片52可以是半导体裸片及硅芯片。然后,第二导线72同时电性连接金属薄膜62的上表面及基板12的上表面121上。而封装结构90设置在基板12的上表面121并且包覆了基板12的部分上表面121、金属薄膜62与第二导线72,增加整体半导体封装防磁结构2的电性。

再来请同时参考图2与图3,图3为本发明的半导体封装防磁结构的第三实施例示意图。如图3所示,本发明的半导体封装防磁结构2包含基板12、第一芯片22、第一导线32、胶层42、第二芯片52、金属薄膜62、第二导线72与封装结构90,其中图3的第三实施例与图2的第二实施例差别在于图3的第三实施例中,胶层42设置于第一芯片22的主动面221上,然后第二芯片52设置在胶层42上,接下来金属薄膜62设置于第二芯片52上,其中第二芯片52的尺寸小于第一芯片22的尺寸,然后第一导线32的一端电性连接第一芯片22的主动面221上的多个焊垫(未在图中表示)及第一导线32的另一端电性连接于基板12的上表面121,第二导线72的一端电性连接于金属薄膜62的上表面及另一端电性连接于基板12的上表面121上。

再来请同时参考图2与图4,图4为本发明的半导体封装防磁结构的第四实施例示意图。如图4所示,本发明的半导体封装防磁结构2包含基板12、第一芯片22、第一导线32、胶层42、第二芯片52、金属薄膜62、第二导线72与封装结构90,其中图4的第四实施例与图2的第二实施例差别在于图4的第四实施例中,胶层42设置于第一芯片22的主动面221上,然后第二芯片52设置在胶层42上,接下来金属薄膜62设置于第二芯片52上,其中第二芯片52的尺寸小于第一芯片22的尺寸,然后第一导线32的一端电性连接于金属薄膜62及另一端电性连接于第一芯片22的主动面221没有被胶层42覆盖的多个焊垫(未在图中表示)上及第二导线72的一端电性连接第一芯片22的多个焊垫上及另一端电性连接于基板12的上表面121。

再来请同时参考图2与图5,图5为本发明的半导体封装防磁结构的第五实施例示意图。如图5所示,本发明的半导体封装防磁结构2包含基板12、第一芯片22、第一导线32、胶层42、第二芯片52、金属薄膜62、第二导线72与封装结构90,其中图5的第五实施例与图2的第二实施例差别在于图5的第五实施例中,胶层42设置于第一芯片22的主动面221上,然后第二芯片52设置在胶层42上,接下来金属薄膜62设置于第二芯片52上,其中第二芯片52的尺寸小于第一芯片22的尺寸,然后在第一芯片22及第二芯片52的一侧(如图5的右侧),第一导线32的一端电性连接于第一芯片22的主动面221且没有被胶层42覆盖的多个焊垫(未在图中表示)上及另一端电性连接于基板12的上表面121。而在图5的左侧,第二导线72分别电性连接于金属薄膜62的上表面及基板12的上表面121上,而第一导线32则是分别电性连接第一芯片22的主动面221上未被胶层42所覆盖的多个焊垫及基板12的上表面121上。在图5的结构中,第一导线32及第二导线72与基板12、第一芯片22及金属薄膜62的打线方式为前述图3及图4的整合结构。

虽然本发明以前述之较佳实施例披露如上,然其并非用以限定本发明,任何熟习本领域技艺者,在不脱离本发明之精神和范围内,当可作些许之更动与润饰,因此其他未脱离本发明所揭示之精神下所完成的等效改变或修饰,均应包含在权利要求中。

- 半导体封装防磁结构

- 一种防磁柜防磁柜体结构