3D NAND闪存及其操作方法

文献发布时间:2023-06-19 13:46:35

技术领域

本发明涉及用于三维(3D)NAND闪存的编程方法和3D NAND闪存,并且更具体地,涉及能够减少3D NAND闪存的写入时间和功耗的3D NAND闪存的编程方法和3D NAND闪存。

背景技术

为了在写入操作中控制阈值电压并实施NAND闪存存储器的多个数据的存储,采取了增量步进脉冲编程(ISPP)技术。ISPP技术被配置为以阈值电压的编程验证操作在两次编程操作之间进行交错。通过编程验证操作的NAND闪存存储器的存储单元被执行抑制编程;未通过编程验证操作的NAND闪存存储器的存储单元先于ISPP技术发生。ISPP技术包括预充电阶段和编程阶段,其中,预充电阶段增强了沟道的耦合电势并减少了编程干扰。编程验证操作通常包括预脉冲阶段、读取阶段和预关断阶段,其中,预脉冲阶段和预关断阶段用于减少电子的注入。

对于具有垂直沟道的三维(3D)NAND闪存存储器,为了防止在编程验证操作中来自未选择串的电压的泄漏干扰,通常会关断未选择串的上选择栅,而未选择串的下选择栅被导通并共享。然而,对于未选择串,当与该未选择串的字线WLn相对应的存储单元处于编程过程中时,该字线WLn是选择字线并且由验证电压来验证。当验证电压小于存储单元的阈值电压时,选择存储单元的未选择串被切断,字线WLn和字线WLn+1之间的沟道电势差出现,并且由于字线WLn+1的电子注入而产生干扰。对于上述问题的常规解决方案是在验证阶段之前添加预脉冲阶段,但是由此增加了写入时间。因此,现有技术需要改进。

发明内容

本发明提供了用于3D NAND闪存的编程方法和3D NAND闪存,以减少3D NAND闪存的写入时间和功耗。

本发明的实施例公开了一种用于三维(3D)NAND闪存的编程方法,包括:对3D NAND闪存的未选择位线的选择字线进行编程;利用至少一个验证电压对选择字线执行第一验证过程;确定用于所述选择字线的第一验证过程的第一验证电压是否高于默认电压;以及当第一验证电压高于默认电压时,去除ISPP的预脉冲阶段;其中,第一验证电压为紧随在第一验证过程之后的验证电压。

本发明的另一个实施例公开了一种三维(3D)NAND闪存,其具有多条位线,其中,所述多条位线包括多个字线(WL)层,所述3D NAND闪存包括:选择位线;至少一个未选择位线;以及控制器,其被配置为对3D NAND的未选择位线的选择字线进行编程,利用至少一个验证电压对选择字线执行第一验证过程,确定用于所述选择字线的第一验证过程的第一验证电压是否高于默认电压,并且当第一验证电压高于默认电压时,去除ISPP的预脉冲阶段;其中,第一验证电压为紧随在第一验证过程之后的验证电压。

在阅读了以下在各个附图中示出的优选实施例的具体实施方式之后,本发明的这些和其他目的对于本领域的普通技术人员无疑将变得显而易见。

附图说明

图1是根据本发明的实施例的用于3D NAND闪存的编程过程的示意图。

图2是根据本发明的实施例的施加编程过程的3D NAND闪存的未选择位线的示意图。

图3是根据本发明的实施例的3D NAND闪存的未选择位线的沟道电势的分布的示意图。

图4是根据本发明的实施例的施加编程过程的3D NAND闪存的选择位串的波形图。

具体实施方式

预脉冲阶段包括在三维(3D)NAND闪存的增量步进脉冲编程(ISPP)中。ISPP的预脉冲阶段将未选择的上选择栅导通,以减小沟道电势差,这增加了3D NAND闪存的写入时间。

为了减少3D NAND闪存的写入时间,图1是根据本发明的实施例的用于3D NAND闪存的编程过程10的示意图。3D NAND闪存可以包括多条位线,其中,所述位线包括多个字线(WL)层。用于3D NAND闪存的编程过程10包括以下步骤:

步骤102:开始。

步骤104:对3D NAND闪存的未选择位线的选择字线进行编程。

步骤106:利用至少一个验证电压对选择字线执行第一验证过程。

步骤108:确定用于选择字线的第一验证过程的第一验证电压是否高于默认电压。如果是,则进行到步骤110;如果否,则进行到步骤104。

步骤110:当第一验证电压高于默认电压时,去除增量步进脉冲编程(ISPP)的预脉冲阶段。

步骤112:确定第一验证电压是否满足目标阈值电压。如果是,则进行到步骤120;如果否,则进行到步骤114。

步骤114:对3D NAND闪存的选择字线进行编程。

步骤116:对3D NAND闪存的选择字线执行第二验证过程。

步骤118:确定第二验证电压是否满足目标阈值电压。如果是,则进行到步骤120;如果否,则进行到步骤114。

步骤120:当第二验证过程的第二验证电压满足目标阈值电压时,抑制3D NAND闪存的选择字线。

步骤122:结束。

编程过程10可以由3D NAND闪存的控制器(在附图中未示出)执行。如图2所示,图2是根据本发明的实施例的施加编程过程10的3D NAND闪存的未选择位线的示意图,该未选择位线包括顶部选择栅TSG、多个上部字线层、字线WLn层、多个下部字线层和底部选择栅BSG。

由于3D NAND闪存的写入操作可以从顶部选择栅TSG或底部选择栅BSG的一端开始,因此,在实施例中,从底部选择栅BSG到顶部选择栅TSG将数据写入,但是不限于此。在其他实施例中,可以从顶部选择栅TSG到底部选择栅BSG开始3D NAND闪存的写入操作。

根据编程过程10,在步骤104中,对3D NAND闪存的未选择位线的选择字线WLn进行编程。

在实施例中,选择字线WLn由ISPP编程。在步骤106中,利用至少一个验证电压对选择字线WLn执行第一验证过程。例如,当3D NAND闪存是多级单元(MLC)3D NAND闪存时,可以基于第一验证过程,通过验证电压PV1、PV2、PV3将3D NAND闪存的存储单元编程为对应于位码11、10、01、00的四个状态,即编程状态P0、P1、P2、P3。在另一个实施例中,当3D NAND闪存是三级单元(TLC)3D NAND闪存时,可以基于第一验证过程,通过验证电压PV1-PV7将3DNAND闪存的存储单元编程为与位码111、110、010、011、001、000、100、101相对应的八个状态。因此,可以在编程状态P1、P2或P3下对MLC 3D NAND闪存的未选择位线的选择字线WLn进行编程。

在步骤108中,确定用于选择字线WLn的第一验证过程的第一验证电压是否高于默认电压。第一验证电压是第一验证过程的验证电压。例如,当MLC 3D NAND闪存的未选择位线的选择字线WLn被编程在编程状态P1下时,第一验证过程的第一验证电压为编程状态P2,并用于步骤108的确定。

在步骤110,当第一验证电压高于默认电压时,ISPP的预脉冲阶段被去除。相反,当第一验证电压低于或等于默认电压时,编程过程10进行到步骤104。

请参考图3,图3为根据本发明的实施例的3D NAND闪存的未选择位线的沟道电势的分布的示意图。图3示出了当选择字线WLn层通过没有预脉冲阶段的验证电压PV1、PV2和PV3时的沟道电势的分布以及当选择字线WLn层通过具有预脉冲阶段的任何验证电压时的沟道电势的分布。

因此,当第一验证电压在验证电压PV2与验证电压PV3之间时,减小验证电压PV3与具有预脉冲阶段的任何验证电压之间的差d1。另外,与差d2和d3相比,减少了未选择位线的从处于擦除状态的字线层WLn+1注入到处于编程状态的字线层WLn的电子。

在ISPP的预脉冲阶段被去除之后,在步骤114中,对3D NAND闪存的选择字线WLn进行编程。在步骤116中,对3D NAND闪存的选择字线WLn执行第二验证过程。第一验证过程基于验证电压PV1、PV2、PV3分别验证3D NAND闪存的存储单元,即从较低的编程状态到较高的编程状态,与第一验证过程不同,第二验证过程被配置为从较高编程状态到较低编程状态验证3D NAND闪存的存储单元。例如,如果在第一验证过程中在编程状态P0下对MLC 3DNAND闪存进行了编程,并且第一验证电压高于默认电压,则第二验证过程首先在编程状态P2下对MLC 3D NAND闪存进行验证,并且然后验证编程状态P1,这会减少MLC 3D NAND闪存的要在较低编程状态下进行验证的单元的数量。

在步骤118中,确定第二验证过程的第二验证电压是否高于目标阈值电压,其中,第二验证电压为第二验证过程的验证电压。例如,当在编程状态P2下对MLC 3D NAND闪存的未选择位线的选择字线WLn进行编程时,第二验证过程的第二验证电压为编程状态P3,并用于步骤118的确定。

当第二验证电压高于目标阈值电压时,编程过程10进行到步骤120。相反,当第二验证电压低于或等于目标阈值电压时,编程过程10进行到步骤114。

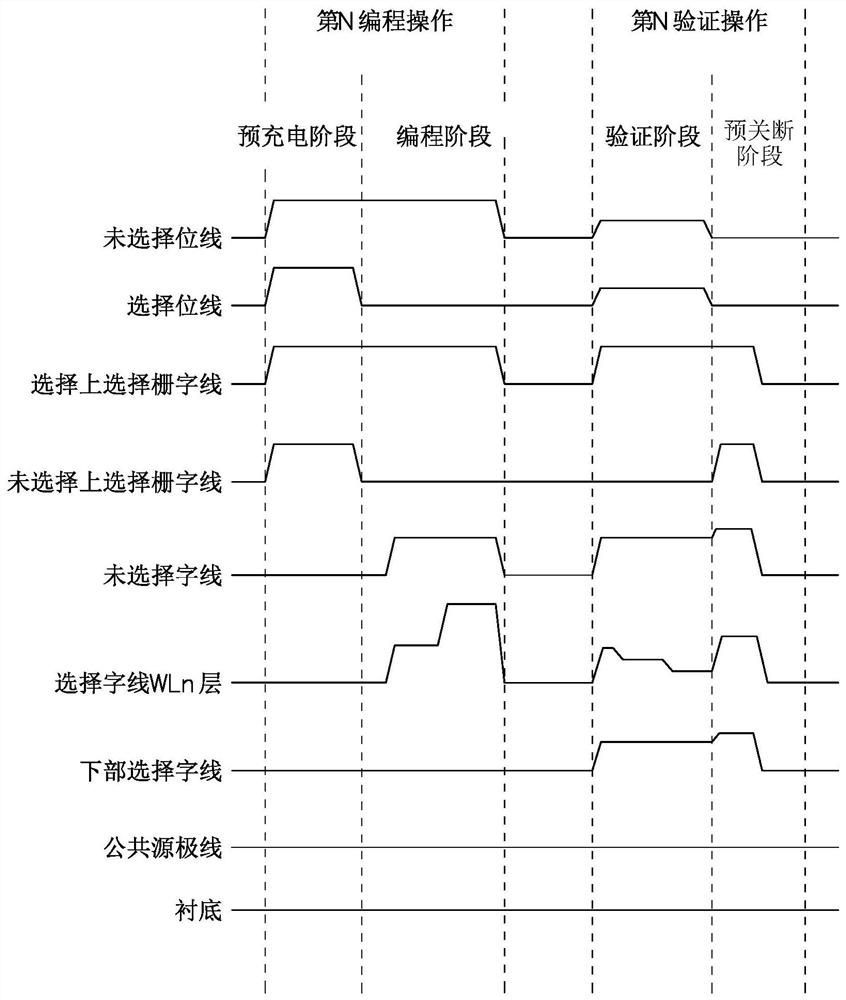

请参考图4,图4是根据本发明的实施例的施加编程过程10的3D NAND闪存的未选择位串的波形图。如图4所示,未选择位串包括未选择位线、选择位线、选择上选择栅字线、未选择字线、选择字线WLn层、下部选择字线、公共源极线和衬底。在图4中,在包括预充电阶段和编程阶段的第N编程操作之后,执行包括验证阶段和预关断阶段的第N验证操作。

如图4所示,去除了第N验证操作的预脉冲阶段,并且从较高编程状态到较低编程状态对选择字线WLn进行验证,这减少了3D NAND闪存的写入时间并减少了字线WLn+1和字线WLn之间的电子注入。这样,减少了干扰。

在步骤120中,当在步骤112中第一验证电压满足目标阈值电压时或在步骤118中第二验证过程的第二验证电压满足目标阈值电压时,禁止3D NAND闪存的选择字线WLn。

值得注意的是,上述实施例说明了本发明的概念,本领域技术人员可以相应地进行适当的修改,例如,其他种类的3D NAND闪存,例如,四级单元(QLC)和单级单元(SLC)都在本发明的范围内,并且不限于此。

总之,本发明提供了用于3D NAND闪存的编程方法和3D NAND闪存,其通过去除ISPP的预脉冲阶段而减少了3D NAND闪存的写入时间,并减少了功耗和字线层之间的电子注入。

本领域技术人员将容易地观察到,在保持本发明的教导的同时,可以对装置和方法进行多种修改和变更。因此,以上公开内容应被解释为仅由所附权利要求的界限来限定。

- 3D NAND闪存的操作方法和3D NAND闪存

- 3D NAND闪存的存储器系统及其操作方法