具有低功率合并读出模式的彩色-红外传感器

文献发布时间:2023-06-19 18:32:25

技术领域

本公开大体上涉及图像传感器,且特定来说而非排他地,涉及具有红外灵敏度及像素合并的彩色图像传感器。

背景技术

图像传感器已变得无处不在,且现在广泛应用于数码相机、蜂窝电话、安全相机以及医疗、汽车及其它应用中。随着图像传感器被集成到更广范围的电子装置中,期望通过装置架构设计及图像获取处理两者以尽可能多的方式(例如,分辨率、功耗、动态范围等)增强其功能性、性能指标及其类似者。用于制造图像传感器的技术继续在飞速发展。例如,对更高分辨率及更低功耗的需求鼓励这些装置的进一步小型化及集成化。

典型的互补金属氧化物半导体(CMOS)图像传感器响应于来自外部场景的图像光入射在图像传感器上而操作。图像传感器包含具有光敏元件(例如,光电二极管)的像素阵列,所述光敏元件吸收入射图像光的一部分并在吸收图像光之后产生图像电荷。由像素光生的图像电荷可经测量为列位线上的模拟输出图像信号,其依据入射图像光而变化。换句话说,所产生的图像电荷的量与图像光的强度成比例,所述图像电荷作为模拟信号从列位线读出并转换为数字值以产生表示外部场景的数字图像(即,图像数据)。

发明内容

本公开的方面涉及一种成像装置,其包括:像素阵列,其包含4x4像素电路分组,其中所述4x4像素电路分组包含所述像素阵列的四个行及四个列;及多个位线,其包含第一位线、第二位线、第三位线及第四位线,其中所述第一、第二、第三及第四位线中的每一者耦合到所述4x4像素电路分组中的相应四个像素电路,其中所述第一、第二、第三及第四位线中的每一者耦合到所述4x4像素电路分组的所有所述四个行及所有所述四个列。

本公开的另一方面涉及一种成像系统,其包括:像素阵列,其包含4x4像素电路分组,其中所述4x4像素电路分组包含所述像素阵列的四个行及四个列;多个位线,其包含第一位线、第二位线、第三位线及第四位线,其中所述第一、第二、第三及第四位线中的每一者耦合到所述4x4像素电路分组中的相应四个像素电路,其中所述第一、第二、第三及第四位线中的每一者耦合到所述4x4像素电路分组的所有所述四个行及所有所述四个列;控制电路,其耦合到所述像素阵列以控制所述像素阵列的操作;及读出电路,其耦合到所述像素阵列以通过所述多个位线从所述像素阵列读出信号,其中所述读出电路包含:位线开关电路,其耦合到所述第一、第二、第三及第四位线;及多个模/数转换器(ADC),其通过所述位线开关电路耦合到所述第一、第二、第三及第四位线。

附图说明

参考以下附图描述本发明的非限制性及非穷尽性实施例,其中除非另有指定,否则类似元件符号贯穿各种视图指代类似部分。

图1说明根据本发明的教示的具有像素阵列的成像系统的一个实例,所述像素阵列包含具有低功率合并读出模式的彩色及红外像素。

图2说明根据本发明的教示的包含耦合到具有低功率合并读出模式的读出电路的4x4彩色及红外像素分组的像素阵列的一个实例的更多细节。

图3说明根据本发明的教示的包含在包含彩色及红外像素的像素阵列的一个实例中的像素电路中的一者的实例示意图。

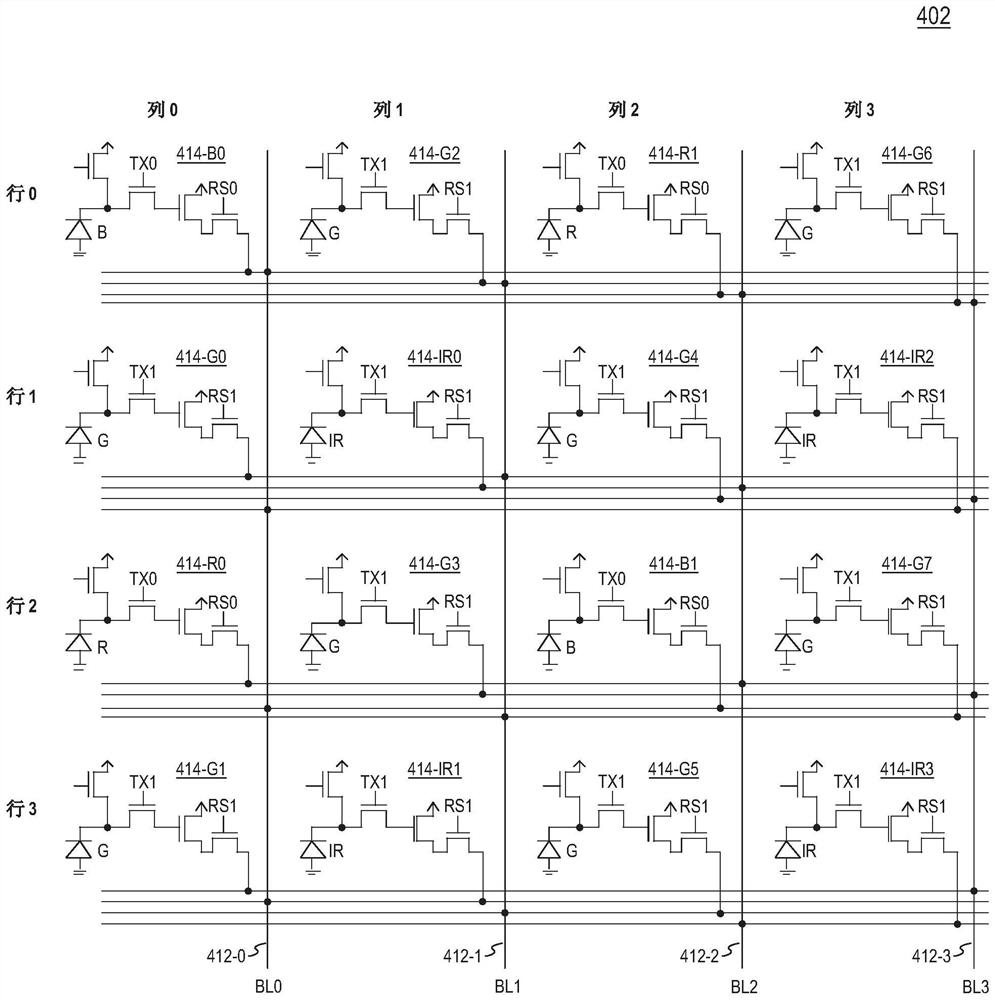

图4说明根据本发明的教示的耦合到包含在像素阵列的一个实例中的四个位线的4x4像素电路分组的一个实例布置,所述像素阵列包含耦合到具有低功率合并读出模式的读出电路的彩色及红外像素。

图5A说明根据本发明的教示的耦合到4x4像素电路分组的四个像素电路的第一位线的一个实例,4x4像素电路分组耦合到包含在像素阵列的一个实例中的四个位线,像素阵列包含耦合到具有低功率合并读出模式的读出电路的彩色及红外像素。

图5B说明根据本发明的教示的耦合到4x4像素电路分组的四个像素电路的第二位线的一个实例,4x4像素电路分组耦合到包含在像素阵列的一个实例中的四个位线,像素阵列包含耦合到具有低功率合并读出模式的读出电路的彩色及红外像素。

图5C说明根据本发明的教示的耦合到4x4像素电路分组的四个像素电路的第三位线的一个实例,4x4像素电路分组耦合到包含在像素阵列的一个实例中的四个位线,像素阵列包含耦合到具有低功率合并读出模式的读出电路的彩色及红外像素。

图5D说明根据本发明的教示的耦合到4x4像素电路分组的四个像素电路的第四位线的一个实例,4x4像素电路分组耦合到包含在像素阵列的一个实例中的四个位线,像素阵列包含耦合到具有低功率合并读出模式的读出电路的彩色及红外像素。

图6A说明根据本发明的教示的耦合到四个位线的实例位线开关电路及模/数转换器的第一行读出周期的一个实例,四个位线在全分辨率模式读出期间耦合到包含在像素阵列的一个实例中的4x4像素电路分组。

图6B说明根据本发明的教示的耦合到四个位线的实例位线开关电路及模/数转换器的第二行读出周期的一个实例,四个位线在全分辨率模式读出期间耦合到包含在像素阵列的一个实例中的4x4像素电路分组。

图6C说明根据本发明的教示的耦合到四个位线的实例位线开关电路及模/数转换器的第三行读出周期的一个实例,四个位线在全分辨率模式读出期间耦合到包含在像素阵列的一个实例中的4x4像素电路分组。

图6D说明根据本发明的教示的耦合到四个位线的实例位线开关电路及模/数转换器的第四行读出周期的一个实例,四个位线在全分辨率模式读出期间耦合到包含在像素阵列的一个实例中的4x4像素电路分组。

图7A说明根据本发明的教示的耦合到四个位线的实例位线开关电路及模/数转换器的第一行读出周期的一个实例,四个位线在低功率合并模式读出期间耦合到包含在像素阵列的一个实例中的4x4像素电路分组。

图7B说明根据本发明的教示的耦合到四个位线的实例位线开关电路及模/数转换器的第二行读出周期的一个实例,四个位线在低功率合并模式读出期间耦合到包含在像素阵列的一个实例中的4x4像素电路分组。

贯穿附图的若干视图,对应参考字符指示对应组件。所属领域的技术人员将了解,图中的元件是出于简单明了的目的而说明,且并不一定按比例绘制。例如,图中的一些元件的尺寸可相对于其它元件被夸大,以帮助提高对本发明的各种实施例的理解。此外,通常不描绘在商业上可行的实施例中有用或必要的共同但充分理解的元件,以便有助于对本发明的这些各种实施例的较少受阻碍的观察。

具体实施方式

本文描述涉及具有像素阵列的成像系统的实例,所述像素阵列包含具有低功率合并读出模式的彩色及红外像素。在以下描述中,阐述许多特定细节以提供对实例的透彻理解。然而,相关领域的技术人员将认识到,可在没有一或多个具体细节的情况下或用其它方法、组件、材料等实践本文中所描述的技术。在其它情况下,未展示或详细地描述众所周知的结构、材料或操作以避免模糊某些方面。

贯穿本说明书对“一个实例”或“一个实施例”的引用意指结合所述实例所描述的特定特征、结构或特性包含在本发明的至少一个实例中。因此,在贯穿本说明书的各个地方出现的短语“在一个实例中”或“在一个实施例中”并不一定都是指同一实例。此外,可在一或多个实例中以任何合适的方式组合特定特征、结构或特性。

为了便于描述,可在本文中使用空间上相对术语,例如“下面”、“下方”、“之上”“之下”、“上方”、“上部”、“顶部”、“底部”、“左侧”、“右侧”、“中心”、“中间”及其类似者,来描述如图所说明的一个元件或特征与另一(些)元件或特征的关系。应理解,除了图中所描绘的定向之外,空间上相对术语还希望涵盖装置在使用或操作中的不同定向。例如,如果图中的装置被旋转或翻转,那么被描述为在其它元件或特征“下方”或“下面”或“之下”的元件将被定向为在其它元件或特征“上方”。因此,示范性术语“下方”或“之下”可涵盖上方及下方两个定向。所述装置可以其它方式定向(旋转90度或处于其它定向),且本文中所使用的空间上相对描述词可相应地进行解释。此外,还将理解,当一元件被称为介于两个其它元件“之间”时,其可为两个其它元件之间的唯一元件,或也可存在一或多个中介元件。

贯穿本说明书,使用了若干技术术语。这些术语具有其所属领域中的普通含义,除非本文中有明确定义或其使用上下文另外清楚地指示。应注意,元素名称与符号可贯穿本文档互换地使用(例如Si对硅);然而,两者具有相同的含义。

将讨论具有像素阵列的成像系统的各种实例,所述像素阵列包含具有低功率合并读出模式的彩色及红外像素。在一个实例中,像素阵列包含4x4像素电路分组。4x4像素电路分组包含像素阵列的四个行及四个列。4x4分组是包含在像素阵列中的多个4x4像素电路分组中的一者。滤色器阵列安置在像素阵列之上。在一个实例中,滤色器阵列包含安置在相应的4x4像素电路分组上的4x4滤色器分组。在实例中,每一4x4滤色器分组包含具有第一色彩的两个滤色器、具有第二色彩的八个滤色器、具有第三色彩的两个滤色器及具有第四色彩的四个滤色器。在一个实例中,第一色彩是红色(R),第二色彩是绿色(G),第三色彩是蓝色(B),且第四色彩是红外(IR)。如将要展示的,滤色器以4x4滤色器分组布置成一图案,使得4x4滤色器分组的滤色器中的每一者邻近于像素阵列的同一行及/或同一列中具有不同色彩的另一滤色器。在实例中,成像装置还包含多个位线。每一4x4像素电路分组耦合到多个位线中的第一位线、第二位线、第三位线及第四位线。如将要展示的,第一、第二、第三及第四位线中的每一者耦合到4x4像素电路分组中的相应四个像素电路。第一、第二、第三及第四位线中的每一者耦合到4x4像素电路分组的所有四个行及所有四个列。读出电路耦合到像素阵列以读出像素阵列。读出电路包含位线开关电路及耦合到位线开关电路的模/数转换器(ADC)。在全分辨率模式读出中,四个ADC经配置以在四个行读出周期中通过第一、第二、第三及第四位线读出4x4像素电路分组中的所有像素电路。在低功率合并模式读出中,两个ADC经配置以在两个行读出周期中通过第一、第二、第三及第四位线读出4x4像素电路分组中的所有像素电路。

为了说明,根据本发明的教示,图1说明根据本发明的教示的具有像素阵列的成像系统100的一个实例,所述像素阵列包含具有低功率合并读出模式的彩色及红外像素。特定来说,成像系统100包含像素阵列102、控制电路110、读出电路106及功能逻辑108。在一个实例中,像素阵列102是像素电路114(例如,P0、P1、…、Pn)的二维(2D)阵列。如所描绘的实例中所说明,像素电路114在像素阵列102中布置成行(例如,R0、R1、…、Ry)及列(例如,C0、C1、…、Cy)以获取人、地点、物体等的图像数据或焦点数据,然后可使用这些图像数据来获取及呈现人、地点、物体等的2D图像。如将在下面的各种实例中所展示,滤色器阵列经安置在像素阵列之上。在各种实例中,滤色器阵列可包含红色(R)、绿色(G)、蓝色(B)及红外(IR)滤色器,其在像素阵列102的像素电路114之上布置成一图案。

在实例中,通过读出电路106从像素阵列102的像素电路114读出信号。被读出的信号可被放大、数字化,然后转移到功能逻辑108。因而,在各种实例中,读出电路106包含放大器、位线开关电路、模/数转换器(ADC)等,其耦合到位线112。功能逻辑108可存储图像数据或甚至通过应用后期图像效果(例如,裁剪、旋转、移除红眼、调整亮度、调整对比度等)来操纵图像数据。

如将在各种实例中所展示,根据本发明的教示,像素阵列102可由读出电路106在全分辨率模式读出或在低功率合并模式读出中读出。在全分辨率模式读出中,每一像素电路114可通过相应的位线112个别地读出,并使用耦合到每一位线的ADC进行数字化。在低功率合并模式读出中,可同时读出安置在相同色彩的滤色器下方的多个像素电路114以提供来自多个像素电路114的信号的经合并读出。因此,根据本发明的教示,减少了读出像素阵列102的所有像素电路114所需的行读出周期的数目及ADC的数目。在各种实例中,当读出通过使用源极跟随器合并耦合到同一位线112的像素电路114时,可执行竖直合并,且可通过将多个位线112耦合到读出电路106中单个ADC的相同输入来执行水平合并。

图2说明根据本发明的教示的像素阵列202的一个实例的更多细节,其包含耦合到具有低功率合并读出模式的读出电路的4x4彩色及红外像素分组。应了解,图2的像素阵列202可为展示如图1中所展示的像素阵列102的更多细节的实例,且上文描述的类似地命名及编号的元件在下文类似地耦合并起作用。

如图2中所描绘的实例中所展示,像素阵列202包含在像素阵列202中布置成行及列的多个像素电路214。特定来说,所描绘的实例展示像素阵列202包含多个4x4像素电路214分组,其在图2中用环绕4x4像素电路214分组中的每一者的深色实线指示。4x4像素电路分组中的每一者包含像素阵列的四个行及四个列。例如,4x4像素电路214分组中的第一者包含像素阵列202的行0到3及列0到3,而4x4像素电路214分组中的第二者包含像素阵列202的行0到3及列4到7,以此类推。

如所描绘的实例中所展示,位线开关电路232通过多个位线212耦合到像素阵列202。模/数转换器(ADC)234通过位线开关电路232耦合到位线212,以将从位线212接收到的模拟信号转换为数字信号。在一个实例中,位线开关电路232及ADC 234可被包含在读出电路(例如,读出电路106)中以从像素阵列202读出信号。如将要讨论的,在各种实例中,根据本发明的教示,像素阵列202可用全分辨率模式读出或以低功率合并模式读出来读取。

在一个实例中,多个位线212包含耦合到相应的4x4像素电路214分组的四个位线的分组。例如,在一个实例中,多个位线212中的位线BL0、BL1、BL2及BL3耦合到包含在像素阵列202的列0到3中的4x4像素电路214分组。类似地,多个位线212中的位线BL4、BL5、BL6及BL7耦合到包含在像素阵列202的列4到7中的4x4像素电路214分组。多个位线212中的位线BL8、BL9、BL10及BL11耦合到包含在像素阵列202的列8到11中的4x4像素电路214分组。多个位线212中的位线BL12、BL13、BL14及BL15耦合到包含在像素阵列202的列12到15中的4x4像素电路214分组。在其它实例中,应了解,像素阵列202可包含更多数目的4x4像素电路214分组,且图2的实例像素阵列202中所说明的16列像素电路214是出于解释目的而提供的。

图2中所说明的实例还说明滤色器阵列安置在像素阵列202的像素电路214之上。在实例中,滤色器阵列包含安置在相应的4x4像素电路214分组之上的4x4滤色器分组。在实例中,滤色器阵列包含具有四种不同色彩的滤色器,其在4x4像素电路214分组之上布置成马赛克图案。图2中描绘的四种色彩包含红色(R)、绿色(G)、蓝色(B)及红外(IR)。应了解,在其它实例中,其它色彩可用于滤色器阵列。

如图2中所描绘的实例中所展示,4x4像素电路214分组的奇数行号(例如,行1、行3等)安置在布置成绿色(G)、红外(IR)、绿色(G)及红外(IR)滤色器的图案的滤色器下方。4x4像素电路214分组的偶数行号(例如,行0、行2等)安置在布置成蓝色(B)、绿色(G)、蓝色(B)及绿色(G)或红色(R)、绿色(G)、红色(R)及绿色(G)滤色器的图案的滤色器下方,如所展示。

因而,应了解,在图2中所展示的实例中,每一4x4像素电路214分组安置在经布置以包含两个蓝色(R)滤色器、八个绿色(G)滤色器、两个蓝色(B)滤色器及四个红外(IR)滤色器的4x4滤色器分组下方。另外,滤色器中的每一者布置成邻近于像素阵列202的同一行或同一列中的不同色彩的另一滤色器,使得同一行或同一列中的两个邻近滤色器不具有相同的色彩。

图3说明根据本发明的教示的包含在实例像素阵列中的像素电路314的一个实例,所述实例像素阵列包含4x4彩色及红外像素分组。应了解,图3的像素电路314可为包含在如图2中所展示的像素阵列202中的像素电路214中的一者的实例,或包含在如图1中所展示的像素阵列102中的像素电路114中的一者的实例,且上文描述的类似地命名及编号的元件在下文类似地耦合并起作用。

在图3中所描绘的实例中,像素电路314包含耦合到转移晶体管316的光电二极管304。在各种实例中,光电二极管304经配置以通过如图2中所讨论的滤色器阵列的滤色器中的一者被照明。因而,光电二极管304经配置以响应于入射的红色(R)光、绿色(G)光、蓝色(B)光或红外(IR)光而光生电荷。在实例中,浮动扩散区318耦合到转移晶体管316。在一个实例中,浮动扩散电容器322耦合到浮动扩散区318,如所展示。在操作中,转移晶体管316经耦合以响应于转移控制信号TX而进行控制。因而,响应于入射光而在光电二极管304中光生的电荷响应于转移控制信号TX而被转移到浮动扩散区318。

继续图3中所描绘的实例,复位晶体管320耦合在电压供应器(例如,PIXVDD)与浮动扩散区318之间。在操作中,复位晶体管320经配置以响应于复位控制信号RST而复位像素电路314,包含浮动扩散区318中的电荷。

如所描绘的实例中所展示,源极跟随器晶体管324的栅极耦合到浮动扩散区318。在实例中,源极跟随器晶体管324的漏极耦合到电压供应器(例如,PIXVDD),且源极跟随器晶体管324的源极耦合到位线BL 312。在所描绘的实例中,行选择晶体管326耦合到源极跟随器晶体管324,使得源极跟随器晶体管324及行选择晶体管326耦合在电压供应器(例如,PIXVDD)与位线BL 312之间。

在操作中,当像素电路314被读出时,行选择晶体管326响应于行选择信号RS而接通,以产生由源极跟随器晶体管324响应于浮动扩散区318中的电荷而产生的输出信号328。输出信号328耦合到位线BL 312,且因此与来自可同时耦合到位线BL 312的其它像素314的任何其它输出信号328组合或竖直合并,以产生总输出信号330,如所展示。在全分辨率模式读出中,通过位线BL 312一次仅读出一个像素314,使得总输出信号330与来自个别像素电路314的输出信号328相同。在低功率合并模式读出中,耦合到位线BL 312的多个像素电路314被同时读出,且总输出信号330将等于来自当时正被读出的像素电路314的所有输出信号328的平均值。

图4说明根据本发明的教示的耦合到包含在像素阵列402的一个实例中的四个位线的4x4像素电路分组的一个实例布置,像素阵列402包含耦合到具有低功率合并读出模式的读出电路的彩色及红外像素。应了解,图4中所说明的4x4像素电路分组可为展示图2的像素阵列204的左上角中所展示的行0到3及列0到3中的4x4像素电路214分组的更多细节的实例,且上文描述的类似地命名及编号的元件在下文类似地耦合并起作用。应进一步了解,图4的实例像素阵列402中所说明的像素电路可为图3中详细描述的像素电路314的实例,且因此为了简洁起见,不再关于图4详细描述。

如图4的实例中所展示,像素阵列402包含包括四个行(例如,行0到3)及四个列(例如,列0到3)的4x4像素电路分组。明确来说,图4中所描绘的实例展示,行0列0处的像素电路414-B0包含经配置以用蓝色(B)光照明的光电二极管,行0列1处的像素电路414-G2包含经配置以用绿色(G)光照明的光电二极管,行0列2处的像素电路414-R1包含经配置以用红色(R)光照明的光电二极管,且行0列3处的像素电路414-G6包含经配置以用绿色(G)光照明的光电二极管。

行1列0处的像素电路414-G0包含经配置以用绿色(G)光照明的光电二极管,行1列1处的像素电路414-IR0包含经配置以用红外(IR)光照明的光电二极管,行1列2处的像素电路414-G4包含经配置以用绿色(G)光照明的光电二极管,且行1列3处的像素电路414-IR2包含经配置以用红外(IR)光照明的光电二极管。

行2列0处的像素电路414-R0包含经配置以用红色(R)光照明的光电二极管,行2列1处的像素电路414-G3包含经配置以用绿色(G)光照明的光电二极管,行2列2处的像素电路414-B1包含经配置以用蓝色(B)光照明的光电二极管,且行2列3处的像素电路414-G7包含经配置以用绿色(G)光照明的光电二极管。

行3列0处的像素电路414-G1包含经配置以用绿色(G)光照明的光电二极管,行3列1处的像素电路414-IR1包含经配置以用红外(IR)光照明的光电二极管,行3列2处的像素电路414-G5包含经配置以用绿色(G)光照明的光电二极管,且行3列3处的像素电路414-IR3包含经配置以用红外(IR)光照明的光电二极管。

所描绘的实例还说明耦合到包含在图4中的4x4像素电路分组的四个位线。四个位线包含位线BL0 412-0、位线BL1 412-1、位线BL2 412-2及位线BL3 412-3。如所展示,位线BL0 412-0、位线BL1 412-1、位线BL2 412-2及位线BL3 412-3中的每一者耦合到4x4像素电路分组中的相应四个像素电路。此外,位线BL0 412-0、BL1 412-1、BL2 412-2及BL3 412-3中的每一者耦合到4x4像素电路分组的所有四个行及所有四个列。换句话说,根据本发明的教示,位线BL0 412-0、BL1 412-1、BL2 412-2及BL3 412-3中的每一者耦合到4x4像素电路分组的所有行(例如,行0到3)及所有列(例如,列0到3)中的相应的像素电路。

在一个实例中,应了解,四个位线BL0 412-0、BL1 412-1、BL2 412-2及BL3 412-3中的每一者可通过在4x4像素电路分组中耦合到沿4x4像素电路分组的对角线的像素电路来耦合到4x4像素电路分组的每一行及每一列。例如,图4中所描绘的实例展示位线BL0412-0耦合到沿包含行0列0中的像素电路414-B0、行1列3中的像素电路414-IR2、行2列2中的像素电路414-B1及行3列1中的像素电路414-IR1的对角线包含的像素电路。位线BL1412-1耦合到沿包含行0列1中的像素电路414-G2、行1列0中的像素电路414-G0、行2列3中的像素电路414-G7及行3列2中的像素电路414-G5的对角线包含的像素电路。位线BL2 412-2耦合到沿包含行0列2中的像素电路414-R1、行1列1中的像素电路414-IR0、行2列0中的像素电路414-R0及行3列3中的像素电路414-IR3的对角线包含的像素电路。位线BL3 412-3耦合到沿包含行0列3中的像素电路414-G6、行1列2中的像素电路414-G4、行2列1中的像素电路414-G3及行3列0中的像素电路414-G1的对角线包含的像素电路。

图5A到5D说明展示根据本发明的教示的耦合到4x4像素电路分组的相应四个像素电路的第一位线BL0 512-0、第二位线BL1 512-1、第三位线BL2 512-2及第四位线BL3 512-3的更多细节的实例。应了解,如图5A到5D中所说明的第一位线BL0 512-0、第二位线BL1512-1、第三位线BL2 512-2及第四位线BL3 512-3,以及耦合其的相应四个像素电路可为如图4中所展示的第一位线BL0 412-0、第二位线BL1 412-1、第三位线BL2 412-2及第四位线BL3 412-3,以及耦合其的相应四个像素电路的实例,且上文描述的类似地命名及编号的元件在下文类似地耦合并起作用。

应进一步了解,图5A到5D中所说明的像素电路也可为如图3中所说明的像素电路314的实例。因而,图5A到5D中的每一像素电路包含光电二极管504,光电二极管504经配置以响应于入射的红色(R)光、绿色(G)光、蓝色(B)光或红外(IR)光而光生电荷。浮动扩散区518耦合到转移晶体管516,且在一个实例中,浮动扩散电容器522耦合到浮动扩散区518,如所展示。转移晶体管516经耦合以响应于转移控制信号(例如,TX0或TX1)而进行控制,以将光电二极管504中光生的电荷转移到浮动扩散区518。复位晶体管520耦合在电压供应器(例如,PIXVDD)与浮动扩散区518之间。复位晶体管520经配置以响应于复位控制信号RST而复位相应的像素电路。源极跟随器晶体管524的栅极耦合到浮动扩散区518。源极跟随器晶体管524的漏极耦合到电压供应器(例如,PIXVDD),且源极跟随器晶体管524的源极耦合到相应的位线(例如,BL0 512-0、BL1512-1、BL2 512-2或BL3 512-3)。行选择晶体管526耦合到源极跟随器晶体管524,使得源极跟随器晶体管524及行选择晶体管526耦合在电压供应器(例如,PIXVDD)与位线BL 512之间。行选择晶体管526响应于行选择信号(例如,RS0或RS1)而接通以将相应的输出信号528耦合到位线512。

现在具体参考图5A中所描绘的实例,第一位线BL0 512-0耦合到:行0列0的像素电路514-B0,其经配置以通过蓝色(B)滤色器用蓝色(B)光照明;行1列3的像素电路514-IR2,其经配置以通过红外(IR)滤色器用红外(IR)光照明;行2列2的像素电路514-B1,其经配置以通过蓝色(B)滤色器用蓝色(B)光照明;及像素电路514-IR1,其经配置以通过红外(IR)滤色器用红外(IR)光照明。因此,应了解,第一位线BL0 512-0耦合到四个像素电路,其中两者用蓝色(B)光照明,且其中两者用红外(IR)光照明。

在一个实例中,在像素阵列的全分辨率模式读出期间,可在第一行读出周期期间经由总输出信号530-0通过位线BL0 512-0从行0列0的像素电路514-B0读出输出信号528-B0。在全分辨率读出的第二行读出周期期间,可经由总输出信号530-0通过位线BL0512-0从行1列3的像素电路514-IR2读出输出信号528-IR2。在全分辨率读出的第三行读出周期期间,可经由总输出信号530-0通过位线BL0 512-0从行2列2的像素电路514-B1读出输出信号528-B1。在全分辨率读出的第四行读出周期期间,可经由总输出信号530-0通过位线BL0512-0从行3列1的像素电路514-IR1读出输出信号528-IR1。因此,应了解,在像素阵列的全分辨率模式读出期间,可在四个行读出周期中读出耦合到位线BL0 512-0的所有四个像素电路。

在一个实例中,在像素阵列的低功率合并模式读出期间,可在第一行读出周期期间经由总输出信号530-0通过位线BL0 512-0同时读出来自行0列0的像素电路514-B0的输出信号528-B0及来自行2列2的像素电路514-B1的输出信号528-B1。因而,蓝色(B)信号528-B1及528-B0两者可经由输出信号530-0在同一行读出周期中组合或合并并读出。应了解,根据本发明的教示,通过同时读出输出信号528-B0及528-B1,实现了竖直合并。出于本公开的目的,应了解,术语“竖直”合并适用于从同一个别位线(例如,位线BL0 512-0)上的多个像素电路(例如,像素电路514-B0及514-B1)同时接收的多个输出信号(例如,输出信号528-B0及528-B1)。换句话说,即使像素电路514-B0及像素电路514-B1物理上布置在4x4像素电路分组的不同列(例如,列0及列2)中,当输出信号528-B0及528-B1两者通过位线BL0 512同时读出时,像素电路514-B0及像素电路514-B1两者也被示意性地耦合到同一位线(例如,位线BL0 512)以出于本公开的目的实现“竖直”合并。如图4中所描绘的实例中所说明,响应于转移控制信号TX0、转移控制信号TX1及行选择信号RS0的断言,可从像素电路514-B0及像素电路514-B1同时读出输出信号528-B0及528-B1两者。另外,根据本发明的教示,通过在一个行读出周期中同时读出输出信号528-B0及528-B1两者,需要更少的行读出周期,这改进了速度及功耗。

继续图5A中所描绘的实例,在像素阵列的低功率合并模式读出的第二行读出周期期间,可经由总输出信号530-0通过位线BL0 512-0同时读出来自行1列3的像素电路514-IR2的输出信号528-IR2及来自行3列1的像素电路514-IR1的输出信号528-IR1。即使像素电路514-IR2及像素电路514-IR1物理上布置在4x4像素电路分组的不同列(例如,列3及列1)中,当输出信号528-IR2及528-IR1两者通过位线BL0 512同时读出时,像素电路514-IR1及像素电路514-IR1两者也被示意性地耦合到同一位线(例如,位线BL0 512)以出于本公开的目的实现“竖直”合并。如图4中所描绘的实例中所说明,响应于转移控制信号TX1及行选择信号RS1的断言,可从像素电路514-IR2及像素电路514-IR1同时读出输出信号528-IR2及528-IR1两者。因此,应了解,在像素阵列的低功率合并模式读出期间,耦合到位线BL0 512-0的所有四个像素电路可在两个行读出周期中读出。

如下文将更详细地描述的,除了通过从第一位线BL0 512-0同时读出输出信号528-IR2及528-IR1而提供的竖直合并之外,在一个实施例中,在第二行读出周期期间,可通过同时读出另外两个红外信号(例如,528-IR0及528-IR3)来进一步实现额外的水平合并,所述另外两个红外信号耦合到第三位线BL2 512-2,这将在下面的图5C中讨论。因此,出于本公开的目的,应了解,术语“水平”合并适用于从多个位线(例如,位线BL0 512-0及位线BL2 512-2)同时接收的多个输出信号(例如,输出信号528-IR2/528-IR1及输出信号528-IR0/528-IR3),即使同时被读出的像素电路可能或可能不一定物理上布置在4x4像素电路分组的同一行中。在实例中,根据本发明的教示,第一位线BL0 512-0及第三位线BL2 512-2两者通过位线开关电路耦合到同一模/数转换器的输入。因而,根据本发明的教示,所有四个红外(IR)信号可同时竖直合并及水平合并,并在同一行读出周期中读出。

现在具体参考图5B中所描绘的实例,第二位线BL1 512-1耦合到:行0列1的像素电路514-G2,其经配置以通过绿色(G)滤色器用绿色(G)光照明;行1列0的像素电路514-G0,其经配置以通过绿色(G)滤色器用绿色(G)光照明;行2列3的像素电路514-G7,其经配置以通过绿色(G)滤色器用绿色(G)光照明;及像素电路514-G5,其经配置以通过绿色(G)滤色器用绿色(G)光照明。因此,应了解,第二位线BL1 512-1耦合到四个像素电路,所有四个像素电路都用绿色(G)光照明。

在一个实例中,在像素阵列的全分辨率模式读出期间,可在第一行读出周期期间经由总输出信号530-1通过位线BL1 512-1从行0列1的像素电路514-G2读出输出信号528-G2。在全分辨率读出的第二行读出周期期间,可经由总输出信号530-1通过位线BL1 512-1从行1列0的像素电路514-G0读出输出信号528-G0。在全分辨率读出的第三行读出周期期间,可经由总输出信号530-1通过位线BL1 512-1从行2列3的像素电路514-G7读出输出信号528-G7。在全分辨率读出的第四行读出周期期间,可经由总输出信号530-1通过位线BL1512-1从行3列2的像素电路514-G5读出输出信号528-G5。因此,应了解,在像素阵列的全分辨率模式读出期间,可在四个行读出周期中读出耦合到位线BL0 512-1的所有四个像素电路。

在一个实例中,在像素阵列的低功率合并模式读出期间,来自行0列1的像素电路514-G2的输出信号528-G2,来自行1列0的像素电路514-G0的输出信号528-G0,来自行2列3的像素电路514-G7的输出信号528-G7,及来自行3列2的像素电路514-G5的输出信号528-G5可在单个行读出周期期间经由总输出信号530-1通过位线BL1 512-1同时读出。因而,耦合到位线BL1 512-1的所有四个绿色(G)信号528-G2、528-G0、528-G7 及528-G5可经由总输出信号530-1在同一行读出周期中组合或合并并读出。应了解,根据本发明的教示,通过同时读出输出信号528-G2、528-G0、528-G7及528-G5,实现了竖直合并。另外,根据本发明的教示,通过在单个行读出周期中同时读出所有四个输出信号528-G2、528-G0、528-G7及528-G5,需要更少的行读出周期,这改进了速度及功耗。因此,应了解,在像素阵列的低功率合并模式读出期间,可在单个行读出周期中读出耦合到位线BL1 512-1的所有四个像素电路。

如下文将更详细地描述的,除了通过从第二位线BL1 512-1同时读出输出信号528-G2、528-G0、528-G7及528-G5而提供的竖直合并之外,在一个实施例中,在同一行读出周期期间,可通过同时读出耦合到第四位线BL3 512-3的另外四个红外信号(例如,528-G6、528-G4、528-G3及528-G1)来进一步实现额外的水平合并,这将在下面的图5D中讨论。在实例中,根据本发明的教示,第二位线BL1 512-1及第四位线BL3 512-3两者通过位线开关电路耦合到同一模/数转换器的输入。因而,根据本发明的教示,所有八个绿色(G)信号可同时竖直合并及水平合并,并在同一行读出周期中读出。

现在具体参考图5C中所描绘的实例,第三位线BL2 512-2耦合到:行0列2的像素电路514-R1,其经配置以通过红色(R)滤色器用红色(R)光照明;行1列1的像素电路514-IR0,其经配置以通过红外(IR)滤色器用红外(IR)光照明;行2列0的像素电路514-R0,其经配置以通过红色(R)滤色器用红色(R)光照明;及像素电路514-IR3,其经配置以通过红外(IR)滤色器用红外(IR)光照明。因此,应了解,第三位线BL2 512-2耦合到四个像素电路,其中两者用红色(R)光照明,且其中两者用红外(IR)光照明。

在一个实例中,在像素阵列的全分辨率模式读出期间,可在第一行读出周期期间经由总输出信号530-2通过位线BL2 512-2从行0列2的像素电路514-R1读出输出信号528-R1。在全分辨率读出的第二行读出周期期间,可经由总输出信号530-2通过位线BL2512-2从行1列1的像素电路514-IR0读出输出信号528-IR0。在全分辨率读出的第三行读出周期期间,可经由总输出信号530-2通过位线BL2 512-2从行2列0的像素电路514-R0读出输出信号528-R0。在全分辨率读出的第四行读出周期期间,可经由总输出信号530-2通过位线BL2512-2从行3列3的像素电路514-IR3读出输出信号528-IR3。因此,应了解,在像素阵列的全分辨率模式读出期间,耦合到位线BL2 512-2的所有四个像素电路可在四个行读出周期中读出。

在一个实例中,在像素阵列的低功率合并模式读出期间,来自行0列2的像素电路514-R1的输出信号528-R1及来自行2列0的像素电路514-R0的输出信号528-R0可在第一行读出周期期间经由总输出信号530-2通过位线BL2 512-2同时读出。因而,红色(R)信号528-R1及528-R0两者可经由总输出信号530-2在同一行读出周期中组合或合并并读出。应了解,根据本发明的教示,通过同时读出输出信号528-R1及528-R0,实现了竖直合并。另外,根据本发明的教示,通过在一行读出周期中同时读出输出信号528-R1及528-R0两者,需要更少的行读出周期,这改进了速度及功耗。继续所述实例,在像素阵列的低功率合并模式读出的第二行读出周期期间,来自行1列1的像素电路514-IR0的输出信号528-IR0及来自行3列3的像素电路514-IR3的输出信号528-IR3可经由总输出信号530-2通过位线BL2 512-2同时读出。因此,应了解,在像素阵列的低功率合并模式读出期间,耦合到位线BL2 512-2的所有四个像素电路可在两个行读出周期中读出。

如上文所提及的,除了通过同时从第三位线BL2 512-2读出输出信号528-IR0及528-IR3而提供的竖直合并之外,在一个实施例中,在第二行读出周期期间,可通过同时读出另外两个红外信号(例如,528-IR2及528-IR1)来进一步实现额外的水平合并,所述另外两个红外信号耦合到第一位线BL0 512-0,如上面在图5A中所讨论的。在实例中,根据本发明的教示,第一位线BL0 512-0及第三位线BL2 512-2两者通过位线开关电路耦合到同一模/数转换器的输入。因而,根据本发明的教示,所有四个红外(IR)信号可同时竖直合并及水平合并,并在同一行读出周期中读出。

现在具体参考图5D中所描绘的实例,第四位线BL3 512-3耦合到:行0列3的像素电路514-G6,其经配置以通过绿色(G)滤色器用绿色(G)光照明;行1列2的像素电路514-G4,其经配置以通过绿色(G)滤色器用绿色(G)光照明;行2列1的像素电路514-G3,其经配置以通过绿色(G)滤色器用绿色(G)光照明;及像素电路514-G1,其经配置以通过绿色(G)滤色器用绿色(G)光照明。因此,应了解,第四位线BL3 512-3耦合到四个像素电路,所有四个像素电路都用绿色(G)光照明。

在一个实例中,在像素阵列的全分辨率模式读出期间,可在第一行读出周期期间经由总输出信号530-3通过位线BL1 512-3从行0列3的像素电路514-G6读出输出信号528-G6。在全分辨率读出的第二行读出周期期间,可经由总输出信号530-3通过位线BL3 512-3从行1列2的像素电路514-G4读出输出信号528-G4。在全分辨率读出的第三行读出周期期间,可经由总输出信号530-3通过位线BL3 512-3从行2列1的像素电路514-G3读出输出信号528-G3。在全分辨率读出的第四行读出周期期间,可经由总输出信号530-3通过位线BL3512-3从行3列0的像素电路514-G1读出输出信号528-G1。因此,应了解,在像素阵列的全分辨率模式读出期间,可在四个行读出周期中读出耦合到位线BL3 512-3的所有四个像素电路。

在一个实例中,在像素阵列的低功率合并模式读出期间,来自行0列3的像素电路514-G6的输出信号528-G6,来自行1列2的像素电路514-G4的输出信号528-G4,来自行2列1的像素电路514-G3的输出信号528-G3,及来自行3列0的像素电路514-G1的输出信号528-G1可在单个行读出周期期间经由总输出信号530-3通过位线BL3 512-3同时读出。因而,耦合到位线BL3 512-3的所有四个绿色(G)信号528-G6、528-G4、528-G3及528-G1可经由总输出信号530-3在同一行读出周期中组合或合并并读出。应了解,根据本发明的教示,通过同时读出输出信号528-G6、528-G4、528-G3及528-G1,实现了竖直合并。另外,根据本发明的教示,通过在单个行读出周期中同时读出所有四个输出信号528-G6、528-G4、528-G3及528-G1,需要更少的行读出周期,这改进了速度及功耗。因此,应了解,耦合到位线BL3 512-3的所有四个像素电路可在像素阵列的低功率合并模式读出期间在单个行读出周期中读出。

如上文所提及的,除了通过从第四位线BL3 512-3同时读出输出信号528-G6、528-G4、528-G3及528-G1而提供的竖直合并之外,在同一行读出周期期间,可通过同时读出另外四个红外信号(例如,528-G2、528-G0、528-G7及528-G5)来进一步实现额外的水平合并,所述另外四个红外信号耦合到第二位线BL1 512-1,如上面在图5B中所讨论的。在实例中,根据本发明的教示,第二位线BL1 512-1及第四位线BL2 512-3两者通过位线开关电路耦合到同一模/数转换器的输入。因而,根据本发明的教示,所有八个绿色(G)信号可同时竖直合并及水平合并,并在同一行读出周期中读出。

图6A到6D说明根据本发明的教示的包含于在全分辨率模式读出期间耦合到四个位线BL0 612-0到BL3 612-3的读出电路中的位线开关电路632及模/数转换器(ADC)ADC0634-0到ADC3 634-3的实例。应了解,图6A到6D中所说明的包含实例位线开关电路632及模/数转换器(ADC)ADC0 634-0到ADC3 634-3的读出电路可为图1中所说明的读出电路106的实例,且上文描述的类似地命名及编号的元件在下文类似地耦合并起作用。应进一步了解,图6A到6D中所提及的实例位线BL0 612-0到BL3 612-3可为图4中所提及的位线BL0 412-0到BL3 412-3的实例,或图5A到5D中所提及的位线BL0 512-0到BL3 512-3的实例,且上文描述的类似地命名及编号的元件在下文类似地耦合并起作用。

下面的表1总结根据本发明的教示的用于执行4x4像素电路分组的全分辨率模式读出的四个行读出周期(RRP)的实例,所述四个行读出周期在下面的图6A到6D中进一步说明。

表1

如上面的表1中所总结的,在第一行读出周期(例如,RRP 0)期间,读出行0,针对行0断言TX0及TX1信号(例如,参见图5A到5D),并针对行0断言RS0及RS1信号(例如,参见图5A到5D),ADC0数字化来自BL0的蓝色(B)信号,ADC1数字化来自BL1的绿色(G)信号,ADC2数字化来自BL2的红色(R)信号,且ADC3数字化来自BL3的绿色(G)信号。

在第二行读出周期(例如,RRP 1)期间,读出行1,针对行1断言TX1信号(例如,参见图5A到5D),并针对行1断言RS1信号(例如,参见图5A到5D),ADC0数字化来自BL2的红外(IR)信号,ADC1数字化来自BL1的绿色(G)信号,ADC2数字化来自BL0的红外(IR)信号,且ADC3数字化来自BL3的绿色(G)信号。

在第三行读出周期(例如,RRP 2)期间,读出行2,针对行2断言TX0及TX1信号(例如,参见图5A到5D),并针对行2断言RS0及RS1信号(例如,参见图5A到5D),ADC0数字化来自BL2的红色(R)信号,ADC1数字化来自BL3的绿色(G)信号,ADC2数字化来自BL0的蓝色(B)信号,且ADC3数字化来自BL1的绿色(G)信号。

在第四行读出周期(例如,RRP 3)期间,读出行3,针对行3断言TX1信号(例如,参见图5A到5D),并针对行3断言RS信号(例如,参见图5A到5D),ADC0数字化来自BL0的红外(IR)信号,ADC1数字化来自BL3的绿色(G)信号,ADC2数字化来自BL2的红外(IR)信号,且ADC3数字化来自BL1的绿色(G)信号。

为了说明,现在具体参考图6A中所描绘的实例,位线开关电路632经配置以将第一位线BL0 612-0耦合到ADC0 634-0以输出数字D

现在具体参考图6B中所描绘的实例,位线开关电路632经配置以将第一位线BL0612-0耦合到ADC2 634-2以输出数字D

现在具体参考图6C中所描绘的实例,位线开关电路632经配置以将第一位线BL0612-0耦合到ADC2 634-2以输出数字D

现在具体参考图6D中所描绘的实例,位线开关电路632经配置以将第一位线BL0612-0耦合到ADC0 634-0以输出数字D

应注意,根据本发明的教示,图6A到6D中针对位线开关电路632所说明的用于全分辨率模式读出的四个行读出周期的耦合方案是出于解释目的而提供的,且可使用用于四个行读出周期的其它耦合方案。应进一步注意,在图6A到6D中针对位线开关电路632所说明的耦合方案中,绿色(G)通道数据总是由奇数的模/数转换器(例如,ADC1 634-1或ADC3 634-3)产生。

图7A到7B说明根据本发明的教示的包含于在低功率合并模式读出期间耦合到四个位线BL0 712-0到BL3 712-3的读出电路中的位线开关电路732及模/数转换器(ADC)ADC0734-0到ADC3 734-3的实例。应了解,图7A到7B中所说明的包含实例位线开关电路732及模/数转换器(ADC)ADC0 734-0到ADC3 734-3的读出电路可为图1中所说明的读出电路106的实例,且上文描述的类似地命名及编号的元件在下文类似地耦合并起作用。应进一步了解,图7A到7B中所提及的实例位线BL0 712-0到BL3 712-3可为图4中所提及的位线BL0 412-0到BL3 412-3的实例,或图5A到5D中所提及的位线BL0 512-0到BL3 512-3的实例,且上文描述的类似地命名及编号的元件在下文类似地耦合并起作用。

下面的表2总结根据本发明的教示的用于执行4x4像素电路分组的低功率合并模式读出的两个行读出周期(RRP)的实例,所述两个行读出周期在下面的图7A到7B中进一步说明。

表2

如上面的表1中所总结的,4x4像素电路分组在低功率合并模式读出中以两个行读出周期读出而不是四个行读出周期读出,这减少了功耗。此外,ADC1及ADC3两者在两个读出周期期间都断电,这进一步减少了功耗。

在第一行读出周期(例如,RRP 0)期间,读出行0及行2,针对BL0及BL2的行0及2断言TX0信号(例如,参见图5A到5D)。针对BL0及BL2的行0及2断言RS0信号(例如,参见图5A到5D)。ADC0数字化来自BL0的竖直合并蓝色(B)信号,ADC1断电,ADC2数字化来自BL2的竖直合并红色(R)信号,且ADC3断电。

在第二行读出周期(例如,RRP 1)期间,读出行0到3,针对BL1及BL3的行0到3以及BL0及BL2的行1及3断言TX1信号(例如,参见图5A到5D)。针对BL1及BL3的行0到3以及BL0及BL2的行1及3断言RS1信号(例如,参见图5A到5D)。ADC0耦合到BL0及BL2两者,这导致BL0及BL2的平均值被数字化以产生来自BL0及BL2的竖直及水平合并的红外(IR)信号,ADC1断电,ADC2耦合到BL1及BL3两者,这导致BL1及BL3的平均值被数字化以产生来自BL1及BL3的竖直及水平合并的绿色(G)信号,且ADC3数字化来自BL3的绿色(G)信号。

为了说明,具体参考图7A中所描绘的实例,在4x4像素电路分组的低功率合并模式读出的第一行读出周期期间,位线开关电路732经配置以将第一位线BL0 712-0耦合到ADC0734-0以输出数字D

具体参考图7B中所描绘的实例,在4x4像素电路分组的低功率合并模式读出的第二行读出周期期间,位线开关电路732经配置以将第一位线BL0 712-0及第三位线BL2 712-2耦合到ADC0 734-0以输出数字D

对本发明所说明的实例的上述描述,包含摘要中所描述的内容,并不希望为穷尽性的,也不希望将本发明限于所公开的精确形式。虽然本文中出于说明性目的而描述本发明的特定实例,但如相关领域的技术人员将认识到的,在本发明的范围内可进行各种修改。

根据上述详细描述,可对本发明进行这些修改。所附权利要求书中所使用的术语不应被解释为将本发明限于本说明书中所公开的特定实例。而是,本发明的范围将完全由所附权利要求书确定,所述权利要求书将根据权利要求书解释的既定原则来解释。

- 具有气体传感器和低功率模式的便携式传感器设备

- 具有气体传感器和低功率模式的便携式传感器设备