发光显示设备以及包括发光显示设备的多屏显示设备

文献发布时间:2024-01-17 01:13:28

相关申请的交叉引用

本申请要求2021年12月23日提交的韩国专利申请No.10-2021-0186120的权益,在此通过引用将其并入本文,如同在本文完全阐述一样。

技术领域

本发明涉及一种发光显示设备以及包括发光显示设备的多屏显示设备。

背景技术

不同于液晶显示(LCD)设备,作为自发光显示设备的发光显示设备不需要单独光源,因此其可被制造为轻且薄。此外,发光显示设备以低压进行驱动,因此功耗降低。此外,发光显示设备在颜色实现、响应时间、视角和对比度方面较佳,因此作为下一代显示设备吸引了大量关注。

发光显示设备基于发光器件层的发光来显示图像,其中发光器件层包括插置在两个电极之间的发光器件。在这种情形下,由发光器件发射的光经由电极和基板释放到外部。

发光显示设备包括被实现为显示图像的显示面板。显示面板可包括:显示部,其包括用于显示图像的多个像素;以及围绕显示部的边框区。

相关技术的发光显示设备可需要用于遮盖位于显示面板的边缘(或外围部)处的边框区的边框(或机构),并且由于边框区的宽度,可增加边框宽度。

近来,多屏显示设备已被商业化,其中通过将多个发光显示设备布置成格子形式(lattice type)来实现大屏幕。

但是,在相关技术的多屏显示设备中,由于多个发光显示设备的每一个的边框区或边框,诸如接缝(seam)之类的边界部形成在相邻的发光显示设备之间。当一个图像显示在多屏显示设备的整个屏幕上时,边界部可导致图像的不连续感(或断续感),由此,可降低观看图像的观看者的沉浸度。

发明内容

因此,本发明旨在提供一种基本上克服了由于相关技术的限制和缺点而导致的一个或多个问题的发光显示设备以及包括发光显示设备的多屏显示设备。

本发明的一个方面旨在提供一种具有零边框宽度的发光显示设备以及包括发光显示设备的多屏显示设备。

本发明的另一方面旨在提供一种发光显示设备以及包括发光显示设备的多屏显示设备,其可具有零边框宽度并且可最小化或减小由于水分(或湿气)的渗透导致的自发光器件的可靠性降低。

本发明的又一方面旨在提供一种发光显示设备以及包括发光显示设备的多屏显示设备,其可检测用于连接前焊盘和后焊盘的布线之间的电短路。

本发明的又一方面旨在提供一种发光显示设备以及包括发光显示设备的多屏显示设备,其可最小化或减小由于用于连接前焊盘和后焊盘的布线之间的电阻偏差导致的图像质量降低。

本发明的又一方面旨在提供一种发光显示设备以及包括发光显示设备的多屏显示设备,其可具有零边框宽度并且可保护像素电路免受静电的影响。

本发明的目的不限于上述目的,本文未描述的其他目的对于所属领域技术人员来说根据下文描述将清楚地理解。

本发明的附加特点和方面将在下文描述中部分地阐述,部分地根据下文描述将变得显而易见,或者可通过本文提供的公开构思的实践而获悉。公开构思的其他特点和方面可通过书面说明及其衍生物以及权利要求书和附图中具体指出的结构来实现和获得。

为了实现公开构思的这些和其他方面,如在此具体化和广义描述的,如在此具体化和广义描述的,一种发光显示设备包括:基板;显示部,所述显示部包括设置在所述基板上的多条像素驱动线以及连接至所述多条像素驱动线的多个像素;发光器件层,所述发光器件层包括设置在所述显示部处的自发光器件;堰部,所述堰部沿着所述基板的外围部设置,所述堰部包括具有金属线的至少一个堰;封装层,所述封装层被设置为覆盖所述发光器件层,所述封装层包括由所述堰部在至少四个边围绕的有机封装层;多个开关电路部,所述开关电路部被设置为与所述至少一个堰交叠并且连接至所述多条像素驱动线;以及前焊盘部,所述前焊盘部包括设置在所述基板的外围部处并且与所述多条像素驱动线以及所述至少一个堰的金属线电连接的多个前焊盘,所述多个开关电路部的每一个包括第一开关电路和第二开关电路,所述第一开关电路和所述第二开关电路的每一个包括与所述至少一个堰的金属线电连接的栅极。

在本发明的另一方面,一种多屏显示设备包括多个显示设备,所述多个显示设备沿着第一方向和与所述第一方向交叉的第二方向中的至少一个方向设置,所述多个显示设备的每一个包括发光显示设备,所述发光显示设备包括:基板;显示部,所述显示部包括设置在所述基板上的多条像素驱动线以及连接至所述多条像素驱动线的多个像素;发光器件层,所述发光器件层包括设置在所述显示部处的自发光器件;堰部,所述堰部沿着所述基板的外围部设置,所述堰部包括具有金属线的至少一个堰;封装层,所述封装层被设置为覆盖所述发光器件层,所述封装层包括由所述堰部在至少四个边围绕的有机封装层;多个开关电路部,所述开关电路部被设置为与所述至少一个堰交叠并且连接至所述多条像素驱动线;以及前焊盘部,所述前焊盘部包括设置在所述基板的外围部处并且与所述多条像素驱动线以及所述至少一个堰的金属线电连接的多个前焊盘,所述多个开关电路部的每一个包括第一开关电路和第二开关电路,所述第一开关电路和所述第二开关电路的每一个包括与所述至少一个堰的金属线电连接的栅极。

在本发明的又一方面,一种发光显示设备包括:显示部,所述显示部包括设置在基板上的多条像素驱动线以及选择性地连接至所述多条像素驱动线的多个像素;发光器件层,所述发光器件层设置在所述显示部处;堰部,所述堰部包括具有金属线的至少一个堰;多个开关电路部,所述开关电路部被设置为与所述至少一个堰交叠并且选择性地连接至所述多条像素驱动线;以及前焊盘部,所述前焊盘部包括与所述多条像素驱动线以及所述至少一个堰的金属线电连接的多个前焊盘,所述多个开关电路部的每一个包括第一开关电路和第二开关电路,所述第一开关电路和所述第二开关电路的每一个包括与所述至少一个堰的金属线电连接的栅极。

根据本发明各示例的除了用于解决上述问题的方式之外的具体细节包括在下文的说明和附图中。

根据本发明的实施方式,可提供一种具有零边框宽度的发光显示设备以及包括发光显示设备的多屏显示设备。

根据本发明的实施方式,可提供一种发光显示设备以及包括发光显示设备的多屏显示设备,其可具有零边框宽度并且可最小化或减小由于水分(或湿气)的渗透导致的自发光器件的可靠性降低。

根据本发明的实施方式,可提供一种发光显示设备以及包括发光显示设备的多屏显示设备,其可检测用于连接前焊盘和后焊盘的布线之间的电短路。

根据本发明的实施方式,可提供一种发光显示设备以及包括发光显示设备的多屏显示设备,其可最小化或减小由于用于连接前焊盘和后焊盘的布线之间的电阻偏差导致的图像质量降低。

根据本发明的实施方式,可提供一种发光显示设备以及包括发光显示设备的多屏显示设备,其可具有零边框宽度并且可保护像素电路免受静电的影响。

根据本发明的实施方式,可提供一种在不具有不连续感的条件下显示图像的多屏显示设备。

将理解,前面的大体描述和下文的详细描述都是示例性的,旨在对要求保护的本发明提供进一步解释。

附图说明

给本发明提供进一步理解并且并入本申请组成本申请一部分的附图图解了本发明的实施方式,并与说明书一起用于解释本发明的原理。在附图中:

图1是图解根据本发明实施方式的发光显示设备的平面图。

图2是图解根据本发明实施方式的发光显示设备的后侧透视图。

图3A是图解根据图1所示的本发明实施方式的一个像素的图。

图3B是图解根据图1所示的本发明另一实施方式的一个像素的图。

图3C是图解根据图1所示的本发明另一实施方式的一个像素的图。

图4是图1所示的区域B1的放大图。

图5是图解图1和4所示的一个子像素的等效电路图。

图6是图解图1和4所示的栅极驱动电路的图。

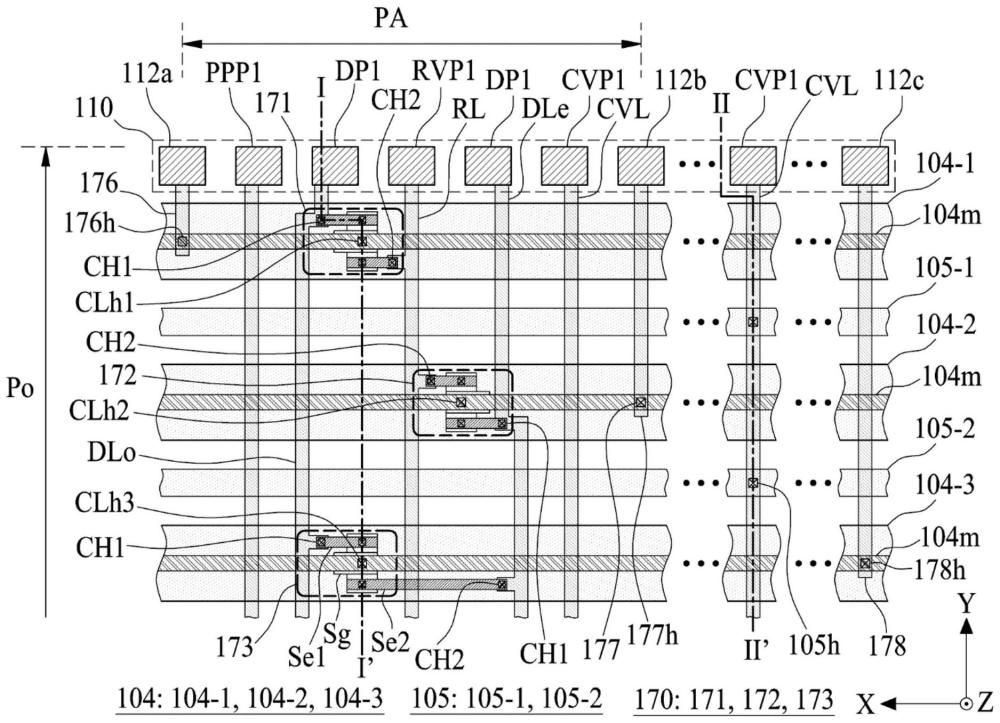

图7是图解根据本发明实施方式的多个开关电路部的图。

图8是图解图7所示的第一焊盘部、一个开关电路部和堰部的图。

图9是沿图2和8所示的线I-I’截取的剖视图。

图10是图9所示的区域B2的放大图。

图11是图9所示的区域B3的放大图。

图12是沿图2和8所示的线II-II’截取的剖视图。

图13是图解根据本发明另一实施方式的第一焊盘部、第二焊盘部和布线部的图。

图14是图解根据本发明另一实施方式的发光显示设备的平面图。

图15是图解根据本发明另一实施方式的发光显示设备的后视图。

图16是示意性图解根据本发明实施方式的开关电路部、驱动IC和时序控制器的图。

图17是图解根据本发明另一实施方式的多个开关电路部的图。

图18是沿图17所示的线III-III’截取的剖视图。

图19是示意性图解根据本发明另一实施方式的开关电路部、驱动IC和时序控制器的图。

图20是图解根据本发明另一实施方式的多个开关电路部的图。

图21是沿图20所示的线IV-IV’截取的剖视图。

图22是沿图20所示的线V-V’截取的剖视图。

图23是示意性图解根据本发明另一实施方式的开关电路部、驱动IC和时序控制器的图。

图24是图解根据本发明实施方式的多屏显示设备的图。

图25是沿图24所示的线VI-VI’截取的剖视图。

具体实施方式

现在详细参考本发明的实施方式进行描述,其中的一些示例可在附图中示出。在下文描述中,当确定对本文相关的公知功能或构造的详细描述会不必要地模糊技术构思的要点时,将省略其详细描述。所描述的处理步骤和/或操作的顺序是示例,步骤和/或操作的顺序不限于本文阐述的那些,而是可如本领域已知的那样进行改变,除非步骤和/或操作必须以某一顺序发生。类似的参考标记通篇指代类似的元件。仅为了便于撰写说明书的目的选定了在下文解释中使用的各元件的名称,因此这些名称可不同于实际产品中使用的名称。

将通过参照附图描述的以下实施方式阐明本发明的优点和特点以及其实现方法。然而,本发明可以以不同的形式实施,不应解释为限于在此阐述的实施方式。而是,提供这些实施方式是为了使本公开内容透彻和完整,并且将本发明的范围充分地传递给所属领域技术人员。

为了描述本发明的多个实施方式而在附图中公开的形状、大小、比例、角度和数量仅仅是示例,因而本发明不限于示出的细节。相同的参考标记通篇指代相同的要素。在下面的描述中,当确定对相关已知功能或配置的详细描述会不必要地使本发明的重点模糊不清时,将省略该详细描述。在本申请中使用“包括”、“具有”和“包含”进行描述的情况下,可添加其他部分,除非使用了“仅”。

在解释一要素时,尽管没有明确说明,但该要素应解释为包含误差范围。

在描述位置关系时,例如,当两部分之间的位置关系被描述为“在……上”、“在……上方”、“在……下方”和“在……之后”时,可在这两部分之间设置一个或多个其他部分,除非使用了更限制性的术语比如“正好”或“直接”。

在描述时间关系时,例如,当时间顺序被描述为例如“在……之后”、“随后”、“接下来”和“在……之前”时,可包括不连续的情形下,除了使用了更限制性的术语比如“正好”、“紧接”或“直接”。

将理解到,尽管在此可使用术语“第一”、“第二”等来描述各种要素,但这些要素不应受这些术语限制。这些术语仅仅是用来将一要素与另一要素区分开。例如,在不背离本发明的范围的情况下,第一要素可被称为第二要素,类似地,第二要素可被称为第一要素。

在描述本发明的要素时,可使用诸如“第一”、“第二”、A、B、(a)、(b)等之类的术语。这些术语仅用于将相应要素与其它要素区分开,并且相应要素的实质、顺序或先后关系不受这些术语的限制。将理解,当一个元件或层和另一元件或层被描述为“在……上”或“连接”时,其不仅可直接位于另一个元件或层上或者直接连接至另一个元件或层,也可存在中间元件或层。此外,应理解,当一个元件设置在另一元件上或下方时,其可指这些元件被设置为彼此直接接触的情形,或者可指这些元件被设置为彼此不直接接触。

术语“至少一个”应当理解为包括相关所列要素中的一个或多个的任意和所有组合。例如,“第一要素、第二要素和第三要素的至少一个”的含义是指从第一要素、第二要素和第三要素中的两个或更多个提出的所有要素的组合以及第一要素、第二要素或第三要素。

本文使用的术语“围绕”包括至少部分地围绕以及完全包围相关元件的一个或多个。类似地,本文使用的术语“覆盖”包括至少部分地覆盖以及完全覆盖相关元件的一个或多个。例如,如果封装层围绕堰,这可被解释为封装层至少部分地围绕堰。但是,在一些实施方式中,封装层可完全包围堰。本文使用的术语“围绕”的含义可基于相关附图和实施方式进行进一步指明。在本发明中,使用术语“围绕”、“至少部分地围绕”、“完全包围”等。根据上文阐述的“围绕”的定义,当在实施方式中仅使用术语“围绕”时,其可指至少部分地围绕或者完全包围相关元件的一个或多个。这同样适用于术语“覆盖”。

如所属领域技术人员可充分理解的,本发明各实施方式的特点可彼此部分或整体地结合或组合,并且可在技术上彼此进行各种互操作和驱动。本发明的多个实施方式可彼此独立实施,或者可以以相互依赖的关系共同实施。

下文中,将参照附图详细描述本发明的实施方式。为了便于说明,附图中示出的每个元件的尺寸不同于实际尺寸,因此不限于附图中示出的尺寸。此外,在对每幅图的元件添加参考标记时,尽管在不同图中示出,但是相似的参考标记可指代相似的元件。

图1是图解根据本发明实施方式的发光显示设备10的平面图,图2是图解根据本发明实施方式的发光显示设备10的后表面的透视图。

参照图1和2,根据本发明实施方式的发光显示设备(或发光显示面板)10可包括基板100、线基板(line substrate)200、接合构件(coupling member)300和布线部400。

基板100可称为第一基板、前基板、基础基板或像素阵列基板。基板100可以是玻璃基板,或者可以是可弯曲或具有柔性的薄玻璃基板或塑料基板。

基板100可包括显示部AA、多个像素P、堰部(dam portion)104以及多个开关电路部。

基板100的显示部AA可以是显示图像的区域,其可称为有源部、有源区或显示区。显示部AA的尺寸可等于或基本等于基板100(或发光显示设备或显示面板)的尺寸。例如,显示部AA的尺寸可等于基板100的第一表面的总尺寸。第一表面可以是基板100的前表面。因此,显示部AA可实现(或设置)在基板100的整个前表面上,由此发光显示设备的整个前表面可实现显示部AA。

显示部AA的端部(或最外部)可与基板100的外表面OS交叠或对准。例如,相对于发光显示设备(或发光显示面板)的厚度方向Z,显示部AA的侧表面(或端线)可在从基板100的外表面OS垂直延伸的垂直延伸线处对准。显示部AA的侧表面可仅被空气围绕而不被单独机构围绕。也就是说,基板100的显示部AA或所有侧表面(或外表面)可设置为与空气直接接触的结构而不被单独机构围绕。因此,与显示部AA的端部对应的基板100的外表面OS可仅被空气围绕(或邻接周围的空气),由此,根据本发明实施方式的发光显示设备(或发光显示面板)可具有空气边框结构或无边框结构(或零边框或没有边框),其中显示部AA的端部(或侧表面)可被空气围绕(或邻接周围的空气)。

多个像素P可沿着第一方向X和第二方向Y的每一个以第一间隔D1布置(或设置)在基板100的显示部AA上。第一方向X可横断第二方向Y或者与第二方向Y交叉或相交。第一方向X可以是基板100或发光显示设备的宽度方向、水平方向或第一长度方向(例如,宽度侧的长度方向)。第二方向Y可以是基板100或发光显示设备的长度方向、垂直方向或第二长度方向(例如,长度侧的长度方向)。

多个像素P的每一个可在基板100的显示部AA上设置的多个像素区实现。多个像素P的每一个可具有平行于第一方向X的第一长度L1以及平行于第二方向Y的第二长度L2。第一长度L1可与第二长度L2或第一间隔D1相同。第一长度L1和第二长度L2可与第一间隔D1相同。因此,所有像素P(或像素区)可全部具有相同尺寸。

沿第一方向X和第二方向Y的每一个彼此相邻的两个像素P在没有制造工艺的误差范围的条件下可具有相同的第一间隔D1。第一间隔D1可以是两个相邻像素P之间的节距(或像素节距)。例如,像素P的第一长度L1或第二长度L2可称为像素节距(pixel pitch)。例如,第一间隔(或者像素节距)D1可以是两个相邻像素P的中心部之间的距离(或长度)。例如,第一间隔(或像素节距)D1可以是两个相邻像素P的中心部之间的最短距离(或最短长度)。

多个像素P的每一个可包括:包括在基板100的像素区中实现的像素电路的电路层;以及设置在电路层处并且接合至像素电路的发光器件层。像素电路可连接至包括位于像素区中的数据线、栅极线和基准电压线的像素驱动线,并且可响应于提供给栅极线的扫描信号来输出与提供给数据线的数据信号和提供给基准电压线的基准电压之间的差电压对应的数据电流。多个像素P可连接至多条像素驱动线。发光器件层可包括自发光器件(或自发光层),其共同设置在除了显示部AA的外围部之外的其余显示部AA上。发光器件层可被配置为通过从像素电路提供的数据电流而发光。下文将描述像素驱动线、像素电路和发光器件层。

多个像素P可被划分(或分类)为最外像素Po和内部像素(或内像素)Pi。

最外像素Po可以是多个像素P中的最靠近基板100的外表面OS设置的像素。例如,最外像素Po可以是在第一水平线(或第一像素行)、最后水平线(或最后像素行)、第一垂直线(或第一像素列)和最后垂直线(或最后像素列)的每一个中布置的像素。

在最外像素Po的每一个的中心部与基板100的外表面OS之间的第二间隔D2可以是第一间隔D1的一半或小于第一间隔D1的一半。例如,第二间隔D2可以是在最外像素Po区的中心部与基板100的外表面OS之间的最短距离(或最短长度)。

当第二间隔D2大于第一间隔D1的一半时,基板100可通过在第一间隔D1的一半与第二间隔D2之间的差区域而具有大于显示部AA的尺寸,由此,在最外像素Po的端部和基板100的外表面OS之间的区域可被配置为围绕整个显示部AA的非显示部。例如,当第二间隔D2大于第一间隔D1的一半时,基板100不可避免地包括基于围绕整个显示部AA的非显示部的边框区。另一方面,当第二间隔D2是第一间隔D1的一半或小于第一间隔D1的一半时,每个最外像素Po的端部可与基板100的外表面OS对准(或者可设置在基板100的外表面OS处),或者显示部AA的端部可与基板100的外表面OS对准(或者可设置在基板100的外表面OS处),由此,显示部AA可在基板100的整个前表面处实现(或设置)。

内部像素Pi可以是多个像素P之中的除了最外像素Po之外的其余像素,或者可以是多个像素P之中的由最外像素Po围绕的像素。内部像素(或第二像素)Pi可被实现为具有与最外像素(或第一像素)Po不同的构造或结构。

堰部104可实现在最外像素Po的外围部处(最外像素Po的外围部实现在基板100的外围部处)或者布置在显示部AA中。例如,堰部104可设置在显示部AA中以沿着最外像素Po的中心部和基板100的外表面OS之间的区域一维地具有闭环线形状(或连续的线形状或闭环形状)。例如,闭环线形状可以是连续连接的环形。

堰部104可被配置为防止位于发光器件层上的封装层的有机封装层在最外像素Po的外围部处扩散或溢出。此外,堰部104可在最外像素Po的外围部处隔离(或断开或分离)发光器件层的至少一些层,由此可阻挡侧向水分渗透路径,从而防止或最小化由侧向水分渗透导致的发光器件层的可靠性降低。

堰部104可包括用于隔离(或断开或分离)发光器件层的至少一些层的底切结构或屋檐结构(eaves structure)。例如,堰部104可包括由底切结构或屋檐结构实现的底切区。因此,发光器件层的至少一部分可被堰部104的底切区物理地隔离(或断开或分离)。例如,形成在堰部104上的发光器件层的自发光器件(或自发光层)可在堰部104的底切区中被隔离(或断开或分离)至少一次。

多个开关电路部的每一个可被配置为与堰部104交叠并连接至多条像素驱动线。例如,多个开关电路部的每一个可设置在堰部104下(或下方)。例如,堰部104可设置在多个开关电路部上方。多个开关电路部的每一个可设置(或包括)在位于基板100的第一外围部处的最外像素Po的每一个中(或内部)。例如,一个开关电路部可设置在一个最外像素Po中(或内部)。下文将描述多个开关电路部。

根据本发明实施方式的发光显示设备(或发光显示面板)10或基板100可进一步包括第一焊盘部110。

第一焊盘部110可以是前焊盘部或第一布线焊盘。第一焊盘部110可设置(或包括)在位于基板100的平行于第一方向X的第一表面的第一外围部(或一个外围部)处的最外像素Po中,由此可不包括基于第一焊盘部110的非显示部(或边框区)。

第一焊盘部110可包括连接(或接合)至像素驱动线的多个第一焊盘(或前焊盘)。例如,第一焊盘部110可包括用于从驱动电路部500接收数据信号、栅极控制信号、像素驱动电源、基准电压和像素公共电压等的多个第一焊盘(或前焊盘)。多个第一焊盘可设置在基板100的一个外围部处并且与多条像素驱动线以及堰部104包括的至少一个堰的金属线电连接。位于基板100的第一外围部处的包括第一焊盘部110的最外像素Po的每一个可包括多个第一焊盘中的至少一个。由此,最外像素Po可包括至少一个第一焊盘,由此可被实现为具有与不包括第一焊盘的内部像素Pi不同的构造或结构。

例如,当第一焊盘部110未设置(或包括)在最外像素Po中(或内部)并且设置在最外像素Po的端部与基板100的外表面OS之间时,基板100可包括非显示部,其中第一焊盘部110设置在最外像素Po的端部与基板100的外表面OS之间,并且由于非显示部,第二间隔D2可大于第一间隔D1的一半,整个基板100不会被实现为显示部AA,可需要用于覆盖非显示部的单独边框。另一方面,根据本发明实施方式的第一焊盘部110可设置(或包括)在最外像素Po中(或内部),从而由于由第一焊盘部110导致的非显示部(或边框区)未形成或设置在最外像素Po的端部与基板100的外表面OS之间,所以第二间隔D2可小于或等于第一间隔D1的一半,由此整个基板100可被实现为显示部AA。

根据本发明实施方式的发光显示设备(或发光显示面板)10或基板100可进一步包括栅极驱动电路150。

栅极驱动电路150可设置或内置在显示部AA内,以向设置在基板100上的像素P提供扫描信号(或栅极信号)。栅极驱动电路150可向与第一方向X平行的水平线中的像素P同时提供扫描信号。例如,栅极驱动电路150可被配置为经由至少一条栅极线向设置在一条水平线中的像素P提供至少一个扫描信号。

栅极驱动电路150可利用包括多个级电路(stage circuits)的移位寄存器来实现。也就是说,根据本发明实施方式的发光显示设备(或发光显示面板)10可包括内置(或嵌入)在基板100的显示部AA中以向像素P提供扫描信号的移位寄存器。

多个级电路的每一个可包括多个分支电路(branch circuits)151,其沿着第一方向X在基板100的每条水平线中彼此分隔地布置。多个级电路的每一个可被设置为在每条水平线内的多个像素P之间分散(或彼此间隔开)。多个分支电路151的每一个可包括至少一个薄膜晶体管(TFT)(或分支TFT)。例如,多个分支电路151的每一个可在一条水平线内逐个地设置在多个像素P(或像素区)的至少一对相邻像素(或像素区)之间。多个级电路的每一个可基于经由栅极控制线提供的栅极控制信号通过多个分支电路151的驱动来产生扫描信号,并且可将扫描信号提供给位于相应水平线内的像素P。

根据本发明实施方式的发光显示设备(或发光显示面板)10或基板100可进一步包括至少一个分离部105。

至少一个分离部105可实现在基板100的外围部处,或者实现在位于显示部AA中的最外像素Po的外围部处。例如,至少一个分离部105可设置在显示部AA内,以沿着堰部104的附近区域(near region)一维地具有闭环线形状(或连续的线形状或闭环形状)。由此,最外像素Po可被配置为包括至少一个分离部105,从而最外像素Po可被实现为具有与内部像素Pi不同的构造或结构。

至少一个分离部105可在最外像素Po内隔离(或断开或分离)发光器件层的至少一些层,由此可阻挡侧向水分渗透路径,从而防止或最小化由侧向水分渗透导致的发光器件层的可靠性降低。至少一个分离部105可包括用于隔离(或断开或分离)发光器件层的至少一些层的底切结构或屋檐结构。例如,至少一个分离部105可包括由底切结构或屋檐结构实现的底切区。因此,发光器件层的至少一部分可被至少一个分离部105的底切区物理地隔离(或断开或分离)。例如,形成在至少一个分离部105上的发光器件层的自发光器件(或自发光层)可在至少一个分离部105的底切区中被隔离(或断开或分离)至少一次。

线基板200可称为第二基板、连接基板(link substrate)、下基板、后基板、布线基板或连接玻璃。线基板200可以是玻璃基板,或者可以是可弯曲或具有柔性的薄玻璃基板或塑料基板。例如,线基板200可包括与基板100相同的材料。线基板200的尺寸可等于或基本等于基板100的尺寸,但本发明的实施方式不限于此,线基板200的尺寸可小于基板100的尺寸。例如,线基板200可被配置为具有与基板100相同的尺寸,以便保持或确保基板100的刚度。

线基板200可包括第二焊盘部210、至少一个第三焊盘部230和连线部250。

第二焊盘部210可以是后焊盘部或第二布线焊盘。第二焊盘部210可设置在与位于基板100的前表面处的第一焊盘部110交叠的、线基板200的后表面200b的一个外围部(或第一后外围部)处。

第二焊盘部210可包括多个第二焊盘(或后焊盘),其沿着第一方向X彼此平行地设置在线基板200的第一外围部处。例如,第二焊盘部210可包括用于从驱动电路部500接收数据信号、栅极控制信号、像素驱动电源、基准电压和像素公共电压等的多个第二焊盘(或后焊盘)。第二焊盘可单独地(或以一一对应的关系)与位于第一焊盘部110处的多个第一焊盘的每一个交叠。换句话说,多个第二焊盘的每一个可与多个第一焊盘中的相应一个交叠。

至少一个第三焊盘部230可以是输入焊盘部、驱动电路连接焊盘部、驱动电路焊接部、或驱动电路焊接焊盘部。至少一个第三焊盘部230可设置在线基板200的后表面200b处。例如,至少一个第三焊盘部230可设置在与线基板200的后表面200b的第一外围部相邻的中部。例如,线基板200可包括连接至第二焊盘部210的两个或更多个第三焊盘部230。例如,第二焊盘部210可被划分为沿着第一方向X的两个或更多个区域,两个或更多个第三焊盘部230的每一个可被配置为连接至第二焊盘部210的相应划分区。

至少一个第三焊盘部230可包括沿着第一方向X彼此间隔开某一间隔的多个输入焊盘(或第三焊盘)。例如,至少一个第三焊盘部230可包括用于从驱动电路部500接收数据信号、栅极控制信号、像素驱动电源、基准电压和像素公共电压等的多个输入焊盘(或第三焊盘)。

连线部250可设置在第二焊盘部210和至少一个第三焊盘部230之间。连线部250可包括多条连线,其被配置为将第二焊盘部210的多个第二焊盘连接至位于至少一个第三焊盘部230处的多个输入焊盘。

设置在至少一个第三焊盘部230处的多个输入焊盘中的一些可经由多条连线中的相应连线单独地(或以一一对应的关系)连接至位于第二焊盘部210处的多个第二焊盘中的一些。换句话说,多个输入焊盘的一些可经由相应连线连接至多个第二焊盘中的相应第二焊盘。例如,在多个输入焊盘中的用于从驱动电路部500接收数据信号、栅极控制信号、像素驱动电源和基准电压的输入焊盘可经由相应连线单独地(或以一一对应的关系)连接至位于第二焊盘部210处的相应第二焊盘。

设置在至少一个第三焊盘部230处的多个输入焊盘中的另一些可共同接合至多个第二焊盘的另一些。例如,多个输入焊盘中的用于接收像素公共电压的一个或多个像素公共电压输入焊盘可经由像素公共电源连线257连接至多个第二焊盘中的用于接收像素公共电压的第二焊盘。

像素公共电源连线257可包括第一公共连线257a和第二公共连线257b。

第一公共连线257a可共同连接至位于至少一个第三焊盘部230处的一个或多个像素公共电压输入焊盘。例如,第一公共连线257a可设置在线基板200的后表面200b处的第三焊盘部230的一侧。

第一公共连线257a可在第二焊盘部210和至少一个第三焊盘部230之间设置或形成在线基板200的后表面200b上方,以具有相对较宽的尺寸(或面积),从而被施加的像素公共电压的压降可减小或最小化。根据本发明实施方式的第一公共连线257a的尺寸可在从其一个侧部到其另一个侧部的方向上逐渐地增加。例如,第一公共连线257a的尺寸可在从至少一个第三焊盘部230到线基板200的外表面OS的方向上逐渐地增加。

第二公共连线257b可设置在线基板200的后表面200b的第一外围部处,以与第二焊盘部210相邻。根据实施方式的第二公共连线257b可与第一方向X平行地设置,以面对设置在第二焊盘部210处的多个第二焊盘的全部。例如,第二公共连线257b可具有尺寸(或面积)相对较宽的条形(bar shape),以便减小或最小化施加给像素公共电源连线257的像素公共电压的压降。

第二公共连线257b可经由连接接触孔(link contact hole)257h电连接至第一公共连线257a的另一侧的至少一部分。第二公共连线257b可朝向位于第二焊盘部210处的多个像素公共电压焊盘延伸(或突出),并且可电连接至多个像素公共电压焊盘的每一个。

接合构件300可插置在基板100和线基板200之间。基板100和线基板200可通过接合构件300彼此相对地接合。接合构件300可以是包含光学透明粘合剂(OCA)或光学透明树脂(OCR)的透明粘合构件,或者双面胶带,但本发明的实施方式不限于此。例如,接合构件300可包括玻璃纤维。

可选地,线基板200可省略。在这种情形下,第二焊盘部210、至少一个第三焊盘部230和连线部250可设置在基板100的后表面处,从而省略其重复描述。因此,当线基板200省略时,可省略接合构件300。

布线部400可称为侧线部、边缘线部、侧布线部、边缘布线部、印刷线部、侧印刷线部或侧配线部等。布线部400可被设置为围绕基板100的外表面OS和线基板200的外表面OS。根据实施方式的布线部400可包括多条布线410,其设置在基板100的外表面OS之中的第一外表面(或一个表面)OS1a和线基板200的外表面OS之中的第一外表面(或一个表面)OS1b的每一个处。

可选地,当线基板200省略时,多条布线410的每一条可被形成为围绕基板100的外表面OS的第一外表面(或一个表面)OS1a,并且可单独地(或以一一对应的关系)将第一焊盘部110的第一焊盘连接至第二焊盘部210的第二焊盘。换句话说,多条布线410的每一条可将第一焊盘中的相应一个连接至第二焊盘中的相应一个。

根据本发明实施方式的发光显示设备可进一步包括驱动电路部500。

驱动电路部500可基于从显示驱动系统提供的时序同步信号和数字图像数据驱动位于基板100上的像素P(例如使像素P发光),以允许显示部AA显示对应于数字图像数据的图像。驱动电路部500可连接(或接合)至位于线基板200的后表面200b处的至少一个第三焊盘部230,并且可向至少一个第三焊盘部230输出用于驱动设置在基板100处的像素P(例如使像素P发光)的驱动电源、数据信号和栅极控制信号。

根据本发明实施方式的驱动电路部500可包括柔性电路膜510、驱动集成电路(IC)530、印刷电路板(PCB)550、时序控制器570和电源电路部590。

柔性电路膜510可连接至位于线基板200的后表面200b处的至少一个第三焊盘部230。

驱动IC 530可安装在柔性电路膜510上。驱动IC 530可接收从时序控制器570提供的数据控制信号和子像素数据,基于数据控制信号将子像素数据转换成模拟数据信号,并输出模拟数据信号。

驱动IC 530可在预定或选定的外部感测时段期间经由设置在基板100处的多条基准电压线(或像素感测线)的每一条感测设置在子像素SP中的驱动TFT的特性值,产生与每个子像素的感测值对应的感测原始数据(sensing raw data),并将每个子像素的感测原始数据提供给时序控制器570。

此外,驱动IC 530可在测试模式中经由多条基准电压线(或像素感测线)的每一条感测(或接收)测试信号,产生与感测值(或接收值)对应的基于线的(line-based)线感测数据,并将线感测数据提供给时序控制器570。

此外,驱动IC 530可在测试模式期间经由多个开关电路部感测多条布线410的至少一些的线电阻,或者可感测多条布线410的每一条的线电阻,并且可产生与感测的线电阻对应的基于线的电阻感测数据,且可将电阻感测数据提供给时序控制器570。例如,驱动IC530可感测分别连接至多条数据线的多条数据布线的每一条的线电阻,产生与数据布线的感测的线电阻对应的电阻感测数据,并且将电阻感测数据提供给时序控制器570。

根据本发明的实施方式,驱动IC 530可输出数据信号,在数据信号中反映出从时序控制器570提供的基于线的电阻补偿值,由此防止或最小化由多条数据布线之间的电阻偏差导致的图像质量缺陷。

根据本发明的另一实施方式,驱动IC 530可包括输出数据信号的多个信号输出电路。多个信号输出电路的每一个的电流选项值(current option value)(或输出电流选项值)可根据从时序控制器570提供的基于线的电阻补偿值(或偏置电压电平)来设定(或改变),由此驱动IC 530可输出数据信号,在数据信号中反映出从时序控制器570提供的基于线的电阻补偿值。

PCB 550可接合至柔性电路膜510的另一侧外围部。PCB 550可在驱动电路部500的元件之间传输信号和电源。

时序控制器570可安装在PCB 550上,并且可经由位于PCB 550处的用户连接器接收从显示驱动系统提供的时序同步信号和数字图像数据。可选地,时序控制器570可不安装在PCB 550上,并且可实现在显示驱动系统中,或者可安装在PCB 550和显示驱动系统之间连接的单独控制板上。

时序控制器570可基于时序同步信号来排列数字图像数据,以产生与设置在显示部AA中的像素排列结构匹配的像素数据,并且可向驱动IC 530提供产生的像素数据。

时序控制器570可基于时序同步信号产生数据控制信号和栅极控制信号的每一个,基于数据控制信号控制驱动IC 530的驱动时序,并且基于栅极控制信号控制栅极驱动电路150的驱动时序。

时序控制器570可在预定或选定的外部感测时段期间基于外部感测模式驱动栅极驱动电路150和驱动IC 530的每一个,基于从驱动IC 530提供的感测原始数据产生用于补偿每个子像素的驱动TFT的特性变化的每个子像素的补偿数据,并且基于产生的每个子像素的补偿数据来调制每个子像素的像素数据。

时序控制器570可在测试模式中驱动多个开关电路部和驱动IC 530的每一个,根据从驱动IC 530提供的基于线的线感测数据来确定是否出现布线短路以及短路缺陷位置,并且通过使用单独的监视器来显示确定结果。

时序控制器570可在测试模式中驱动多个开关电路部和驱动IC 530的每一个,并且可根据从驱动IC 530提供的基于线的电阻感测数据来调制基于子像素的像素数据,或者可设定(或改变)驱动IC 530的电流选项值(或输出电流选项值或转换速率(slew rate)),由此防止或最小化由多条数据布线之间的电阻偏差导致的图像质量缺陷。例如,时序控制器570可根据从驱动IC 530提供的基于线的电阻感测数据来产生用于补偿多条数据布线之间的电阻偏差的基于线的电阻补偿值,并且可将基于线的电阻补偿值提供给驱动IC 530。例如,基于线的电阻补偿值可按照查找表形式存储在存储电路中。

电源电路部590可安装在PCB 550上,并且可通过使用从外部提供的输入电源来产生在像素P上显示图像所需的各种源电压,以将产生的源电压提供给相应的电路。

图3A是图解根据图1所示的本发明实施方式的一个像素的图,图3B是图解根据图1所示的另一实施方式的一个像素的图,图3C是图解根据图1所示的本发明另一实施方式的一个像素的图。

参照图1和3A,根据本发明实施方式的一个像素(或单位像素)P可包括设置在像素区PA处的多个子像素SP1至SP4。例如,一个像素(或单位像素)P可被配置为包括设置在像素区PA处的第一至第四子像素SP1至SP4。

多个子像素或第一至第四子像素SP1至SP4可设置成2×2形式或四边形。第一至第四子像素SP1至SP4的每一个可包括发光区EA和电路区CA。例如,发光区EA可称为开口区、开口部或发光部。

第一至第四子像素SP1至SP4的每一个的发光区EA可具有均匀的四边形结构,以具有尺寸彼此相同(或面积彼此相同)的方形。根据实施方式,具有均匀四边形结构的发光区EA可被设置为在相应子像素区内靠近像素P的中心部CP,以具有比像素P的四等分区的每一个小的尺寸,或者可被设置为集中在像素P的中心部CP处。根据另一实施方式,具有均匀四边形结构的发光区EA可设置在相应子像素区的中心部CP处,以具有比像素P的四等分区的每一个小的尺寸。

第一至第四子像素SP1至SP4的每一个的电路区CA可设置在相应发光区EA的周围(或附近)。电路区CA可包括用于驱动相应子像素,例如使相应子像素发光的像素驱动线和像素电路。例如,电路区CA可称为非发光区、非开口区、非发光部、非开口部、或外围部。

参照图1和3B,根据本发明另一实施方式的第一至第四子像素SP1至SP4的每一个的发光区EA可延伸至电路区CA,以与电路区CA的一些或全部交叠。也就是说,为了提高与发光区EA的尺寸对应的子像素SP1至SP4的开口率或者随着像素P的分辨率的提高而减小像素节距D1,第一至第四子像素SP1至SP4的每一个的发光区EA可延伸至电路区CA以与电路区CA的一些或全部交叠。例如,由于第一至第四子像素SP1至SP4的每一个的发光区EA具有顶发光结构,所以发光区EA可被设置为与相应的电路区交叠。由此,发光区EA可具有等于或大于电路区CA的尺寸。

参照图1和3C,根据另一实施方式的第一至第四子像素SP1至SP4的每一个可具有尺寸不同的非均匀四边形结构。例如,第一至第四子像素SP1至SP4的每一个的发光区EA可具有尺寸不同的非均匀四边形结构。

具有非均匀四边形结构的第一至第四子像素SP1至SP4的每一个的尺寸可基于分辨率、发光效率或图像质量等设定。当发光区EA具有非均匀四边形结构时,在第一至第四子像素SP1至SP4的每一个的发光区EA之中,第四子像素SP4的发光区EA可具有最小尺寸(或面积),第三子像素SP3的发光区EA可具有最大尺寸。第一至第四子像素SP1至SP4的每一个的发光区EA可延伸至电路区CA,以与电路区CA的一些或全部交叠。例如,由于第一至第四子像素SP1至SP4的每一个的发光区EA具有顶发光结构,所以发光区EA可被布置为与相应的电路区CA交叠。由此,发光区EA可具有等于或大于电路区CA的尺寸。

在图3A至3C中,第一子像素SP1可被实现为发射第一颜色的光,第二子像素SP2可被实现为发射第二颜色的光,第三子像素SP3可被实现为发射第三颜色的光,第四子像素SP4可被实现为发射第四颜色的光。例如,第一至第四颜色的每一个可不同。根据本发明的实施方式,第一颜色可以是红色,第二颜色可以是蓝色,第三蓝色可以是白色,第四颜色可以是绿色。根据本发明的另一实施方式,第一至第四颜色的一些可以相同。例如,第一颜色可以是红色,第二颜色可以是第一绿色,第三颜色可以是第二绿色,第四颜色可以是蓝色,但是本发明的实施方式不限于此。

可选地,根据本发明另一实施方式的第一至第四子像素SP1至SP4的每一个可具有1×4的形式、均匀的条纹结构(stripe structure)或非均匀的条纹结构。例如,第一至第四子像素SP1至SP4的每一个的发光区EA可具有1×4的形式、均匀的条纹结构或非均匀的条纹结构。例如,具有均匀条纹结构的第一至第四子像素SP1至SP4的每一个的发光区EA可均具有矩形,其包括平行于第一方向X的短边以及平行于第二方向Y的长边。可选地,在具有1×4的形式、均匀的条纹结构或非均匀的条纹结构的第一至第四子像素SP1至SP4中,被实现为发射白色光的白色子像素可省略。

图4是图1所示的区域B1的放大图,图5是图解图1和4所示的一个子像素的等效电路图。

参照图1、4和5,根据本发明实施方式的基板100可包括:像素驱动线DL、GL、PL、CVL、RL和GCL;多个像素P;公共电极CE;多个公共电极连接部CECP;以及第一焊盘部110。

像素驱动线DL、GL、PL、CVL、RL和GCL可包括多条数据线DL、多条栅极线GL、多条像素驱动电源线PL、多条像素公共电压线CVL、多条基准电压线(或多条基准线)RL和栅极控制线GCL。

多条数据线DL可沿着第二方向Y长长地延伸,并且可沿着第一方向X在基板100的显示部AA中以预定或选定间隔彼此分隔地设置。

多条栅极线GL可沿着第一方向X长长地延伸,并且可沿着第二方向Y在基板100的显示部AA中以预定或选定间隔彼此分隔地设置。

多条像素驱动电源线PL可沿着第二方向Y长长地延伸,并且可沿着第一方向X在基板100的显示部AA中以预定或选定间隔彼此分隔地设置。

多条像素驱动电源线PL中的两条相邻的像素驱动电源线PL可接合至沿着第二方向Y布置的每个像素区PA中设置的多条电源共享线PSL。例如,多条像素驱动电源线PL可通过多条电源共享线PSL彼此电连接(或接触),由此可具有梯子结构(ladder structure)或网结构。多条像素驱动电源线PL可具有梯子结构或网结构,由此可防止或最小化或减小由多条像素驱动电源线PL的每一条的线电阻导致的像素驱动电源的压降(IR降)。因此,根据本发明实施方式的发光显示设备可防止或最小化或减小由于提供给布置在显示部AA处的每个像素的像素驱动电源的偏差导致的图像质量降低。

多条电源共享线PSL的每一条可从相邻的像素驱动电源线PL与第一方向X平行地分支,并且可设置在每个像素区PA的中部区域中,但本发明的实施方式不限于此。

多条像素公共电压线CVL可沿着第二方向Y长长地延伸,并且可沿着第一方向X在基板100的显示部AA中以预定或选定间隔彼此分隔地设置。例如,多条像素公共电压线CVL的每一条可设置在相对于第一方向X的偶数像素区PA的第一外围部处,但本发明的实施方式不限于此。

多条基准电压线RL可沿着第二方向Y长长地延伸,并且可沿着第一方向X在基板100的显示部AA中以预定或选定间隔彼此分隔地设置。多条基准电压线RL的每一条可设置在沿第二方向Y布置的每个像素区PA的中心区处,但本发明的实施方式不限于此。

多条基准电压线RL的每一条可在每个像素区PA中被沿着第一方向X相邻的两个子像素(SP1,SP2)(SP3,SP4)共享。为此,多条基准电压线RL的每一条可包括基准分支线RDL。基准分支线RDL可在每个像素区PA中分支(或突出)到沿着第一方向X相邻的两个子像素(SP1,SP2)(SP3,SP4),并且可电连接至相邻的两个子像素(SP1,SP2)(SP3,SP4)。

多条栅极控制线GCL的每一条可沿着第二方向Y长长地延伸,并且可沿着第一方向X在基板100的显示部AA中以预定或选定间隔彼此分隔地设置。例如,多条栅极控制线GCL的每一条可设置在多个像素区PA之间,或者设置在相对于第一方向X相邻的两个像素区PA之间的边界区处。

多个像素P的每一个可包括至少三个子像素。例如,多个像素P的每一个可包括第一至第四子像素SP1至SP4。第一至第四子像素SP1至SP4的每一个可包括像素电路PC以及发光器件层。

根据实施方式的像素电路PC可设置在像素区PA的电路区中,并且可连接至与其相邻的栅极线GLo或GLe、与其相邻的数据线DLo或DLe、以及像素驱动电源线PL。例如,设置在第一子像素SP1处的像素电路PC可连接至奇数数据线DLo和奇数栅极线GLo,设置在第二子像素SP2处的像素电路PC可连接至偶数数据线DLe和奇数栅极线GLo,设置在第三子像素SP3处的像素电路PC可连接至奇数数据线DLo和偶数栅极线GLe,设置在第四子像素SP4处的像素电路PC可连接至偶数数据线DLe和偶数栅极线GLe。

第一至第四子像素SP1至SP4的每一个的像素电路PC可响应于从相应栅极线GLo或GLe提供的扫描信号来采样从相应数据线DLo或DLe提供的数据信号,并且可基于采样的数据信号来控制从像素驱动电源线PL流入到发光器件层的电流。

根据实施方式的像素电路PC可包括第一开关薄膜晶体管Tsw1、第二开关薄膜晶体管Tsw2、驱动薄膜晶体管Tdr和存储电容器Cst,但本发明的实施方式不限于此。在下文描述中,薄膜晶体管可称为TFT。

第一开关TFT Tsw1可包括:连接至相应栅极线GLo或GLe的栅极、连接至相应数据线DLo或DLe的第一电极(或第一源极/漏极)、以及连接至驱动TFT Tdr的栅极节点n1的第二电极(或第二源极/漏极)。第一开关TFT Tsw1可由经由相应栅极线GLo或GLe提供的扫描信号(或第一栅极信号)导通,并且可将经由相应数据线DLo或DLe提供的数据信号传输给驱动TFT Tdr的栅极节点n1。

第二开关TFT Tsw2可包括:连接至相应栅极线GLo或GLe的栅极、连接至驱动TFTTdr的源极节点n2的第一电极(或第一源极/漏极)、以及连接至相应基准电压线RL的第二电极(或第二源极/漏极)。第二开关TFT Tsw2可由经由相应栅极线GLo或GLe提供的扫描信号(或第二栅极信号)导通,并且可将经由相应基准电压线RL提供的基准电压传输给驱动TFTTdr的源极节点n2。例如,第二开关TFT Tsw2可与第一开关TFT Tsw1同时导通。

存储电容器Cst可形成在驱动TFT Tdr的栅极节点n1和源极节点n2之间。根据实施方式的存储电容器Cst可包括连接至驱动TFT Tdr的栅极节点n1的第一电容器电极、连接至驱动TFT Tdr的源极节点n2的第二电容器电极、以及形成在第一电容器电极和第二电容器电极之间的交叠区中的介电层。存储电容器Cst可利用在驱动TFT Tdr的栅极节点n1和源极节点n2之间的差电压充电,然后可基于其充入的电压来使驱动TFT Tdr导通或截止。

驱动TFT Tdr可包括:共同连接至第一开关TFT Tsw1的第二电极以及存储电容器Cst的第一电容器电极的栅极(或栅极节点n1);共同连接至第二开关TFT Tsw2的第一电极、存储电容器Cst的第二电容器电极、以及发光器件层的像素电极PE的第一电极(或第一源极/漏极或者源极节点n2);以及连接至相应像素驱动电源线PL的第二电极(或第二源极/漏极或者漏极节点)。驱动TFT Tdr可基于存储电容器Cst的电压导通,并且可控制从像素驱动电源线PL流入到发光器件层的电流量。

发光器件层可设置在像素区PA的发光区EA中,并且电连接至(或接触)像素电路PC。根据实施方式的发光器件层可包括电连接至(或接触)像素电路PC的像素电极PE、电连接至(或接触)像素公共电压线CVL的公共电极CE、以及插置在像素电极PE和公共电极CE之间的自发光器件ED。

多个公共电极连接部CECP的每一个可设置在分别与多条像素公共电压线CVL交叠的多个像素P之间,并且可将公共电极CE电连接(或接触)多条像素公共电压线CVL的每一条。相对于第一方向X和第二方向Y,根据实施方式的多个公共电极连接部CECP的每一个可在多个像素P之间的部分中或者在多个像素P之间的边界部中电连接至多条像素公共电压线CVL的每一条,并且可电连接至(或接触)公共电极CE的一部分,由此可将公共电极CE电连接至(或接触)多条像素公共电压线CVL的每一条。

多个公共电极连接部CECP的每一个可设置在多个像素P之间的部分中,以将公共电极CE电连接至(或接触)多条像素公共电压线CVL的每一条,由此可防止或最小化或减小由公共电极CE的表面电阻导致的像素公共电压的压降(IR降)。根据本发明的实施方式,多个公共电极连接部CECP的每一个可与具有至少双层结构的像素电极PE一起形成,以便电连接至(或接触)多条像素公共电压线CVL的每一条。例如,公共电极CE可通过侧向接触结构(或侧向暴露结构)连接至(或接触)多个公共电极连接部CECP的每一个。

堰部104可设置或实现在基板100的外围部处或最外像素Po处,以具有闭环线形状(或闭环形状)。堰部104与参照图1描述的相同,因此省略其重复描述。

根据本发明实施方式的发光显示设备10或基板100可进一步包括分离部105。分离部105可设置或实现在基板100的外围部处或最外像素Po处,以在堰部104的周围(或附近)具有闭环线形状(或闭环形状)。分离部105与参照图1描述的相同,因此省略其重复描述。

第一焊盘部110可包括在基板100的第一外围部处沿着第一方向X彼此平行地设置的多个第一焊盘。多个第一焊盘可划分(或分类)为多个第一数据焊盘DP1、多个第一栅极焊盘GP1、多个第一像素驱动电源焊盘PPP1、多个第一基准电压焊盘RVP1、以及多个第一像素公共电压焊盘CVP1。

多个第一数据焊盘DP1的每一个可单独地(或以一一对应的关系)连接至位于基板100上的多条数据线DLo和DLe的每一条的一个侧端。换句话说,多个第一数据焊盘DP1的每一个可连接至多条数据线DLo和DLe的相应一条的一个侧端。

多个第一栅极焊盘GP1的每一个可可单独地(或以一一对应的关系)连接至位于基板100处的多条栅极控制线GCL的每一条的一个侧端。换句话说,多个第一栅极焊盘GP1的每一个可连接至多条栅极控制线GCL中的相应一条的一个侧端。多个第一栅极焊盘GP1可划分(或分类)为第一起始信号焊盘、多个第一移位时钟焊盘、多个第一进位时钟焊盘、至少一个第一栅极驱动电源焊盘、以及至少一个第一栅极公共电源焊盘等。

多个第一像素驱动电源焊盘PPP1的每一个可单独地(或以一一对应的关系)连接至位于基板100上的多条像素驱动电源线PL的每一条的一个侧端。换句话说,多个第一像素驱动电源焊盘PPP1的每一个可连接至多条像素驱动电源线PL的相应一条的一个侧端。每个第一基准电压焊盘RVP1可单独地(或以一一对应的关系)连接至位于基板100上的多条基准电压线RL的每一条的一个侧端。换句话说,多个第一基准电压焊盘RVP1的每一个可连接至多条基准电压线RL的相应一条的一个侧端。每个第一像素公共电压焊盘CVP1可单独地(或以一一对应的关系)连接至位于基板100上的多条像素公共电压线CVL的每一条的一个侧端。换句话说,多个第一像素公共电压焊盘CVP1的每一个可连接至多条像素公共电压线CVL的相应一条的一个侧端。

根据本发明实施方式的第一焊盘部110可包括沿着第一方向X设置的多个焊盘组PG。多个焊盘组PG的每一个可连接至沿着第一方向X设置的两个相邻像素P。多个焊盘组PG的每一个可包括沿着第一方向X交替设置的第一焊盘组PG1和第二焊盘组PG2。第一焊盘组PG1可包括沿着第一方向X连续或依次地设置在奇数像素区PA内的第一像素驱动电源焊盘PPP1、第一数据焊盘DP1、第一基准电压焊盘RVP1、第一数据焊盘DP1和第一像素公共电压焊盘CVP1。第二焊盘组PG2可包括沿着第一方向X连续地设置在偶数像素区PA内的第一栅极焊盘GP1、第一数据焊盘DP1、第一基准电压焊盘RVP1、第一数据焊盘DP1和第一像素驱动电源焊盘PPP1。

根据本发明实施方式的发光显示设备10或基板100可进一步包括多条辅助电压线SVL和多条辅助线连接部SLCP。

多条辅助电压线SVL的每一条可沿着第二方向Y长长地延伸,并且可被设置为与多条像素公共电压线CVL中的相应像素公共电压线CVL相邻。多条辅助电压线SVL的每一条可在不电连接至(或接触)像素公共电压焊盘CVP1的条件下电连接至(或接触)相邻的像素公共电压线CVL,由此可被提供来自相邻像素公共电压线CVL的像素公共电压。为此,根据本发明实施方式的基板100可进一步包括用于将彼此相邻的像素公共电压线CVL与辅助电压线SVL电连接(或接触)的多个线连接图案LCP。

多个线连接图案LCP的每一个可设置在基板100上,以便与彼此相邻的像素公共电压线CVL和辅助电压线SVL交叉(intersect)或交叠(overlap),并且可经由线跳接结构(line jumping structure)将彼此相邻的像素公共电压线CVL与辅助电压线SVL电连接(或接触)。例如,多个线连接图案LCP的每一个的一侧可经由形成在辅助电压线SVL上方的绝缘层处的第一线接触孔电连接至(或接触)辅助电压线SVL的一部分,并且多个线连接图案LCP的每一个的另一侧可经由形成在像素公共电压线CVL上方的绝缘层处的第二线接触孔电连接至(或接触)像素公共电压线CVL的一部分。

多个辅助线连接部SLCP的每一个可将公共电极CE电连接至(或接触)位于与多条辅助电压线SVL的每一条交叠的多个像素P之间的每条辅助电压线SVL。例如,多个辅助线连接部SLCP的每一个可将公共电极CE电连接至多条辅助电压线SVL的相应一条。相对于第二方向Y,根据实施方式的多个辅助线连接部SLCP的每一个可在多个像素P之间的部分中或者在多个像素P之间的边界部中电连接至(接触)每条辅助电压线SVL,并且可电连接至(或接触)公共电极CE的一部分,从而可将公共电极CE电连接至(接触)每条辅助电压线SVL。因此,公共电极CE可经由辅助线连接部SLCP附加地连接至每条辅助电压线SVL。因此,根据本发明实施方式的发光显示设备10可进一步防止或最小化或减小由于向布置在显示部AA中的每个像素P提供的像素公共电压的偏差导致的图像质量劣化。此外,在根据本发明实施方式的发光显示设备10中,尽管未附加地设置(或形成)连接至每条辅助电压线SVL的像素公共电压焊盘CVP,但是像素公共电压可经由像素公共电压线CVL和多个线连接图案LCP的每一个被提供给每条辅助电压线SVL。

根据本发明实施方式的发光显示设备10或基板100可进一步包括封装层。

封装层可被实现为围绕发光器件层。封装层可包括:设置在发光器件层、堰部104和分离部105上方的第一无机封装层(或第一封装层);设置在第一无机封装层上方的第二无机封装层(或第三封装层);以及设置在由堰部104限定的封装区上或者由堰部104在至少四个边围绕并且插置在第一无机封装层和第二无机封装层之间的有机封装层(或第二封装层)。

有机封装层可覆盖发光器件层的前表面(或顶表面),并且可朝向基板100的端部流动,有机封装层的扩散(或流动)可被堰部104阻挡。堰部104可限定或限制有机封装层的布置区(或封装区),并且可阻挡或防止有机封装层的扩散或溢出。

图6是图解图1和4所示的栅极驱动电路的图。

参照图1、4和6,根据本发明另一实施方式的栅极驱动电路150可被实现(或内置)在基板100的显示部AA内。栅极驱动电路150可基于经由第一焊盘部110和栅极控制线GCL提供的栅极控制信号来产生扫描信号,并将扫描信号依次提供给多条栅极线GL。

栅极控制线GCL可包括起始信号线、多条移位时钟线、至少一条栅极驱动电压线以及至少一条栅极公共电压线。栅极控制线GCL可沿着第二方向Y长长地延伸,并且可沿着第一方向X在基板100的显示部AA中以预定或选定间隔彼此分隔地设置。例如,栅极控制线GCL可沿着第一方向X设置在至少一对相邻像素P之间。

栅极驱动电路150可利用包括多个级电路1501至150m的移位寄存器实现,其中m是2或更大的整数。

多个级电路1501至150m的每一个可沿着第一方向X在基板100的第一表面上单独地设置在每条水平线中,并且可沿着第二方向Y彼此从属地连接。换句话说,多个级电路1501至150m的每一个可设置在基板100的相应一条水平线内。多个级电路1501至150m的每一个可响应于经由第一焊盘部110和栅极控制线GCL提供的栅极控制信号以预定或选定顺序产生扫描信号,并且可将扫描信号提供给相应栅极线GL。

多个级电路1501至150m的每一个可包括多个分支电路1511至151n以及分支网(branch network)153。

多个分支电路1511至151n可经由分支网153选择性地连接至栅极控制线GCL,并且可经由分支网153彼此电连接(或接触)。多个分支电路1511至151n的每一个可基于经由栅极控制线GCL提供的栅极控制信号和分支网153的电压产生扫描信号,并且可将扫描信号提供给相应栅极线GL。

多个分支电路1511至151n的每一个可包括构成多个级电路1501至150m中的一个级电路的多个TFT中的至少一个TFT(或分支TFT)。多个分支电路1511至151n中的任一个分支电路可包括连接至栅极线GL的上拉TFT。多个分支电路1511至151n中的另一分支电路可包括连接至栅极线GL的下拉TFT。

根据实施方式的多个分支电路1511至151n的每一个可设置在位于基板100的每条水平线中的、两个相邻像素P之间的电路区处或者至少两个相邻像素P之间的电路区处,但本发明的实施方式不限于此。例如,多个分支电路1511至151n的每一个可根据构成一个级电路1501至150m的TFT的数量以及设置在一条水平线中的像素P的数量而设置在至少一对相邻像素P之间的电路区(或边界区)处。

分支网153可设置在基板100的每条水平线处并且可将多个分支电路1511至151n彼此电连接(或接触)。分支网153可包括多条控制节点线以及多条网线。

多条控制节点线可设置在基板100的每条水平线处,并且可在一条水平线内选择性地连接至多个分支电路1511至151n。例如,多条控制节点线可设置在基板100的每条水平线内布置的像素区之中的上外围区(或下外围区)处,但本发明的实施方式不限于此。

多条网线可选择性地连接至位于基板100处的栅极控制线GCL,并且可选择性地连接至多个分支电路1511至151n。例如,多条网线可将从栅极控制线GCL提供的栅极控制信号传输给相应的分支电路1511至151n,并且可在多个分支电路1511至151n之间传输信号。

如上所述,根据本发明的实施方式,由于栅极驱动电路150设置在基板100的显示部AA内,所以在最外像素Po的中心部CP与基板100的外表面OS之间的第二间隔D2可等于或小于相邻像素P之间的第一间隔(或像素节距)D1的一半。例如,当栅极驱动电路150未设置在基板100的显示部AA内并且设置在基板100的外围部处时,第二间隔D2由于栅极驱动电路150可不等于或小于第一间隔D1的一半。因此,在根据本发明实施方式的发光显示设备10中,栅极驱动电路150可设置在基板100的显示部AA内,由此第二间隔D2可被实现为等于或小于第一间隔D1的一半,并且发光显示设备10可被实现为具有包括零边框或者未设置边框区的空气边框结构。

图7是用于描述根据本发明实施方式的多个开关电路部的图,图8是图解图7所示的第一焊盘部、一个开关电路部和堰部的图。图7和8示意性示出了根据本发明的实施方式用于感测设置在布线部中的布线的电阻的开关电路部以及与其相关的元件。

参照图1、7和8,在根据本发明实施方式的发光显示设备10中,多个开关电路部170的每一个可被设置为与堰部104交叠,并且可经由第一焊盘部110、布线部400、第二焊盘部210、连线部250和第三焊盘部230连接至驱动电路部500。多个开关电路部170的每一个可被配置为基于从驱动电路部500提供的开关控制信号而驱动(或切换)。

堰部104可包括第一至第三堰104-1至104-3,分离部105可包括设置在第一至第三堰104-1至104-3之间的第一分离结构105-1和第二分离结构105-2。

第一至第三堰104-1至104-3的每一个可被实现为彼此平行并在至少四个边围绕显示部,以一维地具有闭环线形状(或连续的线形状或闭环形状)。第一堰104-1可被设置为围绕第二堰104-2,第二堰104-2可被设置为围绕第三堰104-3。

第一至第三堰104-1至104-3的每一个可包括金属线104m。金属线104m可内置或实现在堰部104中(或内部),由此可一维地具有与堰部104相同的闭环线形状(或连续的线形状或闭环形状)。

第一分离结构105-1和第二分离结构105-2的每一个可被实现为彼此平行,以一维地具有闭环线形状(或连续的线形状或闭环形状)。第一分离结构105-1可设置在第一堰104-1和第二堰104-2之间。第二分离结构105-2可设置在第二堰104-2和第三堰104-3之间。第一分离结构105-1和第二分离结构105-2的每一个可与多条像素驱动线交叉。

在根据本发明实施方式的发光显示设备10中,第一焊盘部110可进一步包括第一至第三前感测控制焊盘112a、112b和112c以及第一至第三焊盘连接线176、177和178。

第一至第三前感测控制焊盘112a、112b和112c的每一个可设置在多个第一焊盘之间。例如,第一至第三前感测控制焊盘112a、112b和112c的每一个可如上参照图4所述逐个地设置在第一焊盘组PG1和第二焊盘组PG2之间的区域中。在测试模式中,第一至第三前感测控制焊盘112a、112b和112c的每一个可经由柔性电路部510、第三焊盘部230、连线部250、第二焊盘部210和布线部400从驱动IC 530接收相应的开关控制信号。

根据本发明的实施方式,第一至第三前感测控制焊盘112a、112b和112c的每一个可选自以某一间隔布置在第一焊盘部110中且未连接至像素驱动电源的多个前虚拟焊盘(front dummy pads)。例如,第一焊盘部110可包括多个前焊盘,多个前焊盘可包括或者被划分(或分类)为:多个第一数据焊盘DP1;多个第一栅极焊盘GP1;多个第一像素驱动电源焊盘PPP1;多个第一基准电压焊盘RVP1;多个第一像素公共电压焊盘CVP1;以及第一至第三前感测控制焊盘112a、112b和112c。

第一焊盘连接线176可被配置为电连接至第一前感测控制焊盘112a以及第一堰104-1的金属线104m。第一焊盘连接线176可沿着第二方向Y长长地延伸,以与第一前感测控制焊盘112a交叠并且与第一堰104-1的金属线104m交叠。例如,第一焊盘连接线176的一侧(或一端)可经由焊盘接触孔电连接至第一前感测控制焊盘112a。第一堰104-1的金属线104m可经由通孔176h电连接至第一焊盘连接线176的另一侧(或另一端)。因此,在测试模式中,从驱动IC 530提供给第一前感测控制焊盘112a的第一开关控制信号可经由第一焊盘连接线176被提供给第一堰104-1的金属线104m。

第二焊盘连接线177可被配置为电连接至第二前感测控制焊盘112b以及第二堰104-2的金属线104m。第二焊盘连接线177可沿着第二方向Y长长地延伸,以与第二前感测控制焊盘112b交叠并且与第二堰104-2的金属线104m交叠。例如,第二焊盘连接线177的一侧(或一端)可经由焊盘接触孔电连接至第二前感测控制焊盘112b。第二堰104-2的金属线104m可经由通孔177h电连接至第二焊盘连接线177的另一侧(或另一端)。因此,在测试模式中,从驱动IC 530提供给第二前感测控制焊盘112b的第二开关控制信号可经由第二焊盘连接线177被提供给第二堰104-2的金属线104m。

第三焊盘连接线178可被配置为电连接至第三前感测控制焊盘112c以及第三堰104-3的金属线104m。第三焊盘连接线178可沿着第二方向Y长长地延伸,以与第三前感测控制焊盘112c交叠并且与第三堰104-3的金属线104m交叠。例如,第三焊盘连接线178的一侧(或一端)可经由焊盘接触孔电连接至第三前感测控制焊盘112c。第三堰104-3的金属线104m可经由通孔178h电连接至第三焊盘连接线178的另一侧(或另一端)。因此,在测试模式中,从驱动IC 530提供给第三前感测控制焊盘112c的第三开关控制信号可经由第三焊盘连接线178被提供给第三堰104-3的金属线104m。

多个开关电路部170的每一个可沿着基板100的第一外围部或沿着最外像素Po的第一外围部设置。多个开关电路部170的每一个可设置(或包括)在多个最外像素Po中的相应最外像素中。多个开关电路部170的每一个可被设置为与堰部104交叠。多个开关电路部170的每一个可设置在堰部104和基板100的外表面之间以与堰部104交叠,由此可防止由多个开关电路部170导致的边框宽度的增加。

根据本发明实施方式的多个开关电路部170的每一个可包括第一至第三开关电路171、172和173。

第一至第三开关电路171、172和173可被设置为与第一至第三堰104-1、104-2和104-3单独地交叠。例如,第一开关电路171可与第一堰104-1交叠,或者可设置在第一堰104-1的下方。第二开关电路172可与第二堰104-2交叠,或者可设置在第二堰104-2的下方。第三开关电路173可与第三堰104-3交叠,或者可设置在第三堰104-3的下方。

第一至第三开关电路171、172和173的每一个可以是包括栅极Sg、第一电极Se1(或第一源极/漏极)和第二电极Se2(或第二源极/漏极)的薄膜晶体管(TFT)。具有这种构造的第一至第三开关电路171、172和173的每一个可与像素电路的驱动TFT Tdr一起形成。

在测试模式中,第一开关电路171可被配置为感测与设置在一个像素区PA中的两条数据线DLo和DLe中的第一数据线(或奇数数据线)DLo连接的数据布线的线电阻以及与基准电压线RL连接的基准布线的线电阻。第一开关电路171可电连接至设置在一个像素区PA中的第一数据线DLo、基准电压线RL和第一堰104-1的金属线104m。在测试模式中,第一开关电路171可基于经由第一堰104-1的金属线104m提供的第一开关控制信号而导通,并且可将经由第一数据线DLo提供的测试信号输出给基准电压线RL。

第一开关电路171的栅极Sg可与第一堰104-1的金属线104m交叠,或者可设置在第一堰104-1的金属线104m的下方,并且可经由第一控制线接触孔CLh1电连接至第一堰104-1的金属线104m。例如,第一堰104-1的金属线104m可以是第一开关控制线。

第一开关电路171的第一电极Se1可电连接至设置在一个像素区PA中的两条数据线DLo和DLe中的第一数据线(或奇数数据线)DLo。例如,第一开关电路171的第一电极Se1可延伸以与第一数据线DLo交叠或交叉,并且可经由第一接触孔CH1电连接至第一数据线DLo。

第一开关电路171的第二电极Se2可电连接至设置在一个像素区PA中的基准电压线RL。例如,第一开关电路171的第二电极Se2可延伸以与基准电压线RL交叠或交叉,并且可经由第二接触孔CH2电连接至基准电压线RL。当第一开关电路171导通时,基准电压线RL可用作感测线。

在测试模式中,第二开关电路172可被配置为感测与设置在一个像素区PA中的两条数据线DLo和DLe中的第二数据线(或偶数数据线)DLe连接的数据布线的线电阻以及与基准电压线RL连接的基准布线的线电阻。第二开关电路172可电连接至设置在一个像素区PA中的第二数据线DLe、基准电压线RL和第二堰104-2的金属线104m。在测试模式中,第二开关电路172可基于经由第二堰104-2的金属线104m提供的第二开关控制信号而导通,并且可将经由第二数据线DLe提供的测试信号输出给基准电压线RL。

第二开关电路172的栅极Sg可与第二堰104-2的金属线104m交叠,或者可设置在第二堰104-2的金属线104m的下方,并且可经由第二控制线接触孔CLh2电连接至第二堰104-2的金属线104m。例如,第二堰104-2的金属线104m可以是第二开关控制线。

第二开关电路172的第一电极Se1可电连接至设置在一个像素区PA中的两条数据线DLo和DLe中的第二数据线(或偶数数据线)DLe。例如,第二开关电路172的第一电极Se1可延伸以与第二数据线DLe交叠或交叉,并且可经由第一接触孔CH1电连接至第二数据线DLe。

第二开关电路172的第二电极Se2可电连接至设置在一个像素区PA中的基准电压线RL。例如,第二开关电路172的第二电极Se2可延伸以与基准电压线RL交叠或交叉,并且可经由第二接触孔CH2电连接至基准电压线RL。当第二开关电路172导通时,基准电压线RL可用作感测线。

在测试模式中,第三开关电路173可被配置为感测与设置在一个像素区PA中的第一数据线DLo和第二数据线DLe中的每一条连接的两条数据布线的线电阻。第三开关电路173可电连接至设置在一个像素区PA中的第一数据线DLo、第二数据线DLe和第三堰104-3的金属线104m。在测试模式中,第三开关电路173可基于经由第三堰104-3的金属线104m提供的第三开关控制信号而导通,并且可将经由第一数据线DLo提供的测试信号输出给第二数据线DLe。

第三开关电路173的栅极Sg可与第三堰104-3的金属线104m交叠,或者可设置在第三堰104-3的金属线104m的下方,并且可经由第三控制线接触孔CLh3电连接至第三堰104-3的金属线104m。例如,第三堰104-3的金属线104m可以是第三开关控制线。

第三开关电路173的第一电极Se1可电连接至第一数据线DLo。例如,第三开关电路173的第一电极Se1可延伸以与第一数据线DLo交叠或交叉,并且可经由第一接触孔CH1电连接至第一数据线DLo。

第三开关电路173的第二电极Se2可电连接至第二数据线DLe。例如,第三开关电路173的第二电极Se2可延伸以与第二数据线DLe交叠或交叉,并且可经由第二接触孔CH2电连接至第二数据线DLe。

图9是沿图2和8所示的线I-I’截取的剖视图,图10是图9所示的区域B2的放大图,图11是图9所示的区域B3的放大图,图12是沿图2和8所示的线II-II’截取的剖视图。图9至12示意性示出了根据本发明的实施方式包括堰部和多个开关电路部等的最外像素的剖面结构,因此在下文描述中,对与上文参照图1-8描述的那些元件相同的元件的描述将省略或简要进行。

参照图2和8至12,根据本发明实施方式的发光显示设备(或发光显示面板)10可包括基板100、线基板200、接合构件(coupling member)300以及布线部400。

根据本发明实施方式的基板100可包括电路层101、多个开关电路部170、平坦化层102、发光器件层EDL、堤部103、堰部104以及封装层106。

电路层101可设置在基板100上。电路层101可称为像素阵列层或TFT阵列层。

根据实施方式的电路层101可包括缓冲层101a和电路阵列层101b。

缓冲层101a可防止在制造TFT的工艺的高温工艺中,包含在基板100中的诸如氢等之类的材料扩散到电路阵列层101b中。此外,缓冲层101a可防止外部水分或湿气渗透到发光器件层EDL中。例如,缓冲层101a可由无机材料形成。

电路阵列层101b可包括:在缓冲层101a上方包括设置在多个像素区PA的每一个中的驱动TFT Tdr的像素电路PC;多个开关电路部170以及钝化层PAS。

设置在每个像素区PA的电路区中的驱动TFT Tdr可包括有源层ACT、栅极绝缘层GI、栅极GE、第一电极SD1和第二电极SD2。

有源层ACT可设置在每个像素区PA中的缓冲层101a上。有源层ACT可包括与栅极GE交叠的沟道区以及彼此平行且其间插置有沟道区的第一电极接触区和第二电极接触区。有源层ACT可在导电化工艺(即,使有源层ACT的材料导电的工艺)中获得导电性,由此可用作直接连接(或接触)显示部AA内的线或者电连接(或接触)不同层上设置的线的跳接结构的桥接线。

栅极绝缘层GI可设置在有源层ACT的沟道区上。栅极绝缘层GI可将有源层ACT与栅极GE绝缘。

栅极GE可设置在栅极绝缘层GI上并且连接至栅极线。栅极GE可与有源层ACT的沟道区在其间具有栅极绝缘层GI的条件下交叠。栅极GE和有源层ACT可被层间绝缘层ILD覆盖。

层间绝缘层ILD可设置在基板100上以覆盖栅极GE和有源层ACT。例如,层间绝缘层ILD可由无机材料形成。根据实施方式的层间绝缘层ILD可包括具有硅氧化物(SiOx)、硅氮化物(SiNx)、硅氮氧化物(SiONx)、钛氧化物(TiOx)和铝氧化物(AlOx)的其中之一的单层结构或其堆叠结构,但本发明的实施方式不限于此。例如,层间绝缘层ILD可称为绝缘层或第一绝缘层。

第一电极SD1可设置在层间绝缘层ILD上并与有源层ACT的第一电极接触区交叠,并且可经由设置在层间绝缘层ILD中的第一通孔电连接至(或接触)有源层ACT的第一电极接触区。例如,第一电极SD1可以是驱动TFT Tdr的源极,有源层ACT的第一电极接触区可以是源极区。

第二电极SD2可设置在层间绝缘层ILD上并与有源层ACT的第二电极接触区交叠,并且可经由设置在层间绝缘层ILD中的第二通孔电连接至(或接触)有源层ACT的第二电极接触区。例如,第二电极SD2可以是驱动TFT Tdr的漏极,有源层ACT的第二电极接触区可以是漏极区。

如图5所示,构成像素电路PC的第一开关TFT Tsw1和第二开关TFT Tsw2的每一个可与驱动TFT Tdr一起形成,因此省略其重复描述。

多个开关电路部170可形成在最外像素Po的外围部MA3中。多个开关电路部170可包括第一至第三开关电路171、172和173。具有这种构造的第一至第三开关电路171、172和173的每一个可与驱动TFT Tdr一起形成,因此省略其重复描述。

根据实施方式的电路层101可进一步包括设置在基板100和缓冲层101a之间的下金属层BML。下金属层BML可包括光阻挡图案(或光阻挡层)LSP,其设置在构成像素电路PC的TFT Tdr、Tsw1和Tsw2的每一个的有源层ACT的下方(或下部)。

光阻挡图案LSP可在基板100和有源层ACT之间设置成岛状。光阻挡图案LSP可阻挡经由基板100入射在有源层ACT上的光,由此防止或最小化由外部光导致的每个TFT的阈值电压变化。可选地,光阻挡图案LSP可电连接至相应TFT的第一电极SD1,由此可用作相应TFT的下栅极;在这种情形下,可最小化、减小或防止由光导致的每个TFT的特性变化以及由偏置电压导致的每个TFT的阈值电压变化。

下金属层BML可用作与栅极线GL、数据线DL、像素驱动电源线PL、像素公共电压线CVL和基准电压线RL的每一条平行地设置的线。例如,下金属层BML可用作沿第二方向Y与设置在基板100上的像素驱动线DL、GL、PL、CVL、RL和GCL彼此平行地设置的线(或金属层)。

钝化层PAS可设置在基板100上,以覆盖包括驱动TFT Tdr的像素电路PC。钝化层PAS可以是覆盖设置在每个子像素SPA中的驱动TFT Tdr的电路层101的最上层,但本发明的实施方式不限于此。钝化层PAS可由与层间绝缘层ILD相同或不同的无机材料形成。例如,钝化层PAS可包括具有硅氧化物(SiOx)、硅氮化物(SiNx)、硅氮氧化物(SiONx)、钛氧化物(TiOx)和铝氧化物(AlOx)的其中之一的单层结构或其堆叠结构。例如,钝化层PAS可称为保护层、电路保护层、电路绝缘层、无机绝缘层、第一无机绝缘层或第二绝缘层等。

平坦化层102可设置在其上设置有钝化层PAS的基板100上,并且可在钝化层PAS上方提供平坦表面。例如,钝化层PAS可设置在层间绝缘层ILD和平坦化层102之间。

平坦化层102可被形成为覆盖除了设置在基板100的外围部处的钝化层PAS的外围部之外的其余电路层101。例如,平坦化层102可设置在基板100和发光器件层EDL之间,或者设置在发光器件层EDL的下方。根据实施方式的平坦化层102可由有机材料形成,但本发明的实施方式不限于此。例如,平坦化层102可由包含丙烯酸树脂、环氧树脂、酚醛树脂、聚酰胺基树脂、聚酰亚胺基树脂等的有机材料形成,但本发明的实施方式不限于此。

发光器件层EDL可设置在平坦化层102上。根据实施方式的发光器件层EDL可包括像素电极PE、自发光器件ED和公共电极CE。应理解,术语“自发光器件”包括当施加电压时输出光的层,其可指与像素电极PE和公共电极CE接触的发光层,即自发光层的任何部分;一般而言,其将包括在像素中存在三个层并且不存在堤部103的所有区域,如图9所示。

像素电极PE可称为自发光器件ED的阳极或第一电极,或者可称为反射电极或下电极。像素电极PE可设置在平坦化层102上并与每个子像素SP的发光区EA交叠。像素电极PE可被设置为与像素电路PC的至少一部分或全部交叠。

像素电极PE可包括设置在发光区EA中并与像素电路PC的至少一部分或全部交叠的多个像素分割电极PEa和PEb,但本发明的实施方式不限于此,像素电极PE可包括单电极结构,其在发光区EA中形成为单体(或一体)并与像素电路PC的至少一部分或全部交叠。

根据本发明实施方式的像素电极PE可包括设置在发光区EA的一个区中的第一像素分割电极PEa以及设置在发光区EA的另一区中的第二像素分割电极PEb。多个像素分割电极PEa和PEb可在相应的发光区EA(或子像素区PSA)内彼此分隔地设置。多个像素分割电极PEa和PEb的每一个的一侧可延伸(或突出)到驱动TFT Tdr的第一电极SD1,并且可经由电极接触孔ECH共同连接至驱动TFT Tdr的第一电极SD1。例如,多个像素分割电极PEa和PEb的每一个可从设置在发光区EA(或子像素区PSA)内的电极接触孔ECH分支。

当由于制造工艺中的颗粒而出现缺陷时,可实现多个像素分割电极PEa和PEb以修复相应子像素(或使相应子像素正常化)。例如,当由于颗粒在多个像素分割电极PEa和PEb的第一像素分割电极PEa中出现缺陷时,驱动TFT Tdr的第一电极SD1可通过在修复工艺中切割第一像素分割电极PEa的延伸部而与第一像素分割电极PEa电断开(或电分离),由此可经由除了第一像素分割电极PEa之外的其他像素分割电极PEb修复相应子像素(或使相应子像素正常化)。

像素电极PE可包括至少两层或更多层像素电极层PEL1和PEL2的堆叠结构。例如,至少两层或更多层像素电极层PEL1和PEL2的每一层可包括选自氧化铟锡(ITO)、氧化铟锌(IZO)、铝(Al)、银(Ag)、钼(Mo)、钛(Ti)、MoTi和铜(Cu)的至少一种材料。例如,至少两层或更多层像素电极层PEL1和PEL2可依次堆叠在平坦化层102上,然后可被同时图案化,但本发明的实施方式不限于此。

根据本发明实施方式的像素电极PE可具有包括设置在平坦化层102上的第一像素电极层(或第一金属层)PEL1以及设置(或堆叠)在第一像素电极层PEL1上的第二像素电极层(或第二金属层)PEL2的双层结构。第一像素电极层PEL1和第二像素电极层PEL2可依次沉积在平坦化层102上,然后可被同时图案化,但本发明的实施方式不限于此。

第一像素电极层PEL1可用作对应于平坦化层102的粘合层,并且可用作自发光器件ED的辅助电极,且可包括氧化铟锡(ITO)或氧化铟锌(IZO)。第二像素电极层PEL2可用作反射板,并且可执行降低像素电极PE的电阻的功能,且可包含铝(Al)、银(Ag)、钼(Mo)、钛(Ti)、MoTi合金(MoTi)和铜(Cu)中的其中一种材料。

根据本发明另一实施方式的像素电极PE可具有IZO/MoTi/ITO或ITO/MoTi/ITO的三层结构、ITO/Cu/MoTi/ITO的四层结构或ITO/MoTi/ITO/Ag/ITO的五层结构,但本发明的实施方式不限于此。

自发光器件ED可设置在基板100上。自发光器件ED可形成在像素电极PE上并且可直接接触像素电极PE。像素电极PE可设置在自发光器件ED的下方(或下部)。

自发光器件ED可以是共同形成在多个子像素SP的每一个中且不以子像素SP为单位进行区分的公共层。自发光器件ED可对在像素电极PE和公共电极CE之间流动的电流作出反应,以发射白色光(或蓝色光)。自发光器件ED可包括有机发光器件,或者可包括有机发光器件和量子点发光器件的堆叠或组合结构。

有机发光器件用于包括与发射白色光(或蓝色光)的两个或更多个有机发光部。例如,有机发光器件可包括用于基于第一光和第二光的组合发射白色光的第一有机发光部和第二有机发光部。例如,第一有机发光部可包括蓝色发光层、绿色发光层、红色发光层、黄色发光层和黄绿色发光层的至少之一。第二有机发光部可包括蓝色发光层、绿色发光层、红色发光层、黄色发光层和黄绿色发光层的至少之一,以便发射与来自第一有机发光部的第一光相组合以产生白色光的第二光。

有机发光器件可进一步包括用于提高发光效率和/或寿命的至少一个或多个功能层。例如,功能层可设置在发光层的上方和/或下方。

公共电极CE可设置在基板100的显示部AA上,并且可电连接至位于多个子像素SP的每一个处的自发光器件ED。公共电极CE可称为阴极电极、透明电极、上电极、阴极或第二电极。公共电极CE可形成在自发光器件ED上,并且可直接接触自发光器件ED或者可电性地直接接触自发光器件ED。公共电极CE可包括透射从自发光器件ED发射的光的透明导电材料。

此外,发光器件层EDL可进一步包括设置在公共电极CE上的盖层(cappinglayer)。盖层可设置在公共电极CE上并且可通过调节从发光器件层EDL发射的光的折射率来提高发光效率。

堤部103可设置在平坦化层102上以包括与子像素区SPA的发光区EA交叠的开口部。堤部103可设置在平坦化层102上以覆盖像素电极PE的外围部。堤部103可与多个子像素SP的每一个的发光区(或开口部)EA相邻并且可将设置在相邻子像素SP中的像素电极PE电隔离。堤部103可被形成为覆盖位于每个像素区PA中的电极接触孔ECH。堤部103可被发光器件层EDL的自发光器件ED覆盖。例如,自发光器件ED可设置在堤部103上以及在每个子像素SP的像素电极PE上。

堰部104可实现在基板100的外围部或者最外像素Po的外围部处。堰部104可设置在显示部AA的电路层101上方以沿着最外像素Po的第三裕度区MA3一维地具有闭环线形状(或连续的线形状或闭环形状)。例如,堰部104可基于形成位置由电路层101的层间绝缘层ILD支撑,或者可设置在开关电路部170上。例如,第三裕度区MA3可以是包括堰部104的区域。

堰部104可被实现为隔离(或断开或分离)位于基板100的外围部或最外像素Po的外围部处的发光器件层EDL的至少一些层。在基板100的外围部或最外像素Po的外围部处,堰部104可包含物理地隔离(或断开或分离)发光器件层EDL的自发光器件ED的功能、阻挡有机封装层的扩散或溢出的功能、以及防止水分(或湿气)在基板100的侧向上渗透的功能。下文将描述用于隔离(或断开或分离)发光器件层EDL的堰部104的结构。

封装层106可设置在除了基板100的最外的外围部之外的其余部分上并且可被实现为覆盖发光器件层EDL。封装层106可实现在基板100上方以围绕发光器件层EDL的前表面和侧表面的全部。例如,封装层106可被实现为围绕发光器件层EDL的前表面和侧表面的全部,由此可防止氧气或水分(或湿气)渗透到发光器件层EDL,从而提高发光器件层EDL对于氧气或水分(或湿气)的可靠性。

封装层106可包括第一封装层106a、第二封装层106b和第三封装层106c。

第一封装层106a可被实现为防止氧气或水分(或湿气)渗透到发光器件层EDL。第一封装层106a可设置在公共电极CE上并且可围绕发光器件层EDL。因此,发光器件层EDL的前表面和侧表面的全部可被第一封装层106a围绕。第一封装层106a可以是包含无机材料的第一无机封装层。例如,第一封装层106a可包括具有硅氧化物(SiOx)、硅氮化物(SiNx)、硅氮氧化物(SiONx)、钛氧化物(TiOx)和铝氧化物(AlOx)的其中之一的单层结构,或其堆叠结构。

第二封装层106b可在由堰部104限定的封装区中实现在第一封装层106a上,并具有相对厚于第一封装层106a的厚度。第二封装层106b可具有被配置为完全覆盖位于或可位于第一封装层106a上的颗粒(或不期望的材料或不期望的结构元素)的厚度。第二封装层106b可被堰部104围绕。第二封装层106b可由于相对较厚的厚度而扩散到基板100的外围部,但是第二封装层106b的扩散可被堰部104阻挡。第二封装层106b可包括有机材料或液体有机材料。例如,第二封装层106b可包括诸如硅碳氧化物(SiOCz)丙烯酸或环氧基树脂等之类的有机材料。例如,第二封装层106b可称为颗粒覆盖层或有机封装层等。

第三封装层106c可被实现为初次(primarily)防止氧气或水分(或湿气)渗透到发光器件层EDL。第三封装层106c可被实现为围绕设置在堰部105内侧的第二封装层106b以及设置在堰部105外侧的第一封装层106a的全部。根据本发明实施方式的第三封装层106c可包括与第一封装层106a相同或不同的无机材料。第三封装层106c可以是包含无机材料的第二无机封装层。

根据本发明实施方式的发光显示设备10或基板100可进一步包括分离部105。

分离部105可设置或实现在基板100的外围部或最外像素Po的外围部处。分离部105可在最外像素Po的第三裕度区MA3中,设置或实现在基板100的外围部或最外像素Po的外围部处以沿着堰部104的附近区域一维地具有闭环线形状(或连续的线形状或闭环形状)。例如,分离部105可设置在电路层101上,并且可被电路层101的缓冲层101a或层间绝缘层ILD支撑。

在最外像素Po中,第一裕度区MA1可设置在第三裕度区MA3和发光区EA之间。例如,基于由水分(或湿气)的侧向渗透导致的发光器件层EDL的可靠性裕度,第一裕度区MA1可设置在最外像素Po的发光区EA的端部(或堤部103)与堰部104之间。例如,第二裕度区MA2可设置在基板100的外表面OS1a和第三裕度区MA3之间。例如,基于由水分(或湿气)的侧向渗透导致的发光器件层EDL的可靠性裕度,第二裕度区MA2可被配置为在基板100的外表面OS1a和堰部104之间具有第二宽度,并且可包括第一焊盘部110。第三裕度区MA3可设置在第一裕度区MA1和第二裕度区MA2之间,并且可包括堰部104。

分离部105可被实现为隔离(或断开或分离)位于最外像素Po的外围部处的自发光器件ED。分离部105可被实现为防止水分(或湿气)在基板100的侧向方向上渗透,以防止自发光器件ED由于水分(或湿气)的侧向渗透而劣化。分离部105可在堰部104附近隔离(或断开或分离)发光器件层EDL的自发光器件ED至少一次,由此可防止水分(或湿气)的侧向渗透。将在下文描述分离部105。

参照图2、4、8和10,根据本发明实施方式的发光显示设备10或基板100可进一步包括第一焊盘部110。

第一焊盘部110可设置在基板100的一个外围部处,并且可按照一一对应的关系电连接至像素驱动线DL、GL、PL、CVL、RL和GCL。

根据实施方式的第一焊盘部110可包括设置在电路层101内部的多个第一焊盘111。多个第一焊盘111可被划分(或分类)为第一数据焊盘DP1、第一栅极焊盘GP1、第一像素驱动电源焊盘PPP1、第一基准电压焊盘RVP1和第一像素公共电压焊盘CVP1。根据实施方式的第一焊盘部110可进一步包括第一至第三前感测控制焊盘112a、112b和112c以及第一至第三焊盘连接线176、177和178。

多个第一焊盘111以及第一至第三前感测控制焊盘112a、112b和112c的每一个可设置在层间绝缘层ILD上,并且可经由穿过层间绝缘层ILD和缓冲层101a的焊盘接触孔PCH电连接至(或接触)像素驱动线DL、GL、PL、CVL、RL和GCL中的相应线。例如,根据实施方式的多个第一焊盘111以及第一至第三前感测控制焊盘112a、112b和112c的每一个可包含与像素电极PE相同的材料,并且可与像素电极PE一起形成。例如,根据另一实施方式的多个第一焊盘111以及第一至第三前感测控制焊盘112a、112b和112c的每一个可包含与TFT的源极/漏极相同的材料,并且可与TFT的源极/漏极一起形成。

多个第一焊盘111以及第一至第三前感测控制焊盘112a、112b和112c的每一个的一部分可经由形成在钝化层PAS处的焊盘开孔POH在基板100上方暴露。

再次参见图9,根据本发明实施方式的发光显示设备10或基板100可进一步包括设置在封装层106上的波长转换层107。

波长转换层107可将从每个子像素区SPA的发光区EA入射到其上的白色光(或蓝色光)转换成与每个子像素区SPA对应的颜色的光,或者可仅透射与子像素SP对应的颜色的光。例如,波长转换层107可包括波长转换构件和滤色器层的至少之一。

波长转换层107可包括多个波长转换构件107a以及保护层107b。

多个波长转换构件107a可设置在位于每个子像素SP的发光区EA处的封装层106上。例如,多个波长转换构件107a可具有等于或宽于每个子像素SP的发光区EA的尺寸。多个波长转换构件107a可分组(或分类)为在红色子像素SP的发光区EA中设置在封装层106上方的红色滤光器(或第一滤光器)、在绿色子像素SP的发光区EA中设置在封装层106上方的绿色滤光器(第二滤光器)、以及在蓝色子像素SP的发光区EA中设置在封装层106上方的蓝色滤光器(或第三滤光器)。

保护层107b可被实现为覆盖波长转换构件107a,并且在波长转换构件107a上提供平坦表面。保护层107b可被设置为覆盖波长转换构件107a以及其中未设置有波长转换构件107a的封装层106。根据实施方式的保护层107b可包含有机材料。可选地,保护层107b可进一步包括用于吸附水分和/或氧气的吸附剂材料(getter material)。

可选地,波长转换层107可变成(或配置为)片形式(sheet form)的波长转换片,并且可设置在封装层106上。在这种情形下,波长转换片(或量子点片)可包括插置在一对膜之间的波长转换构件107a。例如,当波长转换层107或波长转换片包括在子像素SP中再次发射彩色光组(colored light set)的量子点时,子像素SP的发光器件层EDL可被实现为发射白色光或蓝色光。

根据本发明实施方式的发光显示设备10或基板100可进一步包括功能膜108。功能膜108可设置在波长转换层107上。例如,功能膜108可通过透明粘合构件接合至波长转换层107。根据实施方式的功能膜108可包括抗反射层(或抗反射膜)、阻挡层(或阻挡膜)、触摸感测层和光路控制层(或光路控制膜)的至少之一。

抗反射层可包括防止由设置在基板100处的TFT和/或像素驱动线反射的外部光传播到外部的圆偏振层(或圆偏振膜)。阻挡层可包括透水率较低的材料(例如聚合物材料),并且可初次防止水分或氧气的渗透。触摸感测层可包括基于互电容法或自电容法的触摸电极层,并且可经由触摸电极层输出对应于用户触摸的触摸数据。光路控制层可包括交替堆叠有高折射率层和低折射率层的堆叠结构,并且可改变从每个像素P入射的光的路径,以最小化或减小基于视角的色偏移。

根据本发明实施方式的发光显示设备10或基板100可进一步包括侧向密封构件109。

侧向密封构件109可形成在基板100和功能膜108之间,并且可覆盖电路层101和波长转换层107的全部侧表面。例如,侧向密封构件109可在功能膜108和基板100之间覆盖暴露到发光显示设备外部的、电路层101和波长转换层107的每一个的侧表面的全部。此外,侧向密封构件109可覆盖与基板100的第一焊盘部110连接的布线部400的一部分。侧向密封构件109可防止由于在从每个子像素SP的自发光器件ED发射的光之中的、从波长转换层107的内部传播到其外部的光导致的侧向光泄漏。尤其是,与基板100的第一焊盘部110交叠的侧向密封构件109可防止或最小化或减小由设置在第一焊盘部110处的第一焊盘111导致的外部光的反射。可选地,侧向密封构件109可进一步包括用于吸附水分(或湿气)和/或氧气的吸附剂材料。

根据本发明实施方式的发光显示设备10或基板100可进一步包括第一斜切部(chamfer)100c,其设置在第一表面100a和外表面OS之间的拐角部处。第一斜切部100c可减小或最小化由从外部施加的物理冲击导致的基板100的拐角部的损坏,并且可防止由基板100的拐角部导致的布线部400的断开。例如,第一斜切部100c可具有45度角,但本发明的实施方式不限于此。第一斜切部100c可通过使用切割轮、抛光轮、激光等的斜切工艺(chamferprocess)实现。因此,被设置为与第一斜切部100c接触的第一焊盘部110的第一焊盘111的每个外表面可通过经由斜切工艺与基板100的拐角部一起去除或抛光其相应部分而包括倾斜表面,其倾斜了与第一斜切部100c的角度对应的角度。例如,当第一斜切部100c以45度的角度形成在基板100的外表面OS和第一表面100a之间时,第一焊盘部110的第一焊盘111的外表面(或一端)可形成为45度的角度。

参照图2、4、7和9,根据本发明实施方式的线基板200可包括第二焊盘部210、至少一个第三焊盘部230以及连线部250。

第二焊盘部210可包括多个第二焊盘211,其设置在线基板200的后表面200b处并按照一一对应的关系与设置在第一焊盘部110中的多个第一焊盘交叠。多个第二焊盘211可分组(或分类)为多个第二像素驱动电源焊盘、多个第二数据焊盘、多个第二基准电压焊盘、多个第二栅极焊盘以及多个第二像素公共电压焊盘。

多个第二像素驱动电源焊盘可与设置在第一焊盘部110处的多个第一像素驱动电源焊盘PPP1的每一个交叠。多个第二数据焊盘可与设置在第一焊盘部110处的多个第一数据焊盘DP1的每一个交叠。多个第二基准电压焊盘可与设置在第一焊盘部110处的多个第一基准电压焊盘RVP1的每一个交叠。多个第二栅极焊盘可与设置在第一焊盘部110处的多个第一栅极焊盘GP1的每一个交叠。多个第二像素公共电压焊盘可与设置在第一焊盘部110处的多个第一像素公共电压焊盘CVP1的每一个交叠。

第二焊盘部210可进一步包括分别与设置在第一焊盘部110中的第一至第三前感测控制焊盘112a、112b和112c交叠的第一至第三后感测控制焊盘。根据本发明的实施方式,第一至第三后感测控制焊盘的每一个可选自分别与多个前虚拟焊盘交叠的多个后虚拟焊盘。例如,第二焊盘部210可包括多个后焊盘,多个后焊盘可被分组(或分类)为多个第二像素驱动电源焊盘、多个第二数据焊盘、多个第二基准电压焊盘、多个第二栅极焊盘、多个第二像素公共电压焊盘以及第一至第三后感测控制焊盘。

至少一个第三焊盘部230可包括按照某一间隔彼此分隔开的多个第三焊盘(或输入焊盘)231。例如,多个第三焊盘231可分组(或分类)为多个第三像素驱动电源焊盘、多个第三数据焊盘、多个第三基准电压焊盘、多个第三栅极焊盘以及至少一个第三像素公共电压焊盘。至少一个第三焊盘部230可接合至驱动电路部500,并且可从驱动电路部500接收像素驱动电源、数据信号、基准电压、栅极控制信号和像素公共电压。驱动电路部500可向金属线104m提供接地电压。

此外,至少一个第三焊盘部230可进一步包括从驱动电路部500接收第一至第三开关控制信号的第一至第三开关控制信号焊盘。

连线部250可包括在线基板200的后表面200b中设置在第二焊盘部210和至少一个第三焊盘部230之间的多条连线。

多条连线可分组(或分类)为多条像素驱动电源连线、多条数据连线、多条基准电压连线、多条栅极连线以及至少一条像素公共电压连线。

多条像素驱动电源连线可单独地(或以一一对应的关系)连接(或接合)至每个第二像素驱动电源焊盘以及每个第三像素驱动电源焊盘。多条数据连线可单独地(或以一一对应的关系)连接(或接合)至每个第二数据焊盘和每个第三数据焊盘。多条基准电压连线可单独地(或以一一对应的关系)连接(或接合)至每个第二基准电压焊盘和每个第三基准电压焊盘。多条栅极连线可单独地(或以一一对应的关系)连接(或接合)至每个第二栅极焊盘和每个第三栅极焊盘。至少一条像素公共电压连线可共同连接(或接合)至每个第二像素公共电压焊盘以及至少一个第三像素公共电压焊盘。

此外,在连线部250中,多条连线可进一步划分(或分类)为第一至第三感测控制连线。例如,连线部250可进一步包括第一至第三感测控制连线。第一至第三感测控制连线可单独地(或以一一对应的关系)连接至位于第二焊盘部210处的第一至第三后感测控制焊盘的每一个以及位于至少一个第三焊盘部230处的第一至第三开关控制信号焊盘的每一个。

根据本发明实施方式的发光显示设备10或线基板200可进一步包括金属图案层和绝缘层。

金属图案层(或导电图案层)可包括多个金属层。金属图案层可包括第一金属层201、第二金属层203和第三金属层205。绝缘层可包括多个绝缘层。例如,绝缘层可包括第一绝缘层202、第二绝缘层204和第三绝缘层206。绝缘层可称为后绝缘层或图案绝缘层。

第一金属层201可实现在线基板200的后表面200b上。第一金属层201可包括第一金属图案。例如,第一金属层201可称为第一连接层或连线层。第一金属图案可用作连线部250的连线。

第一绝缘层202可实现在线基板200的后表面200b上以覆盖第一金属层201。根据实施方式的第一绝缘层202可包括无机材料。

第二金属层203可实现在第一绝缘层202上。根据实施方式的第二金属层203可包括第二金属图案。例如,第二金属层203可称为第二连接层、跳接线层或桥接线层。第二金属图案可用作连线部250的连线中的栅极连线,但本发明的实施方式不限于此。例如,第二金属层203可用作跳接线(或桥接线),以电连接在连线部250中的不同层上由不同金属材料形成的连线。

可选地,设置在第二金属层203处的连线(例如多条第一连线)可被修改为设置在第一金属层201处,并且设置在第一金属层201处的连线(例如多条第二连线)可被修改为设置在第二金属层203处。

第二绝缘层204可实现在线基板200的后表面200b上,以覆盖第二金属层203。根据实施方式的第二绝缘层204可包含无机材料。

第三金属层205可实现在第二绝缘层204上。根据实施方式的第三金属层205可包括第三金属图案。例如,第三金属层205可称为第三连接层或焊盘电极层。第三金属图案可用作第二焊盘部210的焊盘。例如,由第三金属层205形成的第二焊盘部210的焊盘可经由形成在第一绝缘层202和第二绝缘层204处的焊盘接触孔电连接至(或接触)第一金属层201。

第三绝缘层206可实现在线基板200的后表面200b上以覆盖第三金属层205。根据实施方式的第三绝缘层206可包含有机材料。例如,第三绝缘层206可包含诸如光学丙烯酸(photo acrylic)等之类的绝缘材料。第三绝缘层206可覆盖第三金属层205,以防止第三金属层205暴露到外部。第三绝缘层206可称为有机绝缘层、保护层、后保护层、有机保护层、后涂覆层或后覆盖层。

根据实施方式的布线部400可包括多条布线410,其设置在基板100的外表面OS中的第一外表面OS1a和线基板200的外表面OS中的第一外表面OS1b的每一个处。

多条布线410的每一条可按照一一对应的关系电连接至第一焊盘部110的第一焊盘111和第二焊盘部210的第二焊盘211的每一个。换句话说,多条布线410的每一条可电连接至第一焊盘部110的第一焊盘111中的相应一个以及第二焊盘部210的第二焊盘211中的相应一个。多条布线410可分组(或分类)为多条像素电源布线、多条数据布线、多条基准电压布线、多条栅极布线以及多条像素公共电压布线。

多条像素电源布线可单独地(或以一一对应的关系)连接(或接合)至位于第一焊盘部110处的每个第一像素驱动电源焊盘PPP1和位于第二焊盘部210处的每个第二像素驱动电源焊盘。多条数据布线可单独地(或以一一对应的关系)连接(或接合)至位于第一焊盘部110处的每个第一数据焊盘DP1和位于第二焊盘部210处的每个第二数据焊盘。多条基准电压布线可单独地(或以一一对应的关系)连接(或接合)至位于第一焊盘部110处的每个第一基准电压焊盘RVP1和位于第二焊盘部210处的每个第二基准电压焊盘。多条栅极布线可单独地(或以一一对应的关系)连接(或接合)至位于第一焊盘部110处的每个第一栅极焊盘GP1以及位于第二焊盘部210处的每个第二栅极焊盘。多条像素公共电压布线可单独地(或以一一对应的关系)连接(或接合)至位于第一焊盘部110处的每个第一像素公共电压焊盘CVP1和位于第二焊盘部210处的每个第二像素公共电压焊盘。

此外,在布线部400中,多条布线410可进一步划分(或分类)为第一至第三感测控制布线。例如,布线部400可进一步包括第一至第三感测控制布线。第一至第三感测控制布线可单独地(或以一一对应的关系)连接至位于第一焊盘部110处的第一至第三前感测控制焊盘112a、112b和112c的每一个以及位于第二焊盘部210处的第一至第三后感测控制焊盘的每一个。

多条布线410以及第一至第三感测控制布线的每一条可被形成为围绕基板100的外表面OS1a以及线基板200的外表面OS1b。根据本发明的实施方式,多条布线410以及第一至第三感测控制布线的每一条可通过使用导电胶的印刷工艺形成。根据本发明的另一实施方式,多条布线410以及第一至第三感测控制布线的每一条可通过将导电胶图案转移到柔性材料的转移焊盘并将转移到转移焊盘的导电胶图案转移到布线部400的转移工艺(transfer process)形成。例如,导电胶可以是Ag胶,但本发明的实施方式不限于此。

根据本发明实施方式的发光显示设备10或布线部400可进一步包括边缘涂覆层430。

边缘涂覆层430可被实现为覆盖布线部400。边缘涂覆层430可被实现为覆盖多条布线410以及第一至第三感测控制布线的每一条。例如,边缘涂覆层430可以是边缘保护层或边缘绝缘层。

根据实施方式的边缘涂覆层430可被实现为覆盖基板100的第一外围部和第一外表面OS1a、线基板200的第一外围部和第一外表面OS1b、多条布线410以及第一至第三感测控制布线的全部。边缘涂覆层430可防止包含金属材料的多条布线410以及第一至第三感测控制布线的每一条的腐蚀,或者可防止在多条布线410与第一至第三感测控制布线的每一条之间的电短路。此外,边缘涂覆层430可防止或最小化或减小由多条布线410、第一至第三感测控制布线、以及第一焊盘部110的第一焊盘111导致的外部光的反射。边缘涂覆层430可包含具有黑色墨水的光阻挡材料。边缘涂覆层430可实现(或构成)发光显示设备(或发光显示面板)的最外侧表面(或侧壁),由此可包含冲击吸收材料(或物质)或延展性材料,以便防止基板100和200的外表面OS由于外部冲击而损坏。作为另一实施方式,边缘涂覆层430可包括光阻挡材料和冲击吸收材料的混合材料。

下文将参照图9、11和12描述堰部104、多个开关电路部170以及分离部105。

根据本发明实施方式的堰部104的第一至第三堰104-1至104-3的每一个可包括第一堰图案(或下堰)104a、第二堰图案(或中间堰)104b、金属线104m和第三堰图案(或上堰)104c。

第一堰图案104a可设置在最外像素Po或基板100的第三裕度区MA3的电路层101上。第一堰图案104a的一部分可设置在开关电路部170上。第一堰图案104a可由无机材料形成。

根据本发明的实施方式,第一堰图案104a可包括与钝化层PAS相同的材料。第一堰图案104a可在钝化层PAS的单层结构中实现。在这种情形下,第一堰图案104a可通过钝化层PAS的被原样保留、而不被设置在第三裕度区MA3的层间绝缘层ILD上的钝化层PAS的图案化工艺图案化(或去除)的部分(或非图案化区域)来形成或实现。

根据本发明的实施方式,第一堰图案104a可在钝化层PAS和层间绝缘层ILD的堆叠结构中实现。在这种情形下,第一堰图案104a可通过层间绝缘层ILD和钝化层PAS的被原样保留、而不被设置在第三裕度区MA3的缓冲层101a上的层间绝缘层ILD和钝化层PAS的图案化工艺图案化(或去除)的部分(或非图案化区域)来形成或实现。

第一堰图案104a的侧表面可实现为倾斜结构或正锥形结构。例如,沿着宽度方向截取的第一堰图案104a的剖面可具有梯形剖面结构,其中上侧比下侧窄。

第二堰图案104b可设置在第一堰图案104a上。根据实施方式的第二堰图案104b可由无机材料形成。例如,第二堰图案104b可由与平坦化层102相同的材料形成。第二堰图案104b可具有与平坦化层102相同的高度(或厚度),或者可具有高于平坦化层102的高度。例如,基于平坦化层102的两倍沉积,第二堰图案104b的高度(或厚度)可以是平坦化层102的高度(或厚度)的两倍。第二堰图案104b可通过平坦化层102的被原样保留、而不被平坦化层102的图案化工艺图案化(或去除)的部分(或非图案化区域)来形成或实现。

第二堰图案104b的侧表面可实现为倾斜结构或正锥形结构。例如,沿宽度方向截取的第二堰图案104b的剖面可具有与第一堰图案104a相同的梯形剖面结构。相对于宽度方向,第二堰图案104b的一个边缘部和另一边缘部的每一个可突出到第一堰图案104a的侧表面的外侧。例如,在第二堰图案104b的侧表面的端部与第一堰图案104a的侧表面的端部之间的距离可大于通过将自发光器件ED的厚度与公共电极CE的厚度求和而获得的厚度。

第一堰图案104a的侧表面相对于第二堰图案104b可具有底切结构。例如,堰部104可包括设置在第一堰图案104a和第二堰图案104b之间的边界部或者第一堰图案104a的上侧表面处的底切区。在第二堰图案104b和第一堰图案104a的侧表面之间的底切区可以是用于隔离(或断开或分离)位于堰部104上的发光器件层EDL的至少一部分的结构。例如,在第一堰图案104a和第二堰图案104b之间的底切区可通过对钝化层PAS执行的过蚀刻工艺来形成或实现。第二堰图案104b可基于第一堰图案104a的底切结构突出到第一堰图案104a的侧表面的外侧,由此可覆盖第一堰图案104a的侧表面。因此,第二堰图案104b相对于第一堰图案104a可具有屋檐结构。

金属线104m可设置在第二堰图案104b上。金属线104m可以与像素电极PE相同的材料或相同的结构堆叠在第二堰图案104b上。金属线104m可通过像素电极PE的被原样保留在第二堰图案104b上、而不被像素电极PE的图案化工艺图案化(或去除)的部分(或非图案化区域)来形成或实现。

第三堰图案104c可设置在第二堰图案104b上以围绕金属线104m。第三堰图案104c的侧表面可实现为倾斜结构或正锥形结构。例如,沿着宽度方向截取的第三堰图案104c的剖面可具有与第二堰图案104b相同的梯形剖面结构。

第三堰图案104c可包含有机材料或无机材料。例如,第三堰图案104c可利用与堤部103相同的材料堆叠在第二堰图案104b上。第三堰图案104c可通过堤部103的被原样保留在第二堰图案104b上、而不被堤部103的图案化工艺图案化(或去除)的部分(或非图案化区域)来形成或实现。

根据实施方式,基于在第一堰图案104a和第二堰图案106b之间的底切区(或屋檐结构),设置在第一至第三堰104-1,104-2,104-3的每一个上的自发光器件ED的材料层可在执行沉积工艺时自动隔离(或断开或分离)。例如,由于自发光器件ED的沉积材料具有线性,所以自发光器件ED的材料层不会沉积在被第二堰图案104b覆盖的第一堰图案104a的侧表面上,并且可沉积在第一至第三堰104-1,104-2,104-3和电路层101的每一个的顶表面和侧表面上,因此可在第一至第三堰104-1,104-2,104-3的每一个的第一堰图案104a和第二堰图案106b之间的底切区中隔离(或断开或分离)。因此,自发光器件ED可在执行沉积工艺时在第一至第三堰104-1,104-2,104-3的每一个处自动隔离(或断开或分离),由此可省略用于隔离(或断开或分离)自发光器件ED的分离图案化工艺。因此,设置在基板100上的自发光器件ED可在第一至第三堰104-1,104-2,104-3的每一个处隔离(或断开或分离),由此可通过第一至第三堰104-1,104-2,104-3的每一个阻挡基板100的侧向水分渗透路径。

此外,在执行基于沉积法的沉积工艺时,如同自发光器件ED那样,设置在自发光器件ED上的公共电极CE可通过第一至第三堰104-1,104-2,104-3的每一个的底切区自动隔离(或分离),或者可在不被第一至第三堰104-1,104-2,104-3的每一个的底切区隔离的条件下,被形成为围绕第一至第三堰104-1,104-2,104-3的每一个以及由第一至第三堰104-1,104-2,104-3的每一个隔离的岛状自发光器件EDi的全部。

参照图8、9和11,第一堰104-1的金属线104m可与多个开关电路部170的每一个的第一开关电路171的栅极Sg和第一焊盘连接线176的每一个交叠或交叉。第一堰104-1的金属线104m可经由形成在第一焊盘连接线176和第一堰104-1之间的交叠区中的通孔176h电连接至(或接触)第一焊盘连接线176。第一堰104-1的金属线104m可经由形成在第一开关电路171的栅极Sg和第一堰104-1之间的交叠区中的第一控制线接触孔CLh1电连接至(或接触)第一开关电路171的栅极Sg。因此,内置在第一堰104-1中的金属线104m可设置为闭环线形状(其连续地设置在基板100的外围部处),由此可向每个开关电路部170的第一开关电路171的栅极Sg提供经由第一前感测控制焊盘112a和第一焊盘连接线176提供的第一开关控制信号。例如,内置在第一堰104-1中的金属线104m可用作第一开关控制线。

第二堰104-2的金属线104m可与多个开关电路部170的每一个的第二开关电路172的栅极Sg和第二焊盘连接线177的每一个交叠或交叉。第二堰104-2的金属线104m可经由形成在第二焊盘连接线177和第二堰104-2之间的交叠区中的通孔177h电连接至(或接触)第二焊盘连接线177。第二堰104-2的金属线104m可经由形成在第二开关电路172的栅极Sg和第二堰104-2之间的交叠区中的第二控制线接触孔CLh2电连接至(或接触)第二开关电路172的栅极Sg。因此,内置在第二堰104-2中的金属线104m可设置为闭环线形状(其连续地设置在基板100的外围部处),由此可向每个开关电路部170的第二开关电路172的栅极Sg提供经由第二前感测控制焊盘112b和第二焊盘连接线177提供的第二开关控制信号。例如,内置在第二堰104-2中的金属线104m可用作第二开关控制线。

第三堰104-3的金属线104m可与多个开关电路部170的每一个的第三开关电路173的栅极Sg和第三焊盘连接线178的每一个交叠或交叉。第三堰104-3的金属线104m可经由形成在第三焊盘连接线178和第三堰104-3之间的交叠区中的通孔178h电连接至(或接触)第三焊盘连接线178。第三堰104-3的金属线104m可经由形成在第三开关电路173的栅极Sg和第三堰104-3之间的交叠区中的第三控制线接触孔CLh3电连接至(或接触)第三开关电路173的栅极Sg。因此,内置在第三堰104-3中的金属线104m可设置为闭环线形状(其连续地设置在基板100的外围部处),由此可向每个开关电路部170的第三开关电路173的栅极Sg提供经由第三前感测控制焊盘112c和第三焊盘连接线178提供的第三开关控制信号。例如,内置在第三堰104-3中的金属线104m可用作第三开关控制线。

此外,内置在第一至第三堰104-1,104-2,104-3的每一个中的金属线104m可在发光显示设备的测试模式中用作开关控制线,用于向多个开关电路部170提供从驱动电路部500提供的开关控制信号,并且,可在发光显示设备的正常驱动模式或图像显示模式中用作抗静电线或静电阻挡线。例如,在发光显示设备的正常驱动模式和图像显示模式中,驱动电路部500可向内置在第一至第三堰104-1,104-2,104-3的每一个中的金属线104m提供抗静电电源。例如,抗静电电源可以是接地电压或像素公共电压。因此,内置在第一至第三堰104-1,104-2,104-3的每一个中的金属线104m可阻挡静电从外部流入到显示部AA中,以防止由于静电导致的缺陷。

此外,在内置在第一至第三堰104-1,104-2,104-3的每一个中的金属线104m与第一至第三焊盘连接线176、177和178之间的交叠区中,由于在金属线104m与第一至第三焊盘连接线176、177和178之间的距离(或高度),可难以形成用于暴露第一至第三焊盘连接线176、177和178的通孔176h、177h和178h。因此,中间金属层可附加地设置在金属线104m与第一至第三焊盘连接线176、177和178之间。中间金属层可与驱动TFT Tdr的第一电极SD1一起实现在层间绝缘层ILD上。例如,中间金属层可经由被形成为穿过层间绝缘层ILD和缓冲层101a的中间通孔而电连接至(或接触)第一至第三焊盘连接线176、177和178。此外,金属线104m的一部分可经由穿过第二堰图案104b且暴露中间金属层的通孔176h、177h和178h电连接至(或接触)中间金属层。因此,金属线104m可经由中间金属层电连接至(接触)第一至第三焊盘连接线176、177和178。

根据本发明实施方式的分离部105可实现在堰部104附近(或周围),以隔离(或断开或分离)设置在堰部104附近(或周围)的自发光器件ED。分离部105可被实现为防止水分(或湿气)在基板100的侧向方向上渗透,以防止自发光器件ED由于水分(或湿气)的侧向渗透而劣化。分离部105可在堰部104附近(或周围)隔离(或断开或分离)发光器件层EDL的自发光器件ED至少一次,由此防止水分(或湿气)的侧向渗透。例如,分离部105可以是自发光器件ED的分离区、分离线、隔离区、隔离线、断开区或断开线。

分离部105可实现在堰部104附近(或周围)的电路层101的缓冲层101a或层间绝缘层ILD上。分离部105可包括设置在堰部104附近(或周围)的多个分离结构105-1和105-2。例如,分离部105可包括设置在第一堰104-1和第二堰104-2之间的第一分离结构105-1以及设置在第二堰104-2和第三堰104-3之间的第二分离结构105-2。

第一分离结构105-1和第二分离结构105-2可设置在显示部AA的电路层101上,以一维地具有闭环线形状(或连续的线形状或闭环形状)。第一分离结构105-1可被设置为围绕第一堰104-1。第二分离结构105-2可被设置为围绕第二堰104-2。

第一分离结构105-1和第二分离结构105-2的每一个可包括下结构105a和上结构105b。

下结构105a可基于钝化层PAS实现为单层结构,或者可实现为钝化层PAS和层间绝缘层ILD的堆叠结构。下结构105a的侧表面可实现为倾斜结构或锥形结构。例如,下结构105a可称为诸如基础分离结构、下锥形结构或第一锥形结构等之类的术语。下结构105a可与第一堰图案104a一起实现为与第一堰图案104a相同的结构。

上结构105b可设置在下结构105a上。上结构105b可包含有机材料。上结构105b可由与堤部103相同的材料形成,但本发明的实施方式不限于此。上结构105b的侧表面可实现为倾斜结构或锥形结构。相对于宽度方向,上结构105b的一个边缘部和另一边缘部的每一个可突出到下结构105a的侧表面的外侧。例如,上结构105a可称为诸如上锥形结构或第二锥形结构等之类的术语。

下结构105a的侧表面105as可相对于上结构105b具有底切结构。例如,第一分离结构105-1和第二分离结构105-2的每一个可包含设置在下结构105a的上侧表面或者位于下结构105a和上结构105b之间的边界部处的底切区。位于下结构105a和上结构105b之间的底切区可以是用于隔离(或断开或分离)设置在分离部105上的发光器件层EDL的至少一些层的结构。例如,位于下结构105a和上结构105b之间的底切区可通过钝化层PAS的过蚀刻工艺来形成或实现。上结构105b可基于下结构105a的底切结构突出到下结构105a的侧表面的外侧,由此可覆盖下结构105a的侧表面。因此,上结构105b可设置在下结构105a上以相对于下结构105a具有屋檐结构。

第一分离结构105-1和第二分离结构105-2的至少之一可进一步包括设置在下结构105a和上结构105b之间的金属结构105m。

金属结构105m可设置在下结构105a上。金属结构105m可利用与像素电极PE或者堰部104的金属线104m相同的材料或相同的结构堆叠在下结构105a上。金属结构105m可与堰部104的金属线104m一起形成。金属结构105m的侧表面可实现为倾斜结构或正锥形结构。在宽度方向上,金属结构105m的一个边缘部和另一边缘部的每一个可突出到下结构105a的侧表面的外侧。例如,金属结构105m可称为诸如金属图案层或中间结构等之类的术语。

上结构105b可设置在金属结构105m上。上结构105b可堆叠在金属结构105m的上表面上。在图9、11和12中,上结构105b被图示为仅设置在金属结构105m的上表面处,但本发明的实施方式不限于此,上结构105b可堆叠在下结构105a上以围绕或覆盖金属结构105m的侧表面和上表面的全部。在这种情形下,类似于堰部104的金属线104m,金属结构105m可内置在上结构105b内。

下结构105a的侧表面可相对于金属结构105m具有底切结构。例如,第一分离结构105-1和第二分离结构105-2的每一个可包括设置在位于下结构105a和金属结构105m之间的边界部或者下结构105a的上侧表面处的底切区。位于下结构105a和金属结构105m之间的底切区可通过钝化层PAS的过蚀刻工艺形成或实现。金属结构105m可通过下结构105a的底切结构突出到下结构105a的侧表面的外侧,由此可覆盖下结构105a的侧表面。因此,金属结构105m可相对于下结构105a具有屋檐结构。

根据本发明的实施方式,基于在下结构105a与上结构105b(或金属结构105m)之间的底切区(或屋檐结构),设置在分离部105上的自发光器件ED的材料层可在执行沉积工艺时被自动隔离(或断开或分离)。例如,由于自发光器件ED的沉积材料具有线性,所以自发光器件ED的材料层不会沉积在被上结构105b(或金属结构105m)覆盖的下结构105a的侧表面上,并且可沉积在位于分离部105附近的电路层101和上结构105b的顶表面和侧表面上,由此可在位于下结构105a和上结构105b(或金属结构105m)之间的底切区中被隔离(或断开或分离)。因此,自发光器件ED可在执行沉积工艺时通过分离部105的第一分离结构105-1和第二分离结构105-2被自动隔离(或断开),由此可省略用于隔离(或断开或分离)自发光器件ED的单独图案化工艺。因此,设置在基板100上的自发光器件ED可通过分离部105在堰部104附近(或周围)被附加地隔离(或断开或分离),从而可通过分离部105的第一分离结构105-1和第二分离结构105-2的每一个附加地阻挡基板100的侧向水分渗透路径。

可选地,基于沉积方法,在执行沉积工艺时,类似于自发光器件ED,设置在自发光器件ED上的公共电极CE可通过分离部105的底切区被自动隔离(或分离),并且可在不被分离部105的底切区隔离的条件下,被形成为围绕第一分离结构105-1和第二分离结构105-2的每一个以及由第一分离结构105-1和第二分离结构105-2的每一个隔离的岛状自发光器件EDi的全部。

此外,第一分离结构105-1和第二分离结构105-2的至少之一的金属结构105m可被实现为相对于下结构105a具有屋檐结构,并且防止静电从外部流入到显示部AA。为此,第一分离结构105-1和第二分离结构105-2的每一个的金属结构105m可被实现为电连接至像素公共电压线CVL。例如,如图8和12所示,与像素公共电压线CVL交叠的金属结构105m的一部分可经由被形成为穿过下结构105a和缓冲层101a的通孔105h电连接至(或接触)像素公共电压线CVL。因此,第一分离结构105-1和第二分离结构105-2的每一个的金属结构105m可设置为闭环线形状,其连续地设置在基板100的外围部处,从而可防止静电从外部流入到显示部AA,以防止由静电导致的缺陷。例如,第一分离结构105-1和第二分离结构105-2的至少之一的金属结构105m可释放从外部流入到像素公共电压线CVL的静电,以防止由静电导致的缺陷。

参照图9、11和12,根据本发明实施方式的发光显示设备10或基板100可进一步包括凹槽线GRV。

凹槽线GRV可实现在堰部104和平坦化层102之间。凹槽线GRV可与堰部104一起形成或实现。

凹槽线GRV可通过在堰部104的内部区去除钝化层PAS和平坦化层102的全部或者完全穿过在堰部104的内部区的钝化层PAS和平坦化层102而延伸来实现。例如,凹槽线GRV可以是其中包括位于堰部104和堤部103之间的缓冲层101a上的层间绝缘层ILD、钝化层PAS、平坦化层102、像素电极材料层和堤部103的至少之一的单结构或多层结构等被去除的区域。例如,凹槽线GRV可通过将设置在基板100或最外像素Po的第一裕度区MA1中的堤部103、平坦化层102、钝化层PAS和层间绝缘层ILD的每一个图案化(或去除)来形成或实现。因此,凹槽线GRV可限定或接触平坦化层102的侧表面102s,并且可实现为围绕平坦化层102的侧表面102s的闭环线形状(或连续的线形状或闭环形状)。

凹槽线GRV可限定或接触共同设置在内部像素Pi和最外像素Po中的平坦化层102的侧表面102s、钝化层PAS的侧表面PASs、以及层间绝缘层ILD的侧表面ILDs。例如,凹槽线GRV可限定或接触共同设置在内部像素Pi和最外像素Po中的平坦化层102的侧端102e、钝化层PAS的侧表面PASs、以及层间绝缘层ILD的侧表面ILDs。例如,平坦化层102的侧表面102s、钝化层PAS的侧表面PASs、以及层间绝缘层ILD的侧表面ILDs的每一个可在凹槽线GRV处暴露,由此可实现凹槽线GRV的一个侧壁。

平坦化层102的侧端102e可从钝化层PAS的侧表面PASs朝向凹槽线GRV的中心部(或堰部104)突出。例如,在平坦化层102的侧端102e与基板100的外表面OS之间的距离可小于在钝化层PAS的侧表面PASs与基板100的外表面OS之间的距离。例如,在平坦化层102的侧端102e与钝化层PAS的侧表面PASs之间的距离或者在钝化层PAS的侧表面PASs与平坦化层102的侧端102e之间的距离可大于通过将自发光器件ED的厚度与公共电极CE的厚度求和而得到的厚度。因此,包括平坦化层102的侧表面102s和侧端102e的平坦化层102的外围部(或边缘部)可覆盖钝化层PAS的侧表面PASs并且可直接面对缓冲层101a的上表面。因此,平坦化层102的外围部可相对于钝化层PAS的侧表面PASs具有屋檐结构。

钝化层PAS的侧表面PASs可实现为倾斜结构或正锥形结构。由此,钝化层PAS的侧表面PASs可相对于平坦化层102的外围部具有底切结构。例如,在位于凹槽线GRV的一侧处的钝化层PAS与平坦化层102之间的边界部或者钝化层的上侧表面可相对于平坦化层102具有底切结构。例如,由于凹槽线GRV,在与凹槽线GRV相邻的钝化层PAS的侧表面PASs和与凹槽线GRV相邻的平坦化层102的侧表面102s之间可实现底切区,并且底切区可以是用于隔离(或断开或分离)设置在凹槽线GRV上的发光器件层EDL的至少一些层和平坦化层102的边缘部的结构。位于凹槽线GRV和平坦化层102的侧表面上的自发光器件ED的多个部分可在底切区中被隔离。例如,在钝化层PAS的侧表面PASs与平坦化层102的侧表面102s之间的底切区可通过对钝化层PAS执行的过蚀刻工艺来形成或实现。平坦化层102的侧表面102s可通过钝化层PAS的侧表面PASs的底切结构突出到钝化层PAS的侧表面PASs的外侧,由此可覆盖钝化层PAS的侧表面PASs。因此,平坦化层102的侧表面102s可相对于钝化层PAS的侧表面PASs具有屋檐结构。

根据本发明的实施方式,在执行沉积工艺时,设置在凹槽线GRV和平坦化层102的外围部上的自发光器件ED的材料层可通过在钝化层PAS的侧表面PASs与平坦化层102的侧表面102s之间的底切区(或屋檐结构)被自动隔离(或断开或分离)。例如,由于自发光器件ED的沉积材料具有线性,所以自发光器件ED的沉积材料不会沉积在由平坦化层102的侧表面102s覆盖的钝化层PAS的侧表面PASs上,并且可沉积在平坦化层102的侧表面102s以及凹槽线GRV处的缓冲层101a上,由此可在位于平坦化层102的侧表面102s与钝化层PAS的侧表面PASs之间的底切区处被附加地隔离(或断开或分离)。

此外,在基于沉积的沉积工艺中,类似于自发光器件ED,设置在自发光器件ED上的公共电极CE可通过位于平坦化层102的侧表面102s与钝化层PAS的侧表面PASs之间的底切区被自动隔离(或断开或分离),或者可在不被位于平坦化层102的侧表面102s与钝化层PAS的侧表面PASs之间的底切区隔离的条件下,被形成为覆盖平坦化层102的侧表面102s、钝化层PAS的侧表面PASs以及凹槽线GRV处的缓冲层101a的全部。

如上所述,根据本发明的实施方式,基板100的焊盘部110可设置(或包括)在最外像素Po中,并且电连接至110的布线部400可形成在基板100的侧表面上,从而可实现具有不包括边框区或者包括零边框的空气边框结构的发光显示设备。根据本发明的实施方式,通过控制多个开关电路部170(其被设置为经由内置在堰部104中的金属线104m与堰部104交叠)的每一个的开关操作,可容易地检测在布线之间的电短路,并且可感测布线的线电阻,由此可补偿布线的电阻偏差,从而防止或最小化由于布线的电阻偏差导致的图像质量缺陷。此外,根据本发明的实施方式,自发光器件ED可通过堰部104的底切结构被隔离,由此可防止由于水分(或湿气)的侧向渗透导致的自发光器件ED的可靠性降低。此外,根据本发明的实施方式,自发光器件ED可通过利用凹槽线GRV在平坦化层102的侧表面102s与钝化层PAS的侧表面PASs之间实现的底切区以及在位于堰部104附近(或周围)的分离结构105-1和105-2中的底切区被附加地隔离至少两次或更多次,由此可更好地防止由于水分(或湿气)的侧向渗透导致的自发光器件ED的可靠性降低。此外,根据本发明的实施方式,可提供位于分离结构105-1和105-2中的金属结构和/或内置在堰部104中的金属线104m,由此可保护最外像素中设置的像素电路免受静电的影响。

图13是图解根据本发明另一实施方式的第一焊盘部110、第二焊盘部210和布线部400的图。

参照图13,根据本发明另一实施方式的第一焊盘部110可包括:第一焊盘组PG1;第二焊盘组PG2;以及多个第一至第三前感测控制焊盘112a、112b和112c。

第一焊盘部110的第一焊盘组PG1和第二焊盘组PG2可沿着第一方向X交替布置。第一焊盘部110的第一焊盘组PG1和第二焊盘组PG2可如同上面参照图4描述的那样,因此省略其重复描述。

多个第一至第三前感测控制焊盘112a、112b和112c的每一个可设置在至少两个焊盘组PG1和PG2之间。例如,多个第一至第三前感测控制焊盘112a、112b和112c的每一个可逐个地设置在第一焊盘组PG1和第二焊盘组PG2之间。

第二焊盘部210可包括:第一焊盘组PG1;第二焊盘组PG2;以及多个第一至第三后感测控制焊盘212a、212b和212c。

第二焊盘部210的第一焊盘组PG1和第二焊盘组PG2可沿着第一方向X交替布置。

第二焊盘部210的第一焊盘组PG1可包括以一一对应的关系与位于第一焊盘部110的第一焊盘组PG1中的第一像素驱动电源焊盘PPP1、第一数据焊盘DP1、第一基准电压焊盘RVP1、第一数据焊盘DP1和第一像素公共电压焊盘CVP1交叠的第二像素驱动电源焊盘PPP2、第二数据焊盘DP2、第二基准电压焊盘RVP2、第二数据焊盘DP2和第二像素公共电压焊盘CVP2。

第二焊盘部210的第二焊盘组PG2可包括以一一对应的关系与位于第一焊盘部110的第二焊盘组PG2中的第一栅极焊盘、第一数据焊盘DP1、第一基准电压焊盘RVP1、第一数据焊盘DP1和第一像素驱动电源焊盘PPP1交叠的第二栅极焊盘、第二数据焊盘DP2、第二基准电压焊盘RVP2、第二数据焊盘DP2和第二像素驱动电源焊盘PPP2。

多个第一至第三后感测控制焊盘212a、212b和212c的每一个可设置在至少两个焊盘组PG1和PG2之间。例如,多个第一至第三后感测控制焊盘212a、212b和212c的每一个可逐个地设置在第一焊盘组PG1和第二焊盘组PG2之间。

多个第一后感测控制焊盘212a可共同或并行地连接至连线部250的第一感测控制连线252a。多个第二后感测控制焊盘212b可共同或并行地连接至连线部250的第二感测控制连线252b。多个第三后感测控制焊盘212c可共同或并行地连接至连线部250的第三感测控制连线252c。

布线部400可包括多条布线410以及多条第一至第三感测控制布线412a至412c。

多条布线410的每一条可被形成为以一一对应的关系连接至位于第一焊盘部110的第一焊盘组PG1和第二焊盘组PG2中的焊盘PPP1、DP1、RVP1和CVP1以及位于第二焊盘部210的第一焊盘组PG1和第二焊盘组PG2中的焊盘PPP2、DP2、RVP2和CVP2。

多条第一感测控制布线412a可被形成为以一一对应的关系连接至多个第一前感测控制焊盘112a和多个第一后感测控制焊盘212a。多条第二感测控制布线412b可被形成为以一一对应的关系连接至多个第二前感测控制焊盘112b和多个第二后感测控制焊盘212b。多条第三感测控制布线412c可被形成为以一一对应的关系连接至多个第三前感测控制焊盘112c和多个第三后感测控制焊盘212c。

如上所述,根据本发明的另一实施方式,第一至第三感测控制布线412a至412c的每一条可设置为多条以具有并联连接结构,由此即使在彼此并联连接的多条感测控制布线中的一些中出现线缺陷,可也经由其他线提供开关控制信号。

图14是图解根据本发明另一实施方式的发光显示设备的平面图,图15是图解根据本发明另一实施方式的发光显示设备的后视图。图14和15示出了图1至13所示的发光显示设备中附加设置的辅助焊盘部的实施方式。因此,在下文描述中,通过类似的参考标记指代除了辅助焊盘部和相关元件之外的其他元件,并且省略其重复描述。

参照图14和15,根据本发明另一实施方式的发光显示设备10可进一步包括前辅助焊盘部1110、后辅助焊盘部1210以及辅助连线部1250。

前辅助焊盘部(或第四焊盘部或第二前焊盘部)1110可设置在基板100的与第一外围部平行的第二外围部(或另一外围部)处。前辅助焊盘部1110可包括至少一个前辅助焊盘(或至少一个第四焊盘或至少一个第二前焊盘)1112a、1112b和1112c。例如,前辅助焊盘部1110可包括沿着第一方向X彼此分隔的多个第一至第三前辅助焊盘1112a、1112b和1112c。

多个第一至第三前辅助焊盘1112a、1112b和1112c的每一个可被配置为电连接至位于基板100的第二外围部处的堰部104的金属线104m。除了多个第一至第三前辅助焊盘1112a、1112b和1112c的每一个设置在基板100的第二外围部处之外,多个第一至第三前辅助焊盘1112a、1112b和1112c的每一个可基本等同于位于第一焊盘部110的多个第一至第三前感测控制焊盘112a、112b和112c的每一个,因此省略其重复描述。

后辅助焊盘部(或第五焊盘部或第二后焊盘部)1210可设置在线基板200的后表面处以与前辅助焊盘部1110交叠。后辅助焊盘部1210可包括与位于前辅助焊盘部1110处的至少一个前辅助焊盘1112a、1112b和1112c交叠的至少一个后辅助焊盘(或至少一个第五焊盘或至少一个第二后焊盘)1212a、1212b和1212c。例如,后辅助焊盘部1210可包括设置在线基板200的后表面处的多个第一至第三后辅助焊盘1212a、1212b和1212c,从而以一一对应的关系与设置在前辅助焊盘部1110处的第一至第三前辅助焊盘1112a、1112b和1112c交叠。除了多个第一至第三后辅助焊盘1212a、1212b和1212c的每一个设置在线基板200的第二外围部处之外,多个第一至第三后辅助焊盘1212a、1212b和1212c的每一个可基本等同于设置在第二焊盘部210处的多个第一至第三后感测控制焊盘212a、212b和212c的每一个,因此省略其重复描述。

辅助连线部1250可设置在后辅助焊盘部1210和至少一个第三焊盘部230之间。辅助连线部1250可包括电连接至至少一个后辅助焊盘1212a、1212b和1212c的至少一条辅助连线1252a、1252b和1252c。例如,辅助连线部1250可包括第一至第三辅助连线1252a、1252b和1252c。

第一辅助连线1252a可共同或并行地连接至多个第一后辅助焊盘1212a,并且可连接至设置在至少一个第三焊盘部230处的第一开关控制信号焊盘。

第二辅助连线1252b可共同或并行地连接至多个第二后辅助焊盘1212b,并且可连接至设置在至少一个第三焊盘部230处的第二开关控制信号焊盘。

第三辅助连线1252c可共同或并行地连接至多个第三后辅助焊盘1212c,并且可连接至设置在至少一个第三焊盘部230处的第三开关控制信号焊盘。

根据本发明另一实施方式的发光显示设备10可进一步包括辅助布线部。

辅助布线部可包括被设置为围绕线基板200的第二外表面OS2的多条辅助布线。

多条辅助布线的每一条可单独地(或以一一对应的关系)连接(或接合)至多个第一至第三前辅助焊盘1112a、1112b和1112c的每一个以及多个第一至第三后辅助焊盘1212a、1212b和1212c的每一个。换句话说,多条辅助布线的每一条可电连接至前辅助焊盘部1110的多个第一至第三前辅助焊盘1112a、1112b和1112c的相应一个以及后辅助焊盘部1210的多个第一至第三后辅助焊盘1212a、1212b和1212c的相应一个。除了多条辅助布线的每一条被设置为围绕基板100以及线基板200的第二外表面OS2之外,多条辅助布线的每一条可基本等同于上面参照图13描述的多条感测控制布线412a、412b和412c,因此省略其重复描述。

如上所述,根据本发明的另一实施方式,经由辅助连线部1250、后辅助焊盘部1210、辅助布线部和前辅助焊盘部1110,可将开关控制信号附加地提供给设置在堰部104中的金属线104m。

可选地,在根据本发明另一实施方式的发光显示设备中,设置在堰部104中的金属线104m可在不断开的条件下具有在基板100上一维地接续的闭环线形状,由此可在不具有前感测控制焊盘112a、112b和112c的条件下经由前辅助焊盘部1110将开关控制信号提供给设置在堰部104中的金属线104m。因此,当根据本发明另一实施方式的发光显示设备包括辅助连线部1250、后辅助焊盘部1210、辅助布线部和前辅助焊盘部1110时,可省略前感测控制焊盘112a、112b和112c;后感测控制焊盘212a、212b和212c;感测控制布线412a、412b和412c;以及第二控制连线252a、252b和252c的每一个。在这种情形下,第一焊盘部110的焊盘数量可减少,从而可易于设计具有高分辨率的像素。

图16是示意性图解根据本发明实施方式的开关电路部、驱动IC和时序控制器的图,并且是示出经由开关电路部感测布线的线电阻或布线的短路的图。

参照图16,根据本发明实施方式的驱动IC 530可包括数据驱动器531、感测单元533以及线选择器535。感测单元533可以是感测电路,并且可称为感测电路533。

数据驱动器531可接收从时序控制器570提供的数据控制信号和子像素数据,基于数据控制信号将子像素数据转换成模拟数据信号,并且输出模拟数据信号。例如,在测试模式中,数据驱动器531可将来自时序控制器570的测试数据转换成模拟测试数据并且可输出模拟测试数据。

根据本发明实施方式的数据驱动器531可包括数据信号发生器531a以及多个信号输出电路531o和531e。

数据信号发生器531a可被配置为将从时序控制器570提供的像素数据或测试数据转换成模拟数据信号,并输出模拟数据信号。

多个信号输出电路531o和531e的每一个可经由数据连线、第二焊盘部的第二数据焊盘DP2、数据布线、以及第一焊盘部的第一数据焊盘DP1连接至数据线DLo和DLe。多个信号输出电路531o和531e的每一个可缓存从数据信号发生器531a输出的数据信号,并且可向相应数据线DLo和DLe输出缓存的数据信号。例如,多个信号输出电路531o和531e的每一个可以是输出缓存器,并且可被实现为差分放大器等。例如,多个信号输出电路531o和531e的每一个可以是电压跟随器(voltage follower),其中输出电压被反馈给输入端子。多个信号输出电路531o和531e的每一个的静电流可基于提供给偏置端子的电流选项值(或放大器电流选项值或偏置电压电平)而改变(或变化)。例如,多个信号输出电路531o和531e的每一个的静电流可基于提供给偏置端子的偏置电压电平而增大或减小。

感测单元533可经由数据连线、第二焊盘部的第二基准电压焊盘RVP2、基准布线、以及第一焊盘部的第一基准电压焊盘RVP1选择性地连接至基准电压线RL。感测单元533可被配置为将与经由基准电压线RL输入的电流(或测试信号)对应的感测值转换成感测数据,并且将感测数据提供给时序控制器570。例如,感测单元533可将与经由基准电压线RL输入的电流(或测试信号)对应的感测电压进行数模转换,以产生感测数据,并且可将产生的感测数据提供给时序控制器570。

感测单元533可被设置为具有与设置在基板100处的基准电压线的数量相同的数量。根据本发明实施方式的感测单元533可包括多个感测电路和多个模数转换器。

多个感测电路的每一个可配置有包括运算放大器和电容器的积分器。例如,感测电路的运算放大器可包括选择性地连接至基准电压线RL的反相输入端子(-)、被提供基准电压的非反相输入端子(+)、以及连接至模数转换器的输出端子。电容器可以是连接在运算放大器的反相输入端子(-)和输出端子之间的反馈电容器。此外,多个感测电路的每一个可进一步包括连接在运算放大器的反相输入端子(-)和输出端子之间的反馈开关(或复位开关)。流入反馈电容器的电流可与流入基准电压线RL的电流相同。

多个模数转换器的每一个可对多个感测电路的相应感测电路的输出电压(或感测电压)进行模数转换,以产生感测数据,并且可将产生的感测数据提供给时序控制器570。例如,多个模数转换器的每一个可基于流入相应感测电路的反馈电容器中的电流对相应感测电路的输出电压(或感测电压)进行模数转换,以产生感测数据。

线选择器535可被配置为基于从时序控制器570提供的线选择信号,将连接至偶数数据线DLe的数据连线连接至感测单元533或信号输出电路531o和531e。例如,线选择器535可以是多路复用器。

时序控制器570在测试模式中可产生第一至第三开关控制信号,用于控制第一至第三开关电路171、172和173的每一个的开关操作,并且时序控制器570可产生测试数据和线选择信号,并将产生的测试数据和线选择信号提供给数据驱动器531。时序控制器570可基于从感测单元533提供的感测数据向驱动IC 530提供测试数据并且设定偏置电压电平,其中偏置电压电平被输入给多个信号输出电路531o和531e的每一个的偏置端子。时序控制器570可基于感测数据产生多条布线中的与数据线连接的数据布线的线电阻值,并且基于产生的线电阻值来设定偏置电压电平。在测试模式中,时序控制器570可根据从驱动IC 530的感测单元533提供的基于线的线感测数据来确定布线是否存在短路以及短路缺陷位置,并且可通过使用单独的监视器来显示确定结果。此外,在测试模式中,时序控制器570可根据从驱动IC530的感测单元533提供的基于线的线感测数据来产生用于补偿多条数据布线之间的电阻偏差的基于线的电阻补偿值,产生与基于线的电阻补偿值对应的偏置电压,并且将偏置电压提供给驱动IC 530的相应信号输出电路531o和531e的偏置端子。因此,信号输出电路531o和531e可基于偏置电压电平输出利用电阻补偿值进行了补偿的数据信号。

根据本发明的实施方式,流入布线的电流可与流入感测电路的反馈电容器中的电流相同,因此如下面的等式1所示,时序控制器570可基于对应于电阻感测数据的感测电压、流入布线的电流Current1和流入感测电路的反馈电容器(电容为Cf)的电流Current2来计算线电阻R。

【等式1】

Current 1=(Vdata-Vinv)/R

Current 2=Cf(Vinv-Vsen)/ΔTsen

Current 1=Current 2,(Vdata-Vinv)/R=Cf(Vinv-Vsen)/ΔTsen

R=(ΔTsen×(Vdata-Vinv))/Cf(Vinv-Vsen)

在等式1中,Vdata可表示测试信号的电压电平,Cf可表示反馈电容器的电容,Vinv可表示运算放大器的反相端子(-)的电压电平,Vsen可表示对应于电阻感测数据的感测电压(或感测电路的输出电压),ΔTsen可表示电流流动的时间。当感测电路的反馈开关导通时,Vinv可具有与施加给非反相端子(+)的基准电压相同的电压电平。例如,当感测电路的反馈开关导通并由此使运算放大器的增益值无穷时,Vinv可具有与非反相端子(+)的电压电平相同的电压电平。在等式1中,测试信号的电压电平Vdata、反馈电容器的电容Cf、电流流动的时间ΔTsen以及运算放大器的反相端子的电压电平Vinv可分别为恒定值。因此,时序控制器570可计算对应于电阻感测数据的感测电压Vsen,并且可经由等式1计算布线的线电阻R。例如,在感测电路的反馈开关导通并且电流流入反馈电容器时,时序控制器570可基于等式1计算布线的线电阻R。

可选地,时序控制器570可不产生对应于基于线的电阻补偿值的偏置电压,并且可将基于线的电阻补偿值提供给驱动IC 530。在这种情形下,驱动IC 530可进一步包括偏置电压发生器537。偏置电压发生器537可产生与从时序控制器570提供的每个基于线的电阻补偿值对应的基于线的偏置电压,并且可将产生的基于线的偏置电压提供给相应信号输出电路531o和531e的偏置端子。

此外,根据本发明实施方式的驱动IC 530或驱动电路部500可进一步包括电压选择器539。

电压选择器539可基于时序控制器570的电压选择信号来选择并输出从时序控制器570提供的开关控制信号和接地电压的其中之一。

在测试模式中,电压选择器539可基于从时序控制器570提供的具有第一电压电平的电压选择信号来输出从时序控制器570提供的第一至第三开关控制信号的每一个,由此开关电路部170的第一至第三开关电路171、172和173的每一个可基于从电压选择器539经由第一至第三前感测控制焊盘112a、112b和112c的每一个提供的相应开关控制信号而导通。

电压选择器539在非测试模式或正常驱动模式中,可基于从时序控制器570提供的具有第二电压电平的电压选择信号来输出从时序控制器570提供的接地电压GND,由此,开关电路部170的第一至第三开关电路171、172和173的每一个可通过从电压选择器539经由堰部104的金属线104m和第一至第三前感测控制焊盘112a、112b和112c的每一个提供的接地电压GND保持在截止状态,并且堰部104的金属线104m可保持接地电压GND并且可用作抗静电线或静电阻挡线。

在根据本发明实施方式的发光显示设备中,下文将描述用于测试布线的短路的驱动方法。

首先,具有第一逻辑电平(或第一电压电平或栅极截止电压电平)的第一至第三开关控制信号的每一个可从时序控制器570输出,由此开关电路部170的第一至第三开关电路171、172和173的每一个可截止。

随后,测试数据信号可从驱动IC 530提供给数据线DLo和DLe,由此驱动IC 530的感测单元533可感测经由基准电压线RL和线选择器535输入的电流,以输出线感测数据。

随后,时序控制器570可基于线感测数据确定布线是否出现短路。例如,当在彼此相邻设置的基准电压线RL与数据线DLo和DLe之间出现短路时,流入数据线DLo和DLe的电流可经由短路部分流入基准电压线RL,由此可通过感测流入基准电压线RL的电流来检测在线之间是否出现短路。例如,当线感测数据大于或等于基准阈值电压值时,时序控制器570可确定在布线之间出现短路。应理解,检测的短路可物理地位于显示部、前焊盘部和布线部中的一个或多个中。例如,短路可存在于像素区中的奇数数据线DLo和基准线RL之间、在第一数据焊盘DP1和第一基准电压焊盘RVP1之间、和/或在连接至第一数据焊盘DP1的布线410和连接至第一基准电压焊盘RVP1的布线之间。

因此,根据本发明的实施方式,每个开关电路部170的第一至第三开关电路171、172和173可截止,并且可在将测试信号提供给多条数据线DLo和DLe的每一条的同时感测流入每条基准电压线RL的电流,由此可检测在多条布线之间的短路缺陷。

在根据本发明实施方式的发光显示设备中,下文将描述用于感测布线的线电阻的驱动方法。

首先,在测试模式的第一测试时段中,可感测在奇数数据布线和基准布线之间的线电阻值。根据本发明的实施方式,可从驱动IC 530输出具有第二逻辑电平(或第二电压电平或栅极导通电压电平)的第一开关控制信号以及具有第一逻辑电平的第二和第三开关控制信号,由此开关电路部170的第一开关电路171可导通,并且开关电路部170的第二开关电路172和第三开关电路173的每一个可截止。随后,测试数据信号可从驱动IC 530提供给奇数数据线DLo,由此驱动IC 530的感测单元533可感测经由线选择器535以及包括奇数数据线DLo、第一开关电路171和基准电压线RL的第一电流路径CP1输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生奇数数据布线和基准布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,在测试模式的第二测试时段中,可感测在偶数数据布线和基准布线之间的线电阻值。根据本发明的实施方式,可从驱动IC 530输出具有第二逻辑电平的第二开关控制信号以及具有第一逻辑电平的第一和第三开关控制信号,由此开关电路部170的第二开关电路172可导通,并且开关电路部170的第一开关电路171和第三开关电路173的每一个可截止。随后,测试数据信号可从驱动IC 530提供给偶数数据线DLe,由此驱动IC 530的感测单元533可感测经由线选择器535以及包括偶数数据线DLe、第二开关电路172和基准电压线RL的第二电流路径CP2输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生偶数数据布线和基准布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,在测试模式的第三测试时段中,可感测在奇数数据布线和偶数数据布线之间的线电阻值。根据本发明的实施方式,可从驱动IC 530输出具有第二逻辑电平的第三开关控制信号以及具有第一逻辑电平的第一和第二开关控制信号,由此开关电路部170的第三开关电路173可导通,并且开关电路部170的第一开关电路171和第二开关电路172的每一个可截止。随后,测试数据信号可从驱动IC 530提供给奇数数据线DLo和偶数数据线DLe,由此驱动IC 530的感测单元533可感测经由线选择器535以及包括奇数数据线DLo、第三开关电路173和偶数数据线DLe的第三电流路径CP3输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生奇数数据布线和偶数数据布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,时序控制器570可基于在第一至第三测试时段的每一个中产生的线电阻值,利用下面的等式2产生奇数数据布线的线电阻值R1和偶数数据布线的线电阻值R2,并且可附加地产生基准布线的线电阻值R3。

【等式2】

Rl+R3=Rsum1,R2+R3=Rsum2,R1+R2=Rsum3

Rsum1+Rsum2+Rsum3=Rtot,

2(R1+R2+R3)=Rtot,R1+R2+R3=Rtot/2

R1=(Rtot/2)-Rsum2,R2=(Rtot/2)-Rsum1,R3=(Rtot/2)-Rsum3

在等式2中,R1可表示奇数数据布线的线电阻值,R2可表示偶数数据布线的线电阻值,R3可表示基准布线的线电阻值。此外,Rsum1可表示在第一测试时段中产生的奇数数据布线和基准布线的每一条的线电阻值之和,Rsum2可表示在第二测试时段中产生的偶数数据布线和基准布线的每一条的线电阻之和,Rsum3可表示在第三测试时段中产生的奇数数据布线和偶数数据布线的每一条的线电阻值之和。

随后,时序控制器570可根据基于线的电阻值计算用于补偿基于线的电阻偏差的、基于线的电阻补偿值,并且可按照查找表的形式将基于线的电阻补偿值存储在存储电路中。在本发明的实施方式中,时序控制器570可基于存储在存储电路中的多条数据布线的每一条的电阻补偿值来调制待提供给每条数据线的像素数据,并且可将调制后的像素数据提供给驱动IC 530。在本发明的另一实施方式中,时序控制器570可基于存储在存储电路中的多条数据布线的每一条的电阻补偿值来设定分别对应于多条数据线的多个信号输出电路531o和531e的每一个的电流选项值(或偏置电压电平),将电流选项值存储在存储电路中,并且可将存储在存储电路中的电流选项值提供给相应的信号输出电路531o和531e。因此,多个信号输出电路531o和531e的每一个可基于与从时序控制器570提供的电流选项值对应的偏置电压电平来输出基于偏置电压电平将相应数据布线的电阻值进行了补偿的数据信号,由此可补偿在多条数据布线的线电阻值之间的电阻偏差。

因此,根据本发明的另一实施方式,每个开关电路部170的第一至第三开关电路171、172和173可选择性地导通,并且可在向多条数据线DLo和DLe的每一条提供测试信号的同时感测流入基准电压线RL的电流,从而可检测每条布线的线电阻,并且可补偿在多条数据布线的线电阻值之间的电阻偏差。

图17是图解根据本发明另一实施方式的多个开关电路部的图,图18是沿图17所示的线III-III’截取的剖视图。图17和18示出了通过修改上面参照图1至16描述的发光显示设备中的堰部和多个开关电路部而实现的实施方式。因此,在下文描述中,除了堰部、多个开关电路部和相关元件之外的其他元件是指相似的元件,将省略或简要给出其重复描述。

参照图17和18,根据本发明另一实施方式的堰部104可包括第一堰104-1和第二堰104-2。

第一堰104-1和第二堰104-2的每一个可包括金属线104m。金属线104m可内置或实现在堰部104中(或内部),由此可一维地具有与堰部104相同的闭环线形状(或连续的线形状或闭环形状)。除了堰部104包括第一堰104-1和第二堰104-2之外,堰部104可被配置为具有与上面参照图1至12描述的堰部104基本相同的结构,因此省略其重复描述。

分离部105可包括设置在第一堰104-1和第二堰104-2之间的第一分离结构105-1、以及设置在第二堰104-2的内部区中的第二分离结构105-2和第三分离结构105-3。除了分离部105进一步包括第三分离结构105-3之外,分离部105可被配置为具有与上面参照图1至13描述的分离部105基本相同的结构,因此省略其重复描述。

此外,第一至第三分离结构105-1至105-3的每一个的金属结构可经由通孔105h电连接至(或接触)像素公共电压线CVL。

第一焊盘部110可包括第一和第二前感测控制焊盘112a和112b以及第一和第二焊盘连接线176和177。第一焊盘部110可具有在上面参照图1至13描述的焊盘部110中省略第三前感测控制焊盘112c和第三焊盘连接线的构造,因此省略其重复描述。

根据本发明实施方式的多个开关电路部170的每一个可包括第一和第二开关电路171和172。

第一和第二开关电路171和172可被设置为与第一和第二堰104-1和104-2单独地交叠。例如,第一开关电路171可与第一堰104-1交叠,或者可设置在第一堰104-1的下方。第二开关电路172可与第二堰104-2交叠,或者可设置在第二堰104-2的下方。第一和第二开关电路171和172的每一个可基本等同于上面参照图1至13描述的第一和第二开关电路171和172的每一个,因此省略其重复描述。

此外,上面参照图14和15描述的前辅助焊盘部1110、后辅助焊盘部1210、辅助布线部和辅助连线部1250的每一个可应用于图17和18所示的实施方式。

如上所述,根据本发明的另一实施方式,可获得与上面参照图1至16描述的发光显示设备相同的效果,并且相比上面参照图1至16描述的发光显示设备,由于堰部104占据的面积减小,所以可易于设计具有高分辨率的像素。

图19是示意性图解根据本发明另一实施方式的开关电路部、驱动IC和时序控制器的图,并且是用于描述经由开关电路部来感测布线的线电阻或布线的短路的图。

参照图17至19,根据本发明另一实施方式的驱动IC 530可包括数据驱动器531、感测单元533和线选择器535。除了包括这些元件的驱动IC 530被配置为在测试模式中输出从时序控制器570提供的第一和第二开关控制信号之外,驱动IC 530可基本等同于上面参照图16描述的驱动IC 530,由此省略其重复描述。

时序控制器570可在测试模式中产生用于控制第一开关电路171和第二开关电路172的每一个的开关操作的第一开关控制信号和第二开关控制信号,并且可产生测试数据和线选择信号并将产生的测试数据和线选择信号提供给数据驱动器531。除了时序控制器570控制用于产生第一和第二开关控制信号的开关电路部170的第一和第二开关电路171和172的每一个的开关操作之外,时序控制器570可基本等同于上面参照图16描述的时序控制器570,因此省略其重复描述。

可选地,时序控制器570可不产生与基于线的电阻补偿值对应的偏置电压,并且可将基于线的电阻补偿值提供给驱动IC 530。在这种情形下,驱动IC 530可进一步包括偏置电压发生器537。偏置电压发生器537可产生与从时序控制器570提供的每个基于线的电阻补偿值对应的基于线的偏置电压,并且可将产生的基于线的偏置电压提供给相应信号输出电路531o和531e的偏置端子。

此外,根据本发明另一实施方式的驱动IC 530或驱动电路部500可进一步包括电压选择器539。

电压选择器539可基于时序控制器570的电压选择信号选择并输出从时序控制器570提供的开关控制信号和接地电压的其中之一。

在测试模式中,电压选择器539可基于从时序控制器570提供的具有第一逻辑电平的电压选择信号来输出从时序控制器570提供的第一和第二开关控制信号的每一个,由此开关电路部170的第一和第二开关电路171和172的每一个可基于从电压选择器539经由第一和第二前感测控制焊盘112a和112b的每一个提供的相应开关控制信号而导通。

电压选择器539可在非测试模式或正常驱动模式中,基于从时序控制器570提供的具有第二逻辑电平的电压选择信号来输出从时序控制器570提供的接地电压GND,由此,开关电路部170的第一和第二开关电路171和172的每一个可通过从电压选择器539经由堰部104的金属线104m以及第一和第二前感测控制焊盘112a和112b的每一个提供的接地电压GND保持在截止状态,并且堰部104的金属线104m可保持接地电压GND并且可用作抗静电线或静电阻挡线。

在根据本发明另一实施方式的发光显示设备中,下文将描述用于测试布线的短路的驱动方法。

首先,具有第一逻辑电平的第一和第二开关控制信号的每一个可从时序控制器570输出,由此开关电路部170的第一和第二开关电路171和172的每一个可截止。

随后,测试数据信号可从驱动IC 530提供给数据线DLo和DLe,由此驱动IC 530的感测单元533可感测经由基准电压线RL和线选择器535输入的电流,以输出线感测数据。

随后,时序控制器570可基于线感测数据确定布线是否出现短路。例如,当在彼此相邻设置的基准电压线RL与数据线DLo和DLe之间出现短路时,流入数据线DLo和DLe的电流可经由短路部分流入基准电压线RL,由此感测单元533可通过感测流入基准电压线RL的电流来检测在线之间是否出现短路。例如,当线感测数据大于或等于基准阈值电压值时,时序控制器570可确定在布线之间出现短路。

因此,根据本发明的实施方式,每个开关电路部170的第一和第二开关电路171和172可截止,并且可在将测试信号提供给多条数据线DLo和DLe的每一条的同时感测流入每条基准电压线RL的电流,由此可检测在多条布线之间的短路缺陷。

在根据本发明另一实施方式的发光显示设备中,下文将描述用于感测布线的线电阻的驱动方法。

首先,在测试模式的第一测试时段中,可感测在奇数数据布线和基准布线之间的线电阻值。根据本发明的实施方式,可从驱动IC 530输出具有第二逻辑电平的第一开关控制信号以及具有第一逻辑电平的第二开关控制信号,由此开关电路部170的第一开关电路171可导通,并且开关电路部170的第二开关电路172可截止。随后,测试数据信号可从驱动IC 530提供给奇数数据线DLo,由此驱动IC 530的感测单元533可感测经由线选择器535以及包括奇数数据线DLo、第一开关电路171和基准电压线RL的第一电流路径CP1输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生奇数数据布线和基准布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,在测试模式的第二测试时段中,可感测在偶数数据布线和基准布线之间的线电阻值。根据本发明的实施方式,可从驱动IC 530输出具有第二逻辑电平的第二开关控制信号和具有第一逻辑电平的第一开关控制信号,由此开关电路部170的第二开关电路172可导通,并且开关电路部170的第一开关电路171可截止。随后,测试数据信号可从驱动IC530提供给偶数数据线DLe,由此驱动IC 530的感测单元533可感测经由线选择器535以及包括偶数数据线DLe、第二开关电路172和基准电压线RL的第二电流路径CP2输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生偶数数据布线和基准布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,在测试模式的第三测试时段中,可感测在奇数数据布线和偶数数据布线之间的线电阻值。根据本发明的实施方式,可从驱动IC 530输出具有第二逻辑电平的第一和第二开关控制信号,由此开关电路部170的第一开关电路171和第二开关电路172的每一个可导通。随后,测试数据信号可从驱动IC 530提供给奇数数据线DLo和偶数数据线DLe,由此驱动IC 530的感测单元533可感测经由线选择器535以及包括奇数数据线DLo、第一开关电路171和第二开关电路172、以及偶数数据线DLe的第三电流路径CP3输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生奇数数据布线和偶数数据布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,时序控制器570可基于在第一至第三测试时段的每一个中产生的线电阻值,利用上面的等式1和2产生奇数数据布线的线电阻值和偶数数据布线的线电阻值,并且可附加地产生基准布线的线电阻值。

随后,时序控制器570可根据基于线的电阻值计算用于补偿基于线的电阻偏差的、基于线的电阻补偿值,并且可按照查找表的形式将基于线的电阻补偿值存储在存储电路中。在本发明的实施方式中,时序控制器570可基于存储在存储电路中的多条数据布线的每一条的电阻补偿值来调制待提供给每条数据线的像素数据,并且可将调制后的像素数据提供给驱动IC 530。在本发明的另一实施方式中,时序控制器570可基于存储在存储电路中的多条数据布线的每一条的电阻补偿值来设定分别对应于多条数据线的多个信号输出电路531o和531e的每一个的电流选项值(或偏置电压电平),将电流选项值存储在存储电路中,并且可将存储在存储电路中的电流选项值提供给相应的信号输出电路531o和531e。因此,多个信号输出电路531o和531e的每一个可基于与从时序控制器570提供的电流选项值对应的偏置电压电平来输出将相应数据布线的电阻值进行了补偿的数据信号,由此可补偿在多条数据布线的线电阻值之间的电阻偏差。

因此,根据本发明的另一实施方式,每个开关电路部170的第一和第二开关电路171和172可选择性地导通,并且可在向多条数据线DLo和DLe的每一条提供测试信号的同时感测流入基准电压线RL的电流,从而可检测每条布线的线电阻,并且可补偿在多条数据布线的线电阻值之间的电阻偏差。

图20是图解根据本发明另一实施方式的多个开关电路部的图,图21是沿图20所示的线IV-IV’截取的剖视图,图22是沿图20所示的线V-V’截取的剖视图。图20至22示出了在上面参照图17和18描述的发光显示设备中多个开关电路部被布置为与一个堰部交叠的实施方式。因此,在下文描述中,除了一个堰部、多个开关电路部和相关元件之外的其他元件可指类似元件,将省略或简要给出其重复描述。

参照图20至22,根据本发明另一实施方式的堰部104可被配置为沿着最外像素Po的外围部一维地具有闭环线形状(或连续的线形状或闭环形状)。除了堰部104配置有包括金属线104m的堰(或一个堰)之外,堰部104可被配置为具有与上面参照图1至14描述的堰部104基本相同的结构,因此省略其重复描述。

分离部105可包括设置在堰部(或堰)104的外部区中的至少一个外分离结构(或第一和第二分离结构)105-1和105-2。分离部105可进一步包括设置在堰部(或堰)104的内部区中的至少一个内分离结构(或第三和第四分离结构)105-3和105-4。至少一个外分离结构105-1和105-2可被设置为围绕堰部104。至少一个内分离结构105-3和105-4可被设置为被堰部104围绕。除了分离部105进一步包括至少一个外分离结构105-1和105-2以及至少一个内分离结构105-3和105-4之外,分离部105可被配置为具有与上面参照图1至13描述的分离部105基本相同的结构,因此省略其重复描述。

此外,至少一个外分离结构105-1和105-2以及至少一个内分离结构105-3和105-4的每一个的金属结构可经由通孔105电连接至(或接触)像素公共电压线CVL。

第一焊盘部110可包括第一和第二前感测控制焊盘112a和112b以及第一和第二焊盘连接线176和177。第一焊盘连接线176可经由通孔176h电连接至堰部104的金属线104m,第二焊盘连接线177可经由通孔177h电连接至堰部104的金属线104m。因此,堰部104的金属线104m可共同连接至第一和第二焊盘连接线176和177。此外,第一焊盘部110可配置有仅一个前感测控制焊盘112a和一条焊盘连接线176,但不限于此,其可包括图13所示的多个第一前感测控制焊盘112a。

根据本发明另一实施方式的多个开关电路部170的每一个可包括第一和第二开关电路171和172。除了并联设置的第一和第二开关电路171和172的每一个共同连接至一条金属线104m之外,第一和第二开关电路171和172的每一个可基本等同于上面参照图17和18描述的第一和第二开关电路171和172的每一个,因此省略其重复描述。

此外,上面参照图14和15描述的前辅助焊盘部1110、后辅助焊盘部1210、辅助布线部和辅助连线部1250的每一个可应用于图20至22所示的实施方式。

如上所述,根据本发明的另一实施方式,可获得与上面参照图17和18描述的发光显示设备相同的效果,并且相比上面参照图17和18描述的发光显示设备,由于堰部104占据的面积进一步减小,所以可进一步易于设计具有高分辨率的像素。

图23是示意性图解根据本发明另一实施方式的开关电路部、驱动IC和时序控制器的图,并且是用于描述经由开关电路部来感测布线的线电阻或布线的短路的图。

参照图20至23,根据本发明另一实施方式的驱动IC 530可包括数据驱动器531、感测单元533和线选择器535。除了包括这些元件的驱动IC 530被配置为在测试模式中输出从时序控制器570提供的单个开关控制信号(或一个开关控制信号)之外,驱动IC 530可基本等同于上面参照图16描述的驱动IC 530,由此省略其重复描述。

时序控制器570可在测试模式中产生用于控制第一开关电路171和第二开关电路172的每一个的开关操作的单个开关控制信号,并且可产生测试数据和线选择信号并将产生的测试数据和线选择信号提供给数据驱动器531。除了时序控制器570控制用于产生单个开关控制信号的开关电路部170的第一和第二开关电路171和172的每一个的开关操作之外,时序控制器570可基本等同于上面参照图16描述的时序控制器570,因此省略其重复描述。

可选地,时序控制器570可不产生与基于线的电阻补偿值对应的偏置电压,并且可将基于线的电阻补偿值提供给驱动IC 530。在这种情形下,驱动IC 530可进一步包括偏置电压发生器537。偏置电压发生器537可产生与从时序控制器570提供的每个基于线的电阻补偿值对应的基于线的偏置电压,并且可将产生的基于线的偏置电压提供给相应信号输出电路531o和531e的偏置端子。

此外,根据本发明另一实施方式的驱动IC 530或驱动电路部500可进一步包括电压选择器539。

电压选择器539可基于时序控制器570的电压选择信号选择并输出从时序控制器570提供的开关控制信号和接地电压的其中之一。

在测试模式中,电压选择器539可基于从时序控制器570提供的具有第一逻辑电平的电压选择信号来输出从时序控制器570提供的开关控制信号,由此开关电路部170的第一和第二开关电路171和172的每一个可基于从电压选择器539经由第一和第二前感测控制焊盘112a和112b的每一个提供的开关控制信号而导通。

电压选择器539可在非测试模式或正常驱动模式中,基于从时序控制器570提供的具有第二逻辑电平的电压选择信号来输出从时序控制器570提供的接地电压GND,由此,开关电路部170的第一和第二开关电路171和172的每一个可通过从电压选择器539经由堰部104的金属线104m以及第一和第二前感测控制焊盘112a和112b的每一个提供的接地电压GND保持在截止状态,并且堰部104的金属线104m可保持接地电压GND并且可用作抗静电线或静电阻挡线。

在根据本发明实施方式的发光显示设备中,下文将描述用于测试布线的短路的驱动方法。

首先,具有第一逻辑电平的开关控制信号可从时序控制器570输出,由此开关电路部170的第一和第二开关电路171和172的每一个可截止。

随后,测试数据信号可从驱动IC 530提供给数据线DLo和DLe,由此驱动IC 530的感测单元533可感测经由基准电压线RL和线选择器535输入的电流,以输出线感测数据。

随后,时序控制器570可基于线感测数据确定布线是否出现短路。例如,当在彼此相邻设置的基准电压线RL与数据线DLo和DLe之间出现短路时,流入数据线DLo和DLe的电流可经由短路部分流入基准电压线RL,由此感测单元533可通过感测流入基准电压线RL的电流来检测在线之间是否出现短路。例如,当线感测数据大于或等于基准阈值电压值时,时序控制器570可确定在布线之间出现短路。

因此,根据本发明的实施方式,每个开关电路部170的第一和第二开关电路171和172可截止,并且可在将测试信号提供给多条数据线DLo和DLe的每一条的同时感测流入每条基准电压线RL的电流,由此可检测在多条布线之间的短路缺陷。

在根据本发明另一实施方式的发光显示设备中,下文将描述用于感测布线的线电阻的驱动方法。

首先,在测试模式的第一测试时段中,驱动IC 530的奇数信号输出电路531o被启用,并且偶数信号输出电路531e被禁用,由此可感测在奇数数据布线和基准布线之间的线电阻值。根据本发明的实施方式,可从驱动IC530输出具有第二逻辑电平的开关控制信号,由此开关电路部170的第一开关电路171和第二开关电路172可同时导通。随后,测试数据信号可从驱动IC 530的奇数信号输出电路531o提供给奇数数据线DLo,由此驱动IC 530的感测单元533可感测经由线选择器535以及包括奇数数据线DLo、第一开关电路171和基准电压线RL的第一电流路径CP1输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生奇数数据布线和基准布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,在测试模式的第二测试时段中,驱动IC 530的奇数信号输出电路531o被禁用,并且偶数信号输出电路531e被启用,由此可感测在偶数数据布线和基准布线之间的线电阻值。根据本发明的实施方式,可从驱动IC530输出具有第二逻辑电平的开关控制信号,由此开关电路部170的第一开关电路171和第二开关电路172可同时导通。随后,测试数据信号可从驱动IC 530的偶数信号输出电路531e提供给偶数数据线DLe,由此驱动IC 530的感测单元533可感测经由线选择器535以及包括偶数数据线DLe、第二开关电路172和基准电压线RL的第二电流路径CP2输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生偶数数据布线和基准布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,在测试模式的第三测试时段中,驱动IC 530的奇数信号输出电路531o被启用,并且偶数信号输出电路531e被禁用,由此可感测在奇数数据布线和偶数数据布线之间的线电阻值。根据本发明的实施方式,可从驱动IC 530输出具有第二逻辑电平的开关控制信号,由此开关电路部170的第一开关电路171和第二开关电路172可同时导通。随后,测试数据信号可从驱动IC 530的奇数信号输出电路531o提供给奇数数据线DLo,由此驱动IC530的感测单元533可感测经由线选择器535以及包括奇数数据线DLo、第一开关电路171和第二开关电路172、以及偶数数据线DLe的第三电流路径CP3输入的电流,以产生电阻感测数据。随后,时序控制器570可基于电阻感测数据产生奇数数据布线和偶数数据布线的线电阻值,并且可将产生的线电阻值存储在存储电路中。

随后,时序控制器570可基于在第一至第三测试时段的每一个中产生的线电阻值,利用上面的等式1和2产生奇数数据布线的线电阻值和偶数数据布线的线电阻值,并且可附加地产生基准布线的线电阻值。

随后,时序控制器570可根据基于线的电阻值计算用于补偿基于线的电阻偏差的、基于线的电阻补偿值,并且可按照查找表的形式将基于线的电阻补偿值存储在存储电路中。在本发明的实施方式中,时序控制器570可基于存储在存储电路中的多条数据布线的每一条的电阻补偿值来调制待提供给每条数据线的像素数据,并且可将调制后的像素数据提供给驱动IC 530。在本发明的另一实施方式中,时序控制器570可基于存储在存储电路中的多条数据布线的每一条的电阻补偿值来设定分别对应于多条数据线的多个信号输出电路531o和531e的每一个的电流选项值(或偏置电压电平),将电流选项值存储在存储电路中,并且可将存储在存储电路中的电流选项值提供给相应的信号输出电路531o和531e。因此,多个信号输出电路531o和531e的每一个可基于与从时序控制器570提供的电流选项值对应的偏置电压电平来输出将相应数据布线的电阻值进行了补偿的数据信号,由此可补偿在多条数据布线的线电阻值之间的电阻偏差。

因此,根据本发明的另一实施方式,每个开关电路部170的第一和第二开关电路171和172可同时导通,并且可在向多条数据线DLo和DLe的每一条提供测试信号的同时感测流入基准电压线RL的电流,从而可检测每条布线的线电阻,并且可补偿在多条数据布线的线电阻值之间的电阻偏差。

图24是图解根据本发明实施方式的多屏显示设备的图,图25是沿图24所示的线VI-VI’截取的剖视图。图24和25示出了通过平铺根据图1至23所示的本发明实施方式的发光显示设备而实现的多屏显示设备。

参照图24和25,根据本发明实施方式的多屏显示设备(或多屏发光显示设备或平铺发光显示设备)可包括多个显示设备DA1至DA4。

多个显示设备DA1至DA4的每一个可单独显示图像,或者可分割地显示一个图像。多个显示设备DA1至DA4的每一个可包括根据图1至23所示的本发明实施方式的发光显示设备,因此可省略其重复描述。

多个显示设备DA1至DA4可平铺在单独的平铺框架(tiling frame)上以便在其侧表面中(或以边到边(side-to-side)连接的关系)彼此接触。例如,多个显示设备DA1至DA4可平铺为N×M的形式,由此实现具有大屏幕的多屏显示设备。例如,N是1或更大的正整数,M是2或更大的正整数。例如,N是2或更大的正整数,M是1或更大的正整数。

多个显示设备DA1至DA4的每一个可不包括围绕显示图像的整个显示部AA的边框区(或非显示部),并且可具有显示部AA被空气围绕的空气边框结构。例如,在多个显示设备DA1至DA4的每一个中,基板100的整个第一表面可被实现为显示部AA。

根据实施方式,在多个显示设备DA1至DA4的每一个中,在最外像素Po的中心部CP与第一基板100的最外外表面VL之间的第二间隔D2可被实现为相邻像素之间的第一间隔D1(或像素节距)的一半或更小。因此,在基于侧向接合方法其侧表面沿着第一方向X和第二方向Y彼此连接(或接触)的两个相邻显示设备(DA1至DA4)中,在两个相邻最外像素Po之间的间隔D2+D2可等于或小于在两个相邻像素之间的第一间隔D1。

参照图24,在其侧表面沿着第二方向Y彼此连接(或接触)的第一和第三显示设备DA1和DA3中,在第一显示设备DA1的最外像素Po的中心部CP与第三显示设备DA3的最外像素Po的中心部CP之间的间隔D2+D2可等于或小于设置在第一和第三显示设备DA1和DA3的每一个处的两个相邻像素Po和Pi之间的第一间隔D1(或像素节距)。

因此,在其侧表面沿着第一方向X和第二方向Y彼此连接(或接触)的两个相邻显示设备(DA1至DA4)的最外像素Po的中心部CP之间的间隔D2+D2可等于或小于设置在显示设备DA1至DA4的每一个处的两个相邻像素Po和Pi之间的第一间隔D1,由此在两个相邻显示设备(DA1至DA4)之间可不具有接缝或边界部,从而可不具有由于设置在显示设备DA1至DA4之间的边界部导致的暗区。结果,在多屏显示设备(其中多个显示设备DA1至DA4的每一个以N×M的形式平铺)上显示的图像可连续地显示,而在多个显示设备DA1至DA4之间的边界部没有断开感(或不连续感)。

在图24和25中,示出了多个显示设备DA1至DA4以2×2的形式平铺,但本发明的实施方式不限于此,多个显示设备DA1至DA4可以x×1的形式、1×y的形式、或者x×y的形式平铺。例如,在x×1形式中,x可以是大于或等于2的自然数;在1×y形式中,y可以是大于或等于2的自然数;在x×y形式中,x和y可以是大于或等于2的自然数,并且可彼此相等或不同。例如,在x×y形式中,x可以是大于或等于2的自然数,并且可等于y;或者x和y可以是大于或等于2的自然数,且y可大于或小于x。

如上所述,当多个显示设备DA1至DA4的每一个的显示部AA是一个屏幕并且显示一个图像时,根据本发明实施方式的多屏显示设备可显示在多个显示设备DA1至DA4之间的边界部不断开而是连续的图像,由此可提高观看由多屏显示设备显示的图像的观看者的沉浸感。

下面将描述根据本发明实施方式的发光显示设备和包括发光显示设备的多屏显示设备。

根据本发明实施方式的发光显示设备可包括:基板;显示部,所述显示部包括设置在所述基板上的多条像素驱动线以及选择性地连接至所述多条像素驱动线的多个像素;发光器件层,所述发光器件层包括设置在所述显示部处的自发光器件;堰部,所述堰部沿着所述基板的外围部设置,所述堰部包括具有金属线的至少一个堰;封装层,所述封装层被设置为覆盖所述发光器件层,所述封装层包括由所述堰部围绕的有机封装层;多个开关电路部,所述开关电路部被设置为与所述至少一个堰交叠并且选择性地连接至所述多条像素驱动线;以及前焊盘部,所述前焊盘部包括设置在所述基板的一个外围部处并且与所述多条像素驱动线以及所述至少一个堰的金属线电连接的多个前焊盘,其中所述多个开关电路部的每一个可包括第一开关电路和第二开关电路,所述第一开关电路和所述第二开关电路的每一个包括与所述至少一个堰的金属线电连接的栅极。

根据本发明的一些实施方式,所述多个开关电路部的每一个可设置在所述基板和所述至少一个堰之间。

根据本发明的一些实施方式,所述多个开关电路部的每一个可设置在所述多个像素中的、位于所述基板的第一外围部处的多个最外像素的相应一个中。

根据本发明的一些实施方式,所述至少一个堰的金属线可电连接至所述多个前焊盘的至少之一。

根据本发明的一些实施方式,所述堰部可包括彼此平行地设置并围绕所述显示部的第一堰、第二堰和第三堰,所述第一堰、所述第二堰和所述第三堰的每一个包括所述金属线,所述多个开关电路部的每一个还可包括第三开关电路,所述第一开关电路可被设置为与所述第一堰交叠并且包括与所述第一堰的金属线连接的栅极,所述第二开关电路可被设置为与所述第二堰交叠并且包括与所述第二堰的金属线连接的栅极,所述第三开关电路可被设置为与所述第三堰交叠并且可包括与所述第三堰的金属线连接的栅极。

根据本发明的一些实施方式,所述多个开关电路部的每一个可选择性地连接至所述多条像素驱动线中的彼此相邻设置的奇数数据线、基准电压线和偶数数据线,其中所述第一开关电路还可包括电连接至所述奇数数据线的第一电极和电连接至所述基准电压线的第二电极,所述第二开关电路还可包括电连接至所述偶数数据线的第一电极和电连接至所述基准电压线的第二电极,所述第三开关电路还可包括电连接至所述奇数数据线的第一电极和电连接至所述偶数数据线的第二电极。

根据本发明的一些实施方式,所述堰部可包括彼此平行地设置并围绕所述显示部的第一堰和第二堰,所述第一堰和所述第二堰的每一个包括所述金属线,所述第一开关电路可被设置为与所述第一堰交叠并且包括与所述第一堰的金属线连接的栅极,所述第二开关电路可被设置为与所述第二堰交叠并且包括与所述第二堰的金属线连接的栅极。

根据本发明的一些实施方式,所述多个开关电路部的每一个可选择性地连接至所述多条像素驱动线中的彼此相邻设置的奇数数据线、基准电压线和偶数数据线,其中所述第一开关电路还可包括电连接至所述奇数数据线的第一电极和电连接至所述基准电压线的第二电极,所述第二开关电路还可包括电连接至所述偶数数据线的第一电极和电连接至所述基准电压线的第二电极。

根据本发明的一些实施方式,所述堰部可包括堰,所述堰被设置为围绕所述显示部,所述堰包括所述金属线,所述第一开关电路可被设置为与所述堰交叠并且包括与所述堰的金属线连接的栅极,所述第二开关电路可与所述第一开关电路并联设置并与所述堰交叠,并且所述第二开关电路可包括与所述堰的金属线连接的栅极。

根据本发明的一些实施方式,所述多个开关电路部的每一个可选择性地连接至所述多条像素驱动线中的彼此相邻设置的奇数数据线、基准电压线和偶数数据线,其中所述第一开关电路还可包括电连接至所述奇数数据线的第一电极和电连接至所述基准电压线的第二电极,所述第二开关电路还可包括电连接至所述偶数数据线的第一电极和电连接至所述基准电压线的第二电极。

根据本发明的一些实施方式,所述发光显示设备还可包括用于向所述金属线提供接地电压的驱动电路部。

根据本发明的一些实施方式,所述发光显示设备还可包括:后焊盘部,所述后焊盘部包括分别与所述多个前焊盘交叠的多个后焊盘;连线部,所述连线部包括电连接至所述多个后焊盘的多条连线;输入焊盘部,所述输入焊盘部包括电连接至所述多条连线的多个输入焊盘;连接至所述输入焊盘部的驱动电路部;以及布线部,所述布线部包括分别电连接至所述多个前焊盘和所述多个后焊盘以围绕所述基板的外表面的多条布线。

根据本发明的一些实施方式,所述多个开关电路部的每一个可选择性地连接至所述多条像素驱动线中的彼此相邻设置的奇数数据线、基准电压线和偶数数据线,所述驱动电路部可包括:驱动集成电路,所述驱动集成电路包括数据驱动器和感测单元,所述数据驱动器包括用于向所述奇数数据线或所述偶数数据线输出测试信号的多个信号输出电路,所述感测单元用于基于所述测试信号感测经由所述第一开关电路和所述第二开关电路的至少之一流入所述基准电压线的电流;以及时序控制器,所述时序控制器基于从所述感测单元提供的感测数据向所述驱动集成电路提供测试数据并且设定偏置电压电平,所述偏置电压电平被输入给所述多个信号输出电路的每一个的偏置端子。

根据本发明的一些实施方式,所述时序控制器可基于所述感测数据来确定在所述多条布线之间是否出现短路,或者可产生所述多条布线中的与数据线连接的数据布线的线电阻值,并且基于产生的线电阻值来设定所述偏置电压电平。

根据本发明的一些实施方式,所述发光显示设备还可包括:前辅助焊盘部,所述前辅助焊盘部包括设置在所述基板的第二外围部处并且电连接至所述至少一个堰的金属线的至少一个前辅助焊盘;后辅助焊盘部,所述后辅助焊盘部包括与所述至少一个前辅助焊盘交叠的至少一个后辅助焊盘;以及辅助连线部,所述辅助连线部包括电连接至所述至少一个前辅助焊盘和所述至少一个后辅助焊盘的至少一条辅助连线,其中所述至少一条辅助连线可电连接至所述多个输入焊盘的至少之一。

根据本发明的一些实施方式,所述至少一个堰可包括:在所述基板上的第一堰图案;在所述第一堰图案上的第二堰图案;以及在所述第二堰图案上的第三堰图案,其中所述金属线位于所述第二堰图案和所述第三堰图案之间。

根据本发明的一些实施方式,所述至少一个堰还可包括底切区,所述底切区在所述第一堰图案的侧表面和所述第二堰图案之间实现,在所述堰部上的自发光器件在所述底切区中被隔离。

根据本发明的一些实施方式,所述发光显示设备还可包括分离部,所述分离部包括设置在所述至少一个堰附近的多个分离结构,其中所述多个分离结构的每一个可包括:下结构;以及上结构,所述上结构设置在所述下结构上并且相对于所述下结构具有屋檐结构,其中设置在所述分离部上的自发光器件可被所述屋檐结构隔离。

根据本发明的一些实施方式,所述发光显示设备还可包括分离部,所述分离部包括设置在所述至少一个堰附近的多个分离结构,其中所述多个分离结构的每一个可包括:下结构;以及上结构,所述上结构设置在所述下结构上并且相对于所述下结构具有屋檐结构,其中所述多个分离结构的至少之一还可包括设置在所述下结构和所述上结构之间的金属结构,其中所述金属结构可设置在所述下结构上并且相对于所述下结构具有另一屋檐结构,其中设置在所述分离部上的自发光器件可被所述金属结构隔离。

根据本发明的一些实施方式,所述多个分离结构的每一个可与所述多条像素驱动线交叠,所述金属结构可电连接至所述多条像素驱动线中的至少一条像素公共电压线。

根据本发明的一些实施方式,所述发光显示设备还可包括:位于所述基板和所述发光器件层之间的平坦化层;位于所述基板和所述平坦化层之间的钝化层;凹槽线,所述凹槽线设置在所述堰部的内部区处并且通过去除所述平坦化层和所述钝化层的全部来实现;以及底切区,所述底切区在与所述凹槽线相邻的钝化层的侧表面和与所述凹槽线相邻的平坦化层的侧表面之间实现,其中设置在所述凹槽线以及所述平坦化层的侧表面上的自发光器件可在所述底切区中被隔离。