一种大光敏面高计数率超导纳米线单光子探测器及实施方法

文献发布时间:2024-04-18 19:48:15

技术领域

本发明涉及激光雷达、超导单光子探测技术领域,具体为一种大光敏面高计数率超导纳米线单光子探测器及实施方法。

背景技术

超导纳米线单光子探测器作为性能最优异的光子探测器之一发展至今,其各项性能指标都取得了巨大的突破,具有较宽的响应光谱(响应波段可从中红外覆盖到X射线)、极高的系统探测效率(超过98%)、极低的暗计数(小于10

最大计数率是单光子探测器最重要的性能指标之一,通常定义为探测效率下降3dB时的计数率。超导纳米线的动态电感限制了超导纳米线单光子探测器的恢复时间,从而限制了最大计数率。同时,为了匹配大孔径的接收机,光子探测器需要具有大的探测面积。然而,随着面积的增加,电恢复时间将显著增加。目前,有一些工作通过多个独立的纳米线将最大计数率增加到超过Gcps,但它们消耗了更多的电路资源,并限制了可扩展性。还有工作引入了微米线来扩大超导单光子探测器的探测面积,但在高计数率方面仍然没有突破。还有工作通过将多条纳米线串联,同时分别各自并联电阻,在不增加读取复杂性的情况下有效地提高了最大计数率,然而电感的显著增加无法扩展到大面积,同时也会进一步限制最大计数率和时间精度。因此,同时具备大面积和高最大计数率的超导纳米线单光子探测器仍然是一个重要的课题,目前正在不断研究中。

发明内容

发明目的:为解决目前超导纳米线单光子探测器无法同时满足大光敏面和高计数率的要求,本发明提出了一种大光敏面高计数率超导纳米线单光子探测器及实施方法。

技术方案:一种大光敏面高计数率超导纳米线单光子探测器,包括:

低动态电感超导纳米线,用于检测光子;

放电加速偏置读出电路,用于读出低动态电感超导纳米线检测到的光子数;

其中,所述低动态电感超导纳米线由若干通道呈中心对称分布构成,每个所述通道均由多条纳米线并联组成;

其中,所述放电加速偏置读出电路包括:电感L

所述电感L

所述DC&RF端与低动态电感超导纳米线连接,用于为低动态电感超导纳米线提供偏置电流,以及获取低动态电感超导纳米线检测到的光子数;

所述DC端用于向放电加速偏置读出电路输入电流。

进一步的,每条所述纳米线均串联一片上电阻R到地。

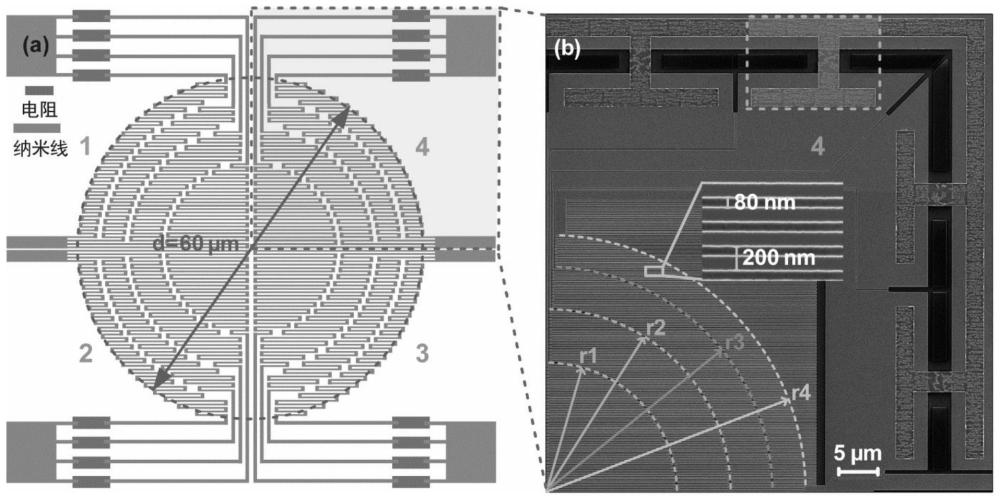

进一步的,对于同一通道中的多条纳米线,其以同心圆的形式进行排布,每条纳米线均为同心圆环结构。

进一步的,每条纳米线接收到的光子数相同。

进一步的,每条纳米线的面积相同。

进一步的,每条纳米线的长度相同。

进一步的,每个片上电阻R均为哑铃状结构,且所有的片上电阻R连成一个整体。

进一步的,所述电感L

本发明还公开了一种大光敏面高计数率超导纳米线单光子探测器的实施方法,包括:

制作低动态电感超导纳米线;

搭建放电加速偏置读出电路;

将低动态电感超导纳米线接入放电加速偏置读出电路,由放电加速偏置读出电路读出低动态电感超导纳米线检测到的光子数;

其中,低动态电感超导纳米线按照以下步骤制作得到:

步骤1:在氮化硅层上沉积氮化铌薄膜;

步骤2:通过电子束曝光获得纳米线图形,显影之后经过反应离子刻蚀得到纳米线;

步骤3:通过电子束曝光获得片上电阻图形;

步骤4:利用磁控溅射生长一层Ti薄膜;

步骤5:剥离得到片上电阻;

其中,所述纳米线图形由若干通道呈中心对称分布构成,每个所述通道均由多条纳米线并联组成;对于同一通道中的多条纳米线,其以同心圆的形式进行排布,每条纳米线均为同心圆环结构;

所述电阻图形为在每条所述纳米线均串联一片上电阻到地;

其中,放电加速偏置读出电路包括:电感L

进一步的,每个片上电阻均为哑铃状结构,且所有的片上电阻连成一个整体。

有益效果:本发明与现有技术相比,具有以下优点:

(1)本发明提出的一种大光敏面高计数率超导纳米线单光子探测器,能在显著扩大光敏面的情况下,同时保证高的计数率;

(2)本发明提出的一种大光敏面高计数率超导纳米线单光子探测器,利用低动态电感超导纳米线设计方法,可以在不显著增加读出复杂度的情况下,进一步扩展到更大光敏面上;

(3)本发明提出的放电加速偏置读出电路也可以应用于其他超导纳米线单光子探测器的偏置读出;

(4)本发明提出的一种大光敏面高计数率超导纳米线单光子探测器具有结构简单、容易制备、易操作、不需要专门的进行人员培训、成本低、工作效率高等优点。

附图说明

图1为低动态电感超导纳米线示意图和4号通道的SEM照片;

图2为超导纳米线单光子探测器件的I-V曲线;

图3为传统偏置读出电路示意图;

图4为放电加速偏置读出电路图;

图5为传统偏置读出电路和放电加速偏置读出电路的仿真结果对比图;

图6为传统偏置读出电路和放电加速偏置读出电路实测的计数率结果对比图;

图7为传统偏置读出电路和放电加速偏置读出电路实测的响应信号和时间抖动对比图。

具体实施方式

现结合附图和实施例进一步阐述本发明的技术方案。

实施例:

本实施例公开了一种大光敏面高计数率超导纳米线单光子探测器,其包括低动态电感超导纳米线和放电加速偏置读出电路。

其中,本实施例的低动态电感超导纳米线采用中心对称分布和并联纳米线结构,该结构可降低超导纳米线的动态电感;具体结构为:

低动态电感超导纳米线采用中心对称分布结构分布为多个通道,在本实施例中分成4个通道,每个通道由四条纳米线并联组成。假定总长度为l的纳米线动态电感为L

本实施例提出的低动态电感超导纳米线可按照以下步骤制备得到:

步骤1:在135nm厚的氮化硅层上沉积约8nm厚的氮化铌薄膜;

步骤2:通过电子束曝光获得纳米线图形,显影之后经过反应离子刻蚀得到蜿蜒的纳米线,纳米线实际线宽约为80nm,周期为200nm;

步骤3:得到纳米线之后,接着通过电子束曝光获得串联电阻图形;

步骤4:利用磁控溅射生长一层约50nm厚的Ti薄膜;

步骤5:剥离得到钛电阻。经过表征,钛电阻在4.2K的低温下阻值约为50欧姆。

制备完成的低动态电感超导纳米线,经对光封装后置于GM制冷机中进行降温,待温度降到2.3K以下进行表征。如图2所示,为上述器件的I-V曲线表征结果。4个通道的超导转变电流比较均匀,都在45μA左右,回滞电流6μA左右,超流回滞比~8,超导转变电流和回滞电流的测试结果是4根并联的纳米线超导转变电流和回滞电流之和。

图3示出了传统的偏置读出电路,传统的偏置读出电路在读出的过程中会存在电容充放电的效应,这会极大的限制超导纳米线单光子探测器的最大计数率。在读出的过程中存在充放电效应的电容包括交流耦合电容C

式中,C

为了缓解交流耦合电容充放电效应对超导纳米线单光子探测器最大计数率的影响,已经有研究报道了相应的改进办法,比如通过“电容-接地”电路泄放电容的放电电流,还有在超导纳米线单光子探测器和偏置读出电路之间加入衰减器进行隔离,这两种方法都能有效缓解电容充放电效应,但也存在一个共同的缺陷,那就是会很大幅度降低信号的幅值,而这对超导纳米线单光子探测器的高时间精度特性是极其不利的。

为了缓解传统的偏置读出电路对超导纳米线单光子探测器最大计数率的限制,本实施例提出了一种放电加速偏置读出电路,如图4所示。本实施例的放电加速偏置读出电路是一个三端电路,包括DC端、DC&RF端和读出端。该放电加速偏置读出电路是在传统偏置读出电路的基础上,在电感L

现结合图4,对本实施例的放电加速偏置读出电路的结构做进一步说明,其主要由电感L

在探测过程中,电容充放电效应仍然存在,与传统偏置读出电路不同的是,串联电阻R

同样地,根据基尔霍夫电流和基尔霍夫电压定律,可以用式(2)和式(3)描述了如图4所示改进电路的电压和电流随时间的变化关系:

式中,i

根据电路模型利用蒙特卡洛法则进行仿真,假定饱和探测效率为1。仿真得到的输出波形如图5中的(a)所示,其中灰色波形代表仿真的传统读出电路输出波形,黑色波形代表仿真的改进读出电路输出波形,对比二者可以看出使用电感接地的改进电路,并不会显著降低响应信号的幅值,而是会导致信号产生明显的过冲,这也是电容放电显著变快的一个表现。使用两种电路得到的计数率仿真结果如图5中的(b)所示,圆圈代表的是使用传统偏置读出电路仿真得到计数率,可以明显看出,计数率曲线后半段出现上翘的现象,并且随着入射光子数的增多,探测器闩锁较早,最大计数率仅为80Mcps。(除此之外,随着入射光强的不断增强,多光子同时到达的概率会逐渐上升,由此也会导致检测概率不断上升,而不再等于系统探测效率,从而也会出现计数率上翘的现象。)相反的,使用放电加速偏置读出电路,探测器的闩锁问题得到明显改善,同时计数率后半段并未出现上翘现象,取而代之的是由于入射光子数增多,探测效率下降,计数率增长变缓的趋势,最终的最大计数率为166Mcps(如图5中的(b)中的三角形所示)。

实际实验中,我们使用中心波长为1064nm的连续激光器作为光源,配合工作波长为1064nm的数字可调衰减器改变入射光子数,对超导纳米线单光子探测器进行辐照测试最大计数率,其中通道4的测试结果如图6所示,图6中的(a)中黑色圆圈为传统偏置读出电路测试结果,可以看到,随着入射光子数的增多,超导纳米线单光子探测器闩锁较早,最大计数率仅为18.4Mcps。灰色空心三角形为放电加速偏置读出电路测试结果,随着入射光子数的增多,超导纳米线单光子探测器闩锁情况得到明显改善,效率下降3dB时的计数率为37.8Mcps,同时动态范围增加了21dB。图6中的(b)显示了使用放电加速偏置读出电路后四个通道的总计数率。当效率降低3dB时,总计数率为147Mcps。

利用中心波段为1064nm的ps脉冲激光器作为光源,配合采样率为40GHz的高速示波器,来超导纳米线单光子探测器件的响应脉冲和时间抖动。分别利用传统偏置读出电路和用于改善高计数率下超导纳米线单光子探测器闩锁的放电加速偏置读出电路进行测试,测试结果如图7所示,使用用于改善高计数率下超导纳米线单光子探测器闩锁的放电加速偏置读出电路,超导纳米线单光子探测器的响应信号信噪比略有下降,从原本的113mV下降到现在的97.9mV,相应的时间抖动就从原本的114ps(FWHM)增大到138.6ps(FWHM)。因此,该放电加速偏置读出电路在显著改善高计数率下超导纳米线单光子探测器闩锁情况的同时,保证了响应脉冲的信噪比,从而保证超导纳米线单光子探测器的时间精度。

综上,本实施例提出的一种大光敏面高计数率超导纳米线单光子探测器能在显著扩大光敏面的情况下,同时保证高的计数率。并且本实施例提出的这种低动态电感超导纳米线设计方法可以在不显著增加读出复杂度的情况下,进一步扩展到更大光敏面上。与此同时,本实施例提出的放电加速偏置读出电路也可以应用于其他超导纳米线单光子探测器的偏置读出。本实施例提出的一种大光敏面高计数率超导纳米线单光子探测器对要求大光敏面、高计数率的激光雷达应用具有重要意义。

以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

以上所述实施例仅表达了本申请的一种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请专利的保护范围应以所附权利要求为准。

- 大光敏面超导纳米线单光子探测器

- 大光敏面超导纳米线单光子探测器