功率模块

文献发布时间:2023-06-19 09:29:07

技术领域

本发明是关于功率模块(power module)。

背景技术

近年,关于功率模块的开发,要求进一步的开关速度的提升。然而,进行高速开关,藉此产生在开关时从功率电路向控制电路输送杂讯的可能性。在专利文献1中,公开了将驱动高侧开关的栅极的路径与主电流路径分离的构成。

又,在非专利文献1登载了以下的构成。即,公开了包含输入控制信号的控制输入电路、以已被输入的信号为基础控制功率半导体的栅极电压的控制输出电路、以及向功率半导体输入输出电流的功率电路的构成。

又,在非专利文献1记载的构成中,在第二层中,在从第一层的控制输入电路隔着绝缘层对向的位置(正下方)配置有控制GND。在Hi-side的控制输出电路的正下方配置有连接到SW电位的图案(控制输出GND(Hi))。又,在Lo-side的控制输出电路的正下方配置有连接到功率GND的图案(控制输出GND(Lo))。

现有技术文献

专利文献

专利文献1:日本公开特许公报“特开2013-141035号”

非专利文献1“GN001 Application Guide Design with GaN Enhancement mode HEMT”Updated on April 12,2018 GaN Systems Inc.(日文翻译“GN001アプリケーションガイドエンハンスメントモードGaN-HEMTを用いたデザイン”)(第四十页)

发明内容

本发明所要解决的技术问题

然而,在专利文献1公开的半导体装置的构成中,由于MOSFET的源极电极与驱动器电路的源极电极被金属配线设为同电位,有产生功率GND的电位变动所致的向控制电路的杂讯的输送的可能性。

又,非专利文献1由于功率GND在功率半导体的开关时电位变动,有因感应电动势(induced electromotive force)对控制输出电路输送杂讯的可能性。换言之,有功率GND的杂讯隔着绝缘材料,输送到配置在不同的层间中对向的位置的控制输出电路的可能性。

本发明的一方案将抑制在开关时功率GND的电位变动所致的杂讯输送到控制电路的控制输出电路设为目的。

解决问题的方案

为了解决上述的课题,本发明的一方案的功率模块包括:功率电路,包括一或多个功率半导体;以及控制电路,对所述一或多个功率半导体的各个供给栅极信号;所述控制电路包含:一或多个栅极驱动器,根据控制信号产生所述各栅极信号,所述控制信号被输入的侧与产生所述各栅极信号的侧被绝缘;控制输入电路,所述控制信号被输入,用以将所述控制信号供给到所述一或多个栅极驱动器;以及控制输出电路,将所述各栅极信号供给到所述各功率半导体;其中所述功率电路的接地、与所述控制电路的接地被分离;所述控制电路的所述控制输出电路的至少一部分、与所述控制电路的接地隔着绝缘层,配置在互相在不同的层中对向的位置。

发明效果

根据本发明的一方案,能够抑制在开关时功率GND的电位变动所致的杂讯输送到控制电路的控制输出电路。

附图说明

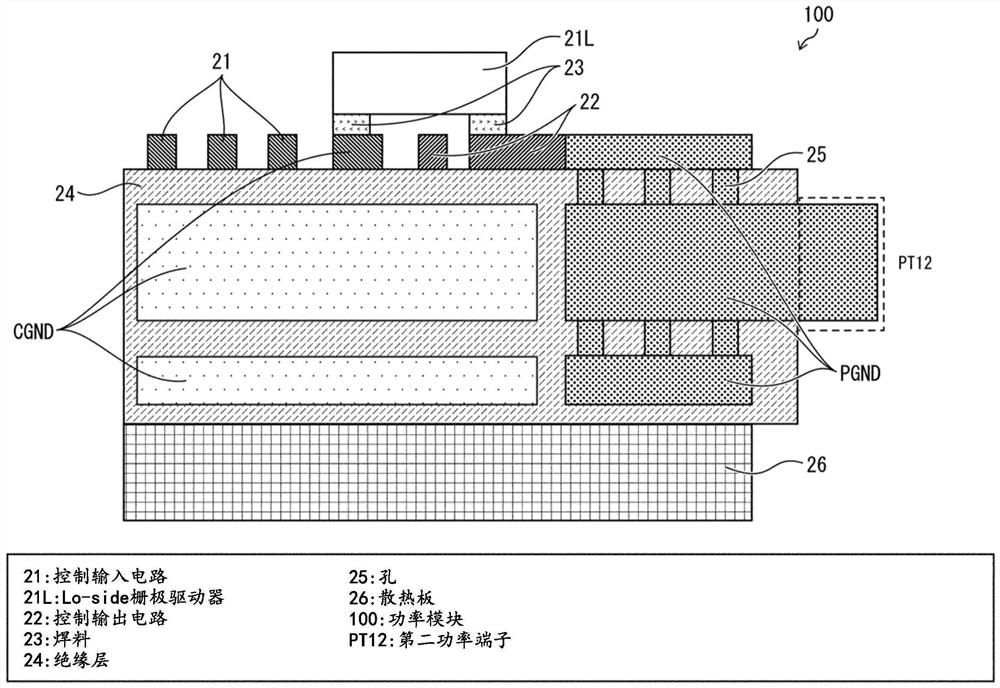

图1是表示本发明的实施方式1的功率模块的构成例的说明图。

图2是图1的A-A’剖面图。

图3是表示图1的功率模块的构成的例子的电路图。

图4的(a)~(c)是表示实施方式1与先前技术的开关时的栅极电压波形的图。

图5是表示本发明的实施方式2的功率模块的构成例的说明图。

图6是图5的A-A’剖面图。

图7是表示图5的功率模块的功率电路部的图。

图8是表示本发明的实施方式3的功率模块的构成例的说明图。

图9是表示比较例的功率模块的构成例的剖面图。

具体实施方式

[实施方式1]

若针对本发明的一实施方式进行说明则如以下所述。以下,为了便于说明,有针对在特定的实施方式已说明的构成与具有相同功能的构成,标注相同的符号,省略其说明的情况。

(功率模块的构成例)

图1是表示本实施方式的功率模块100的构成例的说明图,图2是图1的A-A’剖面图,图3是表示图1的功率模块100的构成的例子的电路图。

首先,如图3所示,功率模块100包括功率电路1、控制电路2。功率电路1包括一或多个功率半导体(在图3的例示中包括High-side(以下称为“Hi-side”)功率半导体11H以及Low-side(以下称为“Lo-side”)功率半导体11L,在本说明书中,不特别区别的情况,有总称功率半导体11的情况)。控制电路2包括控制输入电路21、控制输出电路22。

功率电路1是在例如Hi-side功率半导体11H与Lo-side功率半导体11L使电流输入输出。控制电路2对所述一或多个功率半导体的各个供给栅极信号。具体而言,控制电路2控制各功率半导体11的栅极电压。

在本实施方式中,也将“接地”记载为“GND”。又,图3的符号PWMH是表示Hi-side控制信号,PWML是表示Lo-side控制信号,VCC是表示控制输入电源,CGND(Control Ground)是表示控制输入GND,PGND(Power Ground)是表示功率GND(以下同样)。

又,VDDH是表示Hi-side控制输出电源,VEEH是表示Hi-side控制输出GND,VDDL是表示Lo-side控制输出电源,VEEL是表示Lo-side控制输出GND。

又,Power是表示功率输入,Output是表示功率输出,PGND1是表示第一PGND,PGND2是表示第二PGND。又,不区别第一PGND与第二PGND的情况有总称PGND的情况。

细节虽然于后叙述,但如图3所示,PGND1以及PGND2、与CGND被分离。又,如图2所示,控制电路2的控制输出电路22的至少一部分、与CGND隔着绝缘层24,配置在互相在不同的层中对向的位置。

功率半导体11作为例子例如由GaN等构成。又,如图3所示,在Power(后述的第一功率端子)、PGND1(后述的第二功率端子)(PGND2(后述的第四功率端子))之间,连接有旁路电容器(bypass condenser)12(也参照图1)。针对旁路电容器12的细节于后叙述。

在本实施方式的功率电路1的Hi-side功率半导体11H与Lo-side功率半导体11L中,例如,在导通(turn on)Hi-side功率半导体11H的时候,使接近400V的电压开关动作。另一方面,对上述的Hi-side功率半导体与Lo-side功率半导体11L供给栅极信号的控制电路2是例如导通电压为1V。

在使接近400V的电压开关动作的功率电路1中,功率半导体11的开关时的PGND(PGND1、PGND2)的电位变动大。若PGND的电位变动大,则由于在控制电路2的CGND,功率半导体11的开关时的PGND的电位变动所致的杂讯变得容易输送,有控制电路2的栅极信号使功率半导体11误导通的疑虑。

又,例如,在功率半导体11使用GaN的情况,有因功率半导体11的高速开关,上述的功率半导体11的开关时的PGND的电位变动变得更强的倾向。

(比较例)

图9是表示比较例的功率模块200的构成例的剖面图。在图9所示的一般的功率模块200中,在控制电路(包含221与222。以下同样),包括将输入侧与输出侧绝缘的栅极驱动器221L,对准功率模块200的第一层的输入侧与输出侧(对准栅极驱动器221L)构成第二层的PGND与CGND。然而,如上述,若功率半导体的开关时的PGND的电位变动大,则就算是,即便包括将输入侧与输出侧绝缘的栅极驱动器221L,也从第二层的PGND,向第一层的输出侧的控制电路(控制输出电路222)输送杂讯,有控制电路的栅极信号使功率半导体误导通的疑虑。

(实施方式1的效果)

在本实施方式中,根据上述的构成,PGND1、与CGND被分离,由于控制电路2的控制输出电路22的至少一部分、与CGND隔着绝缘层24,配置在互相在不同的层中对向的位置,能够抑制在开关时PGND的电位变动所致的杂讯输送到控制电路2的控制输出电路22。

因此,根据本实施方式的功率模块100的构成,CGND、与控制输出电路22的一部分隔着绝缘层24在不同的层中对向,藉此起到抑制杂讯从PGND输送到输出侧(控制输出电路22)的效果。

(功率模块的构成例)

接着,一边参照图1以及图2一边详细地说明功率模块100的构成。如上述,控制电路2包括控制输入电路21、控制输出电路22。又,如图1~图3所示,控制电路2包括一或多个栅极驱动器(在例示中Hi-side栅极驱动器21H以及Lo-side栅极驱动器21L)。

栅极驱动器根据控制信号(PWMH、PWML)产生所述各栅极信号。控制输入电路21被输入控制信号(PWMH、PWML),将所述控制信号供给到所述一或多个栅极驱动器。控制输出电路22是将所述各栅极信号供给到功率半导体11。

又,在功率电路1中,如图1以及图3所示,Hi-side功率半导体11H连接到第三功率端子PT13与第一功率端子PT11之间,包括源极电极11Hs、栅极电极11Hg、漏极电极11Hd。

另一方面,Lo-side功率半导体11L连接到第三功率端子PT13与第二功率端子PT12之间,包括源极电极11Ls、栅极电极11Lg、漏极电极11Ld。又,如图三所示,Hi-side功率半导体11H与Lo-side功率半导体11L是晶体管。

又,如图3所示,Hi-side功率半导体11H的源极电极11Hs连接到第三功率端子PT13,栅极电极11Hg连接到Hi-side栅极驱动器21H,漏极电极11Hd连接到第一功率端子PT11。

另一方面,Lo-side功率半导体11L的源极电极11Ls连接到第二功率端子PT12,栅极电极11Lg连接到Lo-side栅极驱动器21L,漏极电极11Ld连接到第三功率端子PT13。

又,在图1中,符号W12表示第一配线,符号W34表示第二配线。针对第一配线W12以及第二配线W34的细节,以实施方式3一边参照图8一边详细地进行说明。

又,如图3所示,由于控制功率半导体11的栅极驱动器,例如Hi-side栅极驱动器21H以及Lo-side栅极驱动器21L使用控制输入电路21与控制输出电路22被绝缘的栅极驱动器,较佳为将功率侧与控制侧杂讯性地分离。

又,图1的符号13(被一点链线包围的部分)是表示第三层(图1的最里侧的层)的功率电路的图案部。

又,如上述,图1的符号PT11~PT14是表示第一~第四功率端子,即表示与功率电路1的Power、PGND1、Output、以及PGND2的各个对应的功率端子。

又,在图1所示的功率模块100中,由于PGND的电位在功率半导体的开关时变动,即便在控制输出电路22的对向面配置PGND图案也不稳定。因此,在本实施方式中,在控制输出电路22的至少一部分的对向面配置CGND。

又,将CGND设为充分的大小,藉此能够防止在开关时控制输出电路22的杂讯的影响通过CGND输送到控制输入电路21。

返回图2继续说明。如上述,图2是图1的A-A’剖面图。如图2所示,在本实施方式中,功率模块100成为例如其基板配线为三层构造。在各层间,设置有绝缘层24。

又,在图2的最下部设置有将功率模块100发出的热向外部散热的散热版26。针对散热版26于后叙述。在散热板26的上面隔着绝缘层接合功率模块100的第三层。如图1以及图2所示,CGND设置在与控制输入电路21以及控制输出电路22两方重叠的范围内。

另一方面,如图1以及图2所示,PGND设置在与功率电路1重叠的范围内。又,在本实施方式中,较佳为设为功率电路1的,例如微细的图案部设置在第一层,在第二层大电流流过的构造。控制输入电路21以及控制输出电路22设置在功率模块100的第一层。

另外,为了明确各层,将功率设备的安装面设为第一层,从第一层依接近的顺序设为第二层、第三层。又,由于在第一层以及第二层的功率电路1的正下方部分设置PGND,藉此电流路径在第二层与第三层成为反向平行(Antiparallel),能够减低寄生电感(parasiticinductance)。

例如使降压斩波器(step-down chopper)动作的情况,若Hi-side功率半导体11H成为ON,则电流从功率端子PT11流入,由此从PT13经由电感器(inductor)朝向负载流动,进一步所述电流从负载通过PT12流入,最后从PT14的PGND2流出。换言之,如此的构造也称为回流构造。由此能够减低上述的寄生电感。

又,如图2所示,功率电路1的外部连接用功率端子较佳为形成为将相对于电流的流路的剖面面积宽广的第二层向外部突出的形状。

根据上述的构成,能够一边以使大电流流过外部连接用功率端子的方式构成,也一边变厚设置在第二层的CGND,能够也提升在开关时对于杂讯的稳定性。

(散热板)

如上述,在本实施方式中,也可以包括以将功率模块100发出的热向外部散热的方式,接合到功率模块100的基板的散热板26。为了提高对散热板26的热传导,基板层数少,并且为了防止功率电路的高的电流密度所致的配线的温度上升,较佳为散热板26的厚度厚。

又,针对散热板26与功率模块100的基板的接合方法不特别限定,也可以是例如藉由黏接剂黏接的方法,也可以藉由螺丝部件等的螺合固定。

本实施方式的功率模块100为了抑制在开关时PGND的电位变动所致的杂讯输送到控制电路2,CGND与PGND被绝缘。又,以PGND与控制电路2在正下方区域不重叠的方式构成。

返回图1~图3继续说明。如图2所示,控制输入电路21、与PGND1通过基板的绝缘材料配置在互相在不同的层中不对向的位置。

具体而言,在图2中,控制输入电路21虽然设置在功率模块100的图2的左侧的第一层,但PGND、与至少第二层以及第三层PGND设置在功率模块100的图2的右侧的,与控制输出电路22不对向的层。

根据上述的构成,能够更适当地抑制在开关时PGND的电位变动所致的杂讯输送到控制电路。

又,图1的左右两端的有切口的圆表示连接配置在第一层~第三层的配线的孔,中心部的圆表示连接配置在第一层~第二层的配线的孔。又,包含CGND所包含的多个点(·)的区域是表示在第二层、第三层重复同样的图案的部分。

图2的符号25是表示连接配置在上述第一层~第三层的配线的孔。符号23是表示用以将Hi-side栅极驱动器21H分别进行CGND以及控制输出电路22的接合的焊料。

(作用效果)

如上述,在非专利文献1中,在控制输入电路的正下方配置有CGND,在控制输出电路的正下方配置有PGND。因此,进行本实施方式的功率模块100与先前技术的验证。其结果表示在图4的(a)~(c)。

图4的(a)~(c)是表示实施方式1与先前技术的开关时的栅极电压波形的图。又,关于图4的验证条件以及图式的说明是如以下。

·验证方法:藉由示波器的电压测量

·导通电压:1V

·黑实线:Lo-side功率半导体的断开(turn off)时的Lo-side栅极输出电压

(PGND电位基准)(左轴)

·灰虚线:Lo-side“功率半导体”断开,Hi-side“功率半导体”导通时的输出电压

(PGND电位基准)(右轴)

·横轴的时间是将Lo-side栅极电压低于2V的时机作为原点

(验证结果例1)

图4的(a)是将PGND与CGND分离,在控制输入电路以及控制输出电路的对向面配置有PGND的情况的结果。如图4的(a)所示,藉由开关的PGND电位变动所致的杂讯因感应电动势隔着绝缘层也对控制输出电路赋予杂讯。之后,因来自被输入包含杂讯的信号的栅极驱动驱动器的输出信号引起误导通。

又,在功率半导体使用GaN设备的情况,晶体管从OFF成为ON的导通的阈值电压为大致1V。在图4的(a)中从70奈秒到110奈秒连续地产生2V左右的杂讯,在杂讯进一步增加超过阈值的情况有因误导通电路短路而模块损坏的危险性。

又,由于为了避免误导通具有将控制输出电路的基准电位相对于PGND电位降低到-2V以下的必要,在开关OFF时产生损失,降低效率。

(验证结果例2)

图4的(b)是将PGND与CGND分离,在控制输入电路的对向面配置有CGND、在控制输出电路的对向面配置有PGND的情况的结果。如图4的(b)所示,从PGND藉由感应电动势隔着绝缘层对控制输出电路赋予杂讯。

又,在图4的(b)中,在50奈秒附近产生3V左右的杂讯,在超过阈值的情况有因误导通电路短路而模块损坏的可能性。又,由于为了避免误导通具有将控制输出电路的基准电位相对于PGND电位降低到-2V以下的必要,在开关OFF时产生损失,降低效率。

(验证结果例3)

如上述,图4的(c)是将PGND与CGND分离,在控制输出电路的对面未包含PGND的情况的结果。如图4的(c)所示,由于开关所致的PGND电位变动未对控制电路赋予影响,不产生误导通。

又,在图4的(c)中,由于杂讯为1V左右,误导通的可能性极少。又,由于若为本构成的杂讯等级则有能够将控制输出电路的基准电位相对于PGND电位不降低地使用的可能性,能够降低开关OFF时的损失,改善效率。

如以上,在验证结果例1~2中,由于未考虑控制输出电路与PGND的位置关系,PGND的电位变动不是对CGND而是对控制输出电路赋予影响。另一方面,本实施方式是由于PGND与控制电路2在正下方区域不重叠的构成、控制电路2的控制输出电路22的至少一部分、CGND使用隔着绝缘层24,配置在互相在不同的层中对向的位置的构成,能够抑制在开关时PGND的电位变动所致的杂讯输送到控制电路2的控制输出电路22。

[实施方式2]

针对本发明的其他实施方式,在以下进行说明。另外,为了便于说明,针对与在上述实施方式已说明的部件与具有相同功能的部件,标注相同图式标记,不重复其说明。

(功率模块的其他构成例)

图5是表示本实施方式的功率模块100a的构成例的说明图,图6是图5的A-A'剖面图。如图6所示,在本实施方式中,功率模块100a成为例如其基板配线为两层构造。在各层间,设置有绝缘层24。

又,在本实施方式,也为了明确各层,依图6的上至下的顺序设为第一层、第二层。另外,若与上述实施方式1比较,则由于本实施方式成为两层构造,能够进一步提升散热性。

与上述实施方式1同样地,本实施方式的功率模块100a为了抑制PGND的电位变动所致的杂讯输送到控制电路2,CGND与PGND被绝缘。又,以PGND与控制电路2在正下方区域不重叠的方式构成。

如图5所示,在功率模块100a中,功率电路1包括作为功率半导体11,半桥(halfbridge)连接的第一功率半导体11H与第二功率半导体11L。又,图5的符号12是表示旁路电容器。

又,功率电路1还包括第一功率端子PT11、第二功率端子PT12、第三功率端子PT13、上述的旁路电容器12。

第一功率端子PT11是经由第一配线W12连接到第一功率半导体11H的漏极电极11Hd。第二功率端子PT12是经由与所述第一配线W12平行的第二配线W34连接到第二功率半导体11L的源极电极11Ls(也参照图3)。旁路电容器12跨及所述第一配线与所述第二配线,连接到积载方向。第三功率端子PT13连接到第一功率半导体11H的源极电极11Hs以及第二功率半导体11L的漏极电极11Ld。

如图5所示,功率电路1的外部连接用功率端子较佳为形成为将相对于电流的流路的剖面面积宽广的第二层向外部突出的形状。

根据上述的构成,能够一边以使大电流流过外部连接用功率端子(PT12、PT13以及PT14)的方式构成,也一边变厚设置在第二层的CGND,能够也提升在开关时对于杂讯的稳定性。

在此,如上述,本实施方式的第一功率端子PT11以及第二功率端子PT12分别相当于实施方式1的第一功率端子以及第二功率端子。

如上述,根据上述的构成,在本实施方式中,除了能够起到实施方式1的作用效果以外也起到下述的效果。即,由于能够将旁路电容器12配置在功率半导体11的附近,能够将漏极电感Ld设为小。由此,由于能够减低导通时的损失,谋求电力变换效率的提升。

(功率电路部)

图7是表示图5的功率模块100a的功率电路部的图。如图7所示,在功率模块100a中,在旁路电容器12的配置处配置有孔25(也参照图6)。

因此,由于能够使通过旁路电容器12的电流的比例增加,能够使杂讯减低效果进一步提升。此外,为了使旁路电容器12的电流密度提升,更佳为将旁路电容器12的地面的部分的配线宽度缩小的构成。

又,在本实施方式中,在相同平面(层)内成为回流构造,藉此谋求减低电感的效果。

[实施方式3]

针对本发明的其他实施方式,在以下进行说明。另外,为了便于说明,针对与在上述实施方式已说明的部件与具有相同功能的部件,标注相同图式标记,不重复其说明。

图8是表示本发明的实施方式的功率模块100b的构成例的说明图。在实施本实施方式的时候,假定为“在控制输出电路的正下方(正下方)包含PGND的功率模块的构成”。

在本实施方式中,成为以下的构成。

在本实施方式的功率模块100b中,所述第一配线W12包括第一配线部W1、第二配线部W2。第一配线部W1一端连接到第一功率端子PT11,从第一功率端子PT11沿着第一方向F1延伸。第二配线部W2连接到第一配线部W1的另一端,从所述另一端,朝向第一功率半导体11H,向与第一方向F1为相反的方向延伸。

又,所述第二配线W34包括第三配线部W3、第四配线部W4。第三配线部W3一端连接到第二功率端子PT12,从第二功率端子PT12沿着第一方向F1延伸。第四配线部W4连接到第三配线部W3的另一端,从所述另一端,朝向第二功率半导体11L,向与第一方向F1为相反的方向延伸。

如此,由于藉由功率线的折返构造,电流路径成为反向平行,能够进一步减低电感。

另外,即便在控制电路2的正下方配置有PGND,在其之间也设置屏蔽图案。例如,将包含控制电路的层设为第一层,将包含第二功率端子PT12的层设为第三层,在其之间等设置屏蔽图案,设为三层构造。

另外,在水平方向的PGND与控制电路2的图案间设置既定的距离。例如,由于以在垂直方向中控制电路2与PGND的图案为一对电容器的方式动作,虽然电场耦合(electricfield coupling)强容易受到杂讯的影响,但由于在水平方向中电场耦合变弱,例如若分离1.0mm左右则能够一定程度地抑制杂讯的影响。

根据上述的构成,能够将PGND与CGND杂讯性地分离。即,能够起到与上述实施方式1~2同样的效果。

[藉由软件的实现例]

功率模块100的控制模块(尤其控制电路2)也可以是由集成电路(IC芯片)等形成的逻辑电路(硬件)实现,也可以由软件实现。

后者的情况,功率模块100包括执行为实现各功能的软件的程序的命令的计算机。此计算机例如包括具备至少一个处理器(控制装置)的,并且存储上述程序的计算机可读取的一个记录介质。然后,在上述计算机中,上述处理器从上述记录介质读取上述程序并加以执行,藉此达本发明的目的。作为上述处理器,例如能够使用CPU(Central ProcessingUnit)。作为上述记录介质,能够使用“非暂时性的有形介质”,例如,除了ROM(Read OnlyMemoryMemory)之外,磁带、硬盘、卡片、半导体存储器、可编程逻辑电路等。又,也可以还包括展开上述程序的RAM(Random Access Memory)等。又,上述程序,也可以经由可传送所述程序的任意的传送介质(通信网络及广播波等)向上述计算机供给。另外,本发明的一方案,也能以上述程序藉由电子性的传送而体现的、埋入于载波的数据信号的方式来实现。

[总结]

为了解决上述的课题,本发明的方案1的功率模块(100~100B)包括:功率电路(1),包括一或多个功率半导体(11);以及控制电路(2),对一或多个功率半导体(11)的各个供给栅极信号;所述控制电路(2)包含:一或多个栅极驱动器(21H以及21L),根据控制信号产生所述各栅极信号,所述控制信号被输入的侧与产生所述各栅极信号的侧被绝缘;控制输入电路(21),所述控制信号被输入,用以将所述控制信号供给到所述一或多个栅极驱动器(21H以及21L);以及控制输出电路(22),用以将所述各栅极信号供给到各功率半导体(11);其中功率电路(1)的接地(PGND)、与控制电路(2)的接地(CGND)被分离;控制电路(2)的控制输出电路(22)的至少一部分、与控制电路(2)的接地(CGND)隔着绝缘层(24),配置在互相在不同的层中对向的位置。

根据上述的构成,能够抑制在开关时功率电路的接地(PGND)的电位变动所致的杂讯输送到控制电路。

本发明的方案2的(100~100b)也可以是,在上述方案1中,控制输入电路(21)、与功率电路(1)的接地(PGND)配置在互相在不同的层中不对向的位置。

本发明的方案3的(100)也可以是,在上述方案1或2中,功率模块(100)的基板配线以三层构成。

本发明的方案4的(100a~100b)也可以是,在上述方案1或2中,功率模块(100a~100b)的基板配线以两层构成。

本发明的方案5的(100a~100b)也可以是,在上述方案1至4中的任一个方案中,功率电路(1)包括:第一功率半导体(11H)与第二功率半导体(11L),作为功率半导体(11)而被半桥连接;功率电路(1)还包括:第一功率端子(PT11),经由第一配线(W12)连接到第一功率半导体(11H);第二功率端子(PT12),经由与第一配线(W12)平行的第二配线(W34)连接到第二功率半导体(11L);第三功率端子(PT13),连接到第一功率半导体(11H)的源极电极(11Hs)以及第二功率半导体(11L)的漏极电极(11Ld);以及旁路电容器(12),跨及所述第一配线与所述第二配线,在积载方向连接。

本发明的方案6的(100a~100b)也可以是,在上述方案5中,所述第一配线包括:第一配线部(W1),一端连接到第一功率端子(PT11),从第一功率端子(PT11)沿着第一方向(F1)延伸;以及第二配线部(W2),连接到第一配线部(W1)的另一端,从所述另一端,朝向第一功率半导体(11H),向与第一方向(F1)为相反的方向延伸;所述第二配线包括:第三配线部(W3),一端连接到第二功率端子(PT12),从第二功率端子(PT12)沿着第一方向(F1)延伸;以及第四配线部(W4),连接到第三配线部(W3)的另一端,从所述另一端,朝向第二功率半导体(11L),向与第一方向(F1)为相反的方向延伸。

本发明的方案7的(100a~100b)也可以是,在上述方案1至6中的任一个方案中,还包括:散热版(26),接合到功率模块(100a~100b)的基板。

本发明并非限定为上述的各实施方式,可于权利要求所示的范围内进行各种变更,针对将分别公开于不同实施方式的技术手段适当地进行组合而得的实施方式,也包含于本发明的技术范围。此外,组合分别在各实施方式公开的技术性方法,藉此能够形成新的技术性特征。

附图标记说明

1...功率电路;2...控制电路;11H...Hi-side功率半导体(功率半导体);11L...Lo-side功率半导体(功率半导体);12...旁路电容器;13...功率电路第三层图案部;21...控制输入电路;21H...Hi-side栅极驱动器;21L...Lo-side栅极驱动器;22...控制输出电路;23...焊料;24...绝缘层;25...孔;26...散热板;100、100a~100b、200...功率模块;PT11...第一功率端子;PT12...第二功率端子;PT13...第三功率端子;PT14...第四功率端子;W1~W4...第一~第四配线部;W12...第一配线;W34...第二配线;F1...第一方向