芯片模组封装结构、封装方法及电路板

文献发布时间:2023-06-19 19:33:46

技术领域

本申请涉及芯片封装技术领域,尤其涉及一种芯片模组封装结构、封装方法及电路板。

背景技术

声表面波滤波器(Saw Filter)的工作原理是声波在芯片表面传输,故针对声表面波滤波器的封装必须要保证叉指换能器表面不能接触其他物质,即需保证其芯片表面是空腔结构,否则影响信号传输。基于声表面波滤波器的射频模组产品,其元件组成还包含天线开关、低噪放大器、电容、电感等常规的无需空腔即可工作的元件,即为非滤波器芯片。

在现有技术中,射频模组内的所有芯片(包括滤波器芯片及非滤波器芯片)的底部都存在空腔,部分非滤波器元器件由于凸点占空比过小,在经过冷热冲击等可靠性测试后,凸点会出现局部裂纹及凸点被熔化的情况,存在可靠性失效风险。

发明内容

本申请的目的是提供一种芯片模组封装结构、封装方法及电路板,以避免芯片的凸点出现局部裂纹,提高芯片模组的可靠性。

本申请第一方面的实施例提供一种芯片模组封装结构,包括:基板,具有相对的第一表面和第二表面;滤波器芯片,包括与所述第一表面之间形成第一空腔的第一芯片本体、以及与所述第一表面电连接的第一凸点;非滤波器芯片,包括与所述第二表面之间形成第二空腔的第二芯片本体、以及与所述第二表面电连接且位于所述第二空腔内的第二凸点;隔离层,在所述第一表面上覆盖所述滤波器芯片,以封闭所述第一空腔;第一塑封层,将所述滤波器芯片和所述隔离层包封于所述第一表面上,并被所述隔离层隔离于所述第一空腔的外侧;第二塑封层,将所述非滤波器芯片包封于所述第二表面上,并填充所述第二空腔。

在一些示例中,所述第一表面上设有至少两个所述滤波器芯片,所述隔离层在至少两个所述滤波器芯片之间连续延伸。

在一些示例中,所述第一空腔的高度不小于所述第一凸点的高度。

在一些示例中,所述滤波器芯片包括多个间隔的所述第一凸点,所述第一表面上设有分别与多个所述第一凸点对应的多个第一金属垫,多个所述第一凸点分别与对应的所述第一金属垫电连接;任意相邻的两个所述第一金属垫之间由设于所述第一表面上的第一绝缘层隔开,所述第一绝缘层将所述第一表面与覆盖所述第一表面的所述隔离层隔离。

在一些示例中,封装结构还包括锡球,锡球设于所述第二表面上,所述锡球的一部分暴露于所述第二塑封层之外,所述锡球的另一部分由所述第二塑封层包封于所述第二表面上。

在一些示例中,所述非滤波器芯片包括多个间隔的所述第二凸点,所述第二表面上设有分别与所述锡球和多个所述第二凸点对应的多个第二金属垫,所述锡球和多个所述第二凸点分别与对应的所述第二金属垫电连接;任意相邻的两个所述第二金属垫之间由设于所述第二表面上的第二绝缘层隔开,所述第二绝缘层将所述第二表面与所述第二塑封层隔离。

本申请第二方面的实施例提供一种芯片模组封装方法,包括:提供基板,所述基板具有相对的第一表面和第二表面;提供滤波器芯片至所述第一表面,所述滤波器芯片包括第一芯片本体和第一凸点,所述第一芯片本体与所述第一表面之间形成第一空腔;将所述第一凸点与所述第一表面电连接;在所述第一表面上形成覆盖所述滤波器芯片的隔离层;形成将所述滤波器芯片和所述隔离层包封于所述第一表面上的第一塑封层,所述第一塑封层被所述隔离层隔离于所述第一空腔的外侧;提供非滤波器芯片至所述第二表面,所述非滤波器芯片包括第二芯片本体和第二凸点,第二芯片本体与所述第二表面之间形成第二空腔且所述第二凸点位于所述第二空腔内;将所述第二凸点与所述第二表面电连接;形成将所述非滤波器芯片包封于所述第二表面的第二塑封层,所述第二塑封层填充所述第二空腔。

在一些示例中,所述方法还包括:在所述第二表面上形成锡球;所述形成将所述非滤波器芯片包封于所述第二表面的第二塑封层,包括:形成将所述非滤波器芯片和所述锡球包封于所述第二表面的第二塑封层;所述方法还包括:去除所述锡球上的部分所述第二塑封层,以使所述锡球的一部分暴露于所述第二塑封层之外。

在一些示例中,所述方法还包括:去除所述锡球周围的部分所述第二塑封层,使所述锡球的外周壁与所述第二塑封层之间形成空隙;在所述锡球表面进行印刷锡膏;进行回流焊接,完成封装。

本申请第三方面的实施例提供一种电路板,包括第一方面实施例所述的芯片模组封装结构。

本申请实施例通过将滤波器芯片和非滤波器芯片分别配置于基板的两个不同表面上,便于对滤波器芯片和非滤波器芯片分别进行不同形式的封装,一方面使第一芯片本体与基板之间的空腔被保留,实现滤波功能,另一方面使第二芯片本体与基板之间的空腔被塑封料填充,非滤波器芯片的凸点被塑封料包裹,或者说塑封料为非滤波器芯片的凸点提供保护,避免了在可靠性测试过程中非滤波功能芯片的凸点被熔化后发生流动导致与基板接触不良的情况,避免凸点出现局部裂纹,提高芯片模组的可靠性。另外,上述结构配置使芯片模组封装结构具有更小的封装尺寸。

附图说明

为了更清楚地说明本说明书实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本说明书中记载的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。在附图中:

图1是本申请实施例中基板的剖面图;

图2是本申请实施例中滤波器芯片配置于基板上的剖视图;

图3是本申请实施例中隔离层包封滤波器芯片的剖视图;

图4是本申请实施例中第一塑封层包封隔离层和滤波器芯片的剖视图;

图5是本申请实施例中锡球配置于基板上的剖视图;

图6是本申请实施例中非滤波器芯片配置于基板上的剖视图;

图7是本申请实施例中第二塑封层包封锡球和非滤波器芯片的剖视图;

图8是本申请实施例中第二塑封层的一部分被去除后的剖视图;

图9是本申请实施例中锡膏印刷于锡球表面的剖视图;

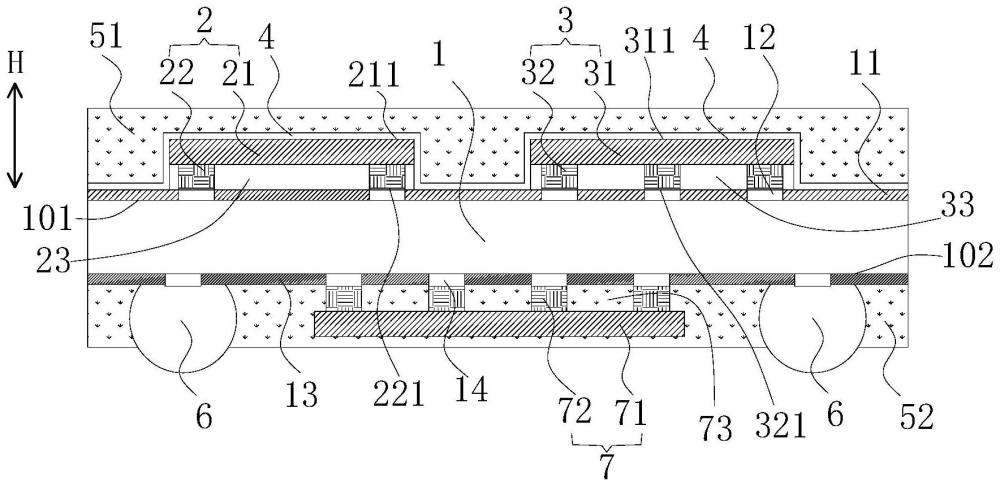

图10是本申请实施例中芯片模组封装结构的剖视图;

图11是本申请实施例中芯片模组封装方法的流程示意图。

具体实施方式

为了使本技术领域的人员更好地理解本说明书中的技术方案,下面将结合本说明书实施例中的附图,对本说明书实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本说明书一部分实施例,而不是全部的实施例。基于本说明书中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都应当属于本说明书保护的范围。

在本申请实施例中,术语“第一”、“第二”等用于对不同元素从称谓上进行区分,但并不表示这些元素的空间排列或时间顺序等,这些元素不应被这些术语所限制。术语“和/或”包括相关联列出的术语的一种或多个中的任何一个和所有组合。术语“包含”、“包括”、“具有”等是指所陈述的特征、元素、元件或组件的存在,但并不排除存在或添加一个或多个其它特征、元素、元件或组件。术语“多个”的含义是两个或两个以上,除非另有说明。

第一方面的实施例

本申请第一方面的实施例提供一种芯片模组封装结构,其包括基板、滤波器芯片、非滤波器芯片、隔离层、第一塑封层和第二塑封层。基板具有相对的第一表面和第二表面。滤波器芯片包括与第一表面之间形成第一空腔的第一芯片本体、以及与第一表面电连接的第一凸点。非滤波器芯片包括与第二表面之间形成第二空腔的第二芯片本体、以及与第二表面电连接且位于第二空腔内的第二凸点。隔离层在第一表面上覆盖滤波器芯片,以封闭第一空腔。第一塑封层将滤波器芯片和隔离层包封于第一表面上,并被隔离层隔离于第一空腔的外侧。第二塑封层将非滤波器芯片包封于第二表面上,并填充第二空腔。

本申请实施例通过将滤波器芯片和非滤波器芯片分别配置于基板的两个不同表面(即第一表面和第二表面)上,便于对滤波器芯片和非滤波器芯片分别进行不同形式的封装,一方面使第一芯片本体与基板之间的空腔被保留,实现滤波功能,另一方面使第二芯片本体与基板之间的空腔被塑封料填充,非滤波器芯片的凸点被塑封料包裹,或者说塑封料为非滤波器芯片的凸点提供保护,避免了在可靠性测试过程中非滤波功能芯片的凸点被熔化后发生流动导致与基板接触不良的情况,避免凸点出现局部裂纹,提高芯片模组的可靠性。另外,上述结构配置使芯片模组封装结构具有更小的封装尺寸。

下面参照附图对本申请实施例的实施方式进行说明。

图10是本申请实施例的芯片模组封装结构的一个示例的示意图。

如图10所示,基板1具有相对的第一表面101和第二表面102。滤波器芯片配置于第一表面101上。尽管图10示出两个滤波器芯片,即滤波器芯片2和滤波器芯片3,应当理解,本申请实施例中滤波器芯片的数量也可以是一个或者多于两个,本申请对此不做限制。

如图10所示,滤波器芯片2包括第一芯片本体21和设于第一芯片本体21上的第一凸点22,第一芯片本体21与第一表面101之间形成第一空腔23,第一凸点22位于第一空腔23内,第一凸点22与第一表面101电连接。类似地,滤波器芯片3包括第一芯片本体31和设于第一芯片本体31上的第一凸点32,第一芯片本体31与第一表面101之间形成第一空腔33,第一凸点32位于第一空腔33内,第一凸点32与第一表面101电连接。在图10的示例中,整个第一凸点22位于第一空腔23内,整个第一凸点32位于第一空腔33内。

尽管图10示出滤波器芯片2包括两个第一凸点22,滤波器芯片3包括三个第一凸点32,应当理解,本申请实施例中每个滤波器芯片的凸点的数量也可以是更少或者更多个,本申请对此不做限制。

如图10所示,隔离层4在第一表面101上覆盖滤波器芯片2、3,以封闭第一空腔23、33,换句话说,第一空腔23、33为密闭的空腔。隔离层4可以是干膜,例如可以是阻焊掩膜,隔离层4的材质可以是绿漆、环氧树脂胶、紫外线胶、PCB、硅胶等隔离材料。

如图10所示,第一塑封层51将滤波器芯片2、3和隔离层4包封于第一表面101上,并被隔离层4隔离于第一空腔23、33的外侧,而不会进入第一空腔23、33的内部。在图10的示例中,隔离层5将基板1与第一塑封层51完全隔离,换句话说,基板1与第一塑封层51不接触。

如图10所示,非滤波器芯片7包括第二芯片本体71和设于第二芯片本体71上的第二凸点72,第二芯片本体71与第二表面102之间形成第二空腔73,第二凸点72位于第二空腔73内,第二凸点72与第二表面102连接。

尽管图10示出一个非滤波器芯片7且非滤波器芯片7包括四个第二凸点72,应当理解,本申请实施例中非滤波器芯片7的数量可以多于一个,每个非滤波器芯片7的凸点的数量也可以是更少或者更多个,本申请对此不做限制。非滤波器芯片7可以是天线开关、低噪放大器、电容、电感等无需空腔即可工作的电子元件。

如图10所示,第二塑封层52将非滤波器芯片71包封于第二表面102上并填充第二空腔73,第二凸点72被第二塑封层52包裹,避免了在可靠性测试过程中非滤波功能芯片7的第二凸点72被熔化后发生流动导致与基板接触不良的情况,避免第二凸点72出现局部裂纹,提高芯片模组的可靠性。

可选地,隔离层4的厚度不大于20μm。隔离层4的厚度可以等于20μm或者小于20μm,例如可以是18μm、15μm、10μm或5μm。因此隔离层4的厚度与现有技术相比更小。较薄的隔离层4使得在塑封时,隔离层4不会冲击第一凸点22、32而影响性能。

在一些实施例中,第一表面101上设有至少两个滤波器芯片,隔离层4在至少两个滤波器芯片之间连续延伸,比如隔离层4可以在全部滤波器芯片之间连续延伸或者在部分滤波器芯片之间连续延伸。在图10的示例中,隔离层4在滤波器芯片2和滤波器芯片3之间连续延伸,换句话说,隔离层4连续覆盖滤波器芯片2和滤波器芯片3,简化封装工艺。另外,由于封装完成后滤波器芯片2和滤波器芯片3之间的隔离层4呈连续而非断开状态,封装结构的整体性更好,整体结构强度更佳。

在一些实施例中,如图10所示,基板1限定高度方向H,第一表面101和第二表面102在高度方向H上彼此相对。在高度方向H上,第一空腔23、33的高度不小于第一凸点22、32的高度,例如第一空腔23、33的高度等于第一凸点22、32的高度。可选地,第一空腔23、33的高度为50μm~60μm,比如可以是55μm。

在一些实施例中,如图10所示,基板1的第一表面101上设有分别与各第一凸点22、32对应的多个第一金属垫12,各第一凸点22、32分别与对应的第一金属垫12电连接,例如可以采用倒装焊接方式将第一凸点22、32与第一金属垫12电性连接。

本实施例中,进一步,任意相邻的两个第一金属垫12之间由设于第一表面101上的第一绝缘层11隔开,以使第一金属垫12之间彼此绝缘,第一绝缘层11将第一表面101与覆盖第一表面101的隔离层4隔离,换句话说,第一绝缘层11铺设于第一表面101上,隔离层4铺设于第一绝缘层11。

可选地,如图10所示,第一绝缘层11的面向隔离层4的表面与第一金属垫12的面向第一凸点22、32的表面在高度方向H上基本平齐,相应地,隔离层4由第一芯片本体21、31的背对基板1的表面211、311朝第一表面101延伸至与第一凸点22、32的朝向基板1的表面221、321在高度方向H上基本平齐。

在一些实施例中,如图10所示,芯片模组封装结构还包括至少一个锡球6,锡球6设于第二表面102上,锡球6的一部分暴露于第二塑封层52之外,锡球6的另一部分由第二塑封层52包封。图10示出两个锡球6,应当理解,本申请实施例中锡球6的数量也可以是更少或者更多个,本申请对此不做限制。在对滤波器芯片2、3和非滤波器芯片7封装后,锡球6为封装结构的外露的电连接焊点。可以采用BGA植球工艺在第二表面102上形成锡球6。

在一些实施例中,如图10所示,第二表面102上设有分别与锡球6和各第二凸点72对应的多个第二金属垫14,锡球6和各第二凸点72分别与对应的第二金属垫14电连接。例如可以采用倒装焊接方式将第二凸点72与第二金属垫14电性连接。

本实施例中,进一步,任意相邻的两个第二金属垫14之间由设于第二表面102上的第二绝缘层13隔开,以使第二金属垫14之间彼此绝缘,第二绝缘层13将第二表面102与第二塑封层52隔离。

第二方面的实施例

如图11所示,本申请第二方面的实施例提供一种芯片模组封装方法。需说明的是,本申请实施例中列举的步骤顺序仅仅为众多步骤执行顺序中的一种方式,不代表唯一的执行顺序。在实际封装工艺中,可以按照实施例或者附图所示的方法顺序执行、调序执行或者并行执行。

本申请的一优选实施例显示于图1~图10中。

参考图1,封装方法可以始于提供基板1。基板1具有相对的第一表面101和第二表面102(参见图2)。在图1的示例中,第一表面101上设有多个第一金属垫12和将各第一金属垫12隔绝的第一绝缘层11,第二表面102上设有多个第二金属垫14和将各第二金属垫14隔绝的第二绝缘层13。

参考图2,提供滤波器芯片2、3至第一表面101。滤波器芯片2、3包括第一芯片本体21、31和第一凸点22、32,第一芯片本体21、31与第一表面101之间形成第一空腔23、33且第一凸点22、32位于第一空腔23、33内。

再参考图2,将第一凸点22、32与第一表面101电连接。示例性地,可以通过倒装焊接方式将各第一凸点22、32与第一表面101上的各第一金属垫12电连接。

参考图3,在第一表面101上形成覆盖滤波器芯片2、3的隔离层4。隔离层4可以是干膜,例如可以是环氧树脂膜。

可选地,隔离层4在至少两个滤波器芯片2、3之间连续延伸,换句话说,隔离层4对至少两个滤波器芯片2、3形成连续覆盖。

可选地,隔离层4可以是干膜,隔离层4可以是阻焊掩膜,例如隔离层4的材质为绿漆、环氧树脂胶、紫外线胶、PCB、硅胶等隔离材料。

参考图4,形成将滤波器芯片2、3和隔离层4包封于第一表面101上的第一塑封层51,第一塑封层51被隔离层4隔离于第一空腔23、33的外侧,从而防止第一塑封层51填充第一空腔23、33,保证滤波器芯片2、3能够实现滤波。

参考图5,可选地,在第二表面102上形成锡球6,锡球6与第二金属垫14电连接。例如可以采用BGA植球工艺在第二表面102上形成锡球6。

参考图6,提供非滤波器芯片7至第二表面102,非滤波器芯片7包括第二芯片本体71和第二凸点72,第二芯片本体71与第二表面102之间形成第二空腔73且第二凸点72位于第二空腔73内。

再参考图6,将第二凸点72与第二表面102电连接。示例性地,可以通过倒装焊接方式将各第二凸点72与第二表面102上的各第二金属垫14电连接。

参考图7,形成将非滤波器芯片7和锡球6包封于第二表面102的第二塑封层52,第二塑封层52填充第二空腔73(参见图8),从而对第二凸点72进行包裹和保护,避免了在可靠性测试过程中非滤波功能芯片7的第二凸点72被熔化后发生流动导致与基板接触不良的情况,避免第二凸点72出现局部裂纹,提高芯片模组的可靠性。

参考图8,可选地,去除锡球6上的部分第二塑封层52,以使锡球6的一部分暴露于第二塑封层52之外。在去除部分第二塑封层52时,需保证非滤波功能芯片7仍被第二塑封层52完全包裹。例如可以采用基板背部研磨工艺去除锡球6上的部分第二塑封层52。

参考图9,可选地,去除锡球6周围的部分第二塑封层52,使锡球6的外周壁与第二塑封层52之间形成空隙8。例如可以采用镭射激光切割机切割去除锡球6周围的部分第二塑封层52,以形成空隙8。

再参考图9,可选地,在锡球6表面进行印刷锡膏9。

参考图10,进行回流焊接,完成封装。经回流焊接后,锡膏9和锡球6重新熔融形成新的锡球凸点,更于后续产品的可焊性。

第三方面的实施例

本申请第三方面的实施例提供一种电路板,其包括第一方面实施例所述的芯片模组封装结构。由于在第一方面的实施例中,已经对该芯片模组封装结构的结构进行了详细说明,其内容被合并于此,此处省略说明。

以上所述仅为本说明书的实施例而已,并不用于限制本说明书。对于本领域技术人员来说,本说明书可以有各种更改和变化。凡在本说明书的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本说明书的权利要求范围之内。

- 芯片封装方法及芯片封装结构

- 电子设备及其电路板结构以及球栅阵列封装模组

- 芯片子模组与凸台的匹配方法及压接型IGBT器件的封装方法

- 一种易于散热的芯片封装结构及其封装方法

- 一种激光芯片封装结构及其封装方法

- 芯片结构、芯片结构的封装方法及电路板模组

- 无封装芯片直埋印制电路板的结构和方法、芯片封装结构