存储器读写电路、存储器控制方法及电子设备

文献发布时间:2023-06-19 19:33:46

技术领域

本公开涉及集成电路技术领域,具体而言,涉及一种存储器读写电路、存储器控制方法及电子设备。

背景技术

动态随机存取存储器(Dynamic Random Access Memory,DRAM)是计算机中常用的半导体存储器件,由于具有结构简单,密度高,功耗低,价格低廉等优点,在计算机领域和电子行业中受到了广泛的应用。

对于DRAM而言,在读写阶段往往对性能具有较高的要求,以确保DRAM具有较好的用户体验。

然而,在刷新阶段,并不需要DRAM具有同样高的性能,因此,在读写阶段和刷新阶段采用不同的控制方式,对于减小DRAM的功耗具有重要意义。

需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

发明内容

本公开的目的在于提供一种存储器读写电路、存储器控制方法及电子设备,以减小DRAM在刷新模式下的瞬时电流。

本公开的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本发明的实践而习得。

根据本公开的第一方面,提供一种存储器读写电路,包括:感应放大器,所述感应放大器的电源电压由第一控制信号或第二控制信号控制供给,所述第一控制信号控制供给的第一电源电压大于所述第二控制信号控制供给的第二电源电压;控制信号产生模块,用于在正常读写模式下,控制产生所述第一控制信号的脉冲时长为第一时长;在刷新模式下,控制产生所述第一控制信号的脉冲时长为第二时长,所述第二时长小于所述第一时长;所述控制信号产生模块,还用于在所述刷新模式下,控制所述存储器中多个存储块的所述第一控制信号顺次开启。

在本公开的一种示例性实施方式中,所述控制信号产生模块还用于,在所述正常读写模式或所述刷新模式下,控制所述第一控制信号终止时,产生所述第二控制信号。

在本公开的一种示例性实施方式中,所述控制信号产生模块还用于,在所述正常读写模式或所述刷新模式下,控制产生所述第二控制信号的脉冲时长大于产生所述第一控制信号的脉冲时长。

在本公开的一种示例性实施方式中,所述第二时长为0。

在本公开的一种示例性实施方式中,所述控制信号产生模块还用于,在所述刷新模式下,不产生所述第一控制信号,直接产生所述第二控制信号,并控制多个所述存储块的所述第二控制信号顺次开启。

在本公开的一种示例性实施方式中,所述感应放大器的负极电压由负极控制信号控制供给,所述控制信号产生模块还用于,在产生所述第一控制信号或所述第二控制信号后,控制产生所述负极控制信号。

在本公开的一种示例性实施方式中,还包括:字线、位线和互补位线,所述感应放大器设置在所述位线和所述互补位线之间;所述控制信号产生模块还用于,在产生所述第一控制信号和所述第二控制信号之前,关闭施加在所述位线和所述互补位线上的位线平衡控制信号;在所述字线上施加字线开启电压,以将与所述字线连接的晶体管打开。

在本公开的一种示例性实施方式中,所述控制信号产生模块还用于,在所述刷新模式下,控制多个所述存储块的所述字线开启电压顺次开启。

在本公开的一种示例性实施方式中,还包括:激活窗口信号产生模块和刷新窗口信号产生模块,所述激活窗口信号产生模块和所述刷新窗口信号产生模块分别与所述控制信号产生模块相连;所述激活窗口信号产生模块用于产生存储块激活窗口信号,所述刷新窗口信号产生模块用于产生刷新窗口信号;所述控制信号产生模块用于在同时获取到存储块激活窗口信号和刷新窗口信号的时候,控制所述存储器进入所述刷新模式;在只获取到激活窗口信号的时候,控制所述存储器进入所述正常读写模式。

在本公开的一种示例性实施方式中,所述控制信号产生模块包括:第一延时子模块、第二延时子模块和第一与非门;其中,所述第一与非门的输入端接入所述第一延时子模块的输出端和所述第二延时子模块的输出端,所述第一与非门的输出端输出所述第一控制信号;所述第二延时子模块的输入端与所述第一延时子模块的输出端相连,所述第一延时子模块的输入端接入所述存储块激活窗口信号,所述第二延时子模块的输出端输出所述第二控制信号。

在本公开的一种示例性实施方式中,所述第一延时子模块包括第一延时单元和第二与非门;其中,所述第二与非门的输入端接入所述第一延时单元的输出端和所述存储块激活窗口信号,所述第一延时单元的输入端接入所述存储块激活窗口信号。

在本公开的一种示例性实施方式中,所述第一延时单元包括:第一多路选择器、第一延时器件、第二延时器件和第一延时选择单元;其中,所述第一延时器件和所述第二延时器件分别用于延迟所述存储块激活窗口信号,所述第一延时器件的延迟时长大于所述第二延时器件的延迟时长,所述第二延时器件的输出端与所述第一延时选择单元的输入端相连,所述第一延时器件的输出端和所述第一延时选择单元的输出端分别与所述第一多路选择器的输入端相连,所述第一延时选择单元的输入端还接入所述存储块激活窗口信号,所述第一延时选择单元的控制端接入第一测试信号;所述第一多路选择器的控制端接入所述刷新窗口信号,用于在产生所述刷新窗口信号时,选择输出所述第一延时选择单元的输出信号,在没有产生所述刷新窗口信号时,选择输出所述第一延时器件的延迟信号。

在本公开的一种示例性实施方式中,所述第二延时子模块包括第二延时单元和第一与门;其中,所述第一与门的输入端与所述第二延时单元的输出端和所述第一延时子模块的输出端分别相连,所述第二延时单元的输入端与所述第一延时子模块的输出端相连。

在本公开的一种示例性实施方式中,所述第二延时单元包括:第三延时器件、第二延时选择单元和第二多路选择器;其中,所述第三延时器件用于延迟所述第一延时子模块的输出信号,所述第二延时选择单元的输入端接入所述第一延时子模块的输出信号,所述第二延时选择单元的输出端与所述第二多路选择器的输入端相连;所述第二多路选择器的控制端接入所述刷新窗口信号,所述第二多路选择器用于在产生所述刷新窗口信号时,选择输出所述第二延时选择单元的输出信号,在没有产生所述刷新窗口信号时,选择输出被所述第三延时器件延迟的所述第一延时单元的输出信号。

在本公开的一种示例性实施方式中,所述第二延时选择单元包括:第二子延时单元、第三子延时单元和第二子多路选择器;其中,所述第二子延时单元的输入端接入所述第一延时子模块的输出信号,所述第三子延时单元的输入端接入所述第二子延时单元的输出信号,所述第二子多路选择器的输入端接入所述第二子延时单元的输出信号和所述第三子延时单元的输出信号,所述第二子多路选择器的控制端接入第二测试信号,在所述第二测试信号作用下,控制所述存储器中多个存储块的所述第一控制信号顺次开启,或控制多个所述存储块的所述第二控制信号顺次开启。

在本公开的一种示例性实施方式中,所述控制信号产生模块还包括:位线平衡控制信号产生子模块、字线开启电压产生子模块和第三延时子模块;其中,所述位线平衡控制信号产生子模块的输入端接入所述存储块激活窗口信号,所述位线平衡控制信号产生子模块的输出端输出所述位线平衡控制信号;所述字线开启电压产生子模块的输入端与所述第三延时子模块的输出端相连,所述字线开启电压产生子模块的输出端输出所述字线开启电压,所述第三延时子模块的输入端接入所述存储块激活窗口信号。

在本公开的一种示例性实施方式中,所述第三延时子模块包括第三延时单元和第二与门;其中,所述第二与门的输入端接入所述第三延时单元的输出信号和所述存储块激活窗口信号,所述第三延时单元的输入端接入所述存储块激活窗口信号。

在本公开的一种示例性实施方式中,所述第三延时单元包括:第三多路选择器、第四延时器件、第五延时器件和第三延时选择单元;其中,所述第四延时器件和所述第五延时器件分别用于延迟所述存储块激活窗口信号,所述第四延时器件的延迟时长大于所述第五延时器件的延迟时长,所述第五延时器件的输出端与所述第三延时选择单元的输入端相连,所述第四延时器件的输出端和所述第三延时选择单元的输出端分别与所述第三多路选择器的输入端相连;所述第三多路选择器的控制端接入所述刷新窗口信号,用于在产生所述刷新窗口信号时,选择输出所述第三延时选择单元的输出信号,在没有产生所述刷新窗口信号时,选择输出所述第四延时器件的延迟信号。

在本公开的一种示例性实施方式中,所述第三延时选择单元包括:第四子延时单元和第三子多路选择器;其中,所述第四子延时单元的输入端接入所述第五延时器件的输出信号,所述第三子多路选择器的输入端接入所述第五延时器件的输出信号和所述第四子延时单元的输出信号,所述第三子多路选择器的控制端接入第三测试信号;不同的所述存储阵列,对应的所述第四子延时单元的延时长度不同。

根据本公开的第二方面,提供一种存储器控制方法,所述存储器包括感应放大器,所述感应放大器的电源电压由第一控制信号或第二控制信号控制供给,所述第一控制信号控制供给的电源电压大于所述第二控制信号控制供给的电源电压,所述方法包括:在正常读写模式下,控制产生所述第一控制信号的脉冲时长为第一时长;在刷新模式下,控制产生所述第一控制信号的脉冲时长为第二时长,所述第二时长小于所述第一时长;在所述刷新模式下,控制所述存储器中多个存储块的所述第一控制信号顺次开启。

在本公开的一种示例性实施方式中,所述方法还包括:在所述正常读写模式或所述刷新模式下,控制所述第一控制信号终止时,产生所述第二控制信号。

在本公开的一种示例性实施方式中,所述方法还包括:在所述正常读写模式或所述刷新模式下,控制产生所述第二控制信号的脉冲时长大于产生所述第一控制信号的脉冲时长。

在本公开的一种示例性实施方式中,所述第二时长为0。

在本公开的一种示例性实施方式中,所述方法还包括:在所述刷新模式下,不产生所述第一控制信号,直接产生所述第二控制信号;并控制多个所述存储块的所述第二控制信号顺次开启。

在本公开的一种示例性实施方式中,所述感应放大器的负极电压由负极控制信号控制供给,所述方法还包括:在产生所述第一控制信号或所述第二控制信号后,控制产生所述负极控制信号。

在本公开的一种示例性实施方式中,所述存储器还包括:字线、位线和互补位线,所述感应放大器设置在所述位线和所述互补位线之间;在产生所述第一控制信号或所述第二控制信号之前,所述方法还包括:关闭施加在所述位线和所述互补位线上的位线平衡控制信号;在所述字线上施加字线开启电压,以将与所述字线连接的晶体管打开。

在本公开的一种示例性实施方式中,所述方法还包括:在所述刷新模式下,控制多个所述存储阵列的所述字线开启电压顺次开启。

在本公开的一种示例性实施方式中,所述方法还包括:在同时获取到激活窗口信号和刷新窗口信号的时候,控制所述存储器进入所述刷新模式;在只获取到激活窗口信号的时候,控制所述存储器进入所述正常读写模式。

根据本公开的第三方面,提供一种电子设备,包括:多个存储块、多个阵列控制器,和多个上述的存储器读写电路;其中,所述存储器读写电路设置在所述阵列控制器中,一个所述存储器读写电路对应控制一个所述阵列。

本公开提供的技术方案可以包括以下有益效果:

本公开示例性实施方式中,通过设置在刷新模式下产生的第一控制信号的脉冲时长小于在正常读写模式下产生的第一控制信号的脉冲时长,使得较高的第一电源电压在刷新模式下的供给时长小于在正常读写模式下的供给时长,如此,,既能满足对tRCD性能没有较高要求的刷新需求,又能减小刷新过程中第一电源电压持续时间较长所造成的电流损耗,避免在刷新模式下产生过大的瞬时电流,也减小了对第一电源电压承载能力设计的要求;另外,通过在刷新模式下,控制多个存储块的第一控制信号顺次开启,可以进一步减小刷新模式下的瞬时电流,提高存储器的VDD承载能力。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

附图说明

此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本公开的实施例,并与说明书一起用于解释本公开的原理。显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。在附图中:

图1示意性示出了根据本公开的示例性实施例的一种存储单元的结构示意图;

图2示意性示出了根据本公开的示例性实施例的一种DRAM中外围电路的结构示意图;

图3示意性示出了根据本公开的示例性实施例的一种DRAM中存储块的结构示意图;

图4示意性示出了根据本公开的示例性实施例的一种DRAM中感应放大器的结构示意图;

图5示意性示出了根据本公开的示例性实施例的一种存储器在正常读写模式下的控制信号波形图;

图6示意性示出了根据本公开的示例性实施例的一种存储器在刷新模式下的控制信号波形图一;

图7示意性示出了根据本公开的示例性实施例的一种存储器在刷新模式下的控制信号波形图二;

图8示意性示出了根据本公开的示例性实施例的一种存储器在刷新模式下的控制信号波形图三;

图9示意性示出了根据本公开的示例性实施例的一种存储器在刷新模式下的控制信号波形图四;

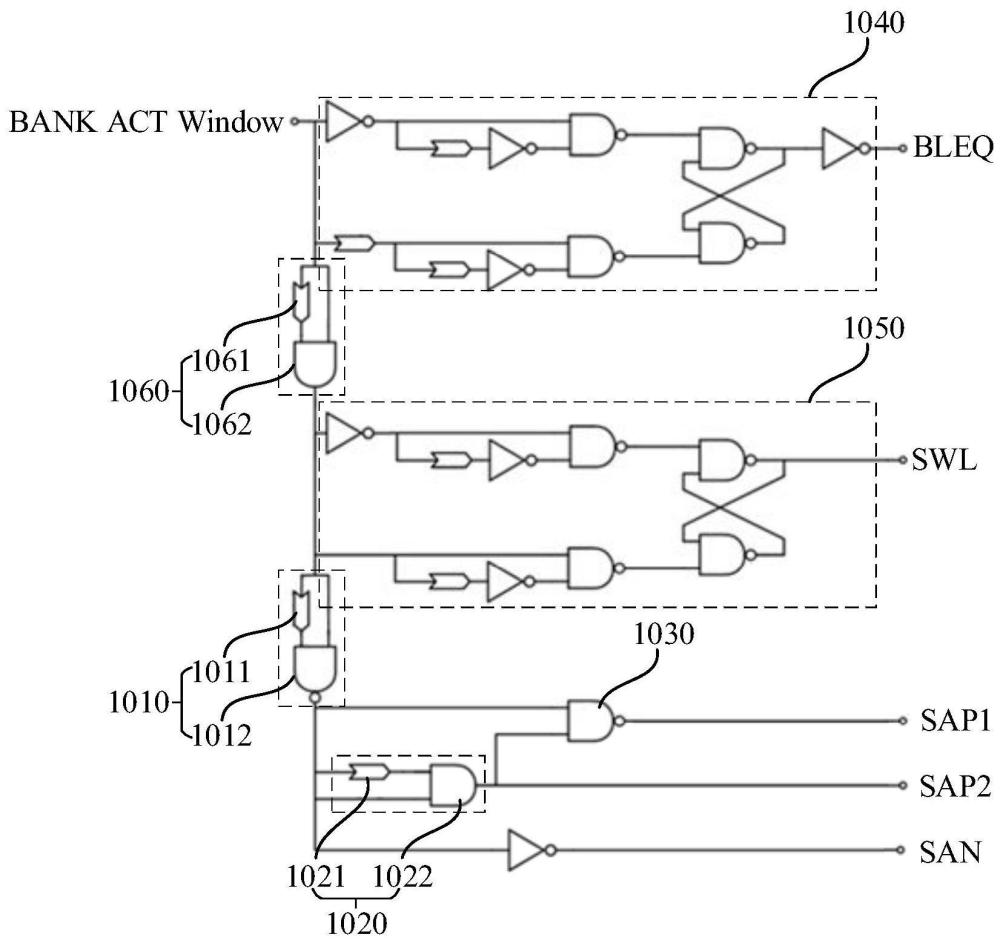

图10示意性示出了根据本公开的示例性实施例的一种存储器读写电路中的控制信号产生模块的电路结构示意图;

图11示意性示出了根据本公开的示例性实施例的存储器读写电路中第一延时单元的电路结构示意图;

图12示意性示出了根据本公开的示例性实施例的存储器读写电路中第二延时单元的电路结构示意图;

图13示意性示出了根据本公开的示例性实施例的存储器读写电路中第三延时单元的电路结构示意图;

图14示意性示出了根据本公开的示例性实施例的存储器控制方法的步骤流程图。

具体实施方式

现在将参考附图更全面地描述示例实施例。然而,示例实施例能够以多种形式实施,且不应被理解为限于在此阐述的实施例;相反,提供这些实施例使得本公开将全面和完整,并将示例实施例的构思全面地传达给本领域的技术人员。在图中相同的附图标记表示相同或类似的部分,因而将省略对它们的重复描述。

此外,所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施例中。在下面的描述中,提供许多具体细节从而给出对本公开的实施例的充分理解。然而,本领域技术人员将意识到,可以实践本公开的技术方案而没有所述特定细节中的一个或更多,或者可以采用其它的方法、组元、装置、步骤等。在其它情况下,不详细示出或描述公知结构、方法、装置、实现、材料或者操作以避免模糊本公开的各方面。

附图中所示的方框图仅仅是功能实体,不一定必须与物理上独立的实体相对应。即,可以采用软件形式来实现这些功能实体,或在一个或多个软件硬化的模块中实现这些功能实体或功能实体的一部分,或在不同网络和/或处理器装置和/或微控制器装置中实现这些功能实体。

半导体存储器用于计算机、服务器、诸如移动电话等手持设备、打印机和许多其他电子设备和应用。半导体存储器的存储器阵列中包括多个存储单元,每个存储单元存储信息的至少一位。DRAM为这种半导体存储器的实例。本方案优选地用于DRAM中。因此,接下来的实施例描述是参考作为非限制性示例的DRAM进行的。

在DRAM集成电路设备中,存储单元阵列典型地以行和列布置,使得特定的存储单元可以通过指定其阵列的行和列来寻址。字线将行连接到一组探测单元中数据的位线感应放大器。然后在读取操作中,选择或者“列选择”感应放大器中的数据子集用于输出。

参照图1,DRAM中的每个存储单元100通常包括电容器110、晶体管120、字线(WordLine,WL)130和位线(Bit Line,BL)140,晶体管120的栅极与字线130相连、晶体管120的漏极与位线140相连、晶体管120的源极与电容器110相连,字线130上的电压信号能够控制晶体管120的打开或关闭,进而通过位线140读取存储在电容器110中的数据信息,或者通过位线140将数据信息写入到电容器110中进行存储。

存储块就是由上述的多个存储单元所组成,存储块一般会占用整个DRAM器件面积的50-65%,DRAM器件的其余面积则主要由外围电路所组成。参照图2,示出了一种外围电路的结构示意图。如图2,DRAM器件的外围电路包括Command Decoder命令解码器210、地址锁存器(Address Latch)220、刷新地址计数器(Refresh Address Counter,RAC)230、地址多路选择器(Address Mux,AM)240和前置解码器(Pre-Decoder,Pre-D)250。其中,CommandDecoder命令解码器210用于对系统下发的RESET_n、CKE、CK_t/CK_c、PAR、TEN、CS_n、ACT_n等命令CMD进行命令解码,Address Latch地址锁存器220则用于对地址代码A<16:0>等进行暂存等。

另外,DRAM器件的外围电路还包括本公开实施例提供的存储器读写电路。其中,该存储器读写电路主要包括:激活窗口信号产生模块261、刷新窗口信号产生模块262和控制信号产生模块263;激活窗口信号产生模块261和刷新窗口信号产生模块262分别与控制信号产生模块263相连,激活窗口信号产生模块261用于产生存储块激活窗口信号BANK ACTWindow,刷新窗口信号产生模块262用于产生刷新窗口信号Refresh Window。

对于DRAM器件的外围电路而言,其中的命令解码器210、地址锁存器220分别与激活窗口信号产生模块261连接,用于为激活窗口信号产生模块261提供输入信号,以便于激活窗口信号产生模块261产生存储块激活窗口信号BANK ACT Window。刷新窗口信号产生模块262则与命令解码器210相连,在解码出刷新信号的情况下,产生刷新窗口信号RefreshWindow。

在介绍本公开实施例中的控制信号产生模块263之前,需要对存储器中的存储块BANK的内部结构进行简要说明。参见图3,示出了一种存储块的结构示意图。该存储块300包括:位线BL、互补位线BL_B、若干字线WL及若干存储单元310,该若干存储单元310共用上述的位线BL或互补位线BL_B。另外,位线BL、互补位线BL_B还用于接入写输入驱动INPUTWrite Driver、INPUT_B Write Driver,并输出输出信号OUTPUT、OUTPUT_B。

本公开示例性实施方式中,存储块300还包括:感应模块320和位线平衡模块330,其中,位线平衡模块330用于在位线平衡控制信号BLEQ作用下,捏合位线BL和互补位线BL_B,以达到关闭对存储单元310的读写操作。

参照图3,感应模块320主要包括感应放大器,感应放大器(Sense Amplifier,SA)可以通过位线BL或BL_B对多个存储单元310进行寻址。常规的感应放大器更具体而言是一种差分放大器,差分放大器利用位线BL和用作参考线的互补位线BL_B(作为参考线)来工作,以检测和放大一对位线BL和BL_B上的电压差。

参照图4,感应放大器400中的四个晶体管分别为第一晶体管410、第二晶体管420、第三晶体管430和第四晶体管440,其中,第一晶体管410和第三晶体管430均为PMOS(Positive channel Metal Oxide Semiconductor)晶体管,第二晶体管420和第四晶体管440均为NMOS(Negative channel Metal Oxide Semiconductor,N型金属氧化物半导体)晶体管。如果存储单元310中所存储的数据为1,在进行读操作时,字线WL的电压首先被拉高到Vccp,存储单元310中的晶体管被打开,此时,存储单元310处于读/写激活状态。一对位线BL、BL_B断开电压,在读出1时,位线BL上产生了正向的电压,此电压导致第四晶体管440被导通,使得N节点上的负电压加在了BL_B线和第一晶体管410的栅极上并使其导通。最终,P节点上的Vcc电压就加在了BL线上,从而可以容易且准确地根据一对位线上的电压差是+Vcc,还是-Vcc来判断出存储单元中存储的数据是1还是0。

如图1所示,对于电容器110,当要写入1时,位线BL上会加以电压Vcc,这一电压Vcc会通过导通的晶体管120,由其漏极传导到源极,并最终加载到电容器110的另一极板上。当要写入0时,位线BL上会加以电压0V,从而导致电容器110的另一极板上的电压也为0V。电容器110的写入1或0的过程与之相同。

当电容器110写1或写0时,电容器110极板电压为1或0,写入完成后BL电压回到V

DRAM存储单元在读操作过程中,同样需要在存储单元的字线WL上加以大于晶体管120开启电压的电压,从而打开晶体管120。此时,电容器110上的电荷会通过晶体管120释放到位线BL、BL_B上。

对于本公开实施例提供的存储器读写电路而言,无论是正常读写模式,还是刷新模式,均需要通过感应放大器完成信号的放大。

本公开示例性实施方式提供的存储器读写电路中,控制信号产生模块263用于在同时获取到存储块激活窗口信号BANK ACT Window和刷新窗口信号Refresh Window的时候,控制存储器进入刷新模式;在只获取到激活窗口信号BANK ACT Window的时候,控制存储器进入正常读写模式。

参考图2和图4,在本公开示例性实施方式提供的控制信号产生模块263的控制下,感应放大器400的电源电压可以由第一控制信号SAP1控制供给,也可以由第二控制信号SAP2控制供给。并且,第一控制信号SAP1控制供给的第一电源电压VDD大于第二控制信号SAP2控制供给的第二电源电压VARY。

通过为感应放大器400设置不同大小的电源电压VDD和VARY,在正常读写模式的初始,可以采用更大的第一电源电压VDD进行供电,以减小感应sensing和单元存储cellstorage过程所耗费的时间,从而达到优化行寻址至列寻址延迟时间tRCD及内存行有效至预充电的最短周期tRAS等性能的效果。

在刷新模式下,则可以设置与正常读写模式时不同的电源供给方式。例如,在正常读写模式下,控制产生第一控制信号SAP1的脉冲时长为第一时长,则在正常读写模式下,由第一电源电压VDD供给的时长为第一时长;在刷新模式下,控制产生第一控制信号SAP1的脉冲时长为第二时长,则在刷新模式下,由第一电源电压VDD供给的时长为第二时长。

本公开示例性实施方式中,第二时长小于第一时长。也就是说,在刷新模式下采用第一电源电压VDD供给的时长要小于在正常读写模式下采用第一电源电压VDD供给的时长。如此,在对tRCD性能没有较高要求的刷新模式下,通过减小第一电源电压VDD供给的时长,既能满足刷新的要求,又能减小刷新过程中VDD电流的消耗,避免在刷新模式下产生过大的瞬时电流,也减小了对VDD承载能力设计的要求。

参照图5,示出了存储器在正常读写模式下的控制信号波形图;参照图6,示出了存储器在刷新模式下的控制信号波形图。以时钟信号CLK为基准,对比图5和图6,在刷新模式下第一控制信号SAP1的脉冲时长T2,明显小于在正常读写模式下第一控制信号SAP1的脉冲时长T1,从而可以实现在刷新模式下,减小第一电源电压VDD供给的时长。

本公开示例性实施方式中,控制信号产生模块263还可以用于在刷新模式下,控制存储器中多个存储块的第一控制信号顺次开启。例如,如图7所示,存储器中的16个存储块Bank0-Bank15中,第一控制信号SAP1顺次开启,即第1个存储块Bank0的第一控制信号SAP1开启预设时间后,第2个存储块Bank1的第一控制信号SAP1开启;接着,第3个存储块Bank2的第一控制信号SAP1开启;直到,第16个存储块Bank15的第一控制信号SAP1开启;其中,顺次开启所间隔的预设时间可以根据实际情况设置,本公开示例性实施方式对此不作特殊限定。

通过多个存储块的第一控制信号SAP1顺次开启,可以进一步减小刷新模式下的瞬时电流,提高存储器的VDD承载能力。

甚至还可以如图8所示,在刷新模式下,取消第一控制信号SAP1的控制,将第一控制信号SAP1的脉冲时长,即第二时长设置为0。此种情况下,在刷新模式时,不产生第一控制信号SAP1,直接产生第二控制信号SAP2,即不会使用第一电源电压VDD对感应放大器400进行供给,而直接使用第二电源电压VARY进行供给。从而可以更进一步地减小存储器在刷新模式下的瞬时电流,更进一步地提高存储器的VDD承载能力。

另外,还可以通过控制信号产生模块263,控制只有第二控制信号的多个存储块的第二控制信号SAP2顺次开启,例如,参照图7中的方式将16个存储块Bank0-Bank15的第二控制信号SAP2间隔开启,从而可以在图8的基础上,更进一步地减小刷新模式下的瞬时电流,提高存储器的VDD承载能力。

在实际应用中,第一电源电压VDD可以是1.2-1.3V,例如1.25V,第二电源电压VARY可以是0.9-1.1V,例如1V。本公开示例性实施方式对于第一电源电压VDD和第二电源电压VARY的具体取值不作特殊限定。

需要说明的是,图5-图8中的PRE代表的是预充电命令,在该预充电命令下,读写结束,进入对存储单元的电容预充电过程。

本公开示例性实施方式中,上述控制信号产生模块263还用于在正常读写模式或刷新模式下,控制第一控制信号SAP1终止时,产生第二控制信号SAP2,并且第二控制信号SAP2的脉冲时长要大于第一控制信号SAP1的脉冲时长。也就是说,无论是在正常读写模式下,还是在刷新模式下,第一电源电压VDD只是在初始阶段时使用,在后续的大部分读写或刷新过程中,存储器的电源电压还是由第二电源电压VARY所供给的。而在初始设置第一电源电压VDD主要是为了减小延迟,提高存储器读写性能。

本公开示例性实施方式中,如图4所示,感应放大器400的负极电压则由负极控制信号SAN控制供给。参照图5和图6可以看出,控制信号产生模块263还用于在产生第一控制信号SAP1之后,控制产生负极控制信号SAN;参照图8可以看出,控制信号产生模块263还用于在产生第二控制信号SAP2之后,控制产生负极控制信号SAN。

如图2所示,本公开实施例提供的控制信号产生模块263除了控制产生第一控制信号SAP1、第二控制信号SAP2和负极控制信号SAN之外,还控制产生位线平衡控制信号BLEQB和字线开启电压SWL。控制信号产生模块263还用于,在产生第一控制信号SAP1和第二控制信号SAP2之前,关闭施加在位线BL和互补位线BL_B上的位线平衡控制信号BLEQ,以将捏合的位线BL和互补位线BL_B分开(即图中的BLT和BLB打开),从而进入对存储单元310的读写操作;接着,在字线上施加字线开启电压SWL,以将与字线连接的晶体管打开,与晶体管连接的电容上的电压通过电荷分享释放到位线BL上,从而产生电压差。接下来,由感应放大器400对上述电压差进行放大,即产生第一电源电压SAP1、第二电源电压SAP2,及负极控制信号SAN。在读写过程快结束的时候,关闭字线开启电压SWL,同时,产生位线平衡控制信号BLEQB,以捏合位线BL和互补位线BL_B(即图中的BLT和BLB电压相等),以关闭对存储单元310的读写操作,完成正常读写过程或刷新过程。

本公开示例性实施方式中,在减小存储器在刷新模式下的瞬时电流的过程中,除了上述的各种方式之外,还可以通过控制信号产生模块263在刷新模式下,控制多个存储块的字线开启电压SWL顺次开启。如图9所示,存储器中的16个存储块Bank0-Bank15中,字线开启电压SWL顺次开启,即第1个存储块Bank0的字线开启电压SWL开启预设时间后,第2个存储块Bank1的字线开启电压SWL开启;接着,第3个存储块Bank2的字线开启电压SWL开启;直到,第16个存储块Bank15的字线开启电压SWL开启;其中,顺次开启所间隔的预设时间可以根据实际情况设置,本公开示例性实施方式对此不作特殊限定。通过多个存储块的字线开启电压SWL顺次开启,可以进一步减小刷新模式下的瞬时电流,提高存储器的VDD承载能力。

参照图10,本公开示例性实施方式提供了一种存储器读写电路中的控制信号产生模块的电路结构。图10中,控制信号产生模块包括:第一延时子模块1010、第二延时子模块1020和第一与非门1030;其中,第一与非门1030的输入端接入第一延时子模块1010的输出端和第二延时子模块1020的输出端,第一与非门1030的输出端输出第一控制信号SAP1。

第二延时子模块1020的输入端与第一延时子模块1010的输出端相连,第一延时子模块1010的输入端接入存储块激活窗口信号BANK ACT Window或者接入存储块激活窗口信号BANK ACT Window的延迟信号,第二延时子模块1020的输出端输出第二控制信号SAP2。

本公开示例性实施方式中,第一延时子模块1010包括第一延时单元1011和第二与非门1012;其中,第二与非门1012的输入端接入第一延时单元1011的输出端和存储块激活窗口信号BANK ACT Window,第一延时单元1011的输入端接入存储块激活窗口信号BANKACT Window。

参照图11所示,第一延时单元1011包括:第一多路选择器1110、第一延时器件1120、第二延时器件1130和第一延时选择单元1140;其中,第一延时器件1120和第二延时器件1130分别用于延迟存储块激活窗口信号BANK ACT Window,第一延时器件1120的延迟时长大于第二延时器件1130的延迟时长;第二延时器件1130的输出端与第一延时选择单元1140的输入端相连,第一延时器件1120的输出端和第一延时选择单元1140的输出端分别与第一多路选择器1110的输入端相连,第一延时选择单元1140的输入端还接入存储块激活窗口信号BANK ACT Window,第一延时选择单元1140的控制端接入第一测试信号TM1。在产生第一测试信号TM1的时候,第一延时选择单元1140直接输出存储块激活窗口信号BANK ACTWindow。

并且第一多路选择器1110的控制端接入刷新窗口信号Refresh Window,用于在产生刷新窗口信号Refresh Window时,选择输出第一延时选择单元1140的输出信号,在没有产生刷新窗口信号时,选择输出第一延时器件1120的延迟信号。如此,在产生刷新窗口信号Refresh Window时,如果没有产生第一测试信号TM1,则第一延时选择单元1140选择输出的第二延时器件1130的延迟信号延迟时长较短,相比于正常刷新模式下,可以获得脉冲时长较短的第一控制信号SAP1;如果产生了第一测试信号TM1,则第一延时选择单元1140选择输出的是存储块激活窗口信号BANK ACT Window,第一多路选择器1110在刷新窗口信号Refresh Window控制下,输出的也是存储块激活窗口信号BANK ACT Window。两个存储块激活窗口信号BANK ACT Window经过第二与非门1012之后,不会产生脉冲信号,因此,在第一测试信号TM1的作用下,可以起到关闭第一控制信号SAP1,即不会产生第一控制信号SAP1,只会产生第二控制信号SAP2,从而达到直接产生第二控制信号SAP2的目的。此处的第一延时选择单元114可以是一个多路选择器。

参照图10所示,第二延时子模块1020包括第二延时单元1021和第一与门1022;其中,第一与门1022的输入端与第二延时单元1021的输出端和第一延时子模块1010的输出端分别相连,第二延时单元1021的输入端与第一延时子模块1010的输出端相连。

参照图12,本公开示例性实施方式中,第二延时单元1021包括:第三延时器件1210、第二延时选择单元1245和第二多路选择器1220;其中,第三延时器件1210用于延迟第一延时子模块1010的输出信号,第二延时选择单元1245的输入端接入第一延时子模块1010的输出信号,第二延时选择单元1245的输出端与第二多路选择器1220的输入端相连;第二多路选择器1220的控制端接入刷新窗口信号Refresh Window,第二多路选择器1220用于在产生刷新窗口信号Refresh Window时,选择输出第二延时选择单元1245的输出信号,在没有产生刷新窗口信号时,选择输出第三延时器件1210的输出信号。

其中,第二延时选择单元1245包括:第二子延时单元1230、第三子延时单元1240和第二子多路选择器1250;其中,第二子延时单元1230的输入端接入第一延时子模块1010的输出信号,第三子延时单元1240的输入端接入第二子延时单元1230的输出信号,第二子多路选择器1250的输入端接入第二子延时单元1230的输出信号和第三子延时单元1240的输出信号,第二子多路选择器1250的控制端接入第二测试信号TM2,在第二测试信号TM2作用下,控制存储器中多个存储块的第一控制信号SAP1顺次开启,或控制多个存储块的第二控制信号SAP2顺次开启。

参照图10所示,控制信号产生模块还包括:位线平衡控制信号产生子模块1040、字线开启电压产生子模块1050和第三延时子模块1060;其中,位线平衡控制信号产生子模块1040的输入端接入存储块激活窗口信号BANK ACT Window,位线平衡控制信号产生子模块1040的输出端输出位线平衡控制信号BLEQ;字线开启电压产生子模块1050的输入端与第三延时子模块1060的输出端相连,字线开启电压产生子模块1050的输出端输出字线开启电压SWL,第三延时子模块的输入端接入存储块激活窗口信号BANK ACT Window。

在产生存储块激活窗口信号BANK ACT Window之后,无论是正常读写模式,还是刷新模式,均需要产生字线开启电压SWL。作为一种示例,如图10所示,字线开启电压SWL包括多个延时单元、多个与非门和多个反相器,其中具体的连接方式此处不再赘述。由于在产生字线开启电压SWL之前,需要关闭位线平衡控制信号BLEQ,因此,与位线平衡控制信号产生子模块1040相比,字线开启电压产生子模块1050多设置了一个延迟单元。

另外,与字线开启电压产生子模块1050相比,位线平衡控制信号产生子模块1040在输出端设置了一个反相器,以达到将产生的位线平衡控制信号BLEQ关闭的目的。

在实际应用中,用于构成位线平衡控制信号产生子模块1040、字线开启电压产生子模块1050的电路连接方式可以有多种,本公开示例性实施方式并不以图10为限。

本公开示例性实施方式中,第三延时子模块1060包括第三延时单元1061和第二与门1062;其中,第二与门1062的输入端接入第三延时单元1061的输出信号和存储块激活窗口信号BANK ACT Window,第三延时单元1061的输入端接入存储块激活窗口信号BANK ACTWindow。

参照图13,本公开示例性实施方式中,第三延时单元1061包括:第三多路选择器1310、第四延时器件1320、第五延时器件1330和第三延时选择单元1345;其中,第四延时器件1320和第五延时器件1330分别用于延迟存储块激活窗口信号BANK ACT Window,第四延时器件1320的延迟时长大于第五延时器件1330的延迟时长,第五延时器件1330的输出端与第三延时选择单元1345的输入端相连,第四延时器件1320的输出端和第三延时选择单元1345的输出端分别与第三多路选择器1310的输入端相连;第三多路选择器1310的控制端接入刷新窗口信号Refresh Window,用于在产生刷新窗口信号Refresh Window时,选择输出第三延时选择单元1345的输出信号,在没有产生刷新窗口信号Refresh Window时,选择输出第四延时器件1320的延迟信号。

参照图13,第三延时选择单元1345包括:第四子延时单元1340和第三子多路选择器1350;其中,第四子延时单元1340的输入端接入第五延时器件1330的输出信号,第三子多路选择器1350的输入端接入第五延时器件1330的输出信号和第四子延时单元1340的输出信号,第三子多路选择器1350的控制端接入第三测试信号TM3;不同的存储阵列,对应的第四子延时单元1340的延时长度不同,从而可以在刷新模式下,控制多个存储块的字线开启电压SWL顺次开启。

综上,本公开示例性实施方式通过设置在刷新模式下产生的第一控制信号的脉冲时长小于在正常读写模式下产生的第一控制信号的脉冲时长,则在刷新模式下采用较大的第一电源电压VDD供给的时长会小于在正常读写模式下采用较大的第一电源电压VDD供给的时长。通过在刷新模式下减小第一电源电压VDD供给的时长,既能满足对tRCD性能没有较高要求的刷新需求,又能减小刷新过程中第一电源电压VDD电流的消耗,进而减小在刷新模式下产生过大的瞬时电流的概率,也减小了对第一电源电压VDD承载能力设计的要求。另外,通过在刷新模式下,控制多个存储块的第一控制信号顺次开启,可以进一步减小刷新模式下的瞬时电流,提高存储器的VDD承载能力。

需要说明的是,尽管在附图中以特定顺序描述了本发明中方法的各个步骤,但是,这并非要求或者暗示必须按照该特定顺序来执行这些步骤,或是必须执行全部所示的步骤才能实现期望的结果。附加的或备选的,可以省略某些步骤,将多个步骤合并为一个步骤执行,以及/或者将一个步骤分解为多个步骤执行等。

此外,在本示例实施例中,还提供了一种存储器控制方法。该存储器控制方法用于控制的存储器,包括前述的感应放大器,其中,感应放大器的电源电压由第一控制信号SAP1或第二控制信号SAP2控制供给,第一控制信号SAP1控制供给的电源电压VDD大于第二控制信号SAP2控制供给的电源电压VARY。

参照图14,该存储器控制方法包括以下步骤:

步骤S1410,在正常读写模式下,控制产生第一控制信号的脉冲时长为第一时长;

步骤S1420,在刷新模式下,控制产生第一控制信号的脉冲时长为第二时长,第二时长小于第一时长;

步骤S1430,在刷新模式下,控制存储器中多个存储块的第一控制信号顺次开启。

在本公开的一种示例性实施方式中,在正常读写模式或刷新模式下,控制第一控制信号终止时,产生第二控制信号。

在本公开的一种示例性实施方式中,存储器控制方法还包括:在正常读写模式或刷新模式下,控制产生第二控制信号的脉冲时长大于产生第一控制信号的脉冲时长。

在本公开的一种示例性实施方式中,第二时长为0。

在本公开的一种示例性实施方式中,存储器控制方法还包括:在刷新模式下,不产生第一控制信号,直接产生第二控制信号;并控制多个存储块的第二控制信号顺次开启。

在本公开的一种示例性实施方式中,感应放大器的负极电压由负极控制信号SAN控制供给,存储器控制方法还包括:在产生第一控制信号或第二控制信号后,控制产生负极控制信号。

在本公开的一种示例性实施方式中,方法还包括:在刷新模式下,控制多个存储阵列的字线开启电压顺次开启。

在本公开的一种示例性实施方式中,存储器还包括:字线、位线和互补位线,感应放大器设置在位线和互补位线之间;在产生第一控制信号或第二控制信号之前,存储器控制方法还包括:关闭施加在位线和互补位线上的位线平衡控制信号BLEQ;在字线上施加字线开启电压SWL,以将与字线连接的晶体管打开。

在本公开的一种示例性实施方式中,存储器控制方法还包括:在同时获取到激活窗口信号BANK ACT Window和刷新窗口信号Refresh Window的时候,控制存储器进入刷新模式;在只获取到激活窗口信号BANK ACT Window的时候,控制存储器进入正常读写模式。

上述中存储器控制方法的具体细节已经在对应的存储器读写电路中进行了详细的描述,因此此处不再赘述。

在本公开的示例性实施例还提供了一种电子设备,该电子设备可以包括:多个阵列、多个阵列控制器,和多个上述的存储器读写电路;其中,上述存储器读写电路设置在阵列控制器中,一个存储器读写电路对应控制一个阵列。其中,存储器读写电路的具体结构细节已经在上述实施方式中进行了详细说明,此处不再赘述。

在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件程序实现时,可以全部或部分地以计算机程序产品的形式来实现。该计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行计算机程序指令时,全部或部分地产生按照本公开实施例所述的流程或功能。所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。所述计算机指令可以存储在计算机可读存储介质中,或者从一个计算机可读存储介质向另一个计算机可读存储介质传输。所述计算机可读存储介质可以是计算机能够存取的任何可用介质或者是包含一个或多个可以用介质集成的服务器、数据中心等数据存储设备。所述可用介质可以是磁性介质(例如,软盘、硬盘、磁带),光介质(例如,DVD)、或者半导体介质(例如固态硬盘(solid state disk,SSD))等。本公开实施例中,计算机可以包括前面所述的装置。

尽管在此结合各实施例对本公开进行了描述,然而,在实施所要求保护的本公开过程中,本领域技术人员通过查看所述附图、公开内容、以及所附权利要求书,可理解并实现所述公开实施例的其他变化。在权利要求中,“包括”(comprising)一词不排除其他组成部分或步骤,“一”或“一个”不排除多个的情况。单个处理器或其他单元可以实现权利要求中列举的若干项功能。相互不同的从属权利要求中记载了某些措施,但这并不表示这些措施不能组合起来产生良好的效果。

尽管结合具体特征及其实施例对本公开进行了描述,显而易见的,在不脱离本公开的精神和范围的情况下,可对其进行各种修改和组合。相应地,本说明书和附图仅仅是所附权利要求所界定的本公开的示例性说明,且视为已覆盖本公开范围内的任意和所有修改、变化、组合或等同物。显然,本领域的技术人员可以对本公开进行各种改动和变型而不脱离本公开的精神和范围。这样,倘若本公开的这些修改和变型属于本公开权利要求及其等同技术的范围之内,则本公开也意图包含这些改动和变型在内。

- 存储器管理方法、存储器控制电路单元与存储器存储装置

- 存储器控制电路单元、存储器存储装置及其控制方法

- 解码方法、存储器存储装置及存储器控制电路单元

- 数据存储方法、存储器存储装置及存储器控制电路单元

- 数据存储方法、存储器控制电路单元及存储器存储装置

- 灵敏放大器及其控制方法、存储器读写电路以及存储器

- 动态随机存取存储器电路、集成电路与读写存储器单元方法