一种输出失调自校准的高增益低功耗比较器

文献发布时间:2023-06-29 06:30:04

技术领域

本发明涉及混合信号集成电路技术领域,尤其涉及一种输出失调自校准的高增益低功耗比较器和模数转换器。

背景技术

随着半导体加工工艺的不断发展,集成电路已发展到“后摩尔时代”,器件性能得到大幅提升,混合信号集成电路的性能也随之不断迭代升级。比较器作为模数转换器电路的核心模块,其比较精度受到失调误差的限制,进而限制了模数转换器的发展。

如图1和图2所示,传统比较器通常采用预放大器级联锁存器的结构,利用预放大器的高增益特点降低锁存器固有失调的影响,再利用输入失调存储和输出失调存储技术,通过耦合电容实现预放大器失调的存储,并在不同工作相位实现失调校准,而引入耦合电容增加了电路负载,会降低比较器的运算速度。

输入失调存储技术通常要求耦合电容值较大,同时对电路闭环稳定性要求较高,且易受时钟馈通效应影响;输出失调存储技术要对放大后的失调误差进行存储,为保证预放大器输出不饱和,故要求其增益不能过高,但这也限制了预放大器对锁存器固有失调的抑制能力。

发明内容

本发明的目的是:克服已有技术的不足之处,提出一种输出失调自校准的高增益低功耗比较器,在不明显增加功耗的基础上,提高比较器增益,有效降低比较器失调误差,节省芯片面积,能够满足高精度低功耗模数转换器的设计需求。

本发明采用的技术方案为:

一种输出失调自校准的高增益低功耗比较器,包括采样开关、预放大器、输出失调自校准单元和输出动态锁存器;

比较器工作相位分为采样共模信号相位和采样输入信号运算相位;在采样共模信号相位,采样开关采样共模信号VCM并传输至预放大器输入端,此时预放大器对失调误差信号进行放大,并将放大后的结果传输至输出失调自校准单元和输出动态锁存器,输出失调自校准单元完成失调误差存储,输出动态锁存器输出复位;

在采样输入信号运算相位,采样开关采样差分输入信号VINP和VINN并传输至预放大器输入端,此时预放大器对差分输入信号进行放大,并将放大后的结果传输至输出失调自校准单元和输出动态锁存器,输出失调自校准单元完成失调误差自校准,输出动态锁存器更新输出结果。

进一步的,所述的采样开关为差分结构,包括输入信号采样开关SW1、SW2、共模信号采样开关SW3、SW4和SW11;分别记为第一开关SW1、第二开关SW2、第三开关SW3、第四开关SW4和第十一开关SW11;

第一开关SW1的第一端与正输入信号VINP相连,第一开关SW1的第二端同时与预放大器的正输入端、第三开关SW3的第一端和第十一开关SW11的第二端相连;第二开关SW2的第一端与负输入信号VINN相连,第二开关SW2的第二端同时与预放大器的负输入端、第四开关SW4的第一端和第十一开关SW11的第一端相连;第三开关SW3和第四开关SW4的第二端同时与共模信号VCM相连。

进一步的,共模信号采样开关SW3、SW4、SW11与输入信号采样开关SW1、SW2工作在不交叠的时钟相位。

进一步的,所述的输出失调自校准单元包括第一失调存储电容C1、第五开关SW5、第六开关SW6、第九开关SW9、第九NMOS晶体管M9、第二失调存储电容C2、第七开关SW7、第八开关SW8、第十开关SW10和第十NMOS晶体管M10;

第一失调存储电容C1的第一端与GND相连,第二端同时与第九NMOS晶体管M9的栅极和第六开关SW6的第一端相连;第九NMOS晶体管M9的衬底和源极均与GND相连,漏极同时与预放大器的负输出端和第五开关SW5的第一端相连;第五开关SW5的第二端同时与第六开关SW6的第二端和第九开关SW9的第一端相连;第九开关SW9的第二端与VDD相连;第二失调存储电容C2的第一端与GND相连,第二端同时与第十NMOS晶体管M10的栅极和第八开关SW8的第一端相连;第十NMOS晶体管M10的衬底和源极均与GND相连,漏极与预放大器的正输出端和第七开关SW7的第一端相连;第七开关SW7的第二端同时与第八开关SW8的第二端和第十开关SW10的第一端相连;第十开关SW10的第二端与VDD相连。

进一步的,第五开关SW5、第六开关SW6、第七开关SW7和第八开关SW8与共模信号采样开关SW3、SW4和SW5工作在相同相位,使能期间完成比较器失调误差的存储;

第9开关SW9和第十开关SW10工作在与共模信号采样开关SW3、SW4和SW5不交叠的反相相位,保证输出失调误差的快速存储,提高比较器信号建立速度。

进一步的,所述的输出动态锁存器包括复位开关SW12和锁存器LATCH,复位开关SW12记为第十二开关SW12;

第十二开关SW12的第一端同时与预放大器的正输出端、第十NMOS晶体管M10的漏极、第七开关SW7的第一端和锁存器LATCH的VN端相连;第十二开关SW12的第二端同时与预放大器的负输出端、第九NMOS晶体管M9的漏极、第五开关SW5的第一端和锁存器LATCH的VP端相连;锁存器LATCH的输出端与DOUT相连。

进一步的,第十二开关SW12在采样共模信号相位初始脉冲阶段进行复位清零。

进一步的,预放大器可以设计为多级预放大器级联的比较器结构,并在每级预放大器输出端设计匹配的输出失调自校准单元。

进一步的,所述比较器包括采样共模信号相位和采样输入信号运算相位,两个相位的时钟为不交叠时钟;

当比较器工作在采样共模信号相位时,第三开关SW3、第四开关SW4和第十一开关SW11首先闭合,预放大器的正输入端和负输入端短接并连接至共模信号VCM;

第十二开关SW12在采样共模信号相位初始脉冲阶段复位,复位预放大器的正输出端和负输出端,同时复位锁存器LATCH;

第六开关SW6和第八开关SW8在第十二开关SW12复位之后早于第五开关SW5和第七开关SW7闭合,失调存储电容C1和C2在第五开关SW5、第六开关SW6、第七开关SW7和第八开关SW8闭合期间实现失调误差充电计算;

随后,第六开关SW6和第八开关SW8早于第五开关SW5和第七开关SW7断开,完成比较器失调误差的准确存储。

进一步的,当比较器工作在采样输入信号运算相位时,第一开关SW1和第二开关SW2闭合,正输入信号VINP通过第一开关SW1连接至预放大器的正输入端,负输入信号VINN通过第二开关SW2连接至预放大器的负输入端,此时预放大器对正输入信号VINP和负输入信号VINN的差值进行放大,预放大器负输出端的失调误差通过失调存储电容C1及与其相连的NMOS晶体管M9所构成的通路泄放,预放大器正输出端的失调误差通过失调存储电容C2及与其相连的NMOS晶体管M10所构成的通路泄放,实现输出失调自校准,此时预放大器的差分输出信号再通过锁存器LATCH运算得到与比较器差分输入信号VINP-VINN对应的比较结果DOUT。

进一步的,当比较器工作在采样输入信号运算相位时,第九开关SW9和第十开关SW10处于闭合状态,将电源信号VDD传输至第九开关SW9和第十开关SW10的第一端,加快失调存储电容C1和C2的失调电压建立速度。

本发明与现有技术相比具有以下几个明显的优点:

(1)本发明在传统比较器结构上,采用了一种输出失调自校准单元,通过开关、电容和NMOS晶体管匹配实现失调误差的存储和校准,减小比较器失调误差。

(2)本发明由于采用了一种输出失调自校准单元电路,不需要额外引入耦合电容,在保证比较器转换速度的同时使得比较器可以保持较高增益,这大大降低了比较器失调误差的影响,同时也降低了电路的功耗、面积和实现复杂度。

(3)本发明采用的输出失调自校准单元,可根据系统需求设计多级预放大器级联的比较器结构,并在每级预放大器输出端设计匹配的输出失调自校准单元,技术可移植性强。

(4)本发明可根据不同模数转换器架构需求设计匹配的时序信号,设计空间大。

附图说明

图1为传统比较器拓扑结构示意图;

图2为现有的采用输入失调存储技术和输出失调存储技术的比较器拓扑结构示意图;

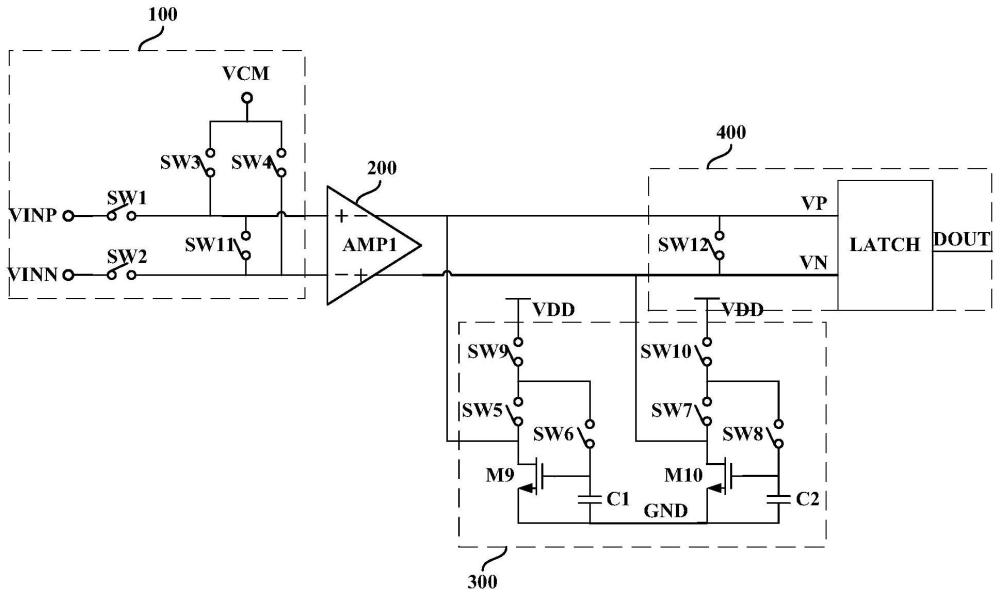

图3为本发明输出失调自校准高增益低功耗比较器拓扑结构示意图;

图4为本发明比较器的工作时序示意图;

图5为本发明比较器采样共模信号相位电路示意图;

图6位本发明比较器采样输入信号运算相位电路示意图。

具体实施方式

本发明提出的一种输出失调自校准高增益低功耗比较器结合附图及实施例详细说明如下。

本发明提出的一种输出失调自校准的高增益低功耗比较器如图3所示,其特征在于:包括采样开关100、预放大器200、输出失调自校准单元300、输出动态锁存器400,各部分的具体电路结构和连接关系说明如下。

采样开关100为差分结构,包括输入信号采样开关SW1和SW2以及共模信号采样开关SW3、SW4和SW11,其中,第一开关SW1的第一端与正输入信号VINP相连,第二端同时与预放大器200的正输入端、第三开关SW3的第一端和第十一开关SW11的第二端相连;第二开关SW2的第一端与负输入信号VINN相连,第二端同时与预放大器200的负输入端、第四开关SW4的第一端和第十一开关SW11的第一端相连;第三开关SW3和第四开关SW4的第二端同时与共模信号VCM相连。

预放大器200采用全差分结构,具有差分输入端和差分输出端。

输出失调自校准单元300由第一失调存储电容C1、第五开关SW5、第六开关SW6、第九开关SW9、第九NMOS晶体管M9和第二失调存储电容C2、第七开关SW7、第八开关SW8、第十开关SW10、第十NMOS晶体管M10组成,其中,第一失调存储电容C1的第一端与GND相连,第二端同时与第九NMOS晶体管M9的栅极和第六开关SW6的第一端相连;第九NMOS晶体管M9的衬底和源极均与GND相连,漏极同时与预放大器200的负输出端和第五开关SW5的第一端相连;第五开关SW5的第二端同时与第六开关SW6的第二端和第九开关SW9的第一端相连;第九开关SW9的第二端与VDD相连;第二失调存储电容C2的第一端与GND相连,第二端同时与第十NMOS晶体管M10的栅极和第八开关SW8的第一端相连;第十NMOS晶体管M10的衬底和源极均与GND相连,漏极与预放大器200的正输出端和第七开关SW7的第一端相连;第七开关SW7的第二端同时与第八开关SW8的第二端和第十开关SW10的第一端相连;第十开关SW10的第二端与VDD相连。

输出动态锁存器400包括复位开关SW12和锁存器LATCH,其中,第十二开关SW12的第一端同时与预放大器200的正输出端、第十NMOS晶体管M10的漏极、第七开关SW7的第一端和锁存器LATCH的VN端相连,第十二开关SW12的第二端同时与预放大器200的负输出端、第九NMOS晶体管M9的漏极、第五开关SW5的第一端和锁存器LATCH的VP端相连;锁存器LATCH的输出端与DOUT相连。

本发明比较器的工作时序如图4所示,主要包括采样共模信号相位和采样输入信号运算相位,其中,两个相位的时钟为不交叠时钟。

具体的,比较器工作在采样共模信号相位时电路示意图如图5所示,第三开关SW3、第四开关SW4和第十一开关SW11首先闭合,预放大器200的正输入端和负输入端短接并连接至共模信号VCM;第十二开关SW12在采样共模信号相位初始脉冲阶段复位,复位预放大器200的正输出端和负输出端,同时复位锁存器LATCH;第六开关SW6和第八开关SW8在第十二开关SW12复位之后早于第五开关SW5和第七开关SW7闭合,失调存储电容C1和C2在第五开关SW5、第六开关SW6、第七开关SW7和第八开关SW8闭合期间实现失调误差充电计算;随后,第六开关SW6和第八开关SW8早于第五开关SW5和第七开关SW7断开,完成比较器失调误差的准确存储。

比较器工作在采样输入信号运算相位时电路示意图如图6所示,第一开关SW1和第二开关SW2闭合,正输入信号VINP通过第一开关SW1连接至预放大器200的正输入端,负输入信号VINN通过第二开关SW2连接至预放大器200的负输入端,此时预放大器200对正输入信号VINP和负输入信号VINN的差值进行放大,预放大器200负输出端的失调误差通过失调存储电容C1及与其相连的NMOS晶体管M9所构成的通路泄放,预放大器200正输出端的失调误差通过失调存储电容C2及与其相连的NMOS晶体管M10所构成的通路泄放,实现输出失调自校准,此时预放大器200的差分输出信号再通过锁存器LATCH运算得到与比较器差分输入信号VINP-VINN对应的比较结果DOUT。

此外,当比较器工作在采样输入信号运算相位时,第九开关SW9和第十开关SW10处于闭合状态,将电源信号VDD传输至第九开关SW9和第十开关SW10的第一端,有效加快失调存储电容C1和C2的失调电压建立速度。

本发明说明书中未作详细描述的内容属本领域专业技术人员的公知技术。虽然结合附图描述了本发明的实施方式,但是本领域普通技术人员可以在所附权利要求的范围内做出各种变形或修改。

- 一种动态比较器失调电压校准方法

- 一种应用于16位低功耗逐次逼近型模数转换器的比较器失调电压校准方法

- 一种应用于16位低功耗逐次逼近型模数转换器的比较器失调电压校准方法