一种基于载网结构的原位力学测试芯片及制备方法

文献发布时间:2023-06-19 12:18:04

技术领域

本发明涉及微电子机械技术领域,具体来说,涉及一种基于载网结构的原位力学测试芯片及制备方法。

背景技术

过去的几十年,人们对二维纳米材料的机械力学性能产生了极大的兴趣,石墨烯、氧化石墨烯、二硫化钼等二维材料是重要的基础研究方向,这是由于它们有异于体块材料的特殊性能以及拥有独特且可定制的物理性能的潜力,包括能量收集和存储、纳米机电系统(NEMS)、柔性电子学和可拉伸电子学在内的各种纳米技术应用。此外,当材料特征尺寸降至微纳米量级时,其力学性能与宏观体材料具有显着不同,并且纳米材料的力学性能与其微纳米尺度的变形机制密切相关。因此,发展一种可以实现TEM/SEM电镜下,能够原位观察在亚埃、原子或纳米尺度下研究材料的显微结构随静、动态力学参数变化,对于提高微纳电子器件的可靠性,促进相关领域的发展具有十分重要的意义。

在厚度方向形变时,由于原子尺度的厚度,二维材料在pN量级的作用力下就显示出非线性特征,但非线性响应与材料特性之间的确切关系仍然难以捉摸,因此对二维材料在厚度方向加载力使之运动,进行非线性动态特性研究是极为重要的力学领域。另外,相较于一维材料,二维材料向测试芯片功能区域的转移技术也是一个巨大挑战,由此器件测试功能区域的结构设计对于力学测试芯片也极为重要。

发明内容

技术问题:本发明所要解决的技术问题是:提出一种基于载网结构的原位力学测试芯片,用于研究单轴拉伸下的静-动态力学分析和非线性响应与材料特性之间的关系,并降低二维材料样品的转移难度,以此对二维材料的机械特性进行非线性高频表征及实现纳米级谐振器的功能研究,提高实用化的多功能原位测试芯片。

技术方案:为解决上述技术问题,本发明设计了一种基于载网结构的原位力学测试芯片,所述测试芯片为轴对称结构,包括硅衬底、位于硅衬底上表面的扩散层、悬浮在扩散层上的悬浮块和承载膜、位于悬浮块四周的悬浮块锚点区、位于悬浮块锚点区表面的上电极引线压焊块、以及位于扩散层上的下电极引线压焊块;

所述扩散层包括位于悬浮块和承载膜下方的扩散层下极板区、与下电极引线压焊块连接的扩散层电极引线区、连接扩散层下极板区与下电极引线区的导电通道;

悬浮在扩散层上的悬浮块和承载膜作为上极板区,与扩散层下极板区共同构成平行板电容执行器;承载膜上表面设置有绝缘层,承载膜下方具有硅衬底掏空结构。

进一步的,所述悬浮块、承载膜、悬浮块锚点区厚度相同,且位于同一平面上,悬浮块是正方形结构,承载膜位于悬浮块的中心位置,悬浮块锚点区位于悬浮块的四周,悬浮块锚点区通过悬浮块锚点固定区与硅衬底固定连接。

有益效果:与现有技术相比,本发明具有以下有益效果:

1.驱动结构是悬浮块与衬底所构成的平行板电容执行器,可以使二维材料在芯片厚度方向上运动,实现单轴拉伸下的静-动态力学分析与非线性动态特性表征。有别于现有原位测试芯片一般为热V形梁结构,或者静电梳齿结构作为驱动结构,实现的是样品材料水平方向拉伸运动。

2.现有原位测试芯片技术中,样品转移到测试芯片,并悬空于样品台上一直是一个技术难点,不同于一维材料的转移只需要端点处固定,二维材料需要更多的接触面积才能实现其牢固固定在测试芯片的样品台上。本发明提出在惯常的悬空样品台上设计承载膜,为满足样品的悬空,把承载膜设计为凹角蜂窝结构,这样一方面可以增加二维材料在样品台面上的接触面积,降低样品转移的难度;另一方面,承载膜中每一个凹角结构单元都是一个悬空台,可以实现样品的悬空,并通过对凹角蜂窝结构的调控实现样品单轴拉伸,实现二维材料力学参数(杨氏模量、预应力)的非线性动态表征;二维材料纳机电谐振研究;二维材料单轴拉伸下的静-动态力学分析(应变、应力、蠕变、疲劳特性);二维材料的可靠性及失效分析。

在测试力学参数(应变、应力、疲劳特性等)的同时,可以通过TEM/SEM电镜对二维材料的表面形貌或原子精细结构进行在线分析,得到二维材料的多参数与材料的形貌或原子精细结构之间的微观构建关系规律。

3.该芯片测试环境不局限于TEM/SEM电镜下,还可用于AFM,Raman、激光干涉仪等测试环境中。

附图说明

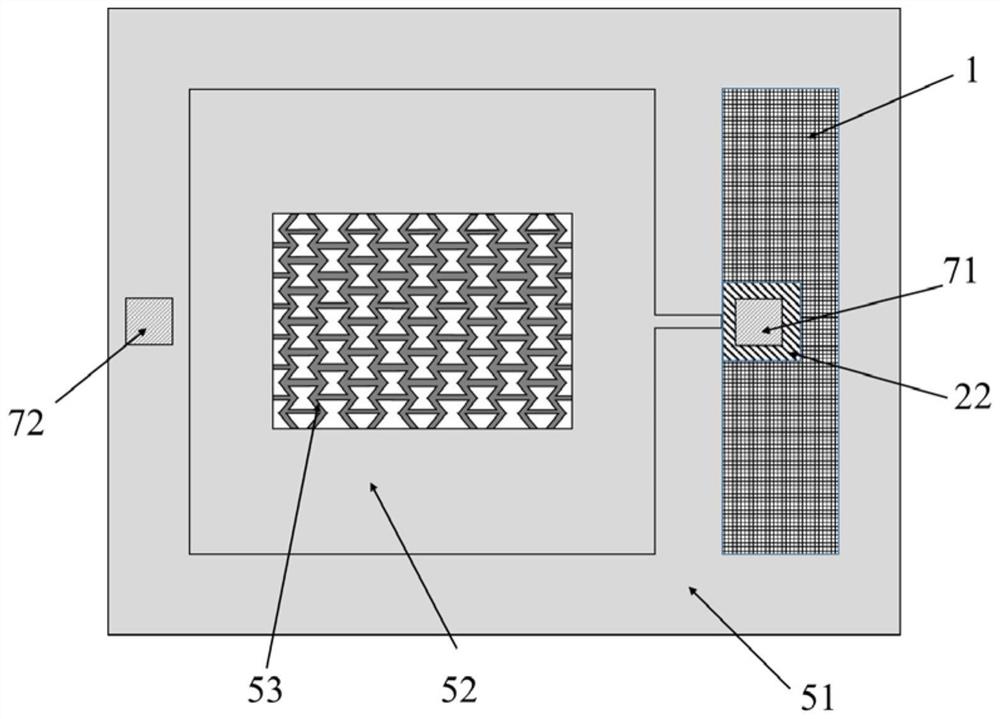

图1为本发明实施例中测试芯片结构示意图;

图2为本发明实施例中制备方法第一步的结构剖视图;

图3是本发明实施例中制备方法第二步的结构剖视图;

图4是本发明实施例中制备方法第三步的结构剖视图;

图5是本发明实施例中制备方法第四步的结构剖视图;

图6是本发明实施例中制备方法第五步的结构剖视图;

图7是本发明实施例中制备方法第六步的结构剖视图;

图8是本发明实施例中制备方法第七步的结构剖视图;

图9是本发明实施例中制备方法第八步的结构剖视图;

图10是本发明实施例中制备方法第九步的结构剖视图;

图11是本发明实施例中制备方法第十步的结构剖视图;

图12是本发明实施例中制备方法第十一步的结构剖视图;

图13是本发明扩散层的结构图;

图14是凹角结构单元力学理论模型示意图;

图15是四分之一凹角结构单元受力力学理论分析示意图。

图中:1、硅衬底;2、扩散层;21、扩散层下极板区;22、扩散层电极引线区;23、导电通道;3、牺牲层;4、悬浮块锚点固定区;5、结构层;51、悬浮块锚点区;52、悬浮块;53、承载膜;6、绝缘层;72、上电极引线压焊块;71、下电极引线压焊块;8、衬底掏空结构。

具体实施方式

下面结合附图,对本发明的技术方案进行详细的说明。

如图1所示,本发明实施例提供一种基于载网结构的原位力学测试芯片,所述测试芯片为轴对称结构,硅衬底1、位于硅衬底1上表面的扩散层2、悬浮在扩散层2上的悬浮块52和承载膜53、位于悬浮块52四周的悬浮块锚点区51、位于悬浮块锚点区51表面的上电极引线压焊块72、位于扩散层2上的下电极引线压焊块71。

如图13所示,所述扩散层2包括位于悬浮块52和承载膜53下方的扩散层下极板区21、与下电极引线压焊块71连接的扩散层电极引线区22、连接扩散层下极板区21与下电极引线区的导电通道23。导电通道23位于对称轴上,扩散层2关于对称轴对称。

悬浮在扩散层2上的悬浮块52和承载膜53作为上极板区,与扩散层下极板区21共同构成平行板电容执行器。在上电极引线压焊块72与下电极引线压焊块71之间加电压后,可实现测试芯片电信号的加载,下电极引线压焊块71通过导电通道23使得扩散层电极引线区22带电,上电极引线压焊块72通过悬浮块锚点区51使得悬浮块52和承载膜53带电,承载膜53在厚度方向上发生位移。

所述悬浮块52、承载膜53、悬浮块锚点区51厚度相同,且位于同一平面上,悬浮块52是正方形结构,承载膜53位于承载膜53的中心位置,悬浮块锚点区51位于悬浮块52的四周,悬浮块锚点区51通过悬浮块锚点固定区4与下方硅衬底1固定连接。

所述承载膜53为凹角蜂窝结构,包括多个重复的凹角结构单元,可以通过对凹角结构单元的尺寸设计,调控承载膜53的泊松比,使得承载膜53在长度方向拉伸应变时,宽度方向的变宽、变窄、或不变。

承载膜53可以实现单轴拉伸的原理如下:

如图14所示,凹角结构单元可以使用以下参数描述:横杆长度w、斜杆长度l、斜杆与纵向垂直线之间的夹角θ、结构厚度t。结构在x方向上受到拉伸,假设该结构中的所有接缝都是刚性的,结构的变形主要是由于凹入支撑杆的弯曲和横向水平杆的纵向拉伸所致,并不考虑扭转作用。

由于凹角结构单元的高度对称性,凹角结构单元可以进一步简化为图15所示四分之一结构进行力学分析。图中斜杆OA拉伸后为OA’,长度均为l,旋转角度为

其中AA’为斜杆受到拉伸后的位移,Δx为斜杆在x方向上的位移,Δy为斜杆在y方向上的位移。

AB,OA,OC在x方向上的投影分别为w/2,lsin(θ),w/2,因此在x方向上的有效长度为w-lsin(θ),在y方向上的有效长度为lcos(θ)。

因此可以计算纵向应变ε

在Timoshenko模型中,假定挠曲角足够小,可以忽略挠曲引起的斜杆长度的减小。确定了x方向拉伸下泊松比的简化表达式为

由公式(6)可知,凹角结构单元泊松比主要受横杆长度w、斜杆长度l、斜杆与纵向垂直线之间的夹角θ调控、通过选择不同的结构尺寸,可以得到不同的泊松比。尤其特别的是,当w=lsin(θ)时,泊松比为0,也就是说,长度方向拉伸时,宽度不变,实现单轴拉伸。

承载膜53上覆有二氧化硅绝缘层6,且下方具有衬底掏空结构8,用于TEM观测。衬底掏空结构8为圆形孔洞,直径约为10μm,均匀分布于承载膜53下方,数量约为10-50个。

本发明的测试芯片尺寸约为5*3mm,其中悬浮块52整体面积约为10mm

具体使用方法:使用压焊技术将电极引线压焊块连接到外界测试电路中,利用移液枪将待测二维材料样品滴在承载膜53上,使待测样品均匀分布,也可使用FIB等转移技术将待测样品进行转移。通过在上下电极施加直流或一定频率的交流电载荷,可实现待测样品的非线性静态或动态高频表征测试,获得二维材料的杨氏模量、预张力等力学参数,和疲劳特性测试,还可进行二维材料纳机电谐振研究。同时,还可以通过在上下电极施加高压载荷,实现二维材料的原位TEM/SEM单轴拉伸测试,从而获得其应变、应力等力学参数。该芯片同样适用于AFM、Raman等测试设备。

上述结构的测试芯片的制备方法,包括以下步骤:

步骤1,如图2所示,在硅衬底1上采用光刻、扩散掺杂工艺形成扩散层2,掺杂材料为硼或磷,所述扩散层2包括扩散层下极板区21、扩散层电极引线区22、以及连接扩散层下极板区21与下电极引线区的导电通道23;

步骤2,如图3所示,在硅衬底1上CVD工艺沉积一层0.5-2μm厚的牺牲层3,所述牺牲层3为SiO

步骤3,如图4所示,采用光刻、反应离子刻蚀工艺对牺牲层3刻蚀出悬浮块锚点固定区4;

步骤4,如图5所示,然后CVD沉积1-2μm的氮化硅层并图案化,填充悬浮块锚点固定区4;

步骤5,如图6所示,在牺牲层3上CVD沉积一层0.5-2μm厚的多晶硅作为结构层5;

步骤6,如图7所示,在结构层5上生长100-500nm二氧化硅,形成绝缘层6;

步骤7,如图8所示,采用光刻、反应离子刻蚀工艺对二氧化硅绝缘层6图案化;

步骤8,如图9所示,采用光刻、反应离子刻蚀工艺对结构层5图案化,形成承载膜53结构图形,以及刻蚀去除位于扩散层电极引线区22上方的结构层5;

步骤9,如图10所示,腐蚀牺牲层3;

步骤10,如图11所示,采用光刻、电子束蒸发工艺在结构层5上制备50/250nm厚的Ti/Au的上电极引线压焊块72、以及扩散层电极引线区22上制备50/250nm厚的Ti/Au的下电极引线压焊块71;

步骤11,如图12所示,采用光刻、深反应离子刻蚀工艺将TEM观测区域下方的硅衬底1刻穿,形成衬底掏空结构8,完成以多晶硅为结构层5的力学测试芯片的制备。

以上显示和描述了本发明的基本原理、主要特征和优点。本领域的技术人员应该了解,本发明不受上述具体实施例的限制,上述具体实施例和说明书中的描述只是为了进一步说明本发明的原理,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明范围内。本发明要求保护的范围由权利要求书及其等效物界定。

- 一种基于载网结构的原位力学测试芯片及制备方法

- 一种原位力学测试芯片及其制备方法