一种电源瞬态突变抑制的低压差线性稳压器

文献发布时间:2023-06-19 18:25:54

技术领域

本发明涉及集成电路技术领域,尤其涉及一种电源瞬态突变抑制的低压差线性稳压器。

背景技术

低压差线性稳压器(low dropout regulator,LDO)是新一代的集成电路稳压器,它与三端稳压器最大的不同点在于,LDO是一个自耗很低的微型片上系统(System-on-a-chip,SoC),可应用于电流主通道控制,芯片上集成了具有极低线上导通电阻的MOS器件,肖特基二极管、取样电阻和分压电阻等硬件电路,并具有过流保护、过温保护、精密基准源、差分放大器、延迟器等功能。

在功率管集成的驱动芯片中,内部集成的功率器件的开关动作中会产生电流的突变di/dt,由于芯片绑定(bonding)线会存在寄生电感

为了抑制LDO瞬态输出跳变,如图1所示,现有技术中通常是通过增大LDO输出偏置电压的滤波电容C_filter1或者增大静态偏置电流来抑制电源的瞬态跳变对LDO输出的影响。但这种方案中需要的滤波电容的容值较大,且芯片功耗较大,不利于绿色环保的理念。

发明内容

为了解决以上技术问题,本发明提供了一种低功耗的电源瞬态突变抑制的低压差线性稳压器。

本发明所解决的技术问题可以采用以下技术方案实现:一种电源瞬态突变抑制的低压差线性稳压器,包括:一输出级,于一偏置电压的作用下输出一输出电压;一第一动态钳位电路,连接于一电源端和所述输出级的输入之间,用于在检测到所述电源端发生瞬态突变时对电源端电压和所述偏置电压的压差进行钳位;一第二动态钳位电路,连接于所述电源端和所述输出级的输出之间,用于当检测到所述电源端电压和所述输出电压的压差超过一预设阈值时进行钳位。

优选地,所述第一动态钳位电路包括:正向钳位模块,用于在检测到所述电源端发生正向瞬态突变时将所述电源端电压和所述偏置电压的压差钳位在第一预定电压。

优选地,所述正向钳位模块包括:第一晶体管,所述第一晶体管的栅极和源极之间连接一第一电阻,所述第一晶体管的源极连接所述电源端,所述第一晶体管的漏极连接所述输出级的输入;第一电容,连接于所述第一晶体管的栅极和漏极之间。

优选地,所述第一动态钳位电路包括:负向钳位模块,用于在检测到所述电源端发生负向瞬态突变时将所述电源端电压和所述偏置电压的压差钳位在第二预定电压。

优选地,所述负向钳位模块包括:第二晶体管,所述第二晶体管的栅极和源极之间连接一第二电阻,所述第二晶体管的源极连接所述输出级的输入,所述第二晶体管的漏极接地;第二电容,连接于所述第二晶体管的栅极和漏极之间。

优选地,所述第二动态钳位电路包括:第三晶体管,所述第三晶体管的栅极连接所述预设阈值,所述第三晶体管的源极连接所述输出电压,所述第三晶体管的漏极通过一第三电阻连接所述电源端;第四晶体管,所述第四晶体管的栅极连接所述第三晶体管的漏极,所述第四晶体管的漏极连接所述输出电压,所述第四晶体管的源极连接所述电源端。

优选地,还包括:一分压模块,用于输出一反馈信号至所述第二动态钳位电路,以根据所述反馈信号调整所述预设阈值。

优选地,还包括:一静态偏置电路,连接于所述电源端和所述输出级的输入之间,用于输出所述偏置电压。

优选地,所述静态偏置电路包括:第五晶体管,所述第五晶体管的源极通过所述分压模块连接所述电源端,所述第五晶体管的栅极和漏极通过一第二滤波电容连接所述电源端,自所述第五晶体管的栅极和漏极输出所述偏置电压;第六晶体管,所述第六晶体管的漏极连接所述第五晶体管的栅极和漏极,所述第六晶体管的栅极连接模拟电压,所述第六晶体管的源极连接一偏置电流。

优选地,所述输出级包括:功率管,所述功率管的栅极连接所述偏置电压,所述功率管的源极通过一第二滤波电容连接所述电源端,所述功率管的漏极接地。

本发明技术方案的优点或有益效果在于:本发明通过设置第一动态钳位电路,在电源端发生瞬态突变时触发钳位,来抑制电源瞬态突变造成的偏置电压的瞬态突变,将偏置电压的瞬态突变限制在一定范围内;通过设置第二动态钳位电路,在电源端发生瞬态突变时触发钳位,来抑制电源瞬态突变造成的输出电压的瞬态突变,将输出电压的瞬态突变限制在一定范围内。

附图说明

图1为现有技术中,开环LDO的示意图;

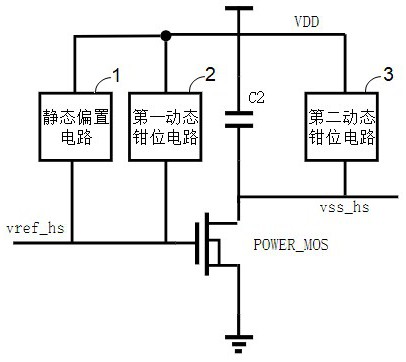

图2为本发明较佳实施例中,电源瞬态突变抑制的低压差线性稳压器的结构框架示意图;

图3为本发明较佳实施例中,电源瞬态突变抑制的低压差线性稳压器具体实施的示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

下面结合附图和具体实施例对本发明作进一步说明,但不作为本发明的限定。

参见图2-图3,本发明的较佳的实施例中,基于现有技术中存在的上述问题,现提供一种电源瞬态突变抑制的低压差线性稳压器,包括:一输出级4,于一偏置电压vref_hs的作用下输出一输出电压vss_hs;一第一动态钳位电路2,连接于一电源端和输出级4的输入之间,用于在检测到电源端发生瞬态突变时对电源端电压和偏置电压vref_hs的压差进行钳位;一第二动态钳位电路3,连接于电源端和输出级4的输出之间,用于当检测到电源端电压和输出电压的压差超过一预设阈值时进行钳位。

具体的,LDO的输出级4通过功率器件对偏置电压vref_hs进行处理后输出输出电压vss_hs,输出电压vss_hs由偏置电压vref_hs决定,而偏置电压vref_hs又与电源端电压相关。在电源端电压发生瞬态突变时偏置电压vref_hs也会产生一定的突变,由于输出电压vss_hs是输出级4功率器件的源极输出,所以输出电压vss_hs会跟随偏置电压vref_hs,至少会出现一个源栅电压幅度大小的突变。

为了解决电源端电压瞬态突变vdd对偏置电压vref_hs和输出电压vss_hs的耦合。在本实施例中,通过设置第一动态钳位电路2,在电源端发生瞬态突变时触发钳位,来抑制电源瞬态突变造成的偏置电压的瞬态突变(定义为:vdd-vref_hs),将偏置电压的瞬态突变限制在一定范围内;通过设置第二动态钳位电路3,在电源端发生瞬态突变时触发钳位,来抑制电源瞬态突变造成的输出电压的瞬态突变(定义为:vdd-vss_hs),将输出电压的瞬态突变限制在一定数百mv的压差范围内,同时对于输出电压vss_hs的抽电流造成的输出电压的正向瞬态突变有限制作用。

作为优选的实施方式,其中,第一动态钳位电路2包括:正向钳位模块,用于在检测到电源端发生正向瞬态突变时将电源端电压和偏置电压的压差(vdd-vref_hs)钳位在第一预定电压。

具体的,电源端出现正向瞬态突变时,由于寄生电容的耦合,会出现正向瞬态突变vdd-vref_hs,其中:

vdd-vref_hs≈Cgd*vdd/(Cgd+C3);

其中,vdd-vref_hs表示偏置电压的正向瞬态突变;Cgd表示功率管POWER_MOS的寄生电容;vdd表示电源端电压;C3表示第一滤波电容C3的容值。

从上述公式可知,vdd-vref_hs大小由第一滤波电容C3和功率管POWER_MOS的寄生电容Cgd电容决定。

为了抑制电源端正向瞬态突变对偏置电压vref_hs的干扰,在本实施例中,正向钳位模块通过对电源端电压进行检测,当检测到发生正向瞬态突变时,触发正向钳位功能,利用电容电压不能突变的原理将其钳位在一定范围内。

作为优选的实施方式,其中,正向钳位模块包括:第一晶体管P1,第一晶体管P1的栅极和源极之间连接一第一电阻R1,第一晶体管P1的源极连接电源端,第一晶体管P1的漏极连接输出级4的输入;第一电容C1,连接于第一晶体管P1的栅极和漏极之间。

具体的,在本实施例中,正向钳位模块使用第一电阻R1、第一电容C1、第一晶体管P1对电源端电压和偏置电压的压差进行动态检测,利用电容的电压不能突变的原理,第一电容C1远大于第一晶体管P1的寄生电容时,第一电阻R1的两端的正向瞬态突变等于vdd-vref_hs;当正向瞬态突变超过第一晶体管P1的导通电压时,第一晶体管P1导通,将vdd-vref_hs钳位在第一预定电压。

进一步的,上述第一预定电压为第一晶体管P1的源栅电压。上述第一晶体管P1可以设置为一个,也可以设置为多个。通过改变第一晶体管P1的数量,调整第一预定电压的大小。

作为优选的实施方式,其中,第一动态钳位电路2包括:负向钳位模块,用于在检测到电源端发生负向瞬态突变时将电源端电压和偏置电压的压差(vdd-vss_hs)钳位在第二预定电压。

作为优选的实施方式,其中,负向钳位模块包括:第二晶体管P2,第二晶体管P2的栅极和源极之间连接一第二电阻R2,第二晶体管P2的源极连接输出级4的输入,第二晶体管P2的漏极接地;第二电容C2,连接于第二晶体管的栅极和漏极之间。

具体的,在本实施例中,正向钳位模块使用第二电阻R2、第二电容C2、第二晶体管P2对电源端电压和偏置电压的压差进行动态检测,利用电容的电压不能突变的原理,第二电容C2远大于第二晶体管P2的寄生电容时,第二电阻R2的两端的负向瞬态突变等于vdd-vref_hs;当负向瞬态突变超过第二晶体管P2的导通电压时,第二晶体管P2导通,将vdd-vref_hs钳位在第二预定电压。

进一步的,上述第二预定电压为第二晶体管P2的源栅电压。上述第二晶体管P2可以设置为一个,也可以设置为多个。通过改变第二晶体管P2的数量,调整第二预定电压的大小。

作为优选的实施方式,其中,第二动态钳位电路3包括:第三晶体管N3,第三晶体管N3的栅极连接预设阈值,第三晶体管N3的源极连接输出电压,第三晶体管N3的漏极通过一第三电阻R3连接电源端;第四晶体管P3,第四晶体管P3的栅极连接第三晶体管N3的漏极,第四晶体管P3的漏极连接输出电压,第四晶体管P3的源极连接电源端。

具体的,在本实施例中,第二动态钳位电路3使用第三电阻R3、第三晶体管N3、第四晶体管P3对电源端电压和输出电压的压差进行动态检测,设置预设阈值vref_clamp的大小可以设置电源端电压和输出电压的压差的过压检测点,当电源端电压和输出电压的压差超过过压检测点时,第三晶体管N3、第四晶体管P3导通,进行钳位,抑制其正向瞬态突变。

进一步的,电路从输出电压vss_hs节点抽电流时,也会导致电源端电压和输出电压之间会出现正向瞬态突变,同理,第二动态钳位电路3还可抑制输出电压vss_hs节点抽电流带来的vss_hs正向瞬态突变。

作为优选的实施方式,其中,还包括:一分压模块,用于输出一反馈信号vref_clamp至第二动态钳位电路3,以根据反馈信号调整预设阈值。

进一步的,其中,分压模块由多个分压电阻并联而成,其中两个分压电阻的连接点输出上述反馈信号vref_clamp,通过对分压电阻的阻值进行调整,以改变触发第二动态钳位电路3的钳位功能的预设阈值的大小。作为举例而非限定,分压电阻包括分压电阻Rb1、Rb2,电阻Rb1、Rb2的连接点连接第三晶体管N3的栅极,输出反馈信号vref_clamp至第三晶体管N3的栅极,通过调整电阻Rb1、Rb2的阻值大小来设置vref_clamp的大小,从而调整vdd-vss_hs的压差过压检测点。

作为优选的实施方式,其中,还包括:一静态偏置电路1,连接于电源端VDD和输出级4的输入之间,用于输出偏置电压vref_hs。

作为优选的实施方式,其中,静态偏置电路1包括:第五晶体管POWER_SENSE,第五晶体管POWER_SENSE的源极通过上述分压模块连接电源端,第五晶体管POWER_SENSE的栅极和漏极通过一第二滤波电容C3连接电源端,自第五晶体管POWER_SENSE的栅极和漏极输出偏置电压vref_hs;第六晶体管NM_HV,第六晶体管NM_HV的漏极连接第五晶体管POWER_SENSE的栅极和漏极,第六晶体管NM_HV的栅极连接模拟电压AVDD,第六晶体管NM_HV的源极连接一偏置电流,其中,该偏置电流由一电流源提供。

具体的,高边LDO输出级4的输出电压vss_hs由偏置电压vref_hs决定,而在静态偏置电路中,偏置电压vref_hs由偏置电流、分压模块的分压电阻Rb1、Rb2和第六晶体管NM_HV决定,具体对应关系为:

其中,

作为优选的实施方式,其中,输出级4包括:功率管POWER_MOS,功率管POWER_MOS的栅极连接偏置电压vref_hs,功率管POWER_MOS的源极通过一第二滤波电容C4连接电源端VDD,功率管POWER_MOS的漏极接地。

以上所述仅为本发明较佳的实施例,并非因此限制本发明的实施方式及保护范围,对于本领域技术人员而言,应当能够意识到凡运用本说明书及图示内容所作出的等同替换和显而易见的变化所得到的方案,均应当包含在本发明的保护范围内。

- 一种快速瞬态响应的低压差线性稳压器

- 一种高电源抑制比快速瞬态响应的低压差线性稳压器

- 一种高电源抑制比快速瞬态响应的低压差线性稳压器