静电放电保护装置

文献发布时间:2023-06-19 19:20:08

技术领域

本发明涉及静电放电保护装置,特别是涉及静电放电保护装置的结构以及布局。

背景技术

包括半导体元件的集成电路很容易受到电性过压(electrical overstress,EOS)的影响而造成损坏,电性过压包括静电放电(ESD)、瞬时状况(transient condition)、电路栓锁作用(latch up)、以及不正确的极性连接,其中电性过压状况分为过电压或过电流事件。由于静电电荷会在物体内部(body)累积,且当累积有电荷的物体碰触到集成电路时,此现象即为静电放电(Electrostatic Discharge),静电放电现象所产生的电流会损坏其中的半导体元件以及电路。因此如何保护半导体元件不受静电放电或其他电性过压状况的影响,是亟待解决的问题。此外,针对高速的高阶芯片,使用二极管或是晶体管也无法解决ESD的问题。

发明内容

本发明一些实施例提供一种静电放电保护装置。静电放电保护装置包括P型半导体基板、第一N型深阱区、第二N型深阱区、第一N型掺杂区、第一P型掺杂区、第二N型掺杂区、第二P型掺杂区、第三N型掺杂区、第三P型掺杂区、第四N型掺杂区、第四P型掺杂区、第一P型阱区以及第二P型阱区。第一N型深阱区位于P型半导体基板中;第一N型掺杂区位于第一N型深阱区中;第一P型掺杂区位于第一N型深阱区中,且与第一N型掺杂区并排且彼此间隔设置;第二N型深阱区位于P型半导体基板中,且与第一N型深阱区并排且彼此间隔设置;第二N型掺杂区位于第二N型深阱区中;第二P型掺杂区位于第二N型深阱区中,且与第二N型掺杂区并排且彼此间隔设置;第一P型阱区位于第一N型深阱区中;第三N型掺杂区位于第一P型阱区中;第三P型掺杂区位于第一P型阱区中,且与第三N型掺杂区并排且彼此间隔设置;第二P型阱区位于第二N型深阱区中;第四N型掺杂区位于第二P型阱区中;以及第四P型掺杂区位于第二P型阱区中,且与第四N型掺杂区并排且彼此间隔设置;其中第一P型掺杂区和第四N型掺杂区电连接至输入/输出端,其中第一N型掺杂区和第二P型掺杂区电连接至电源供应端,其中第三N型掺杂区和第四P型掺杂区电连接至接地端。

附图说明

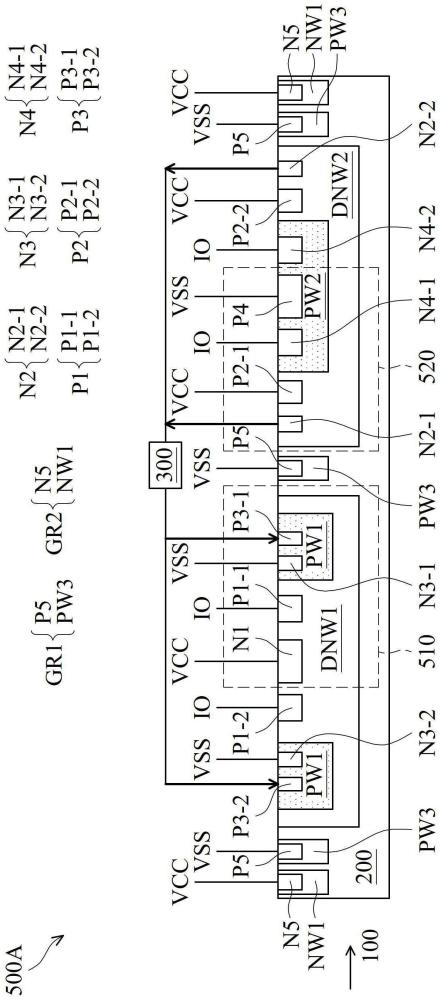

图1为本发明一些实施例的静电放电保护装置的俯视示意图;

图2为沿图1所示的本发明一些实施例的静电放电保护装置的A-A’切线的剖面示意图;

图3为图2的局部放大图,其显示静电放电事件发生于输入/输出端(IO)和电源供应端VCC之间,或静电放电事件发生于接地端(VSS)和输入/输出端(IO)之间的等效放电电路,以及上述等效电路的寄生元件在图2的静电放电保护装置相应位置的示意图;

图4A为静电放电事件发生于输入/输出端(IO)和接地端(VSS)之间的等效放电电路;

图4B为图4A等效电路的寄生元件在图2的静电放电保护装置相应位置的示意图;

图5A为静电放电事件发生于电源供应端(VCC)和输入/输出端(IO)之间的等效放电电路;

图5B为图5A等效电路的寄生元件在图2的静电放电保护装置相应位置的示意图;

图6~图10为本发明一些实施例的静电放电保护装置的局部剖面示意图。

符号说明

100,110:方向

200:P型半导体基板

210,220,230:导线

300:切换电路

300A:侦测电路

302:N型金属氧化物半导体晶体管

500,500A,500B,500C,500D,500E,500F:静电放电保护装置

510,520:区域

A-A’:切线

B-B’,C-C’:虚线

B1:第一寄生双极性接面(结型)晶体管

B2:第二寄生双极性接面晶体管

B3:第三寄生双极性接面晶体管

B4:第四寄生双极性接面晶体管

BT:基极

C1:第一电容

C2:第二电容

D1:第一寄生二极管

D2:第二寄生二极管

D3:第三寄生二极管

D4:第四二极管

DNW1:第一N型深阱区

DNW2:第二N型深阱区

G1:第一栅极结构

G2:第二栅极结构

G3:第三栅极结构

G4:第四栅极结构

GR1:第一保护环

GR2:第二保护环

GT:栅极

IO:输入/输出端

NW1:第一N型阱区

NM1:第一N型金属氧化物半导体晶体管

NM2:第二N型金属氧化物半导体晶体管

N1:第一N型掺杂区

N2,N2-1,N2-2:第二N型掺杂区

N3,N3-1,N3-2:第三N型掺杂区

N4,N4-1,N4-2:第四N型掺杂区

N5:第五N型掺杂区

N6:第六N型掺杂区

N7:第七N型掺杂区

P1,P1-1,P1-2:第一P型掺杂区

P2,P2-1,P2-2:第二P型掺杂区

P3,P3-1,P3-2:第三P型掺杂区

P4:第四P型掺杂区

P5:第五P型掺杂区

P6:第六P型掺杂区

P7:第七P型掺杂区

PW1:第一P型阱区

PW2:第二P型阱区

PW3:第三P型阱区

PM1:第一P型金属氧化物半导体晶体管

PH1,PH2:电流路径

SCR-1:第一寄生半导体控制整流器

SCR-2:第二寄生半导体控制整流器

SDT1:第一源/漏极

SDT2:第二源/漏极

VCC:电源供应端

VSS:接地端

具体实施方式

以下参照本发明实施例的附图以更全面地阐述本发明。然而,本发明也可以各种不同的实施方式实现,而不应限于本文中所述的实施例。附图中的层与区域的厚度可能会为了清楚起见而放大,并且在各附图中相同或相似的参考号码表示相同或相似的元件。

图1为本发明一些实施例的静电放电保护装置500(包括静电放电保护装置500A、500B、500C、500D、500E、500F)的俯视示意图。图2为沿图1所示的本发明一些实施例的静电放电保护装置500A的A-A’切线的剖面示意图。静电放电保护装置500电连接于系统的输入/输出端(IO)和接地端(VSS)之间,用以避免一静电放电电流流经受保护的电路。静电放电保护装置500A包括P型半导体基板200,以及位于P型半导体基板200中的第一保护环GR1、第二保护环GR2、第一N型深阱区DNW1、第二N型深阱区DNW2、第一P型阱区PW1以及第二P型阱区PW2。第一N型深阱区DNW1、第二N型深阱区DNW2、第一P型阱区PW1以及第二P型阱区PW2分别包括至少一对具相反导电类型的重掺杂区(heavily doped region)。为了说明,图1仅显示以上部件,其余部件可见于图2的剖面示意图,其沿着图1的切线A-A截取,切线A-A实质上平行方向100。举例来说,第一N型深阱区DNW1包括第一N型掺杂区N1以及第一P型掺杂区P1(包括第一P型掺杂区P1-1、P1-2),第二N型深阱区DNW2包括第二N型掺杂区N2(包括第二N型掺杂区N2-1、N2-2)以及第二P型掺杂区P2(包括第二P型掺杂区P2-1、P2-2),第一P型阱区PW1包括第三N型掺杂区N3(第三N型掺杂区N3-1、N3-2)以及第三P型掺杂区P3(包括第三P型掺杂区P3-1、P3-2),第二P型阱区PW2包括第四N型掺杂区N4(包括第四N型掺杂区N4-1、N4-2)以及第四P型掺杂区P4。

如图1、图2所示,第一N型深阱区DNW1与第二N型深阱区DNW2都位于P型半导体基板200中,两者沿方向100并排且彼此间隔设置。静电放电保护装置500A还包括位于第一N型深阱区DNW1中的第一N型掺杂区N1以及第一P型掺杂区P1-1、P1-2。第一N型掺杂区N1以及第一P型掺杂区P1-1、P1-2沿方向110延伸,且设置于第一N型深阱区DNW1的中间区域。并且,第一P型掺杂区P1-1、P1-2分别位于第一N型掺杂区N1实质上平行于方向110的相对侧,且沿方向100分别与第一N型掺杂区N1间隔设置。在本实施例中,第一N型掺杂区N1电连接至电源供应端VCC,第一P型掺杂区P1-1、P1-2电连接至输入/输出端IO。

如图1、图2所示,静电放电保护装置500A还包括位于第二N型深阱区DNW2中的第二N型掺杂区N2-1、N2-2以及第二P型掺杂区P2-1、P2-2。第二N型掺杂区N2-1、N2-2以及第二P型掺杂区P2-1、P2-2沿方向110延伸。并且,第二N型掺杂区N2-1、第二P型掺杂区P2-1位于接近于第一N型深阱区DNW1的第二N型深阱区DNW2的周边区域中,两者沿方向100并排且彼此间隔设置。第二N型掺杂区N2-2、第二P型掺杂区P2-2位于远离于第一N型深阱区DNW1的第二N型深阱区DNW2的周边区域中,两者沿方向100并排且彼此间隔设置。在本实施例中,第二N型掺杂区N2-1、N2-2电连接至切换电路300的一个输出端(切换电路300的结构可参考图4A),第二P型掺杂区P2-1、P2-2电连接至电源供应端VCC。

如图1、图2所示,静电放电保护装置500A的第一P型阱区PW1位于第一N型深阱区DNW1中。在如图1的俯视图中,第一P型阱区PW1为环型,且覆盖第一N型深阱区DNW1的周边区域。在如图2的剖面图中,第一P型阱区PW1沿方向110位于第一N型掺杂区N1的相对侧。静电放电保护装置500A还包括位于第一P型阱区PW1中的第三N型掺杂区N3-1、N3-2以及第三P型掺杂区P3-1、P3-2。第三N型掺杂区N3-1、N3-2以及第三P型掺杂区P3-1、P3-2沿方向110延伸。并且,第三N型掺杂区N3-1、第三P型掺杂区P3-1位于接近于第二N型深阱区DNW2的第一N型深阱区DNW1的周边区域中,两者沿方向100并排且彼此间隔设置。第三N型掺杂区N3-2、第三P型掺杂区P3-2位于远离于第二N型深阱区DNW2的第一N型深阱区DNW1的周边区域中,两者沿方向100并排且彼此间隔设置。在本实施例中,第三N型掺杂区N3-1、N3-2电连接至接地端VSS,第三P型掺杂区P3-1、P3-2电连接至切换电路300的另一个输出端(相对第二N型掺杂区N2-1、N2-2)。

如图1、图2所示,静电放电保护装置500A的第二P型阱区PW2位于第二N型深阱区DNW2中,且设置于第二N型深阱区DNW2的中间区域上,使未被第二P型阱区PW2覆盖的第二N型深阱区DNW2在图1的俯视图中为环型。静电放电保护装置500A还包括位于第二P型阱区PW2中的第四N型掺杂区N4-1、N4-2以及第四P型掺杂区P4。第四N型掺杂区N4-1、N4-2以及第四P型掺杂区P4沿方向110延伸。并且,第四N型掺杂区N4-1、N4-2分别位于第四P型掺杂区P4实质上平行于方向110的相对侧,且沿方向100分别与第四P型掺杂区P4间隔设置。在本实施例中,第四N型掺杂区N4-1、N4-2电连接至输入/输出端IO,第四P型掺杂区P4电连接至接地端VSS。

如图1、图2所示,静电放电保护装置500A的第一保护环GR1位于第一N型深阱区DNW1和第二N型深阱区DNW2外侧,分别包围第一N型深阱区DNW1和第二N型深阱区DNW2,且沿方向100位于第一P型阱区PW1和第二P型阱区PW2之间。第一保护环GR1包括第三P型阱区PW3以及位于第三P型阱区PW3中的第五P型掺杂区P5。在本实施例中,P型半导体基板200可通过第五P型掺杂区P5电连接至接地端VSS。

如图1、图2所示,静电放电保护装置500A的第二保护环GR2位于第一N型深阱区DNW1和第二N型深阱区DNW2外侧,且包围第一保护环GR1。第二保护环GR2包括第一N型阱区NW1以及位于第一N型阱区NW1中的第五N型掺杂区N5。在一些实施例中,第五N型掺杂区N5电连接至电源供应端VCC。一般来说,N型保护环(第二保护环GR2)电连接至较高电压位准,而P型保护环(第一保护环GR1)电连接至较低电压位准。

如图1、图2所示,设置于第一N型深阱区DNW1中的第一P型阱区PW1和重掺杂区(包括第一N型掺杂区N1以及第一P型掺杂区P1-1、P1-2),以及设置于第一P型阱区PW1中的重掺杂区(包括第三N型掺杂区N3-1、N3-2以及第三P型掺杂区P3-1、P3-2)以沿方向110穿过第一N型掺杂区N1中心的轴线(如虚线B-B’所示)对称设置。类似的,设置于第二N型深阱区DNW2中的第二P型阱区PW2和重掺杂区(包括第二N型掺杂区N2-1、N2-2以及第二P型掺杂区P2-1、P2-2),以及设置于第二P型阱区PW2中的重掺杂区(包括第四N型掺杂区N4-1、N4-2以及第四P型掺杂区P4)以沿方向110穿过第四P型掺杂区P4中心的轴线(如虚线C-C’所示)对称设置。因此,后续附图将撷取图2的区域510、520说明发生在输入/输出端IO、电源供应端VCC或接地端VSS的各静电放电事件触发的等效电路以及其他实施例的静电放电保护装置。并且,后续附图中的第二、第三以及第四N型掺杂区分别标示为N2、N3、N4,第一、第二以及第三P型掺杂区分别标示为P1、P2、P3。

在下文所述的实施例中,切换电路300会视不同情况将第二N型掺杂区N2和第三P型掺杂区P3切换至不同的电位。举例来说,当受保护的电路在正常工作时(未发生静电放电事件),电连接至切换电路300的第二N型掺杂区N2会电连接至电源供应端VCC(其电压位准等于高位准),且电连接至切换电路300的第三P型掺杂区P3会电连接至接地端VSS(其电压位准等于接地位准)。当静电放电事件发生于输入/输出端IO、电源供应端VCC或接地端VSS时,电连接至切换电路300的第二N型掺杂区N2会电连接至接地端VSS(其电压位准等于接地位准),且电连接至切换电路300的第三P型掺杂区P3会电连接至电源供应端VCC(其电压位准等于高位准)。

图3为图2的区域510、520的放大图,其显示静电放电(ESD)事件发生于输入/输出端IO和电源供应端VCC之间的等效放电电路,或静电放电(ESD)事件发生于接地端VSS和输入/输出端(IO)之间的等效放电电路,以及上述等效放电电路的寄生元件在图2的静电放电保护装置500A相应位置的示意图。如图3所示,第一P型掺杂区P1、第一N型深阱区DNW1和第一N型掺杂区N1构成第一寄生二极管D1。当静电放电事件发生于输入/输出端IO与电源供应端VCC之间时,第一寄生二极管D1被触发导通,以形成从输入/输出端IO至电源供应端VCC的电流路径PH1,将静电荷导离受保护的电路。

如图3所示,第四P型掺杂区P4、第二P型阱区PW2和第四N型掺杂区N4构成第二寄生二极管D2。当静电放电事件发生于接地端VSS与输入/输出端IO之间时,第二寄生二极管D2被触发导通,以形成从接地端VSS至输入/输出端IO的电流路径PH2,将静电荷导离受保护的电路。

图4A显示静电放电(ESD)事件发生于输入/输出端IO与接地端VSS之间的另一种等效放电电路以及与其电连接的切换电路300。图4B显示图4A等效放电电路的寄生元件在图2的静电放电保护装置500A相应位置的示意图。如图4A、图4B所示,除了第一寄生二极管D1之外,静电放电事件发生于输入/输出端IO与接地端VSS之间的等效放电电路还包括由第一P型掺杂区P1、第一N型深阱区DNW1和第一P型阱区PW1构成的第一寄生双极性接面晶体管(BJT)B1(例如寄生PNP BJT)。第一寄生双极性接面晶体管B1的射极(emitter)、基极(base)以及集极(collector)分别由第一P型掺杂区P1、第一N型深阱区DNW1和第一P型阱区PW1构成。上述等效电路还包括由第三N型掺杂区N3、第一P型阱区PW1和第一N型深阱区DNW1构成的第二寄生双极性接面晶体管B2(例如寄生NPN BJT)。第二寄生双极性接面晶体管B2的射极、基极以及集极分别由第三N型掺杂区N3、第一P型阱区PW1和第一N型深阱区DNW1构成。并且,第一寄生双极性接面晶体管B1的基极(第一N型深阱区DNW1)与第二寄生双极性接面晶体管B2的集极(第一N型深阱区DNW1)电连接,第二寄生双极性接面晶体管B2的基极(第一P型阱区PW1)与第一寄生双极性接面晶体管B1的集极(第一P型阱区PW1)电连接,以构成第一寄生半导体控制整流器SCR-1。此外,第一寄生双极性接面晶体管B1的射极(第一P型掺杂区P1)与输入/输出端IO和第一寄生二极管D1的正极电连接,第一寄生双极性接面晶体管B1的基极(第一N型深阱区DNW1)与第一寄生二极管D1的负极电连接。第二寄生双极性接面晶体管B2的射极(第三N型掺杂区N3)与接地端VSS电连接。

图4A也显示切换电路300的等效电路。切换电路300由电阻-电容传感器(RCdetector)构成,其包括电阻、电容、反相器(inverter)以及N型金属氧化物半导体晶体管。

如图4A、图4B所示,当静电放电(ESD)事件发生于输入/输出端IO与接地端VSS之间时,会对第一寄生二极管D1和第一寄生双极性接面晶体管B1的射极(第一P型掺杂区P1)-基极(第一N型深阱区DNW1)接面(结)施加顺向偏压而被触发导通,以形成从输入/输出端IO流经第一寄生双极性接面晶体管B1的射极(第一P型掺杂区P1)-基极(第一N型深阱区DNW1)接面且流至切换电路300的电流路径,使第一寄生双极性接面晶体管B1被触发导通,且使切换电路300对第三P型掺杂区P3(切换电连接至电源供应端VCC)输出高位准,上述高位准高于接地端VSS的接地位准。并且,切换电路300通过导线210电连接第二寄生双极性接面晶体管B2的基极(第一P型阱区PW1),因此,当切换电路300输出的高位准高于接地端VSS的接地位准时,会形成流经导线210的电流路径,而对第二寄生双极性接面晶体管B2的基极(第一P型阱区PW1)-射极(第三N型掺杂区N3)接面施加顺向偏压,使第二寄生双极性接面晶体管B2被触发导通。由于第一寄生双极性接面晶体管B1和第二寄生双极性接面晶体管B2一起被触发导通,从而使第一寄生半导体控制整流器SCR-1被触发导通并形成电流路径。上述电流路径提供触发电流(启动电流),接续触发第一寄生双极性接面晶体管B1(PNP)和第二寄生双极性接面晶体管B2(NPN),而形成第一寄生半导体控制整流器SCR-1,此低维持电压(VHold)、低电阻(R)的第一寄生半导体控制整流器SCR-1可以提供输入/输出端IO至从接地端VSS的电流路径,将静电荷导离受保护的电路。

当系统中的受保护元件在正常工作(未发生静电放电事件)时,第三P型掺杂区P3切换电连接至接地端VSS,第二寄生双极性接面晶体管B2的基极(第一P型阱区PW1)-射极(第三N型掺杂区N3)接面不存在顺向偏压,因此第二寄生双极性接面晶体管B2不会被触发导通。并且,第一N型深阱区DNW1电连接至电源供应端VCC,其为全系统最高电位。因此,第一寄生双极性接面晶体管B1的射极(第一P型掺杂区P1)-基极(第一N型深阱区DNW1)接面不存在顺向偏压,因此第一寄生双极性接面晶体管B1不会被触发导通。由于第一寄生双极性接面晶体管B1和第二寄生双极性接面晶体管B2都不被触发导通,第一寄生半导体控制整流器SCR-1也不会被触发导通,不会产生漏电/栓锁(Latch-up)现象。

图5A显示静电放电(ESD)事件发生于电源供应端VCC和输入/输出端(IO)之间的等效放电电路。图5B显示图5A等效电路的寄生元件在图2的静电放电保护装置500A相应位置的示意图。如图5A、图5B所示,除了第一寄生二极管D1和第二寄生二极管D2之外,等效电路还包括由第二P型掺杂区P2和第二N型深阱区DNW2构成的第三寄生二极管D3,以及由第二P型掺杂区P2、第二N型深阱区DNW2和第二P型阱区PW2构成的第三寄生双极性接面晶体管B3(例如寄生PNP BJT)。第三寄生双极性接面晶体管B3的射极(emitter)、基极(base)以及集极(collector)分别由第二P型掺杂区P2、第二N型深阱区DNW2和第二P型阱区PW2构成。等效电路还包括由第四N型掺杂区N4、第二P型阱区PW2和第二N型深阱区DNW2构成的第四寄生双极性接面晶体管B4(例如寄生NPN BJT)。第四寄生双极性接面晶体管B4的射极(emitter)、基极(base)以及集极(collector)分别由第四N型掺杂区N4、第二P型阱区PW2和第二N型深阱区DNW2构成。并且,第三寄生双极性接面晶体管B3的基极(第二N型深阱区DNW2)与第四寄生双极性接面晶体管B4的集极(第二N型深阱区DNW2)电连接,第四寄生双极性接面晶体管B4的基极(第二P型阱区PW2)与第三寄生双极性接面晶体管B3的集极(第二P型阱区PW2)电连接,以构成第二寄生半导体控制整流器SCR-2。此外,第三寄生双极性接面晶体管B3的射极(第二P型掺杂区P2)与电源供应端VCC和第三寄生二极管D3的正极电连接,第三寄生双极性接面晶体管B3的基极(第二N型深阱区DNW2)与第三寄生二极管D3的负极电连接。第四寄生双极性接面晶体管B4的射极(第四N型掺杂区N4)与输入/输出端IO和第二寄生二极管D2的负极电连接,第四寄生双极性接面晶体管B4的基极(第二P型阱区PW2)与第二寄生二极管D2的正极电连接。

如图5A、图5B所示,当静电放电(ESD)事件发生于电源供应端VCC与输入/输出端IO之间时,静电放电电流会流经切换电路300并通过电阻-电容传感器(RC detector)对第二N型掺杂区N2(此时切换成电连接至接地端VSS)输出低位准形成电流路径,上述低位准低于电源供应端VCC的电压位准。并且,切换电路300通过导线220电连接第三寄生双极性接面晶体管B3的基极(第二N型深阱区DNW2)形成电流路径,因此,当切换电路300输出的低位准低于电源供应端VCC的位准时,会对第三寄生双极性接面晶体管B3的射极(第二P型掺杂区P2)-基极(第二N型深阱区DNW2)接面施加顺向偏压,使第三寄生双极性接面晶体管B3被触发导通。另外,静电放电电流会流经切换电路300并通过电阻-电容传感器(RC detector)形成电流路径对其中的N型金属氧化物半导体晶体管(NMOS)302的栅极输出高位准,上述高位准高于接地端VSS的接地位准,使N型金属氧化物半导体晶体管(NMOS)302导通形成流至接地端VSS的电流路径,且会对第二寄生二极管D2以及第四寄生双极性接面晶体管B4的基极(第二P型阱区PW2)-射极(第四N型掺杂区N4)接面施加顺向偏压,使第四寄生双极性接面晶体管B4被触发导通。由于第三寄生双极性接面晶体管B3和第四寄生双极性接面晶体管B4一起被触发导通,从而使第二寄生半导体控制整流器SCR-2被触发导通并形成流至输入/输出端IO的电流路径。上述电流路径提供触发电流(启动电流),接续触发第三寄生双极性接面晶体管B3(PNP)和第四寄生双极性接面晶体管B4(NPN),而形成第二寄生半导体控制整流器SCR-2,此低维持电压(VHold)、低电阻(R)的第二寄生半导体控制整流器SCR-2可以提供电源供应端VCC至从输入/输出端IO的电流路径,将静电荷导离受保护的电路。

当系统中的受保护元件在正常工作(未发生静电放电事件)时,第二N型掺杂区N2切换电连接至电源供应端VCC,第三寄生双极性接面晶体管B3的射极(第二P型掺杂区P2)-基极(第二N型深阱区DNW2)接面不存在顺向偏压,因此第三寄生双极性接面晶体管B3不会被触发导通。并且,第二P型阱区PW2电连接至接地端VSS,其为全系统最低电位。因此,第四寄生双极性接面晶体管B4的基极(第二P型阱区PW2)-射极(第四N型掺杂区N4)接面不存在顺向偏压,因此第四寄生双极性接面晶体管B4不会被触发导通。由于第三寄生双极性接面晶体管B3和第四寄生双极性接面晶体管B4都不被触发导通,第二寄生半导体控制整流器SCR-2也不会被触发导通,不会产生漏电/栓锁(Latch-up)现象。

图6~图10显示对应图2的区域510、520的本发明一些实施例的静电放电保护装置500B~500F的局部剖面示意图。如图6所示,相较于静电放电保护装置500A,静电放电保护装置500B还包括第一栅极结构G1及/或第二栅极结构G2,以及第六P型掺杂区P6及/或第六N型掺杂区N6。第一栅极结构G1设置于第一N型深阱区DNW1内的P型半导体基板200上,且与第一P型掺杂区P1和设置于第一N型深阱区DNW1中的第六P型掺杂区P6部分重叠。在一些实施例中,第六P型掺杂区P6电连接至电源供应端VCC。因此,第一栅极结构G1、第一N型深阱区DNW1中的第一P型掺杂区P1和第六P型掺杂区P6可构成第一P型金属氧化物半导体晶体管PM1。在一些实施例中,第一P型金属氧化物半导体晶体管PM1的第一P型掺杂区P1可与第一N型掺杂区N1构成寄生二极管,其等效于第一寄生二极管D1。上述图6的左半部(包含寄生的第一寄生二极管D1、第一寄生双极性接面晶体管B1、第二寄生双极性接面晶体管B2)会产生如图4A~图4B的功效。

如图6所示,第二栅极结构G2设置于第二P型阱区PW2内的P型半导体基板200上,且与第四N型掺杂区N4和设置于第二P型深阱区PW2中的第六N型掺杂区N6部分重叠。在一些实施例中第六N型掺杂区N6电连接至接地端VSS。因此,第二栅极结构G2、第二P型阱区PW2中的第四N型掺杂区N4和第六N型掺杂区N6可构成第一N型金属氧化物半导体晶体管NM1。在一些实施例中,第一N型金属氧化物半导体晶体管NM1的第四N型掺杂区N4可与第二P型阱区PW2构成寄生二极管,其等效于第二寄生二极管D2。上述图6的右半部(包含寄生的第二寄生二极管D2、第三寄生双极性接面晶体管B3、第四寄生双极性接面晶体管B4)会产生如图5A~图5B的功效。

如图7所示,相较于静电放电保护装置500A,静电放电保护装置500C还包括第三栅极结构G3及/或第四栅极结构G4,以及第七P型掺杂区P7及/或第七N型掺杂区N7。第三栅极结构G3设置于第一P型阱区PW1内的P型半导体基板200上,且与第三P型掺杂区P3和设置于第一P型阱区PW1中的第七N型掺杂区N7部分重叠。在一些实施例中,第三栅极结构G3电连接至电源供应端VCC,且第七N型掺杂区N7电连接至接地端VSS。因此,静电放电保护装置500C的第一电容C1具有稳定电源供应端VCC与接地端VSS之间电压的功能。在正常情况下,切换电路300会输出低位准电压(VSS)到第三P型掺杂区P3,因此在此情况下,此第一电容C1仍具备一般电容的稳压功能。但是,当静电放电事件发生时,切换电路300会输出高位准电压(VCC)到第三P型掺杂区P3,触发第二寄生双极性接面晶体管B2(NPN),并与对应的第一寄生双极性接面晶体管B1(PNP)形成第一寄生半导体控制整流器SCR-1(图4A)。

如图7所示,第四栅极结构G4设置于第二N型深阱区DNW2内的P型半导体基板200上,且与第二N型掺杂区N2和设置于第二N型深阱区DNW2中的第七P型掺杂区P7部分重叠。在一些实施例中,第四栅极结构G4电连接至接地端VSS),且第七P型掺杂区P7电连接至电源供应端VCC。因此,静电放电保护装置500C的第二电容C2具有稳定电源供应端VCC与接地端VSS之间电压的功能。在正常情况下,切换电路300会输出高位准电压(VCC)到N2,因此在此情况下,此第二电容C2仍具备一般电容的稳压功能。但是,当静电放电事件发生时,切换电路300会输出低位准电压(VSS)到N2,触发第三寄生双极性接面晶体管B3(PNP),并与对应的第四寄生双极性接面晶体管B4(NPN)形成第二寄生半导体控制整流器SCR-2(图5A)。

在一些实施例中,当输入/输出端IO的工作电压低于1V时,第三P型掺杂区P3和第二N型掺杂区N2可直接以导线互连而不需电连接至切换电路300(图2)。如图8所示,相较于静电放电保护装置500A,静电放电保护装置500D还包括导线230。导线230设置于P型半导体基板200的上方。并且,导线230的两末端分别直接电连接第三P型掺杂区P3和第二N型掺杂区N2。当静电放电事件的电流脉冲使电源供应端VCC与接地端VSS之间的电压差大于1.2V时,第二N型掺杂区N2会送出电流并使第三寄生双极性接面晶体管B3的射极(第二P型掺杂区P2)-基极(第二N型深阱区DNW2)接面被触发导通。第三P型掺杂区P3会由导线230接收电流使第二寄生双极性接面晶体管B2的基极(第一P型阱区PW1)-射极(第三N型掺杂区N3)接面被触发导通,进而使第一寄生半导体控制整流器SCR-1和第二寄生半导体控制整流器SCR-2被触发导通,将静电荷导离受保护的电路。

在一些实施例中,当输入/输出端IO的工作电压介于1.0V至1.2V之间时,第三P型掺杂区P3和第二N型掺杂区N2可直接以二极管电性互连而不需电连接至切换电路300(图2)。如图9所示,相较于静电放电保护装置500A,静电放电保护装置500E还包括第四二极管D4。第四二极管D4设置于P型半导体基板200的上方。并且,第四二极管D4的正极和负极分别电连接至第二N型掺杂区N2和第三P型掺杂区P3。在一些实施例中,当静电放电事件的电流脉冲使电源供应端VCC与接地端VSS之间的电压差大于1.8V时,第二N型掺杂区N2会送出电流并使第三寄生双极性接面晶体管B3的射极(第二P型掺杂区P2)-基极(第二N型深阱区DNW2)接面被触发导通。第三P型掺杂区P3会由第四二极管D4接收电流使第二寄生双极性接面晶体管B2的基极(第一P型阱区PW1)-射极(第三N型掺杂区N3)接面被触发导通,进而使第一寄生半导体控制整流器SCR-1和第二寄生半导体控制整流器SCR-2被触发导通,将静电荷导离受保护的电路。在一些其他实施例中,若输入/输出端IO的正常工作电压高于1.2V时,第三P型掺杂区P3和第二N型掺杂区N2可改以多个串联的二极管互连。

在一些实施例中,若输入/输出端IO的正常工作电压高于1.2V时,第三P型掺杂区P3和第二N型掺杂区N2可通过N型金属氧化物半导体晶体管NM2和侦测电路电性互连而不需电连接至切换电路300(图2)。如图10所示,相较于静电放电保护装置500A,静电放电保护装置500F还包括第二N型金属氧化物半导体晶体管NM2和由电阻-电容传感器构成的侦测电路300A。第二N型金属氧化物半导体晶体管NM2具有基极BT、栅极GT、第一源/漏极SDT1和第二源/漏极SDT2。在一些实施例中,基极BT电连接至接地端VSS,栅极GT电连接至侦测电路300A,第一源/漏极SDT1电连接至第三P型掺杂区P3,且第二源/漏极SDT2电连接至第二N型掺杂区N2。在一些实施例中,侦测电路300A由电阻-电容传感器(RC detector)构成,其包括电阻、电容、反相器(inverter)以及N型金属氧化物半导体晶体管。

当静电放电事件发生于输入/输出端IO,并且接地端VSS接收到接地位准时,侦测电路300A中的反相器会输出高位准,使第二N型金属氧化物半导体晶体管NM2的N型沟道(Nchannel)导通,进而在第二N型掺杂区N2和第三P型掺杂区P3之间形成通路。第二N型掺杂区N2会送出电流并使第三寄生双极性接面晶体管B3的射极(第二P型掺杂区P2)-基极(第二N型深阱区DNW2)接面被触发导通。第三P型掺杂区P3会由第二N型金属氧化物半导体晶体管NM2接收电流使第二寄生双极性接面晶体管B2的基极(第一P型阱区PW1)-射极(第三N型掺杂区N3)接面被触发导通,进而使第一寄生半导体控制整流器SCR-1和第二寄生半导体控制整流器SCR-2被触发导通,将静电荷导离受保护的电路。

本发明实施例提供一种静电放电保护装置。上述静电放电保护装置包括分别设置在两个N型深阱区中的功能性保护环结构(functional guard ring structure)。上述两个功能性保护环结构电连接至电阻-电容传感器(RC detector)构成的功能电路。可针对发生于输入/输出端IO、电源供应端VCC或接地端VSS任两个端点的静电放电事件,将静电荷导离受保护的电路。当受保护的电路在正常工作(operation)时或在静电放电(ESD)事件发生时,上述两个功能性保护环结构会经由功能电路视情况切换到不同电位(位准)。在静电放电(ESD)事件发生时会使功能性保护环结构中的寄生半导体控制整流器触发导通,以提供额外的放电路径。并且,当受保护元件在正常工作时,功能性保护环结构中的寄生半导体控制整流器不易触发导通,而具有防止栓锁(Latch-up)的功能。在一些实施例中,可针对不同的输入/输出端IO的正常工作电压条件,改以导线、二极管、N型金属氧化物半导体晶体管以及由电阻-电容传感器构成的侦测电路来取代功能电路。

虽然本发明以前述的实施例揭露如上,然而其并非用以限定本发明。本发明所属技术领域中普通技术人员,在不脱离本发明的精神和范围内,可做些许的更动与润饰。因此本发明的保护范围应当以所附的权利要求所界定的为准。

- 静电放电保护装置及制造静电放电保护装置的方法

- 静电放电保护装置和形成静电放电保护装置的方法