半导体结构及其形成方法

文献发布时间:2023-07-07 06:30:04

技术领域

本发明是关于半导体结构及其形成方法,特别是关于经过加工后可作为存储器装置的半导体结构及其形成方法。

背景技术

属于易失性存储器的动态随机存取存储器(Dynamic Random Access Memory,DRAM)具有储存单元密度高、存取速度快及成本低廉的优点,因此广为发展。

然而,随着半导体装置微缩化的趋势,存储器装置的尺寸持续缩减,使得邻近的元件或互连结构的部件之间的电容耦合增加、产生漏电流及/或发生短路的问题,因此对于存储器装置的性能造成不良的影响。

是以,现存的半导体结构及其形成方法仍未在各方面皆彻底的符合要求。所以,关于进一步加工后可作为存储器装置的半导体结构及其形成方法仍有一些问题需要克服。

发明内容

鉴于上述问题,本发明通过设置第一导电柱、界面(interface)层、第二导电柱及中介结构来共同作为介电插塞(dielectric plug),来降低介电插塞与位线结构之间的短路风险,进而改善半导体结构的电性特征。举例而言,通过调整第一导电柱、界面层、第二导电柱及中介结构的相对设置位置、彼此的接触面积及/或材料的种类,来提升第一导电柱与第二导电柱的接触面积。举例而言,随着接触面积的提升来改变流经介电插塞的电流路经,使得介电插塞的整体的电阻减少。据此,有效地减少介于位线结构与介电插塞之间的寄生电容,从而降低介于介电插塞与位线结构之间的短路风险。

根据一些实施例,提供一种半导体结构,包括基板、位线结构、第一导电柱、界面层、第二导电柱及中介结构。基板具有主动区域及隔离结构。位线结构设置于主动区域上。第一导电柱设置于主动区域上。界面层设置于第一导电柱的顶表面上。第二导电柱设置于界面层上。中介结构设置于第一导电柱及位线结构之间。

根据一些实施例,提供一种半导体结构的形成方法,包括:形成主动区域在基板中。形成多个位线结构在主动区域上。相邻的位线结构之间具有开口。形成介电结构在开口中。刻蚀主动区域,以形成凹部在开口中。形成第一导电柱在凹部上。形成界面层在第一导电柱的顶表面上。形成第二导电柱在界面层上。

附图说明

图1是根据本发明的一些实施例,绘示半导体结构的电路布局示意图。

图2至图14是根据本发明的一些实施例,绘示在各个阶段形成半导体结构的剖面示意图。

具体实施方式

参照图1,半导体结构包括:基板100、隔离结构110、主动区域(active area)AA、位线(bit line)BL、字线(word line)WL与储存节点接触物(storage node contact)CC。为便于说明,图1仅简单绘示前述部件,然而本申请的半导体结构可进一步包括其他部件。再者,前述部件的形状并不限制为如图1所示的形状,且尺寸可依工艺或应用所需而调整。

在一些实施例中,第一方向D1与第二方向D2彼此不同,例如,第一方向D1与第二方向D2互相垂直,但是本申请不限于此。举例而言,第一方向D1及第二方向D2可相交一夹角。

位线BL可为多个并可设置于基板100上。每个位线BL可沿着第一方向D1延伸。相邻的位线BL在不同于第一方向D1的第二方向D2上以一距离间隔排列。相邻的位线BL可间隔相同的距离。

字线WL可为多个并可设置于基板100上。每个字线WL可沿着第二方向D2延伸。相邻的字线WL在第一方向D1上以一距离间隔排列。相邻的字线WL可间隔相同的距离。在一些实施例中,字线WL可为埋入式(buried)字线。举例而言,字线WL的栅极结构可低于基板100的顶表面。在另一些实施例中,字线WL的栅极结构可不低于基板100的顶表面。

可形成隔离结构110于基板100中,以通过隔离结构110定义主动区域AA的范围,并使得相邻的两个主动区域AA彼此电性上地分离。主动区域AA可为多个且可形成于基板100中。每个主动区域AA沿着与第一方向D1具有一夹角的方向延伸。主动区域AA的形状仅为范例,而本申请不限于此。

如图1所示,每个主动区域AA跨越两个字线WL,且跨越一个位线BL。每个主动区域AA与所对应的位线BL具有重叠区域与位于重叠区域的两侧的非重叠区域。在每个主动区域AA中,重叠区域中具有位线接触物BC,而非重叠区域中具有储存节点接触物CC。在一些实施例中,对应于一个主动区域AA的两个储存节点接触物CC分别设置于穿过此主动区域AA的两个字线WL的外侧。储存节点接触物CC可与电容器(capacitor)接触,而因此亦可称为电容器接触物(capacitor contact)。在一些实施例中,储存节点接触物CC位于基板100上,且每个储存节点接触物CC位于相邻的两个位线BL之间,且位于相邻的两个字线WL之间。在一些实施例中,每个位线BL在横越所对应的字线WL时,可利用位线接触物BC来电连接所对应的位于两个字线WL之间的区域。

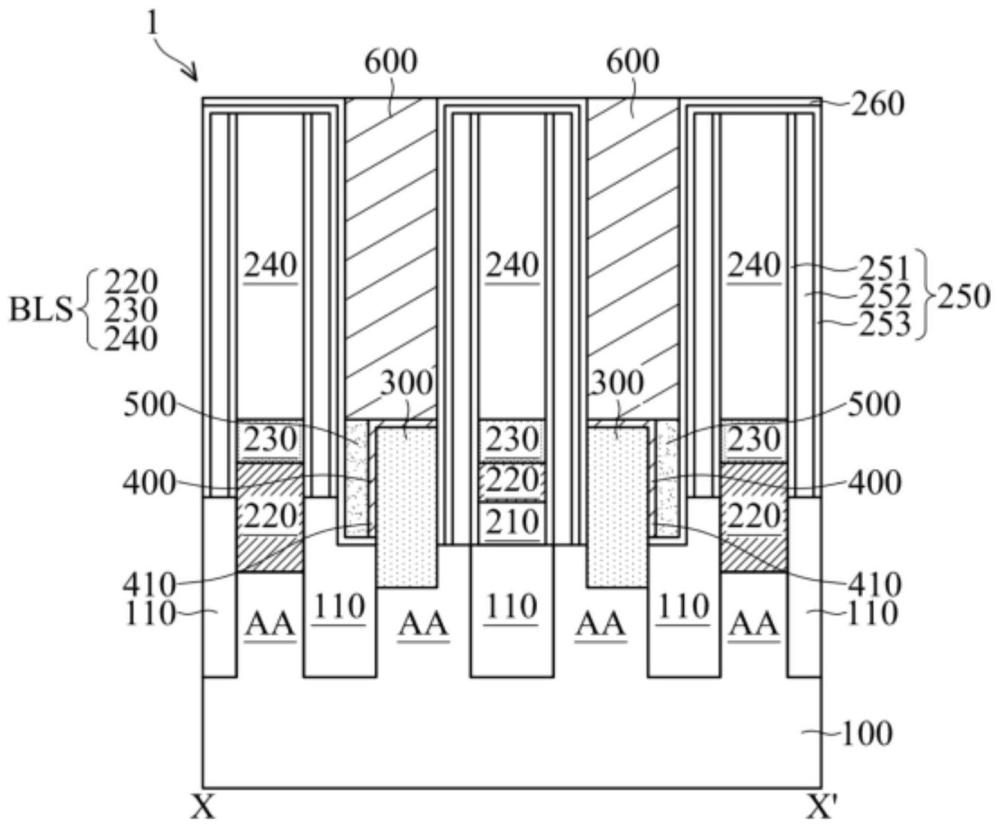

图2至图14是绘示沿着如图1所示的线段XX’撷取的剖面示意图。

参照图2,提供基板100。基板100可为诸如硅晶片(silicon wafer)的晶片、绝缘层上覆半导体(semiconductor-on-insulation,SOI)基板或块材(bulk)半导体基板。基板100可为多层基板或渐变(gradient)基板。在一些实施例中,基板100可为元素半导体,包含硅、锗(germanium);化合物半导体,包含:碳化硅(silicon carbide)、砷化镓(galliumarsenide)、磷化镓(gallium phosphide)、磷化铟(indium phosphide)、砷化铟(indiumarsenide)及/或锑化铟(indium antimonide);合金半导体,包含:SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP及/或GaInAsP;或其任意组合,但本申请不限制于此。在一些实施例中,基板100可为掺杂或未掺杂的半导体基板。

如图2所示,形成主动区域AA及隔离结构110于基板100中。举例而言,先形成主动区域AA于基板100的上部中,再形成隔离结构110于相邻的主动区域AA之间。在一些实施例中,可先形成隔离结构110,再形成主动区域AA于基板100中。隔离结构110可为诸如氧化硅(silicon oxide)的氧化物。在一些实施例中,隔离结构110可通过刻蚀工艺及沉积工艺来形成。

刻蚀工艺可包含干刻蚀、湿法刻蚀、或其他合适的刻蚀方式。干刻蚀可包含但不限于等离子体刻蚀、无等离子体气体刻蚀、溅射刻蚀(sputter etching)、离子研磨(ionmilling)、反应离子刻蚀(reactive ion etching,RIE)。湿法刻蚀可包含但不限于使用酸性溶液、碱性溶液或是溶剂来移除待移除结构的至少一部分。此外,刻蚀工艺也可以是纯化学刻蚀、纯物理刻蚀或其组合。沉积工艺可为化学沉积、物理沉积或其组合。沉积工艺可包括化学气相沉积(chemical vapor deposition,CVD)、有机金属化学气相沉积(MetalOrganic Chemical Vapor Deposition,MOCVD)、原子层沉积(Atomic Layer Deposition,ALD)、其组合、或其类似工艺,但不限于此。隔离结构110可为浅沟槽隔离结构(shallowtrench isolation,STI)。此外,可根据半导体结构的电性需求,进一步形成所需的掺杂区域。

如图2所示,在一些实施例中,形成位线结构BLS于主动区域AA上。位线结构BLS可为多个。位线结构BLS可包括第一导电层220、第二导电层230及遮罩层240。第一导电层220设置于主动区域AA上;第二导电层230设置于第一导电层220上;以及遮罩层240设置于第二导电层230上。第一导电层220及/或第二导电层230可为单层或多层结构。在一些实施例中,可先依序沉积第一导电层220及第二导电层230的材料于基板100上,接着形成经图案化的遮罩层240于第二导电层230上。之后,执行刻蚀工艺以图案化第一导电层220及第二导电层230的材料,而获得第一导电层220及第二导电层230。

第一导电层220及/或第二导电层230可包括导电材料。导电材料可包含多晶硅(polycrystalline silicon)、非晶硅(amorphous silicon)、诸如钨、金、银、铜、钴或其类似物的金属、金属氮化物、导电金属氧化物、其他合适的材料或其组合。举例而言,第一导电层220可包括多晶硅,第二导电层230可包括钨。在一些实施例中,遮罩层240可为硬遮罩层。遮罩层240的材料可包括氧化物、氮化物、氮氧化物、碳化物或其组合。在一些实施例中,遮罩层240可为诸如氮化硅的氮化物。

如图2所示,在一些实施例中,形成位线介电层210于隔离结构110上。在一些实施例中,在形成第一导电层220于基板100上之前,形成位线介电层210于隔离结构110上。在此须说明的是,由于图2显示沿着图1的线段XX’撷取的剖面示意图,因此在中间的两个主动区域AA之间的隔离结构110上形成位线介电层210。位线介电层210可包括氧化物、氮化物、氮氧化物、高介电常数(high-k)材料或其组合。在一些实施例中,位线介电层210可包括诸如氧化硅的氧化物。位线介电层210可为绝缘层。在一些实施例中,可通过沉积工艺来形成位线介电层210。在此实施例中,位于图2中的最左边及最右边的主动区域AA上方的位线结构BLS可与如图1所示的位线接触物BC电性连接,或者位线结构BLS可作为位线接触物BC的一部分。

如图2所示,可进一步形成间隔物结构250于位线结构BLS的侧表面及顶表面上。间隔物结构250可提供位线结构BLS隔离特性。间隔物结构250可为氧化物、氮化物或其组合。例如间隔物结构250可为氧化硅或氮化硅。

间隔物结构250可为单层结构或多层结构。举例而言,间隔物结构250可包括第一间隔物251、第二间隔物252及第三间隔物253。第一间隔物251可设置于位线结构BLS的侧表面上。具体而言,第一间隔物251接触隔离结构110、第一导电层220、第二导电层230及遮罩层240。在一些实施例中,第一间隔物251接触位线介电层210。第二间隔物252可设置于第一间隔物251的侧表面上,且第一间隔物251介于第二间隔物252及位线结构BLS之间。第三间隔物253可设置于第二间隔物252的侧表面上,且第二间隔物252介于第一间隔物251及第三间隔物253之间。在一些实施例中,第三间隔物253可毯覆式地设置在第二间隔物252、第一间隔物251及遮罩层240上。

前述间隔物结构250可通过前述沉积工艺及刻蚀工艺来形成。在一些实施例中,第一间隔物251及第三间隔物253可包括氮化硅,且第二间隔物252可包括氧化硅,因此间隔物结构250可为氮化物-氧化物-氮化物(nitride-oxide-nitride,NON)结构,然而本申请不限于此。

在一些实施例中,可顺应性地(conformally)形成衬层260于主动区域AA、隔离结构110、间隔物结构250及位线结构BLS上。衬层260可为诸如氮化硅的氮化物。在一些实施例中,衬层260可为单层或多层结构,或者可省略衬层260。可通过使用沉积工艺来形成衬层260。

如图2所示,相邻的位线结构BLS之间具有开口OP。开口OP可形成于衬层260上,可通过衬层260的形状对应形成开口OP。图2是沿着如图1所示的线段XX’撷取的剖面示意图,且其显示两个开口OP。然而,开口OP的数量仅为范例,且开口OP的数量会随着沿着图1中的不同线段撷取的剖面示意图而不同,因此本申请不限于此。在一些实施例中,开口OP具有第一高度H1及第一宽度W1。

在下文中,针对形成于开口OP中且与电容器电性连接的介电插塞进行详细说明。

参照图3,形成介电材料270在开口OP中。可通过沉积工艺来形成介电材料270,以使介电材料270填充于开口OP中。在一些实施例中,介电材料270完全填充开口OP。介电材料270接触开口OP的侧表面及底表面。介电材料270可包括氧化物、氮化物、氮氧化物、碳化物或其组合。在一些实施例中,介电材料270可为氧化硅。

参照图4,形成光阻层PR于介电材料270上。光阻层PR覆盖衬层260及介电材料270。在一些实施例中,光阻层PR覆盖介电材料270的一部分且暴露介电材料270的另一部分。光阻层PR覆盖介电材料270的宽度为第二宽度W2。第二宽度W2小于第一宽度W1。在一些实施例中,光阻层PR覆盖介电材料270的顶表面的总面积的20%、30%、40%、50%、60%、70%、80%、90%或前述数值的任意组合的范围,来调整介电材料270及后续形成的第一导电柱的顶表面的面积比例。亦即,可通过光阻层PR的覆盖面积来调整后续形成的中介结构的宽度。

参照图5,接续上述,执行刻蚀工艺,以通过光阻层PR作为刻蚀遮罩,来图案化介电材料270,从而形成经图案化的介电材料271并暴露开口OP的侧表面S1及底表面S2。介电材料271覆盖开口OP的相对侧表面中的一侧表面,且暴露相对侧表面中的另一侧表面S1。介电材料271暴露开口OP的底表面S2的一部分。经图案化的介电材料271的宽度与第二宽度W2实质上相同。介电材料271的宽度可根据电性需求来调整。介电材料271可覆盖隔离结构110的顶表面。在一些实施例中,介电材料271可进一步覆盖主动区域AA的顶表面。在一些实施例中,可执行诸如灰化(ashing)工艺及/或湿法去除(wet strip)的移除工艺来移除光阻层PR。

参照图6,接续上述,执行第一刻蚀工艺,以缩减介电材料271的高度,使得介电材料271的顶表面低于位线结构BLS的顶表面,而形成介电结构272在开口OP中。在一些实施例中,介电结构272具有第二高度H2。第二高度H2小于第一高度H1。在一些实施例中,介电结构272的高度与第二导电层230的高度实质上相同。由于邻近第二导电层230处易产生较大的寄生电容,因此当介电结构272的高度与第二导电层230的高度实质上相同时,能够通过介电结构272来降低寄生电容。在一些实施例中,可根据电性需求调整介电结构272的第二高度H2。在一些实施例中,第一刻蚀工艺为回蚀工艺。可以通过回蚀工艺参数来控制回蚀的深度,进而控制介电结构272的高度。

如图6所示,对主动区域AA执行第二刻蚀工艺,以形成凹部273在开口OP中。具体而言,对主动区域AA及部分衬层260执行第二刻蚀工艺,以移除部分衬层260且移除主动区域AA的一部分,而形成具有深度D的凹部273。在一些实施例中,凹部273介于相邻的隔离结构110之间。在执行第二刻蚀工艺之后,暴露主动区域AA。在一些实施例中,凹部273的底表面低于主动区域AA的顶表面。在另一些实施例中,执行第二刻蚀工艺至暴露主动区域AA即停止,换句话说,仅暴露主动区域AA而不移除主动区域AA的一部分。

需特别说明的是,执行第二刻蚀工艺以移除主动区域AA的一部分,能够提升后续形成的介电插塞与主动区域AA之间的接触面积。具体而言,介电插塞与主动区域AA之间的接触面积可进一步包括接触主动区域AA的侧表面的一部分。举例而言,在主动区域AA中的凹部273的侧表面亦能与后续形成的介电插塞接触。因此,能够通过提升介电插塞与主动区域AA之间的接触面积,来调整流经主动区域AA及介电插塞的电流路径,进而降低介电插塞与位线结构之间的短路风险。

此外,在一些实施例中,用于缩减介电材料271的高度的第一刻蚀工艺以及用于形成凹部273的第二刻蚀工艺可在同一道工艺中执行。举例而言,在执行第一刻蚀工艺来缩减介电材料271的高度的同时,可通过控制介电材料271及衬层260与主动区域AA的材料的刻蚀选择比及刻蚀参数,同时刻蚀衬层260及主动区域AA,以移除经介电结构272暴露的衬层260且使得主动区域AA凹入。因此,可降低工艺成本。在一些实施例中,用于缩减介电材料271的高度的第一刻蚀工艺以及用于形成凹部273的第二刻蚀工艺可在不同道工艺中先后执行。

参照图7,形成第一导电柱300在凹部273上。在一些实施例中,毯覆式地形成第一导电柱300的材料在开口OP中,接着通过回蚀工艺来移除第一导电柱300的材料,以使第一导电柱300的顶表面与介电结构272的顶表面齐平。第一导电柱300可包括导电材料。导电材料可包含多晶硅(polycrystalline silicon)、非晶硅(amorphous silicon)、诸如钨、金、银、铜、钴或其类似物的金属、金属氮化物、导电金属氧化物、其他合适的材料或其组合。在一些实施例中,第一导电柱300可包括多晶硅。

第一导电柱300设置于主动区域AA上。在一些实施例中,第一导电柱300覆盖经暴露的开口OP的侧表面S1的一部分。举例而言,第一导电柱300覆盖开口OP的侧表面S1的下部,且暴露开口OP的侧表面S1的上部。在一些实施例中,第一导电柱300完全覆盖经暴露的开口OP的底表面S2。在一些实施例中,第一导电柱300接触开口OP的相对侧表面S1中的一者,介电结构272接触开口OP的相对侧表面S1中的另一者,且第一导电柱300与介电结构272直接接触。在一些实施例中,第一导电柱300与衬层260、介电结构272、隔离结构110及主动区域AA接触。在一些实施例中,介电结构272介于第一导电柱300与位线结构BLS之间。在一些实施例中,第一导电柱300的顶表面为平坦表面,因此可提升第一导电柱300的可靠性。在一些实施例中,第一导电柱300的形状可不限于柱状。

参照图8,通过刻蚀工艺来移除介电结构272。在一些实施例中,可以第一导电柱300作为刻蚀遮罩,并通过湿法刻蚀工艺来移除介电结构272。移除介电结构272,以暴露位于第一导电柱300及位线结构BLS之间的开口OP的侧表面及底表面。

参照图9,形成界面层400于第一导电柱300的顶表面上。在一些实施例中,在移除介电结构272之后,形成界面层400。在一些实施例中,界面层400顺应式地形成在第一导电柱300的顶表面及侧表面上。换句话说,界面层400可包括延伸部分410。前述界面层400的延伸部分410可设置于第一导电柱300的侧表面上。在一些实施例中,前述界面层400的延伸部分410可介于第一导电柱300及位线结构BLS之间。在另一些实施例中,界面层400可形成于第一导电柱300的顶表面上,且界面层400可至少覆盖第一导电柱300的侧表面的一部分。在又一些实施例中,界面层400可形成于第一导电柱300的顶表面上,且界面层400可完全暴露第一导电柱300的侧表面。在本申请的半导体结构中,对于电阻的影响程度较大的因素包括第一导电柱300与主动区域AA的接触面积,所以在界面层400至少形成在第一导电柱300的顶表面上的情况中,即能有效地操作本申请的半导体结构。在一些实施例中,界面层400可为拐杖形、倒L形或其他合适的形状。

界面层400可以作为用于提升相容性的缓冲层,来提升后续形成的半导体结构的介电插塞可靠性。在一些实施例中,界面层400可包括硅化钴(cobalt silicide)。由于界面层400包括硅化钴,因此界面层400可提升第一导电柱300及后续形成于界面层400上的第二导电柱之间的相容性,以提升整体介电插塞的可靠性。

参照图10,形成第二导电柱600在界面层400上,以获得本申请的半导体结构1。在一些实施例中,用于形成第二导电柱600的材料及形成方法可与用于形成第一导电柱300的材料及形成方法相同或不同。在一些实施例中,第二导电柱600包括钨。

如图10所示,可形成中介结构500在第二导电柱600的下方。在一些实施例中,中介结构500设置于第一导电柱300及位线结构BLS之间。在一些实施例中,中介结构500的顶表面可与界面层400的顶表面齐平。在一些实施例中,用于形成中介结构500的材料及形成方法与用于形成第二导电柱600的材料及形成方法相同或不同。

在一些实施例中,中介结构500的材料与第二导电柱600的材料相同。在一些实施例中,中介结构500及第二导电柱600皆为钨。举例而言,毯覆式地沉积诸如钨的材料于衬层260及界面层400上,以同时形成中介结构500及第二导电柱600。接着,执行平坦化工艺,以使第二导电柱600的顶表面与衬层260的顶表面齐平。换句话说,中介结构500及第二导电柱600可为整体化地形成。在一些实施例中,平坦化工艺可包含化学机械研磨(chemicalmechanical polishing,CMP)工艺,但本申请不限于此。在一些实施例中,在移除介电结构272之后,整体化地形成中介结构500及第二导电柱600在如图9所示的开口OP中。

在一些实施例中,毯覆式地沉积中介结构500及第二导电柱600的材料时,可通过调整如图5所示的第二宽度W2及如图6所示的第二高度H2,来改变介于衬层260及界面层400的延伸部分410之间的沟槽的深宽比。因此,能够通过调整沟槽的深宽比,来调整沉积中介结构500及第二导电柱600的材料的沉积参数及沉积轮廓。在一些实施例中,毯覆式地沉积中介结构500及第二导电柱600的材料,以使中介结构500及第二导电柱600的材料完全填充介于衬层260及界面层400的延伸部分410之间的沟槽。换句话说,中介结构500受到衬层260、界面层400的延伸部分410及第二导电柱600围绕。在一些实施例中,以第二导电柱600的中心轴作为对称轴时,本申请提供一种具有非对称结构的介电插塞。

在此实施例中,界面层400的延伸部分410介于中介结构500及第一导电柱300之间。在一些实施例中,中介结构500介于延伸部分410及位线结构BLS之间。中介结构500介于延伸部分410及衬层260之间。第一导电柱300的底表面低于中介结构500的底表面。因此,可提升第一导电柱300与中介结构500及第二导电柱600之间的接触面积。据此,通过设置中介结构500来调整流经整体介电插塞的电流路径,从而减少介于介电插塞与位线结构BLS之间的短路风险。举例而言,减少介于第一导电柱300与位线结构BLS中的第一导电层220及/或第二导电层230之间的短路风险。

在另一些实施例中,中介结构500的材料与第二导电柱600的材料不同。在此实施例中,可先形成中介结构500,再形成第二导电柱600。

如图10所示,其为沿着图1的线段XX’撷取的剖面示意图。在此剖面图中,沿着如图1所示的第二方向D2横跨五个隔离结构110及四个主动区域AA,其中前述四个主动区域AA分别介于前述五个隔离结构110之间。在此情况中,在正中间的隔离结构110上具有位线介电层210及位线结构BLS,而能够使位线介电层210及位线结构BLS整体化视为虚设(dummy)位线结构。换句话说,图10显示两个相邻的位线结构BLS之间具有一个虚设位线结构的剖面示意图。在图10中,中介结构500邻近位线结构BLS设置且远离虚设位线结构。在一些实施例中,中介结构500及第一导电柱300介于位线结构BLS及虚设位线结构之间。其中,相较于第一导电柱300,中介结构500更靠近位线结构BLS。以虚设位线结构的中心轴作为对称轴,可对称设置第一导电柱300、界面层400、中介结构500及第二导电柱600。换句话说,以虚设位线结构的中心轴作为对称轴时,本申请提供一种对称结构。

参照图11,显示本申请的半导体结构2的剖面示意图。为便于说明,省略相似与重复的叙述。图11为接续图9所示的半导体结构进行进一步工艺的剖面示意图。接续图9,如图11所示,形成第二导电柱600在界面层400上,以获得本申请的半导体结构2。在此实施例中,通过调整介于衬层260及界面层400的延伸部分410之间的沟槽的深宽比,来改变毯覆式地沉积中介结构500的材料的沉积轮廓。

在此实施例中,形成中介部件510于第二导电柱600下方,且形成气隙AG于中介部件510下方。在一些实施例中,沉积中介结构500的材料在如图9所示的开口OP中,以使中介结构500的材料的底表面介于界面层400的顶表面及底表面之间。举例而言,中介结构500的材料的底表面可介于界面层400的顶表面及延伸部分410的底表面之间。

在一些实施例中,中介部件510的材料与第二导电柱600的材料可为相同。换句话说,中介部件510与第二导电柱600为整体化形成。举例而言,毯覆式地沉积第二导电柱600的材料来同时形成第二导电柱600与包括中介部件510及气隙AG的中介结构500。换句话说,在毯覆式地沉积第二导电柱600的材料时,可部分填充第二导电柱600的材料在介于衬层260及界面层400的延伸部分410之间的沟槽中,以形成气隙AG。在一些实施例中,中介部件510与第二导电柱600皆为钨。

在一些实施例中,中介部件510及气隙AG可整体化地视为中介结构500。在一些实施例中,中介部件510及气隙AG分别占据中介结构500的面积可根据沟槽的深宽比及沉积工艺的参数来调整。在一些实施例中,中介部件510占据中介结构500的面积可小于、实质上等于或大于气隙AG占据中介结构500的面积。在一些实施例中,气隙AG的顶表面可低于或齐平于第一导电柱300或界面层400的顶表面。在一些实施例中,中介部件510接触第一导电柱300、界面层400及第二导电柱600。

在一些实施例中,气隙AG可包括惰性气体、空气或是为真空状态。在此实施例中,由于中介结构500可包括设置于中介部件510下方的气隙AG,因此能够有效地降低寄生电容,而降低介于介电插塞及位线结构BLS之间的短路风险。

参照图12,显示本申请的半导体结构3的剖面示意图。为便于说明,省略相似与重复的叙述。图12为接续图9所示的半导体结构进行进一步工艺的剖面示意图。接续图9,如图12所示,形成第二导电柱600在界面层400上,以获得本申请的半导体结构3。如图12所示,第二导电柱600的底表面与界面层400的顶表面齐平,且气隙AG形成于第二导电柱600下方。在一些实施例中,气隙AG直接接触第二导电柱600。在此实施例中,气隙AG可视为中介结构。因此,在中介结构实质上为气隙AG的情况中,能够有效地减少介于第一导电柱300及位线结构BLS之间的寄生电容,而能够降低短路风险。

参照图13,显示本申请的另一实施例的半导体结构的剖面示意图。为便于说明,省略相似与重复的叙述。图13为接续图7所示的半导体结构进行进一步工艺的剖面示意图。接续图7,如图13所示,形成界面层400于第一导电柱300的顶表面上。在一些实施例中,由于界面层400可包括硅化钴,第一导电柱300可包括多晶硅,且介电结构272可包括氧化硅。由于材料的相容性的问题,界面层400可仅形成于第一导电柱300的顶表面上。在此实施例中,保留介电结构272于第一导电柱300及位线结构BLS之间,以省略移除介电结构272及/或进一步形成中介结构的工艺步骤,进而降低工艺成本。在一些实施例中,由于界面层400可通过与第一导电柱300中的多晶硅来形成,因此界面层400的顶表面与介电结构272的顶表面齐平。

如图14所示,形成第二导电柱600于如图13所示的结构上,以获得本申请的半导体结构4。在一些实施例中,第二导电柱600接触界面层400及介电结构272。在一些实施例中,第二导电柱600的底表面与界面层400及介电结构272的顶表面齐平。在此实施例中,介电结构272可视为中介结构。由于介电结构272可于前述工艺中作为刻蚀遮罩,并作为设置在第一导电柱300及位线结构BLS之间的中介结构,所以能够减少工艺步骤并降低工艺成本。此外,由于介电结构272可包括诸如氧化硅的介电材料,因此能够降低寄生电容,以减少介于第一导电柱300及位线结构BLS之间的短路风险。

在一些实施例中,可执行进一步工艺于本申请的半导体结构1、2、3及/或4上,以形成存储器装置。举例而言,在一些实施例中,根据电性需求,可执行掺杂工艺。在一些实施例中,掺质可为诸如硼的P型掺质或诸如磷的N型掺质。

综上所述,本申请的半导体结构包括由第一导电柱、界面层、第二导电柱及中介结构共同作为存储器装置中用于连接电容器的介电插塞。

本申请通过设置与第二导电柱的材料相同的中介结构于第一导电柱及位线结构之间,将中介结构视为第二导电柱的延伸部分,来增加第二导电柱与第一导电柱的接触面积,来降低第一导电柱与位线结构之间的短路风险。本申请通过设置包括气隙或是整体为气隙的中介结构于第一导电柱及位线结构之间,降低介电插塞的寄生电容,来降低第一导电柱与位线结构之间的短路风险。本申请通过设置包括诸如氧化硅的介电材料的中介结构于第一导电柱及位线结构之间,降低介电插塞的寄生电容及/或减少工艺步骤,来降低第一导电柱与位线结构之间的短路风险及/或降低形成方法的工艺成本。

此外,本申请通过设置具有低于第二导电柱及中介结构的底表面的第一导电柱,来增加第一导电柱与第二导电柱及/或中介结构的接触面积。因此能够通过调整流经第一导电柱、第二导电柱及中介结构的电流,来降低短路的风险。再者,本申请通过设置倒L形的界面层,来提升第一导电柱及第二导电柱的相容性,以改善第一导电柱及第二导电柱的可靠性。同时,本申请提供在相邻的位线结构之间具有虚设位线结构的半导体结构,所以在此剖面方向观察时,能够获得具有对称于虚设位线结构的半导体结构。据此,通过设置远离虚设位线结构且邻近虚设位线结构的中介结构,来降低短路风险。

前述内容概述本申请的数个实施例的部件,使得所属技术领域中具有通常知识者可以更好地理解本申请的态样。所属技术领域中具有通常知识者应当理解的是,他们可以容易地将本申请用作改变、取代、替代及/或修改其他工艺及结构的基础,以实现与本文介绍的实施例相同的目的及/或达到相同的优点。所属技术领域中具有通常知识者亦应理解的是,这样的等效构造未脱离本申请的精神及范畴,且在不脱离本申请的精神及范畴的情况下,他们可以在本文中进行各种改变、替换及变更。

- 形成具有经改善的平坦化均匀性的半导体装置与结构的方法及所得的结构与半导体装置

- 用于半导体器件的自对准结构、半导体结构及其形成方法

- 半导电石墨烯结构、形成此类结构的方法及包含此类结构的半导体装置

- 电容结构、包括电容结构的半导体管芯及其形成方法

- 半导体结构及其形成方法、测量电阻的方法

- 半导体封装结构、半导体封装结构的形成方法以及半导体组装结构的形成方法

- 半导体封装结构、半导体封装结构的形成方法以及半导体组装结构的形成方法