一种集成式LED芯片

文献发布时间:2024-01-17 01:28:27

技术领域

本发明涉及半导体技术领域,尤其涉及一种集成式LED芯片。

背景技术

发光二极管(Light Emitting Diode,LED)是一种可将电流转换成特定波长范围的光电半导体元件,其发光原理为电子在n型半导体与p型半导体间移动的能量差,以光的形式释放能量,因此发光二极管被称为冷光源,其具有低功耗、尺寸小亮度高、易与集成电路匹配、可靠性高等优点,作为光源被广泛应用。并且,随着LED技术的成熟,直接利用LED作为自发光显示点像素的Mini LED和Micro LED(微型发光二极管)显示器的技术也逐渐被广泛应用。

Mini LED其芯片尺寸通常介于80~200μm之间,作为下一代显示技术的Mini LED技术,近两年已突破技术瓶颈,得到迅猛发展,已逐渐进入到户内高端显示、会议一体机、车载照明等领域。Micro LED是指芯片尺寸比Mini LED更小的LED芯片,其尺寸通常小于50μm,被认为是最有可能取代OLED,成为下一代LED显示技术,相比于Mini LED,由于其尺寸小,其间距可以做到P0.4以下,广泛应用于具有要求更高亮度、超高解析度和更高色彩饱和度的设备与场所。虽然Micro LED相较于Mini LED有诸多优点,但其仍有诸多技术难题需要解决,其中最主要的是制作成本、测试及返修问题。

发明内容

本发明的目的在于提供一种集成式LED芯片,所述集成式LED芯片可以解决MicroLED无法测试分选,修复成本高的问题。

为了实现上述发明目的,本发明提供以下技术方案:

本发明提供了一种集成式LED芯片,包括生长衬底1;

位于所述生长衬底1表面的外延结构2,所述外延结构2的上表面包括正极性层和刻蚀后暴露出的负极性层;

位于所述外延结构2的正极性层表面的透明导电层3和位于所述透明导电层3表面和所述外延结构2暴露在外的负极性层表面的扩展电极4;

位于暴露在外的所述外延结构2负极性层、透明导电层3、扩展电极4和生长衬底1的表面的透明绝缘层5;

贯穿所述透明绝缘层5至所述扩展电极4的透明绝缘层窗口6;

在位于所述透明绝缘层3和所述透明绝缘层窗口6处的扩展电极表面设置的布线线路7;

位于所述布线线路7表面的Micro LED 8;

位于所述透明绝缘层5、布线线路7和Micro LED 8表面的反射绝缘层9;

贯穿所述反射绝缘层9至布线线路7的反射绝缘层窗口10;

位于所述反射绝缘层9和反射绝缘层窗口10处的布线线路7表面的焊线电极11。

本发明还提供了一种集成式LED芯片,包括第一生长衬底1-1;

位于所述生长衬底表面的第一外延结构2-1;所述第一外延结构2-1为经过刻蚀处理的外延结构,所述第一外延结构2-1的上表面包括正极性层和刻蚀后暴露出的负极性层;所述第一外延结构2-1间隔设置,相邻两第一外延结构2-1之间的间隔通过对所述第一生长衬底表面的第一外延结构2-1进行刻蚀实现;

位于所述第一外延结构2-1的正极性层表面的第一透明导电层3-1;

位于所述第一透明导电层3-1表面的第一透明键合层12-1,所述第一透明键合层12-1的表面尺寸小于所述第一透明导电层3-1的表面尺寸;

位于所述第一透明键合层12-1表面的第二透明键合层12-2,所述第二透明键合层12-2的表面尺寸与所述第一透明键合层12-1的表面尺寸相同;

位于所述第二透明键合层12-2表面的第二透明导电层3-2,所述第二透明导电层3-2的表面尺寸与所述第二透明键合层12-2的表面尺寸相同;

位于所述第二透明导电层3-2表面的第二外延结构2-2,所述第二外延结构2-2的表面尺寸小于所述第二透明导电层3-2的表面尺寸;

位于所述第一外延结构2-1的负极性层、第一透明导电层3-1、第二透明导电层3-2和第二外延结构2-2的负极性层表面部分区域的扩展电极4;

位于所述第一生长衬底1-1、第一外延结构2-1的负极性层、第一透明导电层3-1、第二外延结构2-2的负极性层、第二透明导电层3-2和位于第一透明导电层3-1和第二外延结构2-1的负极型表面的扩展电极4表面的透明绝缘层5;

贯穿所述透明绝缘层5至位于所述第一外延结构2-1的负极性层和第二透明导电层3-2处的扩展电极4的透明绝缘层窗口6;

位于所述透明绝缘层5和透明绝缘层窗口6处的扩展电极表面的布线线路7;

位于所述布线线路7上的Micro LED 8;

位于暴露的所述透明绝缘层5、布线线路7和Micro LED 8表面的反射绝缘层9;

贯穿所述反射绝缘层9至布线线路7的反射绝缘层窗口10;

位于所述反射绝缘层9和反射绝缘层窗口10处的布线线路7之上的焊线电极11。

本发明还提供了一种集成式LED芯片,包括生长衬底1;

位于所述生长衬底表面的外延结构2;所述外延结构2为经过刻蚀处理的外延结构,所述外延结构2的上表面包括正极性层和刻蚀后暴露出的负极性层;所述外延结构2间隔设置,相邻两外延结构2之间的间隔通过对所述衬底表面的外延结构进行刻蚀实现;

位于所述外延结构2表面的透明导电层3;

位于所述透明导电层3的表面和外延结构2中暴露的负极性层表面的扩展电极4;

位于所述生长衬底1表面、外延结构2中暴露的负极型表面和扩展电极4表面的透明粘结层1;

位于所述透明粘结层13表面的Micro LED 8;

位于所述透明粘结层13和Micro LED8表面的反射绝缘层9;

贯穿所述反射绝缘层9至扩展电极4和Micro LED8中的焊线电极(所述Micro LED8本身包括的焊线电极)的反射绝缘层窗口6;

位于所述反射绝缘层9、反射绝缘层窗口6处的扩展电极4和Micro LED8表面的布线线路7;

位于所述反射绝缘层9、布线线路7和Micro LED8表面的绝缘层15;

贯穿所述绝缘层15至布线线路7的绝缘层窗口14;

位于所述绝缘层15、绝缘层窗口14处的布线线路表面的焊线电极11。

优选的,第一外延结构2-1由下到上包括依次层叠设置的负极性层、量子阱发光层和正极性层;

所述第二外延结构2-2由下到上包括依次层叠设置的正极性层、量子阱发光层和负极性层。

优选的,所述外延结构2由下到上独立的包括依次层叠设置的负极性层、量子阱发光层和正极性层。

优选的,所述扩展电极4包括正极型扩展电极和负极型扩展电极;

位于所述透明导电层3表面的扩展电极4为正极型扩展电极,位于所述外延结构暴露在外的负极型表面的扩展电极4为负极型扩展电极4。

优选的,所述扩展电极4由下到上优选包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层;

所述布线线路7由下到上包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层。

优选的,所述布线线路7包括区域一、区域二、区域三和区域四;

所述区域一的布线线路7和所述正极型扩展电极互连;

所述区域二的布线线路7和所述负极型扩展电极互连;

所述区域三和区域四的布线线路7分别和不同的Micro LED8的正极通过共晶键合的方式互连;

所述区域二的布线线路7和Micro LED8的负极通过共晶键合的方式互连。

优选的,所述布线线路7包括区域一、区域二、区域三和区域四;

区域一的布线线路7与位于位于第一外延结构2-1的负极性层和第二透明导电层3-2处的扩展电极4互连;

区域一的布线线路7通过共晶键合的方式与Micro LED8的负极互连;

区域三的布线线路7通过透明绝缘层窗口6与位于第一透明导电层3-1表面的扩展电极4互连;

区域四的布线线路7通过透明绝缘层窗口和位于第二透明导电层3-2表面的扩展电极4互连;同时,区域二的布线线路7通过共晶键合的方式与Micro LED8的正极互连。

优选的,所述透明绝缘层窗口6、反射绝缘层窗口10和绝缘层窗口14的形状为圆形、椭圆形、方形或菱形;

所述透明绝缘层窗口6、反射绝缘层窗口10和绝缘层窗口14的孔径大小从底面到顶面逐渐增加。

本发明提供了一种集成式LED芯片,所述集成式LED芯片通过把RGB micro LED子像素集成制作成一个mini LED像素芯片。该像素芯片可以有效的利用micro LED芯片尺寸小,成本低的优势,同时可以做到像mini LED一样可以点测分选,解决micro LED返修成本高的问题,并且依托于现有的mini LED产业链迅速量产。

附图说明

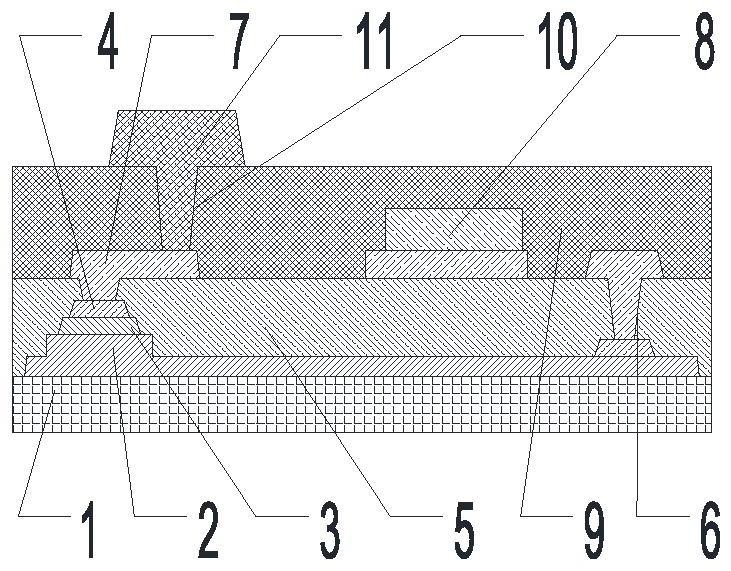

图1为本发明实施例1所述集成式LED芯片的结构示意图;

图2为实施例1所述集成式LED芯片的制备流程示意图;

图3为实施例1所述集成式LED芯片制备过程中步骤S101的结构示意图;

图4为实施例1所述集成式LED芯片制备过程中步骤S102的结构示意图;

图5为实施例1所述集成式LED芯片制备过程中步骤S103的结构示意图;

图6为实施例1所述集成式LED芯片制备过程中步骤S104的结构示意图;

图7为实施例1所述集成式LED芯片制备过程中步骤S105的结构示意图;

图8为实施例1所述集成式LED芯片制备过程中步骤S106的结构示意图;

图9为实施例1所述集成式LED芯片制备过程中步骤S107的结构示意图;

图10为实施例1所述集成式LED芯片制备过程中步骤S108的结构示意图;

图11为实施例1所述集成式LED芯片制备过程中步骤S109的结构示意图;

图12为实施例1所述集成式LED芯片制备过程中步骤S110的结构示意图;

图13为实施例1所述集成式LED芯片制备过程中步骤S112的结构示意图;

图14为本发明实施例2所述集成式LED芯片的结构示意图;

图15为实施例2所述集成式LED芯片的制备流程示意图;

图16为实施例2所述集成式LED芯片制备过程中步骤S201的结构示意图;

图17为实施例2所述集成式LED芯片制备过程中步骤S202的结构示意图;

图18为实施例2所述集成式LED芯片制备过程中步骤S203的结构示意图;

图19为实施例2所述集成式LED芯片制备过程中步骤S204的结构示意图;

图20为实施例2所述集成式LED芯片制备过程中步骤S205的结构示意图;

图21为实施例2所述集成式LED芯片制备过程中步骤S206的结构示意图;

图22为实施例2所述集成式LED芯片制备过程中步骤S207的结构示意图;

图23为实施例2所述集成式LED芯片制备过程中步骤S208的结构示意图;

图24为实施例2所述集成式LED芯片制备过程中步骤S209的结构示意图;

图25为实施例2所述集成式LED芯片制备过程中步骤S210的结构示意图;

图26为实施例2所述集成式LED芯片制备过程中步骤S211的结构示意图;

图27为实施例2所述集成式LED芯片制备过程中步骤S212的结构示意图;

图28为实施例2所述集成式LED芯片制备过程中步骤S213的结构示意图;

图29为实施例2所述集成式LED芯片制备过程中步骤S215的结构示意图;

图30为本发明实施例3所述集成式LED芯片的结构示意图;

图31为实施例3所述集成式LED芯片的制备流程示意图;

图32为实施例3所述集成式LED芯片制备过程中步骤S301的结构示意图;

图33为实施例3所述集成式LED芯片制备过程中步骤S302的结构示意图;

图34为实施例3所述集成式LED芯片制备过程中步骤S303的结构示意图;

图35为实施例3所述集成式LED芯片制备过程中步骤S304的结构示意图;

图36为实施例3所述集成式LED芯片制备过程中步骤S305的结构示意图;

图37为实施例3所述集成式LED芯片制备过程中步骤S306的结构示意图;

图38为实施例3所述集成式LED芯片制备过程中步骤S307的结构示意图;

图39为实施例3所述集成式LED芯片制备过程中步骤S308的结构示意图;

图40为实施例3所述集成式LED芯片制备过程中步骤S309的结构示意图;

图41为实施例3所述集成式LED芯片制备过程中步骤S310的结构示意图;

图42为实施例3所述集成式LED芯片制备过程中步骤S311的结构示意图;

图43为实施例3所述集成式LED芯片制备过程中步骤S313的结构示意图;

其中,1为生长衬底,1-1为第一生长衬底,1-2为第二生长衬底,2为外延结构,2-1为第一外延结构,2-2为第二外延结构,3为透明导电层,3-1为第一透明导电层,3-2为第二透明导电层,4为扩展电极,5为透明绝缘层,6为透明绝缘层窗口,7为布线线路,8为MicroLED,9为反射绝缘层,10为反射绝缘层窗口,11为焊线电极,12-1为第一透明键合层,12-2为第二透明键合层,13为透明粘结层,14为绝缘层窗口,15为绝缘层。

具体实施方式

如图1所示,本发明提供了一种集成式LED芯片,包括生长衬底1;

位于所述生长衬底1表面的外延结构2,所述外延结构(2)的上表面包括正极性层和刻蚀后暴露出的负极性层;

位于所述外延结构2的正极性层表面的透明导电层3和位于所述透明导电层3表面和所述外延结构2暴露在外的负极性层表面的扩展电极4;

位于暴露在外的外延结构2负极性层、透明导电层3、扩展电极4和生长衬底1的表面的透明绝缘层5;

贯穿透明绝缘层5至扩展电极4的透明绝缘层窗口6;

在位于所述透明绝缘层3和透明绝缘层窗口6处的扩展电极表面设置的布线线路7;

位于所述布线线路7表面的Micro LED 8;

位于所述透明绝缘层5、布线线路7和Micro LED 8表面的反射绝缘层9;

贯穿反射绝缘层9至布线线路7的反射绝缘层窗口10;

位于所述反射绝缘层9和反射绝缘层窗口10处的布线线路7表面的焊线电极11。

在本发明中,所述生长衬底1优选为蓝宝石衬底,所述生长衬底1的厚度优选为80~200μm,更优选为100~180μm,最优选为120~150μm。

在本发明中,所述外延结构2优选为蓝光外延结构或绿光外延结构。

在本发明中,所述外延结构2包括由下到上依次层叠设置的负极性层、量子阱发光层和正极性层。

在本发明中,所述外延结构2优选为经过刻蚀处理的外延结构,所述外延结构2的上表面包括正极性层和刻蚀后暴露出的负极性层。

在本发明中,所述相邻两外延结构2之间的间隔优选通过对所述衬底表面的外延结构进行刻蚀实现。

在本发明中,所述透明导电层3的厚度优选为50~200nm,更优选为80~150nm,最优选为100~120nm;所述透明导电层3的材料优选ITO或IZO。

在本发明中,位于透明导电层3表面的扩展电极优选为正极型扩展电极,位于所述外延结构暴露在外的负极性层表面的扩展电极优选为负极型扩展电极。

在本发明中,所述扩展电极4由下到上优选包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层;所述欧姆接触粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述欧姆接触粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~150nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~200nm,更优选为80~160nm,最优选为100~130nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述粘结层的厚度优选为50~200nm,更优选为80~160nm,最优选为100~130nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层。

在本发明中,所述透明绝缘层5的厚度优选为0.5~5μm,更优选为1~4μm,最优选为2~3μm;所述透明绝缘层5优选为二氧化硅层、氧化铝层、三氧化二钛层和BCB(苯并环丁烯)层中的一层或两层以上的叠层。

在本发明中,所述透明绝缘层窗口6的形状优选为圆形、椭圆形、方形或菱形;所述透明绝缘层窗口6的底面尺寸小于所述扩展电极的尺寸,所述透明绝缘层窗口6的边缘至所述扩展电极的边缘之间的宽度优选为2~20μm,更优选为4~15μm,最优选为6~10μm。在本发明中,所述透明绝缘层窗口6的孔径大小优选从底面到顶面逐渐增加。

在本发明中,所述布线线路7由下到上优选包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层;所述欧姆接触粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述欧姆接触粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~160nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~200nm,更优选为80~160nm,最优选为120~130nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述粘结层的厚度优选为50~200nm,更优选为80~160nm,最优选为120~130nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层或所述粘结层优选为Ti、Ni和Cr中的两种金属组成的合金材料。

在本发明中,所述布线线路7优选分为四个区域,包括区域一、区域二、区域三和区域四;所述区域一的布线线路优选和正极型扩展电极互连,区域二的布线线路路优选和负极型扩展电极互连,区域三和区域四的布线线路优选和不同的Micro LED的正极通过共晶键合的方式互连,区域二的布线线路优选和Micro LED的负极通过共晶键合的方式互连。

在本发明中,所述Micro LED 8优选包括蓝光Micro LED芯片、绿光Micro LED芯片和红光Micro LED芯片中的一种或几种;当所述外延结构为蓝光外延结构,所述Micro LED优选包括绿光Micro LED芯片和红光MicroLED芯片;当所述外延结构为绿光外延结构,所述Micro LED优选包括蓝光Micro LED芯片和红光Micro LED芯片。在本发明中,所述绿光Micro LED芯片和红光Micro LED芯片的位置关系或所述蓝光Micro LED芯片和红光MicroLED芯片的位置关系优选为并排排列,相邻两Micro LED芯片之间的间距优选为5~50μm,更优选为10-40μm,最优选为2~30μm。

在本发明中,所述反射绝缘层9的总厚度优选为1~5μm,更优选为2~4μm,最优选为2.5~3.5μm。在本发明中,所述反射绝缘层9由下到上优选包括依次层叠设置的高折射率层和低折射率层;所述高折射率层和低折射率层重复层叠设置的次数优选为15~60次,更优选为25~50次。在本发明中,所述高折射率层的厚度优选为2~5μm,更优选为3-4μm,最优选为3.5μm,所述高折射率层的材料优选为TiO

在本发明中,所述反射绝缘层窗口10的形状优选为圆形、椭圆形、方形或菱形;所述反射绝缘层窗口6的底面尺寸小于所述扩展电极的尺寸,所述反射绝缘层窗口10的边缘至所述扩展电极的边缘之间的宽度优选为2~20μm,更优选为4~15μm,最优选为6~10μm。在本发明中,所述反射绝缘层窗口6的孔径大小优选从底面到顶面逐渐增加。

在本发明中,所述焊线电极由下到上优选包括依次层叠设置的粘结层、反射层、阻挡层和键合层;所述粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~150nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~500nm,更优选为100~300nm,最优选为150~250nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述键合层的厚度优选为0.1~20μm,更优选为5~15μm,最优选为8~12μm;所述键合层优选为Au层、Ag层、Sn层、In层和Cu层中的一层或两层以上的叠层。

在本发明中,如图1所示结构的集成式LED芯片的制备方法优选包括以下步骤:

S101,提供一生长衬底1,如图3所示结构;

S102,在所述生长衬底1的表面制备外延结构2(如图4所示结构);

S103,对所述蓝光外延结构进行部分刻蚀(刻蚀后的形状如图5中左图所示)所述正极性层和量子阱发光层,并暴露出负极性层(如图5所示);

S104,对所述蓝光外延结构的周边进行刻蚀并暴露出所述生长衬底(如图6所示);

S105,在所述蓝光外延结构未刻蚀的部分中的正极性层的表面制作透明导电层(如图7所示);

S106,在所述透明导电层的表面和S103暴露出的部分负极性层的表面上制作扩展电极4(如图8所示);

S107,在S106制备得到的中间产物表面制作透明绝缘层5,然后在位于所述扩展电极4处制作透明绝缘层窗口6(如图9所示);

S108,在所述扩展电极4和透明绝缘层窗口6之间构成的倒梯形结构处,以及在部分所述透明绝缘层表面制作布线线路7(如图10所示);

S109,将Micro LED芯片转移至位于所述透明绝缘层表面的布线线路7的表面(如图11所示);

S110,在Micro LED芯片表面、未放置Micro LED芯片的布线线路7表面和暴露的透明绝缘层的表面上制作反射绝缘层8,然后在未放置MicroLED芯片的布线线路7处制作反射绝缘层窗口10(如图12所示);

S111,在反射绝缘层8、反射绝缘层窗口10处的布线线路7表面制作焊线电极11;

S112,对S111得到的结构进行研磨、切割,形成单个的集成式LED芯片结构(如图13所示)。

如图14所示,本发明还提供了一种集成式LED芯片,包括第一生长衬底1-1;

位于所述生长衬底表面的第一外延结构2-1;所述第一外延结构2-1为经过刻蚀处理的外延结构,所述第一外延结构2-1的上表面包括正极性层和刻蚀后暴露出的负极性层;所述第一外延结构2-1间隔设置,相邻两第一外延结构2-1之间的间隔通过对所述第一生长衬底表面的第一外延结构2-1进行刻蚀实现;

位于所述第一外延结构2-1的正极性层表面的第一透明导电层3-1;

位于所述第一透明导电层3-1表面的第一透明键合层12-1,所述第一透明键合层12-1的表面尺寸小于所述第一透明导电层3-1的表面尺寸;

位于所述第一透明键合层12-1表面的第二透明键合层12-2,所述第二透明键合层12-2的表面尺寸与所述第一透明键合层12-1的表面尺寸相同;

位于所述第二透明键合层12-2表面的第二透明导电层3-2,所述第二透明导电层3-2的表面尺寸与所述第二透明键合层12-2的表面尺寸相同;

位于所述第二透明导电层3-2表面的第二外延结构2-2,所述第二外延结构2-2的表面尺寸小于所述第二透明导电层3-2的表面尺寸;

位于所述第一外延结构2-1的负极性层、第一透明导电层3-1、第二透明导电层3-2和第二外延结构2-2的负极性层表面部分区域的扩展电极4;

位于所述第一生长衬底1-1、第一外延结构2-1的负极性层、第一透明导电层3-1、第二外延结构2-2的负极性层、第二透明导电层3-2和位于第一透明导电层3-1和第二外延结构2-2的负极型表面的扩展电极4表面的透明绝缘层5;

贯穿透明绝缘层5至位于第一外延结构2-1的负极性层和第二透明导电层3-2处的扩展电极4的透明绝缘层窗口6;

位于所述透明绝缘层5和透明绝缘层窗口6处的扩展电极表面的布线线路7;

位于所述布线线路7上的Micro LED 8;

位于暴露的透明绝缘层5、布线线路7和Micro LED 8表面的反射绝缘层9;

贯穿所述反射绝缘层9至布线线路7的反射绝缘层窗口10;

位于反射绝缘层9和反射绝缘层窗口10处的布线线路7之上的焊线电极11。

在本发明中,所述第一生长衬底1-1优选为蓝宝石衬底,所述生长衬底1的厚度优选为80~200μm,更优选为100~180μm,最优选为120~150μm。

在本发明中,所述第一外延结构2-1优选为蓝光外延结构或绿光外延结构。

在本发明中,所述第一外延结构2-1包括由下到上依次层叠设置的负极性层、量子阱发光层和正极性层。

在本发明中,所述第一透明导电层3-1的厚度优选为50~200nm,更优选为80~150nm,最优选为100~120nm;所述第一透明导电层3-1的材料优选ITO或IZO。

在本发明中,所述第一透明键合层12-1的厚度优选为0.5~10μm,更优选为1~8μm,最优选为2~5μm;所述第一透明键合层12-1的材料优选为有机透明材料或无机透明材料;所述有机透明材料优选为BCB,所述无机透明材料优选为二氧化硅。

在本发明中,所述第二透明键合层12-2的厚度优选为1~10μm,更优选为2~8μm,最优选为3~5μm;所述第二透明键合层12-2的材料优选为有机透明材料或无机透明材料;所述有机透明材料优选为BCB,所述无机透明材料优选为二氧化硅。

在本发明中,所述第二透明导电层3-2的厚度优选为50~200nm,更优选为80~150nm,最优选为100~120nm;所述第二透明导电层3-2的材料优选ITO或IZO。

在本发明中,所述第二外延结构2-2包括由下到上依次层叠设置的正极性层、量子阱发光层和负极性层。在本发明中,所述第二外延结构2-2优选为蓝光外延结构或绿光外延结构,所述第一外延结构2-1和第二外延结构2-2的种类不同。

在本发明中,所述扩展电极4由下到上优选包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层;所述欧姆接触粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述欧姆接触粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~150nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~200nm,更优选为80~160nm,最优选为100~130nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述粘结层的厚度优选为50~200nm,更优选为80~160nm,最优选为100~130nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层。在本发明中,位于所述第一外延结构2-1的负极性层表面的扩展电极4记为区域一,位于所述第一透明导电层3-1表面的扩展电极4记为区域二,位于所述第二透明导电层3-2表面的扩展电极4记为区域四和位于所述第二外延结构2-2的负极性层表面的扩展电极4记为区域三。

在本发明中,所述透明绝缘层5的厚度优选为0.5~5μm,更优选为1~4μm,最优选为2~3μm;所述透明绝缘层5优选为二氧化硅层、氧化铝层、三氧化二钛层和BCB(苯并环丁烯)层中的一层或两层以上的叠层。

在本发明中,所述透明绝缘层窗口6的形状优选为圆形、椭圆形、方形或菱形;所述透明绝缘层窗口6的底面尺寸小于所述扩展电极的尺寸,所述透明绝缘层窗口6的边缘至所述扩展电极4的边缘之间的宽度优选为2~20μm,更优选为4~15μm,最优选为6~10μm。在本发明中,所述透明绝缘层窗口6的孔径大小优选从底面到顶面逐渐增加。

在本发明中,所述布线线路7分为四个区域,其中区域一的布线线路通过透明绝缘层窗口与位于位于第一外延结构2-1的负极性层和第二透明导电层3-2处的扩展电极4互连,同时区域一的布线线路通过共晶键合的方式与Micro LED的负极互连,区域三的布线线路通过透明绝缘层窗口与位于第一透明导电层3-1表面的扩展电极4互连,区域四的布线线路通过透明绝缘层窗口和位于第二透明导电层3-2表面的扩展电极4互连;同时,区域二的布线线路通过共晶键合的方式与Micro LED的正极互连。

在本发明中,所述布线线路7由下到上优选包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层;所述欧姆接触粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述欧姆接触粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~160nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~200nm,更优选为80~160nm,最优选为120~130nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述粘结层的厚度优选为50~200nm,更优选为80~160nm,最优选为120~130nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层或所述粘结层优选为Ti、Ni和Cr中的两种金属组成的合金材料。在本发明中,所述MicroLED 8优选为红光Micro LED芯片。

在本发明中,所述反射绝缘层9的总厚度优选为1~5μm,更优选为2~4μm最优选为2.5~3.5μm。在本发明中所述反射绝缘层9由下到上优选包括依次层叠设置的高折射率层和低折射率层;所述高折射率层和低折射率层重复层叠设置的次数优选为15~60次,更优选为25~50次。在本发明中,所述高折射率层的厚度优选为2~5μm,更优选为3-4μm,最优选为3.5μm,所述高折射率层的材料优选为TiO

在本发明中,所述反射绝缘层窗口10的形状优选为圆形、椭圆形、方形或菱形;所述反射绝缘层窗口6的底面尺寸小于所述扩展电极的尺寸,所述反射绝缘层窗口10的边缘至所述扩展电极4的边缘之间的宽度优选为2~20μm,更优选为4~15μm,最优选为6~10μm。在本发明中,所述反射绝缘层窗口6的孔径大小优选从底面到顶面逐渐增加。

在本发明中,所述焊线电极11由下到上优选包括依次层叠设置的粘结层、反射层、阻挡层和键合层;所述粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~150nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~500nm,更优选为100~300nm,最优选为150~250nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述键合层的厚度优选为0.1~20μm,更优选为5~15μm,最优选为8~12μm;所述键合层优选为Au层、Ag层、Sn层、In层和Cu层中的一层或两层以上的叠层。

如图15所示流程,在本发明中所述集成式LED芯片的制备方法优选包括以下步骤:

S201,提供第一组件,所述第一组件由下到上包括依次层叠设置的第一生长衬底1-1,第一外延结构2-1,第一透明导电层3-1和第一透明键合层12-1,如图16所示结构;

S202,提供第二组件,所述第二组件由下到上包括依次层叠设置的第二生长衬底1-2,倒置的第二外延结构2-2,第二透明导电层3-2和第二透明键合层12-2,如图17所示结构;

S203,通过键合的方式,将所述第一组件和第二组件进行堆叠互联,其中所述第一组件的第一透明键合层12-1与所述第二组件的第二透明键合层12-2键合,如图18所示结构;

S204,通过激光剥离的方式,去除所述第二生长衬底1-2,如图19所示;

S205,去除第二组件部分区域倒置的第二外延结构2-2的负极性层、量子阱发光层和正极性层,并暴露出第二透明导电层3-2,如图20所示结构;

S206,去除第二组件部分区域的第二透明导电层12-2、第二透明键合层12-2和部分区域的第一透明键合层12-1,暴露所述第一组件的第一透明导电层3-1,如图21所示结构;

S207,去除所述第一组件的部分区域的第一透明导电层3-1,第一组件中第一外延结构的正极性层和量子阱发光层,并暴露出第一组件中第一外延结构的负极性层,如图22所示结构;

S208,去除部分区域的第一外延结构2-1,暴露出第一生长衬底1-1,如图23所示结构;

S209,在暴露出的第一外延结构1-1的负极性层表面的部分区域、第一透明导电层3-1表面的部分区域、第二透明导电层3-2的部分区域和倒置的第二外延结构的负极性层表面的部分区域上制作扩展电极4,如图24所示结构;

S210,在暴露的第一生长衬底1-1、第一外延结构2-1的负极性层、第一透明导电层3-1、第二透明导电层3-2和倒置的第二外延结构2-2负极性层的表面制作透明绝缘层5,然后在扩展电极4处制作透明绝缘层窗口6,至暴露出扩展电极4,如图25所示结构;

S211,在暴露的扩展电极4上制作布线线路7,如图26所示结构;

S212,通过转移的方式,将Micro LED 8转移至所述布线线路7上,如图27所示结构;

S213,在所述Micro LED 8、暴露的布线线路7和透明绝缘层5的表面制作反射绝缘层9,在未设置Micro LED 8的布线线路7处制作反射绝缘层窗口10,至暴露出所述布线线路7,如图28所示结构;

S214,在所述反射绝缘层9和反射绝缘层窗口10出的布线线路7上制作焊线电极11;

S215,对S214得到的结构进行研磨、切割,形成单个的集成式LED芯片结构(如图29所示结构)。

如图30所示,本发明还提供了一种集成式LED芯片,包括生长衬底1;

位于所述生长衬底表面的外延结构2;所述外延结构2为经过刻蚀处理的外延结构,所述外延结构2的上表面包括正极性层和刻蚀后暴露出的负极性层;所述外延结构2间隔设置,相邻两外延结构2之间的间隔通过对所述衬底表面的外延结构进行刻蚀实现;

位于所述外延结构2表面的透明导电层3;

位于所述透明导电层3的表面和外延结构2中暴露的负极性层表面的扩展电极4;

位于所述生长衬底表面、外延结构中暴露的负极型表面和扩展电极表面的透明粘结层13;

位于所述透明粘结层13表面的Micro LED 8;

位于所述透明粘结层和Micro LED表面的反射绝缘层9;

贯穿反射绝缘层至扩展电极和所述Micro LED中的焊线电极的反射绝缘层窗口6;

位于所述反射绝缘层、反射绝缘层窗口处的扩展电极和Micro LED表面的布线线路7;

位于所述反射绝缘层、布线线路和Micro LED表面的绝缘层15;

贯穿所述绝缘层15至布线线路7的绝缘层窗口14;

位于所述绝缘层、绝缘层窗口处的布线线路表面的焊线电极11。

在本发明中,所述生长衬底1优选为蓝宝石衬底,所述生长衬底1的厚度优选为80~200μm,更优选为100~180μm,最优选为120~150μm。

在本发明中,所述外延结构2优选为蓝光外延结构或绿光外延结构。

在本发明中,所述外延结构2包括由下到上依次层叠设置的负极性层、量子阱发光层和正极性层。

在本发明中,所述外延结构2优选为经过刻蚀处理的外延结构,所述外延结构2的上表面包括正极性层和刻蚀后暴露出的负极性层。

在本发明中,所述相邻两外延结构2之间的间隔优选通过对所述衬底表面的外延结构进行刻蚀实现。

在本发明中,所述透明导电层3的厚度优选为50~200nm,更优选为80~150nm,最优选为100~120nm;所述透明导电层3的材料优选ITO或IZO。

在本发明中,位于透明导电层3表面的扩展电极优选为正极型扩展电极,位于所述外延结构暴露在外的负极性层表面的扩展电极优选为负极型扩展电极。

在本发明中,所述扩展电极4由下到上优选包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层;所述欧姆接触粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述欧姆接触粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~150nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~200nm,更优选为80~160nm,最优选为100~130nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述粘结层的厚度优选为50~200nm,更优选为80~160nm,最优选为100~130nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层。

在本发明中,所述透明粘结层13的厚度优选为0.5~5μm,更优选为1~4μm,最优选为2~3μm。在本发明中,所述透明粘结层13的材料优选为BCB(苯并环丁烯)和/或聚酰亚胺。在本发明中,所述透明粘结层透明、绝缘且具有粘性。

在本发明中,所述Micro LED 8优选包括蓝光Micro LED芯片、绿光Micro LED芯片和红光Micro LED芯片中的一种或几种;当所述外延结构为蓝光外延结构,所述Micro LED优选包括绿光Micro LED芯片和红光MicroLED芯片;当所述外延结构为绿光外延结构,所述Micro LED优选包括蓝光Micro LED芯片和红光Micro LED芯片。在本发明中,所述绿光Micro LED芯片和红光Micro LED芯片的位置关系或所述蓝光Micro LED芯片和红光MicroLED芯片的位置关系优选为并排排列,相邻两Micro LED芯片之间的间距优选为5~50μm,更优选为10-40μm,最优选为2~30μm。

在本发明中,所述反射绝缘层9的总厚度优选为1~5μm,更优选为2~4μm,最优选为2.5~3.5μm。在本发明中,所述反射绝缘层9由下到上优选包括依次层叠设置的高折射率层和低折射率层;所述高折射率层和低折射率层重复层叠设置的次数优选为15~60次,更优选为25~50次。在本发明中,所述高折射率层的厚度优选为2~5μm,更优选为3-4μm,最优选为3.5μm,所述高折射率层的材料优选为TiO

在本发明中,所述反射绝缘层窗口10的形状优选为圆形、椭圆形、方形或菱形;所述反射绝缘层窗口6的底面尺寸小于所述扩展电极的尺寸,所述反射绝缘层窗口6的边缘至所述扩展电极的边缘之间的宽度优选为2~20μm,更优选为4~15μm,最优选为6~10μm。在本发明中,所述反射绝缘层窗口6的孔径大小优选从底面到顶面逐渐增加。

在本发明中,所述布线线路7由下到上优选包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层;所述欧姆接触粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述欧姆接触粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~160nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~200nm,更优选为80~160nm,最优选为120~130nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述粘结层的厚度优选为50~200nm,更优选为80~160nm,最优选为120~130nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层或所述粘结层优选为Ti、Ni和Cr中的两种金属组成的合金材料。

在本发明中,所述布线线路7优选分为四个区域,包括区域一、区域二、区域三和区域四;所述区域一的布线线路优选和正极型扩展电极互连,区域二的布线线路路优选和负极型扩展电极互连,区域三和区域四的布线线路优选和不同的Micro LED的正极通过共晶键合的方式互连,区域二的布线线路优选和Micro LED的负极通过共晶键合的方式互连。

在本发明中,所述绝缘层15的厚度优选为0.5~5μm,更优选为1~4μm,最优选为2~3μm;所述绝缘层优选为二氧化硅层、氧化铝层、三氧化二钛层和BCB层中的一层或两种以上的叠层。

在本发明中,所述绝缘层窗口14的形状优选为圆形、椭圆形、方形或菱形;所述绝缘层窗口6的底面尺寸小于所述扩展电极的尺寸,所述绝缘层窗口14的边缘至所述扩展电极的边缘之间的宽度优选为2~20μm,更优选为4~15μm,最优选为6~10μm。在本发明中,所述反射绝缘层窗口6的孔径大小优选从底面到顶面逐渐增加。

在本发明中,所述焊线电极11由下到上优选包括依次层叠设置的粘结层、反射层、阻挡层和键合层;所述粘结层的厚度优选为2~10nm,更优选为3~8nm,最优选为4~6nm;所述粘结层优选为Ti层、Ni层和Cr层中的一层或两层以上的叠层;所述反射层的厚度优选为10~200nm,更优选为50~150nm,最优选为80~120nm;所述反射层优选为Al层、Ag层和Pt层中的一层或两层以上的叠层;所述阻挡层的厚度优选为50~500nm,更优选为100~300nm,最优选为150~250nm;所述阻挡层优选为Pt层、Ti层、Ni层、W层和Zr层中的一层或两层以上的叠层;所述键合层的厚度优选为0.1~20μm,更优选为5~15μm,最优选为8~12μm;所述键合层优选为Au层、Ag层、Sn层、In层和Cu层中的一层或两层以上的叠层。

如图31所示流程,在本发明中所述集成式LED芯片的制备方法优选包括以下步骤:

S301,提供一生长衬底1,如图32所示结构;

S302,在所述生长衬底1的表面制备外延结构2(如图33所示结构);

S303,对所述外延结构进行部分刻蚀(刻蚀后的形状如图34中左图所示)所述正极性层和量子阱发光层,并暴露出负极性层(如图34所示);

S304,对暴露出的负极性层进行部分去除并暴露出生长衬底(如图35所示);

S305,在所述正极性层的表面制作透明导电层3(如图36所示);

S306,在所述透明导电层3和负极性层的表面制作扩展电极4(如图37所示),且所述扩展电极4的尺寸小于所述透明导电层3的尺寸;

S307,在暴露出的负极性层、暴露出的透明导电层3、暴露出的扩展电极4和暴露出的生长衬底1的表面制作透明粘结层13(如图38所示);

S308,将Micro LED 8转移至位于所述负极性层表面的部分透明粘结层表面(如图39所示);

S309,在所述Micro LED 8和暴露的透明粘结层13的表面制作反射绝缘层9,然后分别对位于扩展电极4和Micro LED 8表面的反射绝缘层9进行刻蚀制作反射绝缘层窗口6(如图40所示);

S310,在所述反射绝缘层、反射绝缘层窗口处的扩展电极和所述MicroLED中的焊线电极表面制作布线线路7(如图41所示);

S311,在所述反射绝缘层9和布线线路7的表面制作绝缘层15,然后制作绝缘层窗口14(如图42所示);

S312,在所述绝缘层窗口14和位于所述绝缘层窗口14周围的绝缘层15表面制作焊线电极11;

S313,对S312得到的结构进行研磨、切割,形成单个的集成式LED芯片结构(如图43所示)。

下面结合实施例对本发明提供的集成式LED芯片进行详细的说明,但是不能把它们理解为对本发明保护范围的限定。

实施例1

集成式LED芯片的结构如图1所示:所述集成式LED芯片包括生长衬底1(蓝宝石衬底);

位于所述生长衬底1表面的外延结构2(由下到上依次为负极性层、量子阱发光层和正极性层),所述外延结构2在所述生长衬底1的表面间隔分布;

位于所述外延结构的正极性层表面的透明导电层3(厚度为100nm,材料为ITO)和位于所述透明导电层3表面和所述外延结构暴露在外的负极性层表面的扩展电极4,其中位于透明导电层3表面的扩展电极为正极型扩展电极,位于所述外延结构暴露在外的负极性层表面的扩展电极为负极型扩展电极,所述扩展电极由下至上包括依次层叠设置的厚度为2nm的欧姆接触粘结层(材料为Cr),厚度为100nm的反射层(材料为Al),厚度为200nm的阻挡层(材料为Pt)和厚度为50nm的粘结层(材料为Ti);

位于暴露在外的外延结构负极性层、透明导电层、扩展电极和生长衬底的表面的透明绝缘层5(厚度为2000nm,材料为SiO2);

贯穿透明绝缘层5至扩展电极4的透明绝缘层窗口6(形状为圆形,底面尺寸小于所述扩展电极的尺寸,所述透明绝缘层窗口6的边缘至所述扩展电极的边缘之间的宽度为3nm,孔径大小从底面到顶面逐渐增加);

在位于所述透明绝缘层3和透明绝缘层窗口6处的扩展电极表面设置的布线线路7(由下到上包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层),所述布线线路7分为四个区域,其中区域一的布线线路和正极型扩展电极互连,区域二的布线线路路和负极型扩展电极互连,区域三和区域四的布线线路和不同的Micro LED的正极通过共晶键合的方式互连,区域二的布线线路和Micro LED的负极通过共晶键合的方式互连;

位于所述布线线路7上的Micro LED 8,所述Micro LED 8包括绿光Micro LED芯片和红光Micro LED芯片,所述绿光Micro LED芯片和红光Micro LED芯片的位置关系并排排列;

位于所述透明绝缘层5、布线线路7和Micro LED 8表面的反射绝缘层9(由下到上包括依次层叠设置的SiO2层和TiO2层,所述SiO2的厚度为1.4μm,TiO2层的厚度为1.6μm,所述SiO2层和TiO2层重复层叠设置的次数为15次);

贯穿反射绝缘层9至布线线路的反射绝缘层窗口10(形状为圆形,底面尺寸小于所述扩展电极的尺寸,反射绝缘层窗口10的边缘至扩展电极的边缘之间的宽度为2.5μm,孔径大小从底面到顶面逐渐增加);

位于所述反射绝缘层9和反射绝缘层窗口10处的布线线路7表面的焊线电极11(由下到上包括依次层叠设置的粘结层、反射层、阻挡层和键合层,);

如图2所示流程,所述集成式LED芯片的制备方法为:

S101,提供一生长衬底1,如图3所示结构;

S102,在所述生长衬底1的表面制备外延结构2(如图4所示结构);

S103,对所述蓝光外延结构进行部分刻蚀(刻蚀后的形状如图5中左图所示)所述正极性层和量子阱发光层,并暴露出负极性层(如图5所示);

S104,对所述蓝光外延结构的边缘处进行刻蚀并暴露出所述生长衬底(如图6所示);

S105,在所述蓝光外延结构未刻蚀的部分中的正极性层的表面制作透明导电层(如图7所示);

S106,在所述透明导电层的表面和S103暴露出的部分负极性层的表面上制作扩展电极4(如图8所示);

S107,在S106制备得到的中间产物表面制作透明绝缘层5,然后在位于所述扩展电极4处制作透明绝缘层窗口6(如图9所示);

S108,在所述扩展电极4和透明绝缘层窗口6之间构成的倒梯形结构处,以及在部分所述透明绝缘层表面制作布线线路7(如图10所示);

S109,将Micro LED芯片转移至位于所述透明绝缘层表面的布线线路7的表面(如图11所示);

S110,在Micro LED芯片表面、未放置Micro LED芯片的布线线路7表面和暴露的透明绝缘层的表面上制作反射绝缘层8,然后在未放置Micro LED芯片的布线线路7处制作反射绝缘层窗口10(如图12所示);

S111,在反射绝缘层8、反射绝缘层窗口10处的布线线路7表面制作焊线电极11;

S112,对S111得到的结构进行研磨、切割,形成单个的集成式LED芯片结构(如图13所示)。

实施例2

集成式LED芯片的结构如图14所示:包括第一生长衬底1-1(蓝宝石衬底);

位于所述生长衬底表面的第一外延结构2-1(从下至上依次层叠设置的负极性层、量子阱发光层和正极性层);所述第一外延结构2为经过刻蚀处理的外延结构,所述第一外延结构2-1的上表面包括正极性层和刻蚀后暴露出的负极性层;所述第一外延结构2-1间隔设置,相邻两第一外延结构2-1之间的间隔通过对所述第一生长衬底表面的第一外延结构2-1进行刻蚀实现;

位于所述第一外延结构2-1的正极性层表面的第一透明导电层3-1(厚度为100nm,材料为ITO);

位于所述第一透明导电层3-1表面的第一透明键合层12-1(厚度为500nm,材料为SiO2),所述第一透明键合层12-1的表面尺寸小于所述第一透明导电层3-1的表面尺寸;

位于所述第一透明键合层12-1表面的第二透明键合层12-2(厚度为500nm,材料为SiO2),所述第二透明键合层12-2的表面尺寸与所述第一透明键合层12-1的表面尺寸相同;

位于所述第二透明键合层12-2表面的第二透明导电层3-2(厚度为100nm,材料为ITO),所述第二透明导电层3-2的表面尺寸与所述第二透明键合层12-2的表面尺寸相同;

位于所述第二透明导电层3-2表面的第二外延结构2-2(从下至上依次层叠设置的正极性层、量子阱发光层和负极性层),所述第二外延结构2-2的表面尺寸小于所述第二透明导电层3-2的表面尺寸;

位于所述第一外延结构2-1的负极性层、第一透明导电层3-1、第二透明导电层3-2和第二外延结构2-2的负极性层表面部分区域的扩展电极4(所述扩展电极4由下到上包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层);

位于所述第一生长衬底1-1、第一外延结构2-1的负极性层、第一透明导电层3-1、第二外延结构2-2的负极性层、第二透明导电层3-2和位于第一透明导电层3-1和第二外延结构2-2的负极型表面的扩展电极4表面的透明绝缘层5(厚度为2000nm,材料为SiO2);

贯穿透明绝缘层5至位于第一外延结构2-1的负极性层和第二透明导电层3-2处的扩展电极4的透明绝缘层窗口6(形状为圆形,底面尺寸小于所述扩展电极的尺寸,所述透明绝缘层窗口6的边缘至所述扩展电极的边缘之间的宽度为3nm,孔径大小从底面到顶面逐渐增加);

位于所述透明绝缘层5和透明绝缘层窗口6处的扩展电极表面的布线线路7(由下到上包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层),所述布线线路7分为四个区域,其中区域一的布线线路通过透明绝缘层窗口与位于位于第一外延结构2-1的负极性层和第二透明导电层3-2处的扩展电极4互连,同时区域一的布线线路通过共晶键合的方式与Micro LED的负极互连,区域三的布线线路通过透明绝缘层窗口与位于第一透明导电层3-1表面的扩展电极4互连,区域四的布线线路通过透明绝缘层窗口和位于第二透明导电层3-2表面的扩展电极4互连;同时,区域二的布线线路通过共晶键合的方式与Micro LED的正极互连;

位于所述布线线路7上的Micro LED 8;

位于暴露的透明绝缘层5、布线线路7和Micro LED 8表面的反射绝缘层9(由下到上包括依次层叠设置的SiO2层和TiO2层,所述SiO2的厚度为1.4μm,TiO2层的厚度为1.6μm,所述SiO2层和TiO2层重复层叠设置的次数为15次);

贯穿所述反射绝缘层9至布线线路的反射绝缘层窗口10(形状为圆形,底面尺寸小于所述扩展电极的尺寸,所述反射绝缘层窗口10的边缘至所述扩展电极4的边缘之间的宽度为3μm,孔径大小从底面到顶面逐渐增加);

位于反射绝缘层9和反射绝缘层窗口10处的布线线路7之上的焊线电极11(由下到上包括依次层叠设置的粘结层、反射层、阻挡层和键合层,所述粘结层的厚度为5nm,材料为Cr;所述反射层的厚度为150nm,材料为Al;所述阻挡层的厚度为200nm,材料为Ti;所述键合层的厚度为300nm,材料为Au);

如图15所示流程,所述集成式LED芯片的制备方法为:

S201,提供第一组件,所述第一组件由下到上包括依次层叠设置的第一生长衬底1-1,第一外延结构2-1,第一透明导电层3-1和第一透明键合层12-1,如图16所示结构;

S202,提供第二组件,所述第二组件由下到上包括依次层叠设置的第二生长衬底1-2,倒置的第二外延结构2-2,第二透明导电层3-2和第二透明键合层12-2,如图17所示结构;

S203,通过键合的方式,将所述第一组件和第二组件进行堆叠互联,其中所述第一组件的第一透明键合层12-1与所述第二组件的第二透明键合层12-2键合,如图18所示结构;

S204,通过激光剥离的方式,去除所述第二生长衬底1-2,如图19所示;

S205,去除第二组件部分区域倒置的第二外延结构2-2的负极性层、量子阱发光层和正极性层,并暴露出第二透明导电层3-2,如图20所示结构;

S206,去除第二组件部分区域的第二透明导电层12-2、第二透明键合层12-2和部分区域的第一透明键合层12-1,暴露所述第一组件的第一透明导电层3-1,如图21所示结构;

S207,去除所述第一组件的部分区域的第一透明导电层3-1,第一组件中第一外延结构的正极性层和量子阱发光层,并暴露出第一组件中第一外延结构的负极性层,如图22所示结构;

S208,去除部分区域的第一外延结构2-1,暴露出第一生长衬底1-1,如图23所示结构;

S209,在暴露出的第一外延结构1-1的负极性层表面的部分区域、第一透明导电层3-1表面的部分区域、第二透明导电层3-2的部分区域和倒置的第二外延结构的负极性层表面的部分区域上制作扩展电极4,如图24所示结构;

S210,在暴露的第一生长衬底1-1、第一外延结构2-1的负极性层、第一透明导电层3-1、第二透明导电层3-2和倒置的第二外延结构2-2负极性层的表面制作透明绝缘层5,然后在扩展电极4处制作透明绝缘层窗口6,至暴露出扩展电极4,如图25所示结构;

S211,在暴露的扩展电极4上制作布线线路7,如图26所示结构;

S212,通过转移的方式,将Micro LED 8转移至所述布线线路7上,如图27所示结构;

S213,在所述Micro LED 8、暴露的布线线路7和透明绝缘层5的表面制作反射绝缘层9,在未设置Micro LED 8的布线线路7处制作反射绝缘层窗口10,至暴露出所述布线线路7,如图28所示结构;

S214,在所述反射绝缘层9和反射绝缘层窗口10出的布线线路7上制作焊线电极11;

S215,对S214得到的结构进行研磨、切割,形成单个的集成式LED芯片结构(如图29所示结构)。

实施例3

集成式LED芯片的结构如图30所示:包括生长衬底1(蓝宝石衬底);

位于所述生长衬底表面的外延结构2(从下至上依次层叠设置的负极性层、量子阱发光层和正极性层);所述外延结构2为经过刻蚀处理的外延结构,所述外延结构2的上表面包括正极性层和刻蚀后暴露出的负极性层;所述外延结构2间隔设置,相邻两外延结构2之间的间隔通过对所述衬底表面的外延结构进行刻蚀实现;

位于所述外延结构2的正极性层表面的透明导电层3(厚度为200nm,材料为ITO),所述透明导电层3的尺寸小于所述正极性层的尺寸;

位于所述透明导电层3的表面和外延结构2中暴露的负极性层表面的扩展电极4,位于所述透明导电层3表面的扩展电极为正极性扩展电极,位于所述外延结构2中暴露的负极性层表面的扩展电极为负极性扩展电极;所述扩展电极4由下到上包括依次层叠设置的欧姆接触粘结层、反射层、阻挡层和粘结层;

位于所述生长衬底表面、外延结构中暴露的负极型表面和扩展电极表面的透明粘结层13(厚度为1μm,材料为BCB);

位于所述透明粘结层13表面的Micro LED 8,所述Micro LED 8位于所述负极性层表面的部分透明粘结层13表面(所述Micro LED 8包括绿光Micro LED芯片和红光MicroLED芯片,所述绿光Micro LED芯片和红光Micro LED芯片的位置关系并排排列);

位于所述透明粘结层和Micro LED表面的反射绝缘层9(由下到上包括依次层叠设置的SiO2层和TiO2层,所述SiO2的厚度为1.4μm,TiO2层的厚度为1.6μm,所述SiO2层和TiO2层重复层叠设置的次数为15次);

贯穿反射绝缘层至扩展电极和所述Micro LED中的焊线电极的反射绝缘层窗口6(形状为圆形,底面尺寸小于所述扩展电极的尺寸,所述反射绝缘层窗口6的边缘至所述扩展电极的边缘之间的宽度为5μm,孔径大小从底面到顶面逐渐增加);

位于所述反射绝缘层、反射绝缘层窗口处的扩展电极和Micro LED表面的布线线路7(由下到上包括依次层叠设置的厚度为5nm的欧姆接触粘结层(材料为Cr)、厚度为150nm的反射层(材料为Al)、厚度为200nm的阻挡层(材料为Pt)和厚度为300nm的粘结层(材料为Ti)),所述布线线路7分为四个区域,其中区域一的布线线路和正极型扩展电极互连,区域二的布线线路路和负极型扩展电极互连,区域三和区域四的布线线路和不同的Micro LED的正极通过共晶键合的方式互连,区域二的布线线路和Micro LED的负极通过共晶键合的方式互连;

位于所述反射绝缘层、布线线路和Micro LED表面的绝缘层15(厚度为5μm,材料为BCB);

贯穿所述绝缘层15至布线线路7的绝缘层窗口14(形状为圆形,底面尺寸小于所述扩展电极的尺寸,所述绝缘层窗口14的边缘至所述扩展电极的边缘之间的宽度为5μm,孔径大小从底面到顶面逐渐增加);

位于所述绝缘层、绝缘层窗口处的布线线路表面的焊线电极11(由下到上包括依次层叠设置的粘结层、反射层、阻挡层和键合层,所述粘结层的厚度为5nm,材料为Cr;所述反射层的厚度为120nm,材料为Al;所述阻挡层的厚度为150nm,材料为Ti;所述键合层的厚度为300nm,材料为Au);

如图31所示流程,所述集成式LED芯片的制备方法为:

S301,提供一生长衬底1,如图32所示结构;

S302,在所述生长衬底1的表面制备外延结构2(如图33所示结构);

S303,对所述外延结构进行部分刻蚀(刻蚀后的形状如图34中左图所示)所述正极性层和量子阱发光层,并暴露出负极性层(如图34所示);

S304,对暴露出的负极性层进行部分去除并暴露出生长衬底(如图35所示);

S305,在所述正极性层的表面制作透明导电层3(如图36所示);

S306,在所述透明导电层3和负极性层的表面制作扩展电极4(如图37所示),且所述扩展电极4的尺寸小于所述透明导电层3的尺寸;

S307,在暴露出的负极性层、暴露出的透明导电层3、暴露出的扩展电极4和暴露出的生长衬底1的表面制作透明粘结层13(如图38所示);

S308,将Micro LED 8转移至位于所述负极性层表面的部分透明粘结层表面(如图39所示);

S309,在所述Micro LED 8和暴露的透明粘结层13的表面制作反射绝缘层9,然后分别对位于扩展电极4和Micro LED 8表面的反射绝缘层9进行刻蚀制作反射绝缘层窗口6(如图40所示);

S310,在所述反射绝缘层、反射绝缘层窗口处的扩展电极和所述Micro LED中的焊线电极表面制作布线线路7(如图41所示);

S311,在所述反射绝缘层9和布线线路7的表面制作绝缘层15,然后制作绝缘层窗口14(如图42所示);

S312,在所述绝缘层窗口14和位于所述绝缘层窗口14周围的绝缘层15表面制作焊线电极11;

S313,对S312得到的结构进行研磨、切割,形成单个的集成式LED芯片结构(如图43所示)。

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 一种集成控制芯片和LED晶片的灯丝

- 一种集成式LED散热器驱动装置

- 一种驱动芯片的PWM信号控制电路以及汽车阅读灯LED驱动芯片

- 一种白光芯片加齐纳芯片的LED封装结构

- 一种倒装LED芯片结构集成多晶硅二极管的LED芯片

- 一种具有上下电极LED芯片陶瓷基板的LED集成模块及其集成封装工艺