半导体器件的制造方法

文献发布时间:2023-06-19 19:20:08

技术领域

本说明书中公开的技术总体涉及半导体器件的制造方法。

背景技术

已经开发了一种技术,其中在半导体衬底的一个主表面上形成器件结构,然后从半导体衬底上剥离具有器件结构的器件层。通过使用这种技术,可以重复使用已经剥离器件层的半导体衬底,从而降低半导体器件的制造成本。

在专利文献1中,通过将激光照射到半导体衬底的在其预定深度延伸的表面,并通过沿着形成改变层的表面从半导体衬底上剥离器件层,在半导体衬底内部形成改变层。

专利文献1:日本未审专利公开号2020-102520。

在半导体衬底中可能发生翘曲。如果半导体衬底翘曲,半导体衬底中的改变层也会翘曲。在这种情况下,当从半导体衬底上剥离器件层时,剥离力不太可能沿着改变层传递,因此可能导致剥离失败或半导体衬底的破损。

发明内容

本公开的目的是提供一种能够减少半导体衬底翘曲和适当地从半导体衬底剥离器件层的技术。

根据本公开的一个方面,半导体器件的制造方法包括沟槽形成步骤、激光照射步骤和剥离步骤。在沟槽形成步骤中,在半导体衬底的第一主表面上形成多个沟槽,该半导体衬底除了具有带器件结构的第一主表面外,还具有第二主表面。在激光照射步骤中,激光从第二主表面照射到平面表面,该平面表面在半导体衬底的预定深度处定位并延伸。在剥离步骤中,沿着激光照射的平面表面从半导体衬底剥离器件层。剥离步骤可以在沟槽未填充或填充具有低于半导体衬底的热膨胀系数的材料的状态下进行。

在该制造方法中,通过在半导体衬底中形成沟槽,施加到半导体衬底的应力是可减轻的,并且半导体衬底的翘曲是可减少的。此外,在沟槽形成步骤中形成的沟槽即使在剥离步骤中也保持在未填充或填充具有低热膨胀系数的材料的状态。因此,可以在抑制半导体衬底翘曲的同时进行剥离步骤。根据这样的制造方法,当器件层从半导体衬底剥离时,剥离力沿改变层传递,从而可以适当地执行从半导体衬底剥离器件层。

附图说明

本公开的目的、特征和优点将从以下参照附图所作的详细描述中变得更加明显,其中:

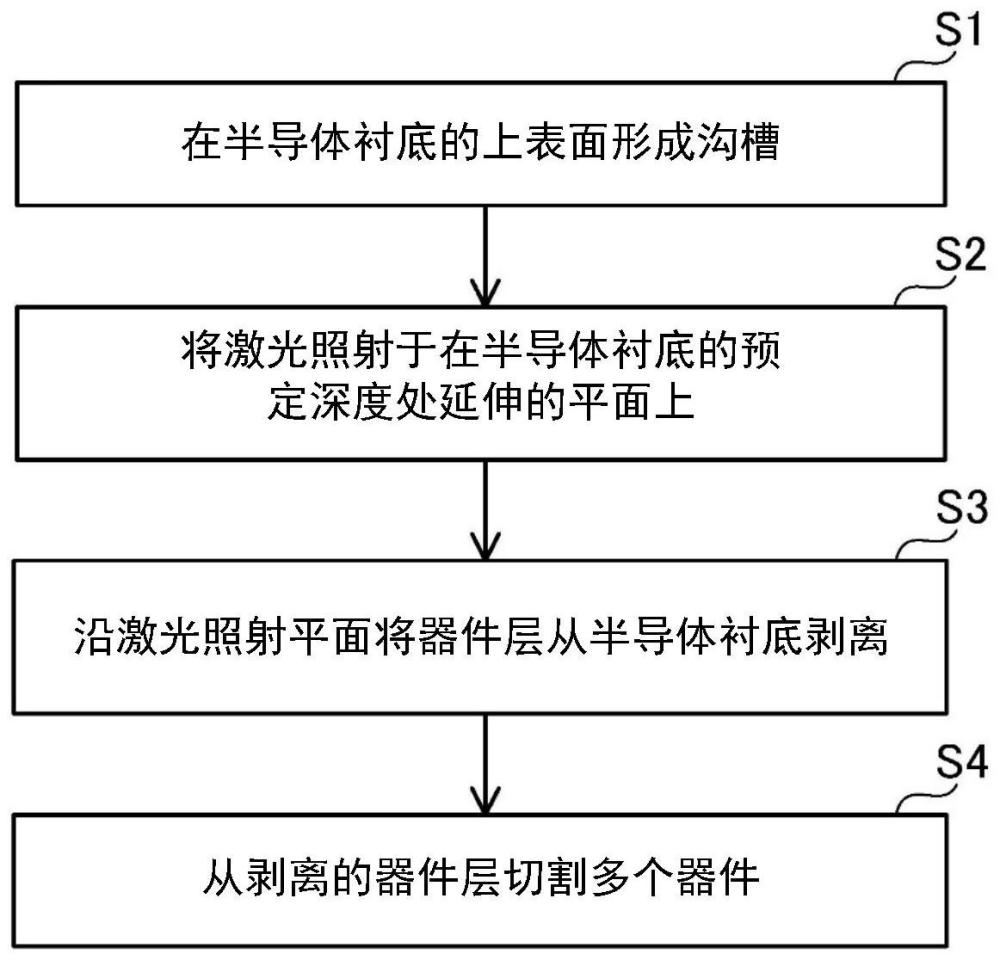

图1是根据本公开实施例的半导体器件的制造方法中的沟槽形成步骤、激光照射步骤、剥离步骤和切割步骤的流程图;

图2是示意性地示出根据该实施例,沿着图3的II-II线截取的半导体衬底在半导体器件制造工艺中的横截面图;

图3是示意性地示出根据该实施例的半导体衬底的器件区域布置的俯视图;

图4是示意性地示出根据该实施例,沿着图5的IV-IV线截取的半导体衬底在半导体器件制造工艺中的横截面图;

图5是示意性地示出根据该实施例的半导体衬底上的沟槽布置的俯视图;

图6是示出根据该实施例的半导体衬底在半导体器件的制造工艺中的横截面图;

图7是根据该实施例的半导体衬底在半导体器件的制造工艺中的横截面图;

图8是在根据该实施例的半导体器件的制造工艺中从半导体衬底剥离的器件层的横截面图;

图9是示意性地示出了根据本公开的修改实施例的半导体衬底的沟槽布置的放大视图;

图10是示意性地示出了根据本公开的另一修改实施例的半导体衬底的沟槽布置的放大视图;

图11是示出根据本公开的半导体衬底的直径与沟槽节距之间的关系的图。

具体实施方式

本公开的半导体器件的制造方法可包括沟槽形成步骤、激光照射步骤和剥离步骤。在沟槽形成步骤中,沟槽是在具有第一主表面和第二主表面的半导体衬底的第一主表面上形成的。该半导体衬底没有特别限制,但可以是化合物半导体。尽管半导体衬底是一个示例,但它也可以是包括氮化镓、碳化硅或氧化镓的氮化物半导体。由于半导体衬底是可重复使用的,因此制造本说明书中公开的半导体器件的方法在被应用到昂贵的化合物半导体的半导体衬底上时特别有用。器件结构可以在半导体衬底的第一主表面上形成。在激光照射步骤中,半导体衬底的在预定深度延伸的平面表面被激光照射。在激光照射步骤中,激光从未形成沟槽的第二主表面照射到半导体衬底的预定深度。在剥离步骤中,具有器件结构的器件层沿着激光照射的平面表面从半导体衬底剥离。剥离步骤可以在沟槽未填充或填充有具有低于半导体衬底的热膨胀系数的材料的状态下执行。

在沟槽形成步骤中,当在俯视图中看半导体衬底即从半导体衬底的第一主表面上方观察时,沟槽可以形成为在第一主表面上沿着至少一个方向重复出现。由于沟槽形成为重复出现,因此半导体衬底在至少一个方向上的翘曲减少了。在这种情况下,沟槽可以沿至少一个方向以规则间隔布置。

当沟槽形成为重复出现时,沿至少一个方向测量的沟槽的最大节距可以是半导体衬底直径的0.0177倍或更小。在这里,沟槽节距意味着相邻沟槽之间的距离。根据这样的制造方法,剥离成功率可以显著提高。

在沟槽形成为重复出现的情况下,在剥离步骤中,器件层可以从半导体衬底的一端沿着至少一个方向向另一端从半导体衬底剥离。由于器件层沿着半导体衬底翘曲减少的方向从半导体衬底剥离,因此器件层可以从半导体衬底适当地剥离。

可以在器件层中提供通过切割线分隔的多个器件区域。在这种情况下,多个器件区域的每个区域都是其中形成有器件结构的区域。沟槽可以延伸跨过多个器件区域。

在半导体器件的俯视图中,即,当从第一主表面上方观察半导体衬底时,该沟槽可以包括沿第一方向延伸的第一沟槽和沿与第一方向正交的第二方向延伸的第二沟槽。第一沟槽和第二沟槽可以以平面T形连接。根据这种制造方法,第一沟槽和第二沟槽连接处的部分的应力减小,并且可以抑制对半导体衬底的损坏。

半导体衬底可以是六方晶体半导体。在这种情况下,当从第一主表面的上方观察半导体衬底时,沟槽可以像无间隙布置的六边形延伸。根据这种制造方法,由于沟槽形成为当从第一主表面上方观察半导体衬底时沿三个方向重复出现,因此半导体衬底作为整体的翘曲可以以良好平衡的方式减少。此外,由于沟槽连接部分处沟槽之间的角度变为钝角,因此该部分的应力是可消除的,并且半导体衬底的断裂是可抑制的。

实施例

在下文中,将参照附图描述根据本公开的实施例的半导体器件的制造方法,其包括沟槽形成步骤、激光照射步骤、剥离步骤和切割步骤。请注意,除沟槽形成步骤、激光照射步骤、剥离步骤和切割步骤之外的各种其它步骤,如形成器件结构的步骤,可以利用已知的制造技术来执行。例如,形成器件结构的工艺,即步骤,可以在沟槽形成步骤和激光照射步骤之间进行。

图1示出了沟槽形成步骤(步骤S1)、激光照射步骤(步骤S2)、剥离步骤(步骤S3)和切割步骤(步骤S4)的流程。通过在图2和图3所示的半导体衬底上执行这些步骤,本说明书中公开的半导体器件的制造方法可以制造多个半导体器件,其也可称为半导体芯片。

如图2所示,半导体衬底1具有上表面1a和下表面1b,每个表面都是平面的。上表面1a和下表面1b彼此平行延伸。这些上表面1a和下表面1b也可以分别称为主表面。尽管半导体衬底1没有特别限制,但氮化镓衬底可以用作示例。如将在后面描述,在半导体衬底1的预定深度处延伸的平面表面3是用激光照射的激光照射表面3,即,多个激光焦点集中的表面。在本公开中,半导体衬底1在激光照射表面3上方的一部分,即将要从半导体衬底1剥离的部分称为器件层2。在下面的描述中,平行于半导体衬底1的上表面1a的方向被定义为x方向,平行于半导体衬底1的上表面1a且与x方向正交的方向被定义为y方向,并且与x方向和y方向都正交的方向被定义为z方向。z方向也可以称为半导体衬底1的厚度方向。

如图2和图3所示,半导体衬底1的器件层2设置有多个由切割线分隔的器件区域4。器件结构形成于多个器件区域4中的每个区域中。尽管对器件结构没有特别限制,但是其例如是开关元件结构。具体地,当从与半导体衬底1的上表面1a正交的方向观察时,即当从上方观察半导体衬底1时,开关元件结构包括布置在器件区域4的中心区域侧的元件区域和设置在元件区域周围的端部区域。元件区域是设置绝缘栅极的区域和电流流过的区域。端部区域是设置高击穿电压结构(例如,保护环结构或RESURF层)的区域。这种开关元件结构的例子包括MOSFET(金属氧化物半导体场效应晶体管)和IGBT(绝缘栅双极晶体管)。

如图4和图5所示,在沟槽形成步骤(图1中的步骤S1)中,沟槽6使用干法蚀刻技术在半导体衬底1的上表面1a上形成,以从上表面1a延伸预定尺寸。在这样的示例中,所述沟槽6包括多个沿y方向延伸并在x方向上设置的第一沟槽6a,以及多个沿x方向延伸并在y方向上设置的第二沟槽6b。多个第一沟槽6a中的每一个在y方向上从半导体衬底1的一个端面延伸到另一端面,并且在x方向上以规则间隔设置。多个第二沟槽6b中的每一个在x方向上从半导体衬底1的一个端面延伸到另一端面,并且在y方向上以规则间隔设置。此外,在图5中,为了使附图更清楚,仅示出了多个第一沟槽6a和多个第二沟槽6b的一部分。

多个第一沟槽6a的一部分延伸跨过多个器件区域4,并且在器件区域4中形成的器件结构的元件区域内延伸。类似地,多个第二沟槽6b的一部分也延伸跨过多个器件区域4,并且在器件区域4中形成的器件结构的元件区域内延伸。第一沟槽6a和第二沟槽6b的这种设置减小了器件结构的元件区域的面积,从而降低了器件结构可以承载的最大电流。因此,第一沟槽6a和第二沟槽6b的设置适当地考虑了器件结构的应力松弛和电气特性而设定,这将在后面描述。

在沟槽形成步骤之前,半导体衬底1经常翘曲,使得由于在如晶体生长和退火的过程中施加的热应力而使下表面1b变得凸起。通过执行沟槽形成步骤,半导体衬底1的热应力减小,并且半导体衬底1的翘曲减少。在沟槽形成步骤之后,执行器件结构的形成步骤。

如图6所示,在激光照射步骤(图1中的步骤S2)中,半导体衬底1的在预定深度延伸的平面表面3被激光照射。照射激光,以便从半导体衬底1的未形成沟槽6的下表面1b在半导体衬底1的预定深度处收集激光。例如,激光是具有透射半导体衬底(例如,在该示例中为氮化镓衬底)的波长范围的激光。在激光收集点的位置处,形成半导体衬底1的晶体(在本示例中为氮化镓单晶)被加热和分解。结果,作为形成半导体衬底1的晶体的复合原子的沉淀,例如作为氮化镓的沉淀层,在激光收集点的位置处形成改变层作为沉淀层。改变层的强度低于形成半导体衬底1的晶体的强度。因此,改变层的强度低于半导体衬底1的周围晶体的强度。

如图7所示,在剥离步骤(图1中的步骤S3)中,具有器件结构的器件层2沿着激光照射的平面表面3从半导体衬底1剥离。具体地,将粘合片附接在半导体衬底1的上表面1a和下表面1b的每个表面上,并且通过拉动粘合片从半导体衬底1剥离器件层2。在该示例中,器件层2从半导体衬底1在x方向上的一端(即图7中的左端)朝向另一端(即图7中的右端)剥离。在该剥离步骤中,在沟槽形成步骤6中形成的沟槽保持未填充。在这种情况下,由于保持半导体衬底1的翘曲可抑制的状态,由激光照射形成的改变层在半导体衬底1内的同一平面上延伸。结果,当器件层2从半导体衬底1剥离时,剥离力可以如图7中的箭头所示沿改变层适当地传递,使得器件层2能够适当地从半导体衬底1剥离。

如上所述,在该剥离步骤中,器件层2从半导体衬底1的一端在x方向上朝向另一端从半导体衬底1剥离。半导体衬底1的翘曲在沟槽6的节距窄且沟槽6重复出现的方向上适当减小。在半导体衬底1中,x方向是沟槽6的节距最小的方向,x方向上的翘曲适当减小。在该剥离步骤中,由于器件层2沿x方向从半导体衬底1剥离,剥离力可以沿改变层适当地传递。出于同样的原因,在剥离步骤中,器件层2可以从半导体衬底1的一端在y方向上朝向另一端从半导体衬底1剥离。

在该示例的剥离步骤中,沟槽形成步骤6中形成的沟槽是未填充的。可替代地,沟槽6可以填充有比半导体衬底1(即本例中的氮化镓衬底)的材料具有更低热膨胀系数的材料。通过用具有低热膨胀系数的材料填充沟槽6,可以抑制半导体衬底1的翘曲,并抑制由于残留在沟槽6中的工艺残留物而产生的异物。具有这种低热膨胀系数的材料没有特别限制,但可以是例如氧化硅(SiO2)或氮化硅(SiN)。当使用这些绝缘材料时,它们也可以用作器件结构端接区域中高击穿电压结构的一部分。

已经从其剥离器件层2的半导体衬底1被重新用于制造半导体器件。例如,在对半导体衬底1的剥离表面进行抛光和蚀刻之后,使用外延晶体生长技术在剥离表面上形成外延层,从而能够在这种外延层上形成器件结构。

如图8所示,在切割步骤(图1中的步骤S4)中,在从半导体衬底1剥离的器件层2上执行抛光工艺、电极形成工艺等之后,切割多个器件(即,也可以称为管芯)以完成半导体器件。

在上述实施例中,当从上表面1a的一侧观察半导体衬底1时,第一沟槽6a和第二沟槽6b被设置成彼此交叉。代替这样的设置,如图9的修改所示,当从上方观察半导体衬底1时,第一沟槽6a和第二沟槽6b可以以平面T形连接。与上述实施例中沟槽相互交叉的情况相比,第一沟槽6a和第二沟槽6b之间的连接部分处的应力减小,并且减少了对半导体器件1的损坏。

此外,如图10的修改所示,当从上方观察半导体衬底1时,沟槽6可以像无间隙设置的六边形一样延伸。此外,沟槽6可以延伸以形成蜂窝结构,其中规则的六边形没有间隙地设置。在这样的示例中,半导体衬底1是六方晶体氮化镓衬底,并且半导体衬底1的厚度方向(z轴)是c轴。此外,六边形的每一边都平行于m平面、a平面或任何其它任意平面延伸。在这种修改中,当从上方观察半导体衬底1时,沟槽6形成为沿成120°角度的三个方向重复出现,从而使半导体衬底1的翘曲作为一个整体很好地平衡。此外,由于沟槽6连接部分处的沟槽6之间的角度变为钝角,因此该部分处的应力减小,并且对半导体衬底1的损坏是可抑制的。

此外,在上述实施例和修改中,沟槽6在半导体衬底1的上表面上连续延伸而不中断。代替这些例子,或者除了这些例子之外,还可以分布沟槽。例如,当从上方观察半导体衬底1时,可以形成在器件区域4中形成电路的沟槽,或者可以形成沿着切割线5在器件区域4周围形成电路的沟槽。

沟槽6的横截面形状没有特别限制。例如,底面可具有朝向下方突出的凸曲面。在具有这种横截面形状的沟槽6中,施加到沟槽6底部的应力减小,并且对半导体衬底1的损坏是可抑制的。

此外,沟槽6的深度没有特别限制,但可比外延层更深。半导体衬底1翘曲的原因之一被认为是在外延层的晶体生长过程中施加到外延层的应力(即,主要是拉伸应力)。因此,通过形成比外延层更深的沟槽6,半导体衬底1的翘曲被有效地减少。

(关于沟槽节距)

在以下条件下对上述示例的半导体衬底1进行了剥离试验。

半导体衬底1的直径:50mm

半导体衬底1的厚度:0.4mm

第一沟槽6a的宽度:10μm

第一沟槽6a的深度:10μm

第一沟槽6a的节距:1mm

第二沟槽6b的宽度:10μm

第二沟槽6b的深度:10μm

第二沟槽6b的节距:1mm

由剥离试验的结果证实,与没有形成沟槽的情况相比,适当剥离的概率(即剥离成功率)大大提高。具体而言,无沟槽示例的剥离成功率为25%,而有沟槽示例的剥离成功率为75%。在对应于下面所示的SEMI标准的晶圆尺寸中,使用简单的梁均匀分布载荷方程计算用于获得与剥离试验相同的载荷分布的沟槽的节距,并将结果绘制在图11中。x轴是半导体衬底的直径,y轴是沟槽节距。

[表1]

图11中的回归线表明,当沟槽6的节距为半导体衬底1直径的0.0177倍时,可以获得与剥离试验相当的剥离成功率。根据该结果,在形成为在一个主表面上沿至少一个方向重复出现的沟槽中,当沿至少一个方向测量的沟槽的最大节距等于或小于半导体衬底直径的0.0177倍时,可以获得等于或高于上述剥离试验的剥离成功率。

例如,制造半导体器件的方法包括:在半导体衬底的具有器件结构的第一主表面上形成多个沟槽;将激光从半导体衬底的第二主表面照射到预定的内表面,该内表面在半导体衬底的预定深度处定位并延伸,并沿着激光照射的预定内表面从半导体衬底剥离器件层。剥离是在半导体衬底的第一主表面上形成沟槽的状态下进行的。剥离步骤可以在沟槽未填充或填充有具有低于半导体衬底的热膨胀系数的材料的状态下进行。在本公开中,其它步骤和工艺可以根据条件适当地改变。

尽管以上详细描述了实施例,但这些仅仅是示例,并不限制本公开的范围。本公开中描述的技术包括上述特定示例的各种变化和修改。在本说明书或附图中描述的技术元件单独地或以各种组合显示出技术有用性,其不仅限于上述组合。此外,本说明书或附图中所示的技术同时实现多个目标,或者实现多个目标中的至少一个。

- 半导体器件、半导体封装及制造半导体器件的方法

- 制造半导体器件的方法和半导体器件

- 制造半导体器件的方法和半导体器件

- 一种半导体器件的制造方法及半导体器件

- 半导体器件的制造方法及半导体器件

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置