数据传输的物理地址管理方法、装置、存储介质和设备

文献发布时间:2024-01-17 01:27:33

技术领域

本公开涉及数据传输技术领域,尤其是一种数据传输的物理地址管理方法、装置、存储介质和设备。

背景技术

PCIE(peripheral component interconnect express,高速串行计算机扩展总线标准系统)通常由一个RC(Root Complex根复合体,通常对应数据传输的发送端)节点和一个或多个EP(Endpoint终点,通常对应数据传输的接收端)节点组成,其中RC和EP之间的通信主要通过DMA(direct memory access,直接内存访问)的方式进行数据的传输和通信。在RC节点与EP节点之间通过DMA进行数据传输的过程中,需要接收端的物理地址作为目的地址接收数据,因此在进行DMA之前,发送端就需要知道接收端的一块连续的物理地址作为接收数据的目的地址。

发明内容

本公开的实施例提供了一种数据传输的物理地址管理方法、装置、存储介质和设备。

根据本公开实施例的一个方面,提供了一种数据传输的物理地址管理方法,包括:

基于连续的预设大小的物理地址确定用于接收待传输数据的数据接收地址,同步所述数据接收地址对应的第一地址信息;

将所述待传输数据存储在目标地址;其中,所述目标地址为所述数据接收地址中的部分或全部;

基于与所述待传输数据相关的计数信息,确定所述目标地址的回收状态;

根据所述目标地址的回收状态,回收所述目标地址,同步所述目标地址对应的第二地址信息。

根据本公开实施例的另一方面,提供了一种数据传输的物理地址管理装置,包括:

地址申请模块,用于基于连续的预设大小的物理地址确定用于接收待传输数据的数据接收地址,同步所述数据接收地址对应的第一地址信息;

数据存储模块,用于将所述待传输数据存储在目标地址;其中,所述目标地址为所述数据接收地址中的部分或全部;

回收状态确定模块,用于基于与所述待传输数据相关的计数信息,确定所述目标地址的回收状态;

地址回收模块,用于根据所述目标地址的回收状态,回收所述目标地址,同步所述目标地址对应的第二地址信息。

根据本公开实施例的又一方面,提供了一种计算机可读存储介质,所述存储介质存储有计算机程序,所述计算机程序用于执行上述任一实施例所述的数据传输的物理地址管理方法。

根据本公开实施例的还一方面,提供了一种电子设备,所述电子设备包括:

处理器;

用于存储所述处理器可执行指令的存储器;

所述处理器,用于从所述存储器中读取所述可执行指令,并执行所述指令以实现上述任一实施例所述的数据传输的物理地址管理方法。

基于本公开上述实施例提供的数据传输的物理地址管理方法、装置、存储介质和设备,通过与待传输数据相关的计数信息,来回收用户不再使用的目标地址,将目标地址对应的第二地址信息进行同步,实现简单高效的地址释放,提高了目标地址的利用率,通过简单高效的地址管理方式,提升了数据传输的效率。

下面通过附图和实施例,对本公开的技术方案做进一步的详细描述。

附图说明

通过结合附图对本公开实施例进行更详细的描述,本公开的上述以及其他目的、特征和优势将变得更加明显。附图用来提供对本公开实施例的进一步理解,并且构成说明书的一部分,与本公开实施例一起用于解释本公开,并不构成对本公开的限制。在附图中,相同的参考标号通常代表相同部件或步骤。

图1-1是本公开一示例性实施例提供的数据传输系统的结构示意图;

图1-2是本公开另一示例性实施例提供的数据传输系统的结构示意图;

图1-3是本公开又一示例性实施例提供的数据传输系统的结构示意图;

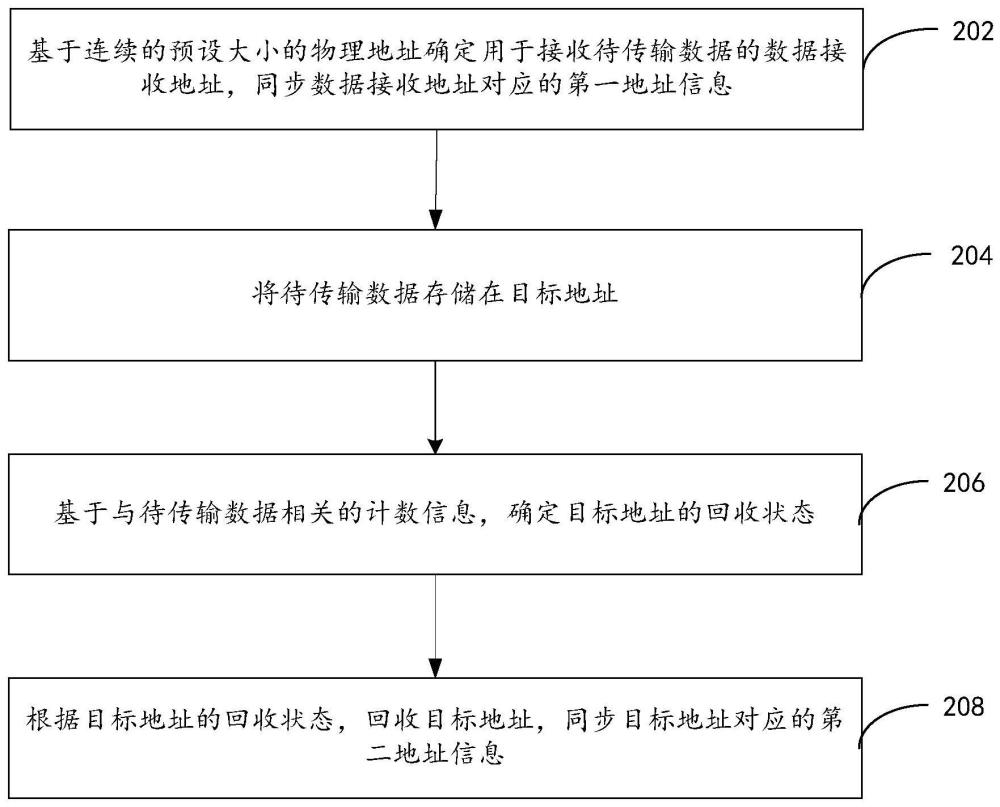

图2是本公开一示例性实施例提供的数据传输的物理地址管理方法的流程示意图;

图3是本公开图2所示的实施例中步骤204的一流程示意图;

图4-1是本公开图2所示的实施例中步骤206的一流程示意图;

图4-2是本公开一示例性实施例提供的数据传输的物理地址管理方法中地址信息同步的示意图;

图5是本公开图2所示的实施例中步骤204的另一流程示意图;

图6-1是本公开图2所示的实施例中步骤204的又一流程示意图;

图6-2是本公开图2所示的实施例中步骤204的一个示例性的地址管理示意图;

图7是本公开一示例性实施例提供的数据传输的物理地址管理装置的结构示意图;

图8-1是本公开另一示例性实施例提供的数据传输的物理地址管理装置的结构示意图;

图8-2是本公开又一示例性实施例提供的数据传输的物理地址管理装置的结构示意图;

图8-3是本公开还一示例性实施例提供的数据传输的物理地址管理装置的结构示意图;

图8-4是本公开再一示例性实施例提供的数据传输的物理地址管理装置的结构示意图;

图8-5是本公开又再一示例性实施例提供的数据传输的物理地址管理装置的结构示意图;

图9是本公开一示例性实施例提供的电子设备的结构图。

具体实施方式

为了解释本公开,下面将参考附图详细地描述本公开的示例实施例,显然,所描述的实施例仅是本公开的一部分实施例,而不是全部实施例,应理解,本公开不受示例性实施例的限制。

应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本公开的范围。

在实现本公开的过程中,发明人发现,相关技术中在使用PCIE在RC和EP之间进行DMA方式的数据传输时,至少存在以下问题:每一次通过DMA进行数据传输,都需要接收端的物理地址作为目的地址接收数据;向该目的地址发送数据后,如果目的地址的数据用户没有使用完成或者被用户拷贝走,则不应该向该地址继续发送数据,否则会造成之前数据的写覆盖,接收的数据就是不正确的。

图1-1是本公开一示例性实施例提供的数据传输系统的结构示意图。RC和EP是两个独立的芯片,并且具有独立的操作系统,如果在两个芯片间使用DMA方式传输数据时,需要知道接收端的一段物理地址,比如RC中一段物理地址src1(RC中可包括多段物理地址,例如,如图1-1所示包括三段:src1、src2和src3)中的数据通过DMA传输到EP中一段物理地址dst1(EP中可包括多段物理地址,例如如图1-1所示包括三段:dst1、dst2和dst3)的位置上;在发送端主动发送数据前,需要知道接收端的一段物理地址,该地址值是在接收端申请的,接收端申请后,需要将地址信息同步给发送端;这样发送端才可以开始发送数据。因此需要有一个地址信息同步机制,在发送端可以选择可用的地址作为发送目的地址;在数据发送过程中,也需要有地址管理单元,发送端可以从地址管理单元中可以获取到可用的发送地址,接收端也可以将不再使用的地址反馈给地址管理单元,防止地址管理单元中的地址被一直消耗导致没有可用的地址。为了解决这些技术问题,本公开提出了如图1-2所示的数据传输系统。

图1-2是本公开另一示例性实施例提供的数据传输系统的结构示意图。如图1-2所示,包括数据接收端11和数据发送端12。可选地,该数据传输系统可以应用在系统级芯片(System on Chip,SOC)中,数据接收端11可以是系统级芯片中的控制逻辑模块或存储模块;数据发送端12可以是系统级芯片中与外部进行通讯的接口模块。

在使用PCIE在数据发送端(RC)12和数据接收端(EP)11之间进行DMA方式的传输时,RC可对应多个EP,例如,如图1-3提供的又一数据传输系统的结构示意图所示,首先,数据接收端11预先申请一段连续的预设大小的物理地址,作为接收数据的内存池;数据接收端11将物理地址对应的地址信息同步给数据发送端12。

数据发送端12读取到地址信息后,将物理地址加入到数据发送端12的内存管理单元中,数据发送端12每次发送数据时可以从内存管理单元中获取数据对应的地址大小,作为数据发送的目标地址;数据发送端12将数据发送到数据接收端11的目标地址中。

数据接收端11在基于目标地址接收数据后,通过计数信息确定目标地址中的数据不再被使用后,回收该目标地址,并将该目标地址对应的地址信息同步给数据发送端12,以便于数据发送端12向该目标地址继续发送数据,提升了物理地址的利用率。

图2是本公开一示例性实施例提供的数据传输的物理地址管理方法的流程示意图。本实施例可应用在系统级芯片等电子设备上,如图2所示,包括如下步骤:

步骤202,基于连续的预设大小的物理地址确定用于接收待传输数据的数据接收地址,同步数据接收地址对应的第一地址信息。

可选地,该步骤可在系统级芯片的数据接收端执行,在初始通信阶段,或者数据接收端下线并重新上线后,会进行地址信息的申请和同步,防止写入到已经无效的物理地址中。

其中,预设大小可以根据实际情况设定大小或根据经验值进行设置;第一地址信息中至少包括数据接收地址的位置和大小;连续的物理地址保证了接收待传输数据的完整性,避免由于物理地址不连续导致的无法接收完整的待传输数据的问题;在数据接收端申请了数据接收地址后,将第一地址信息同步到系统级芯片的数据发送端,以便于数据发送端根据第一地址信息发送待传输数据。

步骤204,将待传输数据存储在目标地址。

其中,目标地址为数据接收地址中的部分或全部。

在一实施例中,由于第一地址信息已经同步到数据发送端,因此,数据发送端在发送待传输数据时,根据待传输数据的大小可确定对应该待传输数据的目标地址,数据接收端基于该目标地址接收待传输数据,克服了接收地址与待传输数据大小不匹配导致的无法正确接收的问题,提升了数据接收效率和准确率。

步骤206,基于与待传输数据相关的计数信息,确定目标地址的回收状态。

可选地,可通过计数信息来表示待传输数据是否被操作,例如,通过计数信息表示操作待传输数据的数据应用端的数量;目标地址的回收状态包括可回收状态或不可回收状态,不同的计数信息对应不同的回收状态,本实施例通过计数信息来确定回收状态,提升了回收状态的准确率,减少了回收状态的误判。

步骤208,根据目标地址的回收状态,回收目标地址,同步目标地址对应的第二地址信息。

响应于目标地址的回收状态为可回收状态,回收目标地址,使该目标地址可以重新接收新的数据,而不会发生数据被覆盖的问题;响应于目标地址的回收状态为不可回收状态,不回收该目标地址,目标地址被当前待传输数据占用,不能接收新的数据。

另外,当数据接收端程序下线时,数据发送端同步的第一地址信息全部变为不可用状态,数据发送端会将第一地址信息清除,等待下一次数据接收端上线后同步新的地址信息。

本公开上述实施例提供的数据传输的物理地址管理方法,通过待传输数据对应的计数信息确定目标地址的回收状态,对回收状态为可回收状态的目标地址进行释放,实现简单高效的地址释放,通过回收用户不再使用的目标地址,将目标地址对应的第二地址信息进行同步,提高了目标地址的利用率,通过简单高效的地址管理方式,提升了数据传输的效率。

如图3所示,在上述图2所示实施例的基础上,步骤204可包括如下步骤:

步骤2041,通过确定用于存储待传输数据的目标地址,接收待传输数据。

可选地,基于第一地址信息,从数据接收地址确定连续的对应待传输数据大小的一段物理地址作为目标地址,该目标地址的大小与待传输数据相匹配。

步骤2042,将待传输数据和目标地址的地址信息存入智能指针。

可选地,数据接收端将接收到的待传输数据和目标地址的地址信息存放在一个智能指针中,并将该智能指针提供给用户操作,用户可以从该智能指针获取地址信息中的待传输数据。

步骤2043,通过智能指针接收至少一个数据应用端对目标地址中存储的待传输数据的操作。

数据应用端可以是通过智能指针对待传输数据进行操作的任意设备端或任意设备中的应用模块(或单元),例如,数据接收端内部设置的消息地址回收单元、外部数据读取装置、外部数据应用装置等。

本实施例中,通过将存放了地址信息和待传输数据的智能指针提供给用户,用户通过智能指针实现对待传输数据的操作,并且,智能指针每接收一个操作对待传输数据的计数信息加一,即通过智能指针接收用户的操作并对操作数进行累计,以实现对待传输数据的状态监测,本实施例通过智能指针实现对待传输数据和目标地址进行管理,基于智能指针的特性确定待传输数据的引用计数,基于引用计数确定计数信息,无需额外引入其他计数工具对计数信息进行计算,实现快速确定计数信息。

如图4-1所示,在上述图2所示实施例的基础上,步骤206可包括如下步骤:

步骤2061,基于智能指针确定与待传输数据相关的计数信息。

其中,计数信息表示操作待传输数据的数据应用端的数量。

智能指针(smart pointer)的一种通用实现技术是使用引用计数(referencecount)。智能指针类将一个计数器与类指向的对象相关联,引用计数跟踪该类有多少个对象的指针指向同一对象。本实施例利用智能指针确定的引用计数来确定计数信息,例如,将引用计数直接作为计数信息,或将引用计数经过计算后(例如,引用计数加或减设定数值等)作为计数信息,因此,通过将待传输数据和目标地址的地址信息存入智能指针,即可通过智能指针确定待传输数据对应的计数信息。

步骤2062,基于计数信息,确定目标地址的回收状态。

本实施例中,如果用户不再使用该条消息,即不存在其他数据应用端对待传输数据进行操作,该智能指针的计数信息会降低为设定数值,此时该目标地址的回收状态为可回收状态;因此,可实现数据接收端通过智能指针确定的计数信息,来回收用户不再使用的待处理数据对应的目标地址;通过智能指针确定待传输数据的计数信息,再通过计数信息可直接确定待传输数据对应的目标地址是否可被回收的回收状态,根据回收状态实现对目标地址的回收,整个过程简单高效,通过简单高效的地址管理方式,提升了数据传输的效率。

可选地,步骤206还可以包括:

确定与待传输数据相关的计数信息与设定数值之间的对应关系;

基于对应关系,确定目标地址的回收状态。

本实施例中,计数信息表示操作待传输数据的数据应用端的数量。可选地,响应于计数信息与设定数值之间的对应关系为相等,确定目标地址的回收状态为可回收状态;响应于计数信息与设定数值之间的对应关系为不相等,确定目标地址的回收状态为不可回收状态。本实施例中,可通过在数据接收端内部设置消息地址回收单元,该消息地址回收单元会检查当前待传输数据的计数信息,如果某个待传输数据的计数信息与设定数值相等时(例如,设定数值可以为1,在该示例中计数信息等于引用计数,引用计数为1表示待传输数据仅被消息地址回收单元操作),说明用户不再使用该待传输数据,则会对待传输数据对应的目标地址进行回收。

可选地,同步数据接收地址对应的第一地址信息,包括:

通过基址寄存器同步数据接收地址对应的第一地址信息。

本实施例中,使用基址寄存器(base address register,bar)空间同步初始申请的第一地址信息,数据接收端会在bar空间的指定位置写入同步的第一地址信息,bar空间为数据接收端和数据发送端都可以访问的一段共享空间,数据发送端可以从bar空间的指定位置读取该第一地址信息,这样第一地址信息就在数据发送端和数据接收端之间完成了同步。例如,如图4-2所示,在数据接收端的内存中预先申请第一地址信息(从空闲地址的起始位置开始读取一段连接的地址),将第一地址信息写入bar空间,其中,为了确保指定位置的地址信息已经准备好了,可以在第一地址信息的前后加上预设的magic nmuber(图中简写为magic);第一地址信息的结构包括addr(地址,图中仅示出addr_1和addr_2作为示例,具体应用中数量根据实际情况确定)以及len(功能为返回文本字符串中用于代表字符的字节数);以及channel(通道);在bar空间写入第一地址信息时可以按照channel_id,依次从后向前放置;其中,int32_t表示整数类型的宽度正好是32位;int64_t表示整数类型的宽度正好是64位;char用于C或C++中定义字符型变量,只占一个字节,取值范围为-128~+127;总数(total)为33byte(字节)。

可选地,同步第二数据接收地址对应的第二地址信息,包括:

通过直接内存访问的方式同步目标地址对应的第二地址信息。

本实施例中,数据接收端对可回收状态的第二地址信息的反馈采用了DMA的方式传输,DMA的传输速度快,使传输更加高效,并且,由于DMA对CPU占用比较低,更能发挥出PCIE DMA传输的速度优势。

在上述实施例中,初始申请的第一地址信息的同步采用bar空间同步的方式,而在数据传输过程中,采用DMA的方式反馈数据接收端不再使用的第二地址信息,通过bar空间同步和DMA两种同步方式的组合,使物理地址信息的管理更高效。

可选地,步骤204还可以包括:

根据第一地址信息,以及待传输数据的大小,确定用于存储待传输数据的目标地址;

利用直接内存访问的方式,将待传输数据存入目标地址。

本实施例中,通过在数据发送端中设置的内存管理单元,对第一地址信息进行管理,使发送的待传输数据的大小没有固定限制,而是基于待传输数据的大小从第一地址信息对应的数据接收地址中确定一段连续的物理地址作为目标地址,该目标地址的大小与待传输数据相匹配,由于目标地址的大小与待传输数据相匹配,可直接通过DMA方式传输待传输数据,使DMA的发送更加高效简单。

如图5所示,在另一些实施例中,在上述图2所示实施例的基础上,步骤204可包括如下步骤:

步骤501,根据第一地址信息确定数据接收地址中包括的空闲地址。

其中,空闲地址为数据接收地址中未存储数据的物理地址。本实施例中,数据发送端通过内存管理单元对同步的第一地址信息进行管理,当第一地址信息对应的数据接收地址中某些地址被占用后,内存管理单元对齐占用情况进行记录,因此,通过内存管理单元确定数据接收地址中的空闲地址的大小和位置。

步骤502,基于空闲地址确定目标地址的起始位置。

在确定空闲地址的位置后,即可基于该空闲地址的起始位置作为目标地址的起始位置,如果从空闲地址中的任意位置作为目标地址的起始位置,那么在目标地址之前可能存在一些较小的空闲地址,这些空闲地址会成为碎片地址,碎片地址由于大小较小而无法使用,降低了空闲地址的利用率,不利于数据传输;而本实施例基于空闲地址的起始位置作为目标地址的起始位置,避免出现碎片地址,提升了空闲地址的利用率。

步骤503,根据待传输数据的大小,确定地址偏移量。

可选地,将待传输数据的大小作为地址偏移量,即,要存储待传输数据需要对应大小的地址偏移量。

步骤504,基于起始位置和地址偏移量,确定目标地址。

可选地,从起始位置开始叠加地址偏移量,即可获得结束位置,从起始位置到结束位置对应的一段连续物理地址即为确定的目标地址,该目标地址的大小由于由地址偏移量确定,因此与待传输数据相匹配。

步骤505,利用直接内存访问的方式,将待传输数据存入目标地址。

本实施例中,每次发送数据时可以从内存管理单元中获取适合大小的地址偏移量,作为数据发送的目的地址,在确定了与待传输数据相匹配的目标地址后;发送数据的大小可以是任意大小,不会限制内存块为固定的大小;由于可以发送任意大小的数据,提升了数据传输的效率。

如图6-1所示,在又一些实施例中,在上述图2所示实施例的基础上,步骤204可包括如下步骤:

步骤601,根据待传输数据的大小和第二地址信息,确定是否存在与待传输数据的大小匹配的第二地址信息;如果存在,执行步骤602,否则,执行步骤603。

步骤602,将匹配的第二地址信息对应的物理地址作为待传输数据对应的目标地址,将待传输数据存入目标地址。

步骤603,基于待传输数据的大小和第一地址信息,从数据接收地址中获取一段连续的物理地址作为待传输数据对应的目标地址,将待传输数据存入目标地址。

本实施例中,数据发送端的内存管理单元会同时管理初始同步的一整块大的第一地址信息和数据接收端不再使用的至少一个第二地址信息,数据发送端发送数据时可用从两块内存池(一个内存池对应第一地址信息,另一个内存池对应至少一个第二地址信息)中获取可用的地址和大小得到内存块。可选地,在匹配地址信息时,会优先从回收的离散的第二地址信息中查找合适的地址;如果没有合适大小的第二地址信息,则从第一地址信息对应的数据接收地址中,重新分配一块合适的地址。例如,如图6-2所示,数据发送端的内存管理单元管理原始连续的内存池(对应第一地址信息)和数据接收端返回的第二地址信息;并且,数据发送端可以从原始连续的内存池或第二地址信息中获取可用的地址信息作为数据的目的地址;消息地址回收单元进行消息队列检查,检查消息队列(Message Holder),检查消息的引用计数,如果计数信息为1(在该示例中计数信息等于引用计数,引用计数为1表示待传输数据仅被消息地址回收单元操作),说明用户不再使用该待传输数据,则会对待传输数据对应的目标地址进行回收;当目标地址可被回收,将该消息移出消息队列,并将目标地址发送给数据发送端作为第二地址信息;本实施例可以节省地址,先使用离散的地址,使数据接收地址中保存有更大的连续物理地址,用于接收更大的数据,克服对发送的数据的大小限制问题,即使后续数据发送端发送很大的数据,也可以找到符合大小的地址;使DMA传输更加简单高效。

本公开实施例提供的任一种数据传输的物理地址管理方法可以由任意适当的具有数据处理能力的设备执行,包括但不限于:终端设备和服务器等。或者,本公开实施例提供的任一种数据传输的物理地址管理方法可以由处理器执行,如处理器通过调用存储器存储的相应指令来执行本公开实施例提及的任一种数据传输的物理地址管理方法。下文不再赘述。

图7是本公开一示例性实施例提供的数据传输的物理地址管理装置的结构示意图。如图7所示,提供的装置包括:

地址申请模块71,用于基于连续的预设大小的物理地址确定用于接收待传输数据的数据接收地址,同步数据接收地址对应的第一地址信息。

数据存储模块72,用于将待传输数据存储在目标地址。

其中,目标地址为数据接收地址中的部分或全部。

回收状态确定模块73,用于基于与待传输数据相关的计数信息,确定目标地址的回收状态。

地址回收模块74,用于根据目标地址的回收状态,回收目标地址,同步目标地址对应的第二地址信息。

本公开上述实施例提供的数据传输的物理地址管理装置,通过待传输数据对应的计数信息,来回收用户不再使用的目标地址,将目标地址对应的第二地址信息进行同步,实现简单高效的地址释放,提高了目标地址的利用率,通过简单高效的地址管理方式,提升了数据传输的效率。

图8-1是本公开另一示例性实施例提供的数据传输的物理地址管理装置的结构示意图。如图8-1所示,提供的装置中,数据存储模块72,包括:

数据接收单元721,用于通过确定用于存储待传输数据的目标地址,接收待传输数据;

指针存储单元722,用于将待传输数据和目标地址的地址信息存入智能指针;

操作接收单元723,用于通过智能指针接收至少一个数据应用端对目标地址中存储的待传输数据的操作。

在一些实施例中,回收状态确定模块73可以包括:

计数信息确定单元731,用于基于智能指针确定与待传输数据相关的计数信息;其中,计数信息表示操作待传输数据的数据应用端的数量。

状态确定单元732,用于基于计数信息,确定目标地址的回收状态。

图8-2是本公开又一示例性实施例提供的数据传输的物理地址管理装置的结构示意图。如图8-2所示,提供的装置中,回收状态确定模块73包括:

关系确定单元733,用于确定与待传输数据相关的计数信息与设定数值之间的对应关系;

地址回收单元734,用于基于对应关系,确定目标地址的回收状态。

图8-3是本公开还一示例性实施例提供的数据传输的物理地址管理装置的结构示意图。如图8-3所示,提供的装置中,数据存储模块72包括:

地址确定单元724,用于根据第一地址信息,以及待传输数据的大小,确定用于存储待传输数据的目标地址;

地址传输单元725,用于利用直接内存访问的方式,将待传输数据存入目标地址。

图8-4是本公开再一示例性实施例提供的数据传输的物理地址管理装置的结构示意图。如图8-4所示,提供的装置中,数据存储模块72,包括:

空闲地址确定单元801,用于根据第一地址信息确定数据接收地址中包括的空闲地址;其中,空闲地址为数据接收地址中未存储数据的物理地址;

起始位置确定单元802,用于基于空闲地址确定目标地址的起始位置;

偏移量确定单元803,用于根据待传输数据的大小,确定地址偏移量;

目标地址确定单元804,用于基于起始位置和地址偏移量,确定目标地址;

数据存入单元805,用于利用直接内存访问的方式,将待传输数据存入所述目标地址。

图8-5是本公开又再一示例性实施例提供的数据传输的物理地址管理装置的结构示意图。如图8-5所示,提供的装置中,数据存储模块72,包括:

地址匹配单元806,用于根据待传输数据的大小和第二地址信息,确定是否存在与待传输数据的大小匹配的第二地址信息;

第一存储单元807,用于响应于存在与待传输数据的大小匹配的第二地址信息,将匹配的第二地址信息对应的物理地址作为待传输数据对应的目标地址,将待传输数据存入目标地址;

第二存储单元808,用于响应于不存在与待传输数据的大小匹配的第二地址信息,基于待传输数据的大小和第一地址信息,从数据接收地址中获取一段连续的物理地址作为待传输数据对应的目标地址,将待传输数据存入目标地址。

下面,参考图9来描述根据本公开实施例的电子设备。该电子设备可以是第一设备和第二设备中的任一个或两者、或与它们独立的单机设备,该单机设备可以与第一设备和第二设备进行通信,以从它们接收所采集到的输入信号。

图9图示了根据本公开实施例的电子设备的框图。

如图9所示,电子设备90包括一个或多个处理器91和存储器92。

处理器91可以是中央处理单元(CPU)或者具有数据处理能力和/或指令执行能力的其他形式的处理单元,并且可以控制电子设备90中的其他组件以执行期望的功能。

存储器92可以包括一个或多个计算机程序产品,所述计算机程序产品可以包括各种形式的计算机可读存储介质,例如易失性存储器和/或非易失性存储器。所述易失性存储器例如可以包括随机存取存储器(RAM)和/或高速缓冲存储器(cache)等。所述非易失性存储器例如可以包括只读存储器(ROM)、硬盘、闪存等。在所述计算机可读存储介质上可以存储一个或多个计算机程序指令,处理器91可以运行所述程序指令,以实现上文所述的本公开的各个实施例的数据传输的物理地址管理方法以及/或者其他期望的功能。在所述计算机可读存储介质中还可以存储诸如输入信号、信号分量、噪声分量等各种内容。

在一个示例中,电子设备90还可以包括:输入装置93和输出装置94,这些组件通过总线系统和/或其他形式的连接机构(未示出)互连。

例如,在该电子设备是第一设备或第二设备时,该输入装置93可以是上述的麦克风或麦克风阵列,用于捕捉声源的输入信号。在该电子设备是单机设备时,该输入装置93可以是通信网络连接器,用于从第一设备和第二设备接收所采集的输入信号。

此外,该输入装置93还可以包括例如键盘、鼠标等等。

该输出装置94可以向外部输出各种信息,包括确定出的距离信息、方向信息等。该输出装置94可以包括例如显示器、扬声器、打印机、以及通信网络及其所连接的远程输出设备等等。

当然,为了简化,图9中仅示出了该电子设备90中与本公开有关的组件中的一些,省略了诸如总线、输入/输出接口等等的组件。除此之外,根据具体应用情况,电子设备90还可以包括任何其他适当的组件。

除了上述方法和设备以外,本公开的实施例还可以是计算机程序产品,其包括计算机程序指令,所述计算机程序指令在被处理器运行时使得所述处理器执行本说明书上述“示例性方法”部分中描述的根据本公开各种实施例的数据传输的物理地址管理方法中的步骤。

计算机程序产品可以以一种或多种程序设计语言的任意组合来编写用于执行本公开实施例操作的程序代码,所述程序设计语言包括面向对象的程序设计语言,诸如Java、C++等,还包括常规的过程式程序设计语言,诸如“C”语言或类似的程序设计语言。程序代码可以完全地在用户计算设备上执行、部分地在用户设备上执行、作为一个独立的软件包执行、部分在用户计算设备上部分在远程计算设备上执行、或者完全在远程计算设备或服务器上执行。

此外,本公开的实施例还可以是计算机可读存储介质,其上存储有计算机程序指令,计算机程序指令在被处理器运行时使得处理器执行上述“示例性方法”部分中描述的本公开各种实施例的数据传输的物理地址管理方法中的步骤。

计算机可读存储介质可以采用一个或多个可读介质的任意组合。可读介质可以是可读信号介质或者可读存储介质。可读存储介质例如但不限于包括电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。可读存储介质的更具体的例子(非穷举的列表)包括:具有一个或多个导线的电连接、便携式盘、硬盘、随机存取存储器(RAM)、只读存储器(ROM)、可擦式可编程只读存储器(EPROM或闪存)、光纤、便携式紧凑盘只读存储器(CD-ROM)、光存储器件、磁存储器件、或者上述的任意合适的组合。

以上结合具体实施例描述了本公开的基本原理,但是,在本公开中提及的优点、优势、效果等仅是示例而非限制,不能认为其是本公开的各个实施例必须具备的。另外,上述公开的具体细节仅是为了示例的作用和便于理解的作用,而非限制,上述细节并不限制本公开为必须采用上述具体的细节来实现。

本领域的技术人员可以对本公开进行各种改动和变型而不脱离本申请的精神和范围。这样,倘若本申请的这些修改和变型属于本公开权利要求及其等同技术的范围之内,则本公开也意图包含这些改动和变型在内。

- 一种后端存储设备的管理方法、装置、设备以及存储介质

- 多版本数据存储管理方法及装置、电子设备、存储介质

- 存储设备管理方法、装置及可读存储介质

- 存储设备管理方法、装置及可读存储介质

- 数据传输方法、装置、电子设备及存储介质

- 一种物理地址的识别方法、装置、计算机设备和存储介质

- 物理地址确定方法、装置、设备及存储介质