提高多元系III族氮化物基半导体材料晶体质量的方法

文献发布时间:2024-01-17 01:19:37

技术领域

本发明特别涉及一种提高多元系III族氮化物基半导体材料晶体质量的方法,属于半导体技术领域。

背景技术

氮化铝镓(AlGaN)基半导体是直接宽带隙材料,其禁带宽度在3.4eV~6.2eV之间连续可调,是制备工作波长在200nm至365nm之间紫外光电子器件(如紫外LED、探测器、激光器)的理想材料,在紫外光固化、杀菌消毒、生物医疗、日盲探测等领域具有广阔的应用前景。

由于缺乏大尺寸、低成本的AlN单晶衬底,AlGaN基半导体材料通常异质外延生长在蓝宝石、硅、碳化硅等衬底上。异质外延生长AlGaN通常需要首先生长一层AlN缓冲层以减小衬底和外延层之间的晶格失配。尽管如此,衬底/AlN半导体材料之间的晶格失配也会导致AlN材料中产生高密度的穿透位错缺陷,从而在AlN上外延生长的AlGaN材料中的穿透位错密度很高。此外,在AlN材料上外延生长AlGaN材料,面内晶格失配应变的弛豫将进一步增加AlGaN材料中的穿透位错密度。因此,目前AlGaN材料中的穿透位错密度普遍较高,材料晶体质量较差,在其上外延生长的其它氮化物半导体材料(如GaN等)晶体质量也很难大幅提高。

传统改善AlGaN晶体质量的有侧向外延生长法(ELOG),通过在AlGaN半导体材料或衬底表面制备掩膜图形,然后利用外延生长条件控制掩膜窗口区氮化物半导体材料的横向生长、合并,利用倾斜面的镜像力牵引位错倾斜拐弯,从而促进窗口区的穿透位错湮灭,进而降低穿透位错密度、提高材料质量。还有一种方法是通过原位刻蚀或生长条件控制形成孔洞、再合并的方法,其降低位错密度的原理与ELOG类似,只是不需要掩膜介质,而是通过原位孔洞合并过程中倾斜面的镜像力作用牵引位错拐弯。

现有技术中还公开了一种采用侧向外延ELOG提高Al(Ga)N基半导体材料晶体质量的方法,其主要是通过在成核层上制备掩膜图形,利用掩膜图形屏蔽一部分生长区域,然后在无掩膜介质的窗口区二次外延生长Al(Ga)N基半导体材料,利用窗口区材料侧向外延生长合并时位错的拐弯和湮灭,来降低材料中的穿透位错密度。这种方法虽然可以降低穿透位错密度,但面临掩膜介质高温分解导致Al(Ga)N半导体材料中杂质沾污的问题,影响材料光学和电学特性。更重要的是,在侧向外延生长过程中,在掩膜介质上横向生长的Al(Ga)N半导体材料与掩膜介质之间存在相互作用力,导致掩膜介质上的Al(Ga)N半导体材料产生倾斜Tilt角。有倾斜Tilt角的相邻侧翼区半导体材料在合并过程中不可避免地会形成新的位错、甚至晶界缺陷。此外,这种ELOG技术需要掩膜、图形化、二次外延生长,工艺繁琐,生产效率低,很难实际运用到大规模的商业化生产当中。

通过氢气原位刻蚀或调控Al(Ga)N生长条件形成孔洞,然后再横向生长促进孔洞合并,是一种更高效地降低AlGaN材料位错密度的方法。这种方法实施起来有两种方式:

第一种方式是在AlN薄膜内部通过控制温度、V/III比等生长条件来产生孔洞,而后再合并,通过降低AlN材料中的穿透位错密度来降低其上生长的AlGaN材料中的穿透位错密度。这种方法可以一定程度上降低AlN材料中的穿透位错密度,但却存在两方面问题:1)需要很厚的AlN材料来合并孔洞,使得AlN材料整体应力很大;并且由于AlN生长速率慢,外延成本提高,生产效率也大幅降低;2)这种方式通过降低AlN中的穿透位错来抑制其向AlGaN材料中延伸,但却无法抑制由于AlN/AlGaN界面晶格失配应变弛豫而产生的新位错。因此,采用这种方法来降低AlGaN材料中的穿透位错,效果十分有限;

第二种方式是直接在AlGaN材料中,高温下采用氢气原位刻蚀AlGaN材料表面,将位错线位置腐蚀出若干不连续分布地孔洞,然后原位沉积岛状SiNx插入层来填充孔洞并形成微掩膜,进而利用后续AlGaN材料的侧向外延生长来降低穿透位错密度;这种方式可以与方式一相结合,同时从AlN和AlGaN材料中抑制穿透位错,进而提高材料质量。然而,这种方式的问题在于,由于Al-N键能极强,高温氢气刻蚀AlGaN十分困难,不但耗时长,而且效果差;同时,要想精确控制原位SiNx岛来填充孔洞难度非常大,因此重复性、均匀性面临极大考验;由此可见,采用这种方式来降低AlGaN材料晶体质量并不实用。

发明内容

本发明的主要目的在于提供一种提高多元系III族氮化物基半导体材料晶体质量的方法,以克服现有技术中的不足。

为实现前述发明目的,本发明采用的技术方案包括:

本发明实施例提供了一种提高多元系III族氮化物基半导体材料晶体质量的方法,包括:

在一反应腔室内于衬底上生长形成第一半导体材料层;

向所述反应腔室内输入卤素基源对第一半导体材料层进行刻蚀,使所述第一半导体材料层表面形成多个凹陷部;

向所述反应腔室内输入氮源和金属源,在所述第一半导体材料层上生长形成第二半导体材料层。

与现有技术相比,本发明的优点包括:

1)本发明实施例提出的一种提高多元系III族氮化物基半导体材料晶体质量的方法,工艺简单,重复可控,完全适合大规模生产;

2)本发明实施例提出的一种提高多元系III族氮化物基半导体材料晶体质量的方法,可避免传统ELOG生长中掩膜介质分解导致的杂质污染等问题;

3)本发明实施例提供的一种提高多元系III族氮化物基半导体材料晶体质量的方法,采用的卤素基源可以完全兼容MOCVD设备,大幅简化了工艺流程,节约了成本。

附图说明

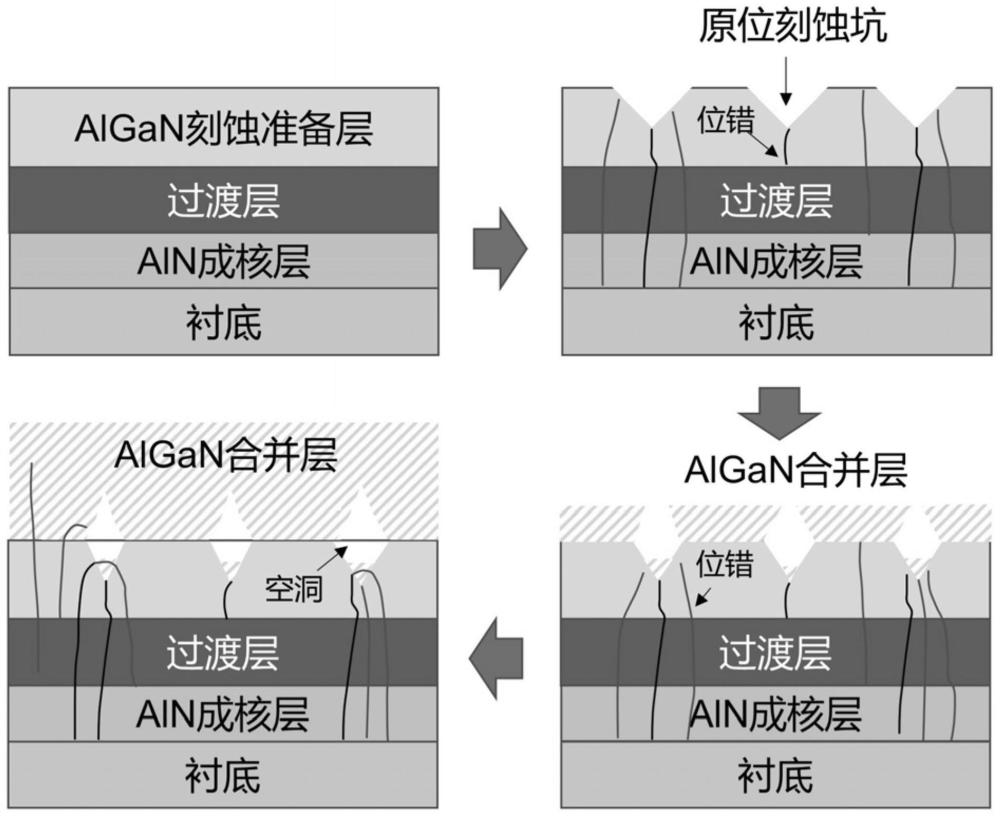

图1是本发明一典型实施案例中提供的一种原位刻蚀再合并制备高质量AlGaN材料的方法流程示意图;

图2a是本发明实施例1中利用卤素基原子/基团选择性刻蚀Al

图2b是发明实施例1中刻蚀孔洞合并之后的Al

图3是对比例1中在刻蚀后的Al

图4是对比例2中以TBCl处理后的Al

图5是对比例3中Al

具体实施方式

鉴于现有技术中的不足,本案发明人经长期研究和大量实践,得以提出本发明的技术方案。如下将对该技术方案、其实施过程及原理等作进一步的解释说明。

本发明实施例主要针对现有改善AlGaN等多元系III族氮化物基半导体材料晶体质量的方法,提出一种提高多元系III族氮化物基半导体材料晶体质量的方法:在AlGaN等多元系III族氮化物基半导体材料生长过程中,通过原位引入卤素基源,利用卤素基原子/基团与AlGaN等多元系III族氮化物基半导体材料化学反应活化能低的优势(化学分解过程),以及位错核心附近悬挂键密度高、易发生化学反应的特点,在较低地温度下即可对AlGaN等多元系III族氮化物基半导体材料进行高效率、选择性地刻蚀,从而原位产生刻蚀坑(或者称之为凹陷部或孔洞或者刻蚀位错坑);然后再通过AlGaN等多元系III族氮化物基半导体材料的侧向外延生长、合并来湮灭穿透位错,从而大幅提高AlGaN等多元系III族氮化物基半导体材料晶体质量;而且,可以通过控制反应室温度、卤素基源流量等条件,来控制刻蚀坑的尺寸和密度,从而大幅简化工艺流程,节约成本,同时提高良率,非常适合于商业化应用。

本发明实施例提供了一种提高多元系III族氮化物基半导体材料晶体质量的方法,包括:

在一反应腔室内于衬底上生长形成第一半导体材料层;

向所述反应腔室内输入卤素基源对第一半导体材料层进行刻蚀,使所述第一半导体材料层表面形成多个凹陷部;

向所述反应腔室内输入氮源和金属源,在所述第一半导体材料层上生长形成第二半导体材料层。

在一些较为具体的实施方案中,所述第一半导体材料层、第二半导体材料层的材质包括多元系III族氮化物。

在一些较为具体的实施方案中,所述多元系III族氮化物包括In

在一些较为具体的实施方案中,以卤素基源对第一半导体材料层进行刻蚀的温度、压力等条件,通常对第一半导体材料层刻蚀采用的温度低于第二半导体材料层的生长温度,刻蚀的压力高于第二半导体材料等生长压力,当然,也可以与第二半导体材料层的生长温度、压力等条件相同。

在一些较为具体的实施方案中,所述的方法包括:在第一温度及第一压力条件下对第一半导体材料层进行刻蚀,以及,在第二温度及第二压力条件下生长形成第二半导体材料层;所述第一温度低于第二温度,所述第一压力高于第二压力。

在一些较为具体的实施方案中,所述第一温度为500-1300℃,所述第一压力为10-500Torr。

在一些较为具体的实施方案中,所述第一温度为800-900℃,所述第一压力为50-200Torr。

在一些较为具体的实施方案中,所述的方法包括:在对第一半导体材料层进行刻蚀时,控制氮源的流量为0-100slm。

在一些较为具体的实施方案中,在对第一半导体材料层进行刻蚀时,控制氮源的流量为0.1-10slm。

在一些较为具体的实施方案中,所述第二温度为500-1300℃,所述第二压力为10-500Torr。

在一些较为具体的实施方案中,所述第二温度为1000-1300℃,所述第二压力为50-100Torr。

在一些较为具体的实施方案中,所述的方法包括:在生长形成第二半导体材料层时,控制氮源的流量为0.1-100slm。

在一些较为具体的实施方案中,在生长形成第二半导体材料层时,控制100 在一些较为具体的实施方案中,所述卤素基源的通入流量为10-1000sccm。 在一些较为具体的实施方案中,所述卤素基源的通入时间为0.1-120min。 在一些较为具体的实施方案中,所述卤素基源包括氯代物、氟代物、溴代物中的任意一种或两种以上的组合,但不限于此。 在一些较为具体的实施方案中,所述氯代物包括叔丁基氯、氯化氢、氯气、四氯甲烷中的任意一种或两种以上的组合,但不限于此。 在一些较为具体的实施方案中,所述第一半导体材料形成在应力过渡层上,所述应力过渡层形成在底层上,其中,所述应力过渡层和底层的材质均为III族氮化物。 在一些较为具体的实施方案中,所述的方法还包括:在所述第二半导体材料层上生长外延层。 如下将结合附图对该技术方案、其实施过程及原理等作进一步的解释说明,除非特别说明的之外,本发明实施例中外延生长各结构层的设备可以是本领域技术人员已知的。 为实现上述发明目的,如下以AlGaN材料为例,请参阅图1,本发明实施例提供的一种提高多元系III族氮化物基半导体材料晶体质量的方法,可以包括如下步骤: (1)首先,采用金属化学气相沉积(MOCVD)等方法在在反应室内于衬底上依次外延生长AlN、AlGaN应力过渡层、AlGaN刻蚀准备层(即前述第一半导体材料层,下同); (2)停止通入Al、Ga金属源,将反应室的压力调整至10-500Torr,温度调整至500-1300℃,NH (3)向反应室内通入卤素基源,卤素基源的通入流量为10-1000sccm,通入时间为0.1-120min,以对AlGaN刻蚀准备层表面进行原位刻蚀,形成一定尺寸的刻蚀坑(即前述凹陷部,下同),所述刻蚀坑的深度大于50nm; (4)停止卤素基源的供应,将反应室的压力调整至10-500Torr,温度调整至900-1300℃,NH (5)重新向反应室通入Al、Ga金属源,在低压(<100Torr)、较低V/III比(100<V/III<3000)、高温(≥900℃)条件下进行AlGaN合并层(即第二半导体材料层,下同)的生长,且使AlGaN合并层的横向/纵向生长速率比为0.04-1,从而使刻蚀坑在0.1-2μm厚度范围内逐渐合并,并在AlGaN合并层中形成狭长的空洞,其目的是利用刻蚀坑内壁晶面的镜像力诱导位错拐弯湮灭,同时抑制AlGaN合并过程中相邻台面晶粒因取向差异而产生大量的新位错; (6)在合并之后的AlGaN合并层表面继续生长一定厚度的AlGaN外延层,最终得到表面平整、高质量的AlGaN厚层薄膜材料。 本发明实施例提供的方法的关键点是在AlGaN材料外延生长过程中,通入卤素基源,利用卤素基活性原子/基团与AlGaN材料化学反应活化能低的优势,原位刻蚀AlGaN材料表面,通过控制反应室温度等条件,使位错周围区域优先刻蚀、平面其它区域几乎不刻蚀,从而形成原位刻蚀坑,然后再利用侧向生长合并的方式驱动位错拐弯湮灭,从而大幅提高AlGaN材料的晶体质量。 本发明实施例提供的方法利用卤素基活性原子/基团原位刻蚀AlGaN材料形成孔洞的技术方法,可以规避传统干法刻蚀损伤大、存在杂质污染等缺点,也摒弃了高温下氢气原位刻蚀AlGaN效率低、耗时长、刻蚀各向异性差的缺陷,有效利用卤素基活性原子与AlGaN材料化学反应活化能低的优势,以及位错核心附近悬挂键密度高、易发生化学反应的特点,原位刻蚀AlGaN材料表面,通过控制反应室温度等条件,使位错周围区域优先刻蚀、平面其它区域几乎不刻蚀,从而形成原位刻蚀坑,然后再利用侧向生长合并的方式驱动位错拐弯湮灭,从而显著降低AlGaN材料中的穿透位错密度。 本发明实施例提供的方法在AlGaN材料中“原位形成刻蚀坑、而后合并来提高材料质量”;本发明实施例提供的方法的优势在于通过卤素基活性原子/基团原位刻蚀AlGaN产生刻蚀坑,产生的刻蚀坑在合并过程中有利于促进位错拐弯湮灭,同时,刻蚀坑合并之后在AlGaN材料内部形成闭合的空洞结构,这种空洞结构受材料应力的影响可以发生微形变,从而弛豫一部分应力,有助于降低AlGaN材料中的应力,抑制AlGaN材料中的组分不均匀和应力诱导的表面粗糙。 此外,本发明实施例提供的方法不仅限于用于提高AlGaN基半导体材料的晶体质量,在基由本发明制备的高质量AlGaN材料上继续外延生长GaN等其它氮化物半导体材料晶体质量也会大幅改善。 实施例1 利用叔丁基氯(TBCl)原位刻蚀Al S1:利用金属物化学气相沉积MOCVD设备,在普通蓝宝石衬底上依次生长1μm AlN底层、500nm Al S2:停止通入TMAl、TMGa金属源,将反应室的压力增加至200Torr,温度降低至900℃,NH S3:向反应室内通入TBCl源,TBCl源的通入流量10sccm的流量,持续通入120min,以对Al S4:停止TBCl源供应,将反应室的压力降低到60Torr,温度升高到1100℃,NH S5:重新向反应室内通入TMAl、TMGa金属源,在压力为60Torr、V/III为2000、温度为1100℃条件下进行Al S6:在合并之后的Al 以扫描电子显微镜对步骤S3中经过刻蚀后的Al 实施例2 利用叔丁基氯(TBCl)原位刻蚀Al S1:利用金属物化学气相沉积MOCVD设备,在普通蓝宝石衬底上依次生长1μm AlN底层、500nm Al S2:停止通入Al、Ga金属源,将反应室的压力增加至200Torr,温度升高至1300℃,NH S3:向反应室内通入TBCl源,TBCl源的通入流量为1000sccm,持续通入0.1min,以对Al S4:停止TBCl源供应,将反应室的压力降低到60Torr,温度降低至1100℃,NH S5:重新向反应室内通入TMAl、TMGa金属源,在压力为60Torr、V/III为2000、温度为1100℃条件下进行Al S6:在合并之后的Al 实施例2中,S3经过刻蚀后的AlGaN表面,在扫描电子显微镜下可以观察到六角形的刻蚀坑,无刻蚀坑的区域仍然相对平整;S6经过合并之后的2μm Al 实施例3 在纳米图形化蓝宝石NPSS衬底制备高质量AlN的基础上,利用TBCl原位刻蚀Al S1:利用MOCVD设备,在NPSS衬底上首先外延生长4μm高质量的AlN底层,然后外延生长500nm AlN/Al S2:停止通入Al、Ga金属源,将反应室压力提高至100Torr,温度降低至850℃,NH S3:向反应室内通入TBCl源,TBCl源的通入流量为500sccm,并维持40min,以对Al S4:停止TBCl源供应,并将反应室的压力提高至150Torr,温度升高至1050℃,NH S5:重新向反应室内通入TMAl、TMGa金属源,在压力为150Torr、V/III为2500、温度为1050℃条件下进行Al S6:在合并之后的Al 以光学显微镜对所获的Al 实施例4 利用四氯化碳(CCl S1:利用金属物化学气相沉积MOCVD设备,在普通蓝宝石衬底上依次生长1μm AlN底层、500nm Al S2:停止通入TMAl、TEB金属源,将反应室的压力提高至50Torr,温度降低至800℃,NH S3:向反应室内通入CCl S4:停止CCl S5:重新向反应室内通入TMAl、TEB金属源,在压力为200Torr、V/III为2000、温度为1100℃条件下进行B S6:在合并之后的B 以光学显微镜对所获的B 实施例5 利用叔丁基氯(TBCl)原位刻蚀AlN形成孔洞而后合并,制备高质量AlN深紫外光电子材料: S1:利用MOCVD设备,在SiC衬底上首先外延生长1μm高质量的AlN底层; S2:停止通入TMAl金属源,将反应室压力降低至10Torr,温度降低至980℃,NH S3:向反应室内通入TBCl源,TBCl源的通入流量为200sccm,并维持80min,以对AlN底层表面进行原位刻蚀,形成一定密度的刻蚀坑,所述刻蚀坑的平均深度约70nm; S4:停止TBCl源供应,将反应室的压力提高至50Torr,温度升高到1090℃,NH S5:重新向反应室内通入TMAl金属源,在压力为50Torr、V/III为1500、温度为1090℃条件下进行AlN合并层的生长,且使AlN合并层的横向/纵向生长速率比达到0.04,从而使刻蚀坑在2μm厚度范围内逐渐合并,其目的是利用刻蚀内壁晶面的镜像力诱导位错拐弯湮灭,同时抑制AlN合并层合并过程中相邻台面晶粒因取向差异而产生大量的新位错; S6:在合并之后的AlN合并层表面继续生长1μm厚的AlN外延层,最终得到表面平整、高质量的AlN薄膜材料。 以光学显微镜对所获的AlN薄膜材料进行观察,光学显微镜下可以观察到AlN薄膜表面光滑,无可见的刻蚀坑,通过XRD扫描获得其(0002)面摇摆曲线半高宽为85arscec,(10-12)面半高宽为90arscec,远低于直接外延生长AlN(0002)和(10-12)面的双晶92arcsec、140arcsec,说明采用本发明提供的方法可以显著改善AlN材料的晶体质量。 对比例1 对比例1中的一种Al 经测试发现,即使刻蚀处理时间只有短短5s,Al 对比例2 对比例2中的一种Al 经试验发现,反应室内的温度低于500℃时,NH 对比例3 在通入TBCl源后,不以特定的V/III比进行铝镓氮材料的生长 对比例3中的一种Al 需要说明的是,以上实施例仅是示例性的,其仅用于解释和说明本发明的技术方案,当然,本发明实施例所采用的外延生长AlGaN材料的方法还可以是分子束外延(MBE)、氢化物气相外延(HVPE)、脉冲激光沉积(PLD)等;并不限于金属物化学气相沉积(MOCVD)。 本发明实施例进行原位刻蚀所使用的卤素基源包括但不仅限于等各种氯代物,例如还可以是各种氟代物、溴代物以及它们的任意组合。 本发明实施例用于刻蚀和生长的材料包括但不仅限于AlGaN材料,也可以为In 本发明实施例刻蚀形成的刻蚀坑,在后续AlGaN材料生长过程中并非一定要形成闭合的空洞结构,也可以被AlGaN等材料填充以致完全合并。 本发明实施例外延AlGaN所采用的衬底包括但不仅限于蓝宝石、硅、自支撑AlN单晶、自支撑GaN单晶、碳化硅、金刚石等衬底。 与现有技术相比,本发明实施例提出的一种提高AlGaN基半导体材料晶体质量的方法,通过在AlGaN等多元系III族氮化物基半导体材料生长过程中引入卤素基源,利用卤素基原子与AlGaN多元系III族氮化物基半导体材料化学反应活化能低的优势(化学分解过程),以及位错核心附近悬挂键密度高、易发生化学反应的特点,通过控制反应室温度等条件,可以实现位错周围区域优先刻蚀、平面区域几乎不刻蚀,从而对AlGaN等多元系III族氮化物基半导体材料高效率、选择性刻蚀,通过原位产生刻蚀坑,可避免传统ELOG生长中掩膜介质分解导致的杂质污染等问题。 本发明实施例提出的一种提高AlGaN基半导体材料晶体质量的方法,工艺简单,重复可控,完全适合大规模生产;本发明实施例采用的卤素基源可以完全兼容MOCVD设备,在生长完AlGaN等多元系III族氮化物基半导体材料之后,无需降温、光刻掩膜、二次外延等复杂的工艺流程,只需通过引入卤素基源,通过控制源流量、反应室压力、温度等条件即可精确控制原位刻蚀坑的尺寸,大幅简化了工艺流程,节约了成本。 本发明提出了一种提高AlGaN基半导体材料晶体质量的方法,可以克服现有技术方案的缺点,且具有工艺简单、稳定可控、无掩膜介质等突出优点,完全适合大规模生产。 应当理解,上述实施例仅为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。