PCIe总线网络接口卡的系统级验证平台

文献发布时间:2023-06-19 18:34:06

技术领域

本发明涉及网络系统技术领域,具体地,涉及一种PCIe总线网络接口卡的系统级验证平台,尤其是一种PCIe总线10/100/1000Mbps网络接口卡的系统级验证平台。

背景技术

芯片被称为“工业粮食”,是制造业的核心技术,芯片产业也是非常重要的环节。当前,集成电路芯片的结构越来越复杂,单颗芯片内集成的逻辑门电路越来越多,芯片验证技术作为集成电路设计中至关重要的一环,需要伴随着芯片复杂度的提高而不断发展。集成电路设计及验证领域,我国的发展还相对落后。现有的传统基于Verilog的验证方法,验证效率低,重用性差,验证覆盖率难以提高,而且往往需要大量的人力物力,难以保证验证的准确性。而基于 System Verilog的UVM验证方法学引入了一个通用的验证平台,具有面向对象编程、动态线程和多线程通信、随机测试、功能及代码覆盖率自动收集等特性,将极大地提高芯片验证效率。

基于PCIe的以太网接口卡通常具有以太网接口、主机侧高速PCIe接口等高速复杂总线接口,而且各个接口所采用的特性通常与接口卡直接相关,各个接口之间必须协调配合才能保证网络接口卡的正常工作。因此,即使采用UVM验证方法学搭建验证平台也存在验证复杂度高、平台搭建困难等问题。当前,还未见相关系统级验证平台的发布,这无疑会严重制约以太网接口卡芯片的快速开发验证,阻碍芯片国产化的脚步。

由此,如何利用UVM验证方法学搭建基于PCIe的以太网接口卡的系统级验证平台并完成高覆盖率、高效率、高可重用性的验证是当前亟待需要解决的问题。

发明内容

针对现有技术中的缺陷,本发明的目的是提供一种PCIe总线网络接口卡的系统级验证平台。

根据本发明提供的一种PCIe总线网络接口卡的系统级验证平台,包括:PCIe UVC组件、GMAC UVC组件、scoreboard模块、checker组件、JTAG UVC组件以及待测设计DUT;

所述PCIe UVC组件连接所述待测设计DUT,所述PCIe UVC组件与所述待测设计DUT之间进行数据帧的传输;所述PCIe UVC组件与所述scoreboard模块连接,所述 PCIeUVC组件向所述scoreboard模块发送帧记录;

所述待测设计DUT连接所述GMAC UVC组件,所述待测设计DUT与所述GMAC UVC组件之间进行数据帧的传输;所述GMAC UVC组件连接所述scoreboard模块,所述GMAC UVC组件向所述scoreboard模块发送帧记录;

所述GMAC UVC组件连接所述checker组件,所述GMAC UVC组件与所述checker 组件之间进行数据帧的传输;所述checker组件连接scoreboard模块,所述checker组件向所述scoreboard模块发送帧记录;

外部发送测试sequence向所述PCIe UVC组件发送数据帧,外部接收测试sequence向所述GMAC UVC组件发送数据帧。

优选的,所述PCIe UVC组件包括第一Driver组件、第一Monitor组件、第一Sequencer组件及第一配置模块;

所述第一Driver组件完成PCIe事务到PCIe VIP底层读写的映射;

所述第一Monitor组件监控PCIe接口的数据通信,并通过TLM通信将检测到的数据发送给所述scoreboard模块的记分板进行数据对比;

所述第一Sequencer组件连接所述第一Driver组件和外部sequence;

所述第一配置模块用于配置所述PCIe UVC组件的配置信息。

优选的,所述GMAC UVC组件包括第二Driver组件、第二Monitor组件、第二Sequencer组件及第二配置模块;

所述第二Driver组件将GMII事务转换成GMII接口信号;

所述第二Monitor组件在网络接口端收发两路上同时检测接口信号的变化,自动识别数据帧的发送,并将数据帧识别出来后汇报给所述scoreboard模块的记分板;

所述第二Sequencer组件连接所述第二Driver组件和外部sequence。

优选的,所述第一配置模块的配置参数包括如下参数:

PCIe通道数、lane的memory基地址、通道lane的中断memory基地址、收发Ring 的基本信息以及发送确认回收的超时时长。

优选的,所述第一Driver组件内置发送TX Ring模块和接收RX Ring模块,实现收发Ring环。

优选的,所述TX Ring模块实现如下任务:

Init Task:执行Ring环的初始化,使Ring中各个entry的信息通过PCIe的存储器写任务MemWr_DW task写入待测设计DUT片内寄存器;

Enable Task:通知待测设计DUT启用发送Ring的发送操作;

Recycle Task:常驻无限循环task,负责读取待测设计DUT的Head寄存器更新,依次检测Ring环的Head更新后的每个entry所对应的特定位是否有被待测设计DUT写回表示发送完成;若特定位被更新,表示发送已完成,则将对应的事务层数据包发送给scoreboard模块的的记分板;同时标记该entry为空闲;

SendFrame Task:负责将事务层表示的数据帧封装成Ring环中的数据包,其中,数据帧的数据由软件通过PCIe VIP的后门访问Backdoor MemWr_dw task模拟写入主机内存;同时更新Ring环的Tail位置,使其指向下一个可用的空闲entry;基于发送机制,平台自动识别帧数据的第一位,当第一位为0时,平台将依序将数据帧放置到发送缓存中,不移动Ring环的Tail位置;当第一位为1时,平台将数据帧依序放置到缓存中后,将移动Ring环的Tail位置,通知硬件执行发送操作。

优选的,所述RX Ring模块实现如下任务:

Init Task:执行Ring环的初始化,使Ring中各个entry的信息通过PCIe的 MemWr_DW task写入待测设计DUT片内寄存器;

Enable Task:通知待测设计DUT启用接收Ring的接收操作;

Recycle Task:常驻无限循环task,负责读取待测设计DUT的Head寄存器更新,依次检测Ring环的head更新后的每个entry所对应的特定位是否有被待测设计DUT写回表示接收完成;若特定被更新,表示接收已完成,则将此entry所对应的接收数据帧内存,通过PCIe VIP的后门访问Backdoor MemRd_dw task全部读取后,封装成事务层数据包发送给scoreboard的记分板;同时标记该entry为空闲;向后移动tail,将空闲entry 设置为可接收状态。

优选的,所述第二配置模块的配置参数包括如下参数:

网络端口数、是否启用Reduce模式、是否启用自动协商、接口支持的速率、是否支持全双工模式及接口连接状态。

优选的,包括如下两个过程:

数据帧发送:通过所述PCIe UVC组件的内置接口调用PCIe VIP向所述待测设计DUT发送数据帧,同时向scoreboard模块的记分板发送帧记录;所述待测设计DUT完成处理以后,向所述GMAC UVC组件的GMAC接口发送数据帧,所述GMAC UVC组件中对应的GMAC UVC完成数据帧的接收,并通过一组校验和所述checker组件向最终的所述scoreboard模块的记分板发送数据帧记录;所述scoreboard模块的记分板接收到两端的帧记录后,进行数据一致性比较;

数据帧接收:数据帧通过测试sequence配置所述GMAC UVC组件的GMAC发送接收数据帧,GMAC向所述待测设计DUT的GMAC接口发送接收数据帧,同时,向所述scoreboard模块的记分板发送接收数据帧记录;所述待测设计DUT完成处理后,向所述PCIe VIP发送数据帧;所述PCIe VIP接收到数据帧后,通过所述PCIe UVC组件的内部组件向所述scoreboard模块的记分板发送数据帧记录;所述scoreboard模块的记分板接收到两端的帧记录后,进行数据一致性比较。

优选的,全平台的运行环境的配置参数包括如下参数:

平台自动比对的超时限制、待测设计DUT寄存器配置的使用通路、发送端校验和检测等级、数据帧收发统计数据的汇报周期以及配置平台启用的通道。

与现有技术相比,本发明具有如下的有益效果:

1、本发明提供了一个通用的验证环境,配置参数多,设计灵活,可实现各类 PCIe总线网络接口卡待测设计DUT的快速替换,方便以较高的效率,较低的成本快速实现网络接口卡DUT硅前验证平台;

2、本发明解决了当前网络接口卡验证环境搭建复杂、可重用性差的问题,可以显著提高验证人员的工作效率,减少搭建验证环境的时间;

3、本发明自带多级校验和检测checker,可实现实时对数据帧的校验检查,避免传统验证结构人工检测效率低、准确率差的问题,很大程度地提高了验证效率。

附图说明

通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

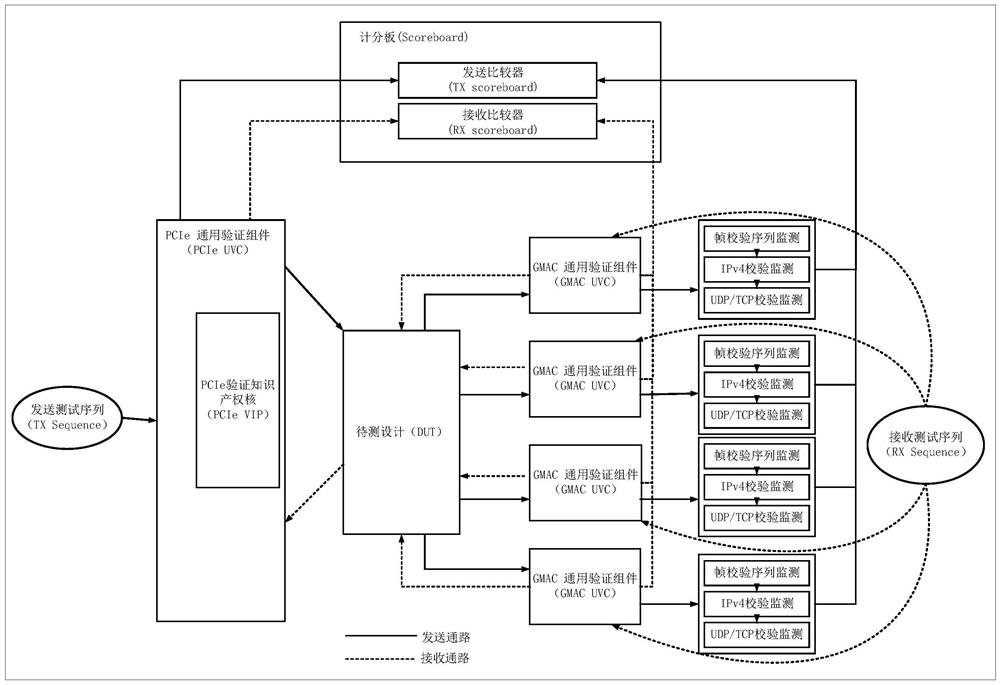

图1为本发明的PCIe总线网络接口卡的系统级验证平台的结构示意图;

图2为本发明的TX Ring的结构示意图;

图3为本发明的RX Ring的结构示意图;

图4为本发明的scoreboard模块的记分板的事务流操作示意图。

具体实施方式

下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变化和改进。这些都属于本发明的保护范围。

如图1~4所示,本实施例提供一种PCIe(peripheral component interconnectexpress,高速串行计算机扩展总线标准)总线网络接口卡的系统级验证平台,包括:PCIeUVC (Universal Verification Component,通用验证组件)组件、GMAC(Gbps MediaAccess Control,千兆介质访问控制器)UVC组件、scoreboard(计分板)模块、checker(检验器)组件、JTAG UVC组件以及待测设计DUT(Design Under Test,待测设计),PCIe UVC组件连接待测设计DUT,PCIe UVC组件与待测设计DUT之间进行数据帧的传输, PCIe UVC组件与scoreboard模块连接,PCIe UVC组件向scoreboard模块发送帧记录,待测设计DUT连接GMACUVC组件,待测设计DUT与GMAC UVC组件之间进行数据帧的传输,GMAC UVC组件连接scoreboard模块,GMAC UVC组件向scoreboard模块发送帧记录,GMAC UVC组件连接checker组件,GMAC UVC组件与checker组件之间进行数据帧的传输,checker组件连接scoreboard模块,checker组件向scoreboard 模块发送帧记录,外部发送测试sequence向PCIe UVC组件发送数据帧,外部接收测试 sequence向GMAC UVC组件发送数据帧。

包括如下两个过程:

数据帧发送:通过PCIe UVC组件的内置接口调用PCIe VIP向待测设计DUT发送数据帧,同时向scoreboard模块的记分板发送帧记录;待测设计DUT完成处理以后,向GMACUVC组件的GMAC接口发送数据帧,GMAC UVC组件中对应的GMAC UVC 完成数据帧的接收,并通过一组校验和checker组件向最终的scoreboard模块的记分板发送数据帧记录;scoreboard模块的记分板接收到两端的帧记录后,进行数据一致性比较;

数据帧接收:数据帧通过测试sequence配置GMAC UVC组件的GMAC发送接收数据帧,GMAC向待测设计DUT的GMAC接口发送接收数据帧,同时,向scoreboard 模块的记分板发送接收数据帧记录;待测设计DUT完成处理后,向PCIe VIP发送数据帧;PCIe VIP接收到数据帧后,通过PCIe UVC组件的内部组件向scoreboard模块的记分板发送数据帧记录;scoreboard模块的记分板接收到两端的帧记录后,进行数据一致性比较。

全平台的运行环境的配置参数包括如下参数:平台自动比对的超时限制、待测设计 DUT寄存器配置的使用通路、发送端校验和检测等级、数据帧收发统计数据的汇报周期以及配置平台启用的通道。

PCIe UVC组件包括第一Driver(驱动器)组件、第一Monitor(监视器)组件、第一Sequencer(序列器)组件及第一配置模块,第一Driver组件完成PCIe事务到PCIe VIP(PCIe验证知识产权核)底层读写的映射,第一Monitor组件监控PCIe接口的数据通信,并通过TLM(Transaction Level Modeling,事务级建模)通信将检测到的数据发送给scoreboard模块的记分板进行数据对比,第一Sequencer组件连接第一Driver组件和外部sequence,第一配置模块用于配置PCIe UVC组件的配置信息。

第一配置模块的配置参数包括如下参数:PCIe通道数、lane(通道)的memory(内存)基地址、通道lane的中断memory基地址、收发Ring(收发描述符环)的基本信息以及发送确认回收的超时时长。

第一Driver组件内置发送TX Ring模块和接收RX Ring(接收描述符环)模块,实现收发Ring环。TX Ring模块实现如下任务:

Init Task(初始化任务):执行Ring环的初始化,使Ring中各个entry(入口)的信息通过PCIe的存储器写任务MemWr_DW task写入待测设计DUT片内寄存器;

Enable Task(发送使能任务):通知待测设计DUT启用发送Ring的发送操作;

Recycle Task(轮询任务):常驻无限循环task,负责读取待测设计DUT的Head 寄存器更新,依次检测Ring环的Head更新后的每个entry所对应的特定位是否有被待测设计DUT写回表示发送完成;若特定位被更新,表示发送已完成,则将对应的事务层数据包发送给scoreboard模块的的记分板;同时标记该entry为空闲;

SendFrame Task(帧发送任务):负责将事务层表示的数据帧封装成Ring环中的数据包,其中,数据帧的数据由软件通过PCIe VIP的后门访问Backdoor MemWr_dw task (后门四字节内存写任务)模拟写入主机内存;同时更新Ring环的Tail(描述符尾指针) 位置,使其指向下一个可用的空闲entry;基于发送机制,平台自动识别帧数据的第一位,当第一位为0时,平台将依序将数据帧放置到发送缓存中,不移动Ring环的Tail 位置;当第一位为1时,平台将数据帧依序放置到缓存中后,将移动Ring环的Tail位置,通知硬件执行发送操作。

RX Ring模块实现如下任务:

Init Task:执行Ring环的初始化,使Ring中各个entry的信息通过PCIe的 MemWr_DW task写入待测设计DUT片内寄存器;

Enable Task:通知待测设计DUT启用接收Ring的接收操作;

Recycle Task:常驻无限循环task,负责读取待测设计DUT的Head寄存器更新,依次检测Ring环的head更新后的每个entry所对应的特定位是否有被待测设计DUT写回表示接收完成;若特定被更新,表示接收已完成,则将此entry所对应的接收数据帧内存,通过PCIe VIP的后门访问Backdoor MemRd_dw task(后门四字节内存读任务) 全部读取后,封装成事务层数据包发送给scoreboard的记分板;同时标记该entry为空闲;向后移动tail,将空闲entry设置为可接收状态。

GMAC UVC组件包括第二Driver组件、第二Monitor组件、第二Sequencer组件及第二配置模块,第二Driver组件将GMII(千兆介质无关接口)事务转换成GMII接口信号,第二Monitor组件在网络接口端收发两路上同时检测接口信号的变化,自动识别数据帧的发送,并将数据帧识别出来后汇报给scoreboard模块的记分板,第二Sequencer 组件连接第二Driver组件和外部sequence。第二配置模块的配置参数包括如下参数:网络端口数、是否启用Reduce(指代RMII及RGMII接口模式)模式、是否启用自动协商、接口支持的速率、是否支持全双工模式及接口连接状态。

本领域技术人员可以将本实施例理解为实施例1的更为具体的说明。

如图1~4所示,本实施例公开了一种基于通用验证方法学UVM的PCIe总线网络接口卡的系统级验证平台,该平台通过灵活的设计可实现不同类型PCIe总线网络接口卡待测设计DUT的快速替换,方便以较高的效率,较低的成本快速实现网络接口卡DUT 硅前验证平台。

验证平台基于UVM和PCIe VIP构建,平台设计实现了通过PCIe验证组件UVC 接收和发送以太网数据帧的功能。同时,GMAC验证组件UVC可完成网络上以太网帧的接收和发送。此外,平台自带多级校验和检测checker,可实现实时对数据帧的校验检查。配置的灵活性涉及网络接口的类型及数量、PCIe总线的接口类型等。本发明将系统介绍该验证方法的整体思路,并具体介绍该验证平台的系统结构。

本实施例提供的一种基于通用验证方法学UVM的PCIe总线网络接口卡的系统级验证平台,具体包括:

PCIe UVC,该通用验证组件UVC封装了PCIe VIP,可实现PCIe Host端RootComplex(RC,根复合体)模式的模拟,从而实现与待测设计DUT之间的PCIe数据通信。PCIeUVC组件基于UVM实现,包括Driver、Monitor、Sequencer及配置组件。Driver 完成PCIe事务到PCIe VIP底层读写的映射;同时,内置发送TX Ring和接收RX Ring,可实现收发Ring环(对应存储数据帧接收和发送描述符)的模拟。

Ring环的特性如下:TX Ring的结构如图2所示,主要包含以下任务Task:(1)InitTask:执行Ring环的初始化,包括Ring中各个entry的信息通过PCIe的存储器写任务MemWr_DW task写入待测设计DUT片内寄存器;(2)Enable Task:通知待测设计DUT 启用发送Ring的发送操作;(3)Recycle:常驻无限循环task,负责读取待测设计DUT 的Head寄存器更新,然后依次检测Ring环的Head更新后的每个entry所对应的特定位是否有被待测设计DUT写回表示发送完成;若特定位被更新,表示发送已完成,此时,将对应的事务层数据包发送给计分板;同时标记该entry为空闲;(4)SendFrame:负责将事务层表示的数据帧封装成Ring环中的数据包,其中,数据帧的数据由软件通过PCIe VIP的后门访问Backdoor MemWr_dw task模拟写入主机内存。同时更新Ring环的Tail 位置,使其指向下一个可用的空闲entry。基于发送机制的特殊性,平台会自动识别帧数据的第一位,当第一位为0时,平台将依序将数据帧放置到发送缓存中,并不移动 Ring环的Tail位置;当第一位为1时,平台将数据帧依序放置到缓存中以后,将移动 Ring环的Tail位置,通知硬件执行发送操作。

RX Ring的结构如图3所示,主要包含以下任务Task:(1)Init Task:执行Ring环的初始化,包括Ring中各个entry的信息通过PCIe的MemWr_DW task写入待测设计 DUT片内寄存器;(2)Enable Task:通知待测设计DUT启用接收Ring的接收操作;(3) Recycle:常驻无限循环task,负责读取待测设计DUT的Head寄存器更新,然后依次检测Ring环的head更新后的每个entry所对应的特定位是否有被待测设计DUT写回表示接收完成;若特定被更新,表示接收已完成,此时,将此entry所对应的接收数据帧内存,通过PCIe VIP的后门访问Backdoor MemRd_dw task全部读取后,封装成事务层数据包发送给计分板scoreboard;同时标记该entry为空闲;随后,向后移动tail,尽可能多的将空闲entry设置为可接收状态。Monitor组件负责监控PCIe接口的数据通信,并通过TLM通信将检测到的数据发送给计分板scoreboard以供数据对比;Sequencer负责连接Driver和外部sequence。配置模块主要包含PCIe UVC的配置信息,主要的可配置信息有:PCIe通道数(x1/x2/x4/x8/x16)、通道lane的memory基地址、通道lane的中断memory基地址、收发Ring的基本信息以及发送确认回收的超时时长等。

GMAC UVC,该组件可实现网络接口端对端网络设备的模拟,从而实现与待测设计DUT之间的以太网通信。GMAC UVC组件基于UVM实现,包括Driver、Monitor、 Sequencer及配置组件。Driver负责将GMII事务转换成GMII接口信号,支持 GMII/MII/RGMII/RMII四种模式。举例来说,GMII发送数据包括以下内容:(1)前导码Preamble[7]:0x55,0x55,0x55,0x55,0x55,0x55,0x55;(2)SDF(帧起始定界符:0xD5); (3)帧数据:对于Reduce模式的RMII和RGMII,需要在发送正式帧数据前发送8位链路信息码:{4’b0000,linkup[0],speed[1:0],duplex[0]}。Monitor负责在网络接口端收发两路上同时检测接口信号的变化,自动识别数据帧的发送,并将数据帧识别出来以后汇报给计分板scoreboard。Sequencer负责连接Driver和外部sequence,以启动不同的测试序列完成特定功能的验证。配置模块主要包括GMAC UVC的配置信息,主要有网络端口数、是否启用Reduce模式、是否启用自动协商、接口支持的速率 (10Mbps/100Mbps/1000Mbps)、是否支持全双工模式及接口连接状态等。

数据比对模块scoreboard及各类检测checker,平台的计分板scoreboard提供了一系列接口函数便于用户访问计分板scoreboard内的事物,从而实现按需进行事物处理的需求。通常在测试用例的main_phase中,在完成事物的发送后进行事物流的操作,检测事物流出入的情况是否正常,标准的事物流操作图4所示。检测checker主要用于数据帧的分类,以方便scoreboard进一步对比。

JTAG UVC,该通用验证组件UVC负责与待测设计DUT的JTAG接口通信,负责待测设计DUT内部所有内部寄存器的配置操作。通常,待测设计DUT内部的寄存器配置操作通过PCIe UVC内部PCIe VIP提供的PCIe接口实现,使用JTAG此类低速接口,可以作为高速PCIe接口寄存器配置的补充。

待测设计DUT,使用一款PCIe总线千兆网络接口卡作为待测设计DUT。DUT接口模块PCIe接口、接口模块GMAC接口用于验证平台和待测设计DUT的数据通信。

验证平台主体由PCIe UVC、GMAC UVC、数据比对模块scoreboard及各类检测checker、JTAG UVC及待测设计DUT构成,验证平台的整体结构如图1所示,数据帧的发送与接收过程如下:(1)、数据帧发送通过PCIe UVC的内置接口调用PCIe VIP向待测设计DUT发送数据帧,同时向记分板scoreboard发送帧记录;待测设计DUT完成处理以后,向GMAC接口发送数据帧,对应的GMAC UVC会完成数据帧的接收,并通过一组校验和checker向最终的记分板发送数据帧记录。记分板接收到两端的帧记录以后,会进行数据一致性比较。确保发送通路的数据正确。(2)、数据帧接收:数据帧通过测试sequence配置GMAC发送接收数据帧,GMAC向待测设计DUT的GMAC接口发送接收数据帧,同时,向记分板发送接收数据帧记录。待测设计DUT完成处理以后,向PCIe VIP发送数据帧。PCIe VIP接收到数据帧以后,通过PCIeUVC的内部组件向计分板scoreboard发送数据帧记录。记分板scoreboard接收到两端的帧记录以后,会进行数据一致性比较。确保发送通路的数据正确。全平台的运行环境也包括一些可配置参数,主要包括:平台自动比对的超时限制、待测设计DUT寄存器配置的使用通路(PCIe/JTAG)、发送端校验和检测等级、数据帧收发统计数据的汇报周期、配置平台启用的通道等。

本发明提供了一个通用的验证环境,配置参数多,设计灵活,可实现各类PCIe 总线网络接口卡待测设计DUT的快速替换,方便以较高的效率,较低的成本快速实现网络接口卡DUT硅前验证平台;

以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本申请的实施例和实施例中的特征可以任意相互组合。

- 系统级仿真加速器验证环境用PCIE设备板卡扩展连接装置

- 一种系统级芯片的验证平台及验证方法