翻译控制方法、二进制翻译方法、指令执行方法及装置

文献发布时间:2024-01-17 01:18:42

技术领域

本发明涉及计算机技术领域,尤其涉及一种翻译控制方法、二进制翻译方法、指令执行方法及装置。

背景技术

动态二进制翻译技术通常用于在宿主机上执行不同指令集的客户程序,其基本工作过程是将一段客户指令序列翻译成语义等价的宿主指令序列并执行。

在翻译过程中,客户程序会被划分为一个或多个基本块。当一个基本块被执行结束之后,再翻译下一个基本块并执行。如果要在宿主机中执行客户程序,宿主机需要在翻译态和执行态之间来回切换,严重影响二进制翻译性能和指令执行效率。

发明内容

本发明实施例提供一种翻译控制方法、二进制翻译方法、指令执行方法及装置,可以解决在宿主机中执行客户程序时,宿主机需要在翻译态和执行态之间来回切换,影响二进制翻译性能和指令执行效率的问题。

第一方面,本发明实施例公开了一种翻译控制方法,应用于翻译控制器,所述翻译控制器与宿主机、二进制翻译器均连接在总线上;所述方法包括:

对所述总线上传输的数据进行实时监测;

在监测到所述宿主机发送的取指请求的情况下,记录所述取指请求对应的取指目标地址;

在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,向所述二进制翻译器发送第一指示;所述第一指示用于指示所述取指目标地址对应的基本块需要进行二进制翻译;所述基本块为所述二进制翻译器的基本处理单位;

从所述取指目标地址处重新取指,得到翻译后的目标指令;

将所述目标指令发送至所述宿主机。

第二方面,本发明实施例公开了一种二进制翻译方法,应用于二进制翻译器,所述二进制翻译器与翻译控制器、宿主机均连接在总线上;所述方法包括:

接收所述翻译控制器发送的第一指示;所述第一指示用于指示取指目标地址对应的基本块需要进行二进制翻译;所述取指目标地址为所述宿主机发送的取指请求中携带的地址;所述基本块为所述二进制翻译器的基本处理单位;

对所述取指目标地址对应的基本块进行二进制翻译,得到翻译后的目标指令;所述目标指令属于所述宿主机支持的指令集;

利用所述目标指令覆盖所述取指目标地址对应的基本块。

第三方面,本发明实施例公开了一种指令执行方法,所述宿主机与翻译控制器、二进制翻译器、内存均连接在总线上;所述方法包括:

向所述内存发送取指请求,所述取指请求中携带取指目标地址;

接收所述内存返回的取指结果并执行;或者,

接收所述翻译控制器发送的目标指令并执行;

其中,所述目标指令为所述取指目标地址对应的基本块被翻译后得到的指令;所述取指结果与所述目标指令均属于所述宿主机支持的指令集。

第四方面,本发明实施例公开了一种翻译控制装置,应用于翻译控制器,所述翻译控制器与宿主机、二进制翻译器均连接在总线上;所述装置包括:

监测模块,用于对所述总线上传输的数据进行实时监测;

记录模块,用于在监测到所述宿主机发送的取指请求的情况下,记录所述取指请求对应的取指目标地址;

第一指示发送模块,用于在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,向所述二进制翻译器发送第一指示;所述第一指示用于指示所述取指目标地址对应的基本块需要进行二进制翻译;所述基本块为所述二进制翻译器的基本处理单位;

取指模块,用于从所述取指目标地址处重新取指,得到翻译后的目标指令;

指令发送模块,用于将所述目标指令发送至所述宿主机。

第五方面,本发明实施例公开了一种二进制翻译装置,应用于二进制翻译器,所述二进制翻译器与翻译控制器、宿主机均连接在总线上;所述装置包括:

第一指示接收模块,用于接收所述翻译控制器发送的第一指示;所述第一指示用于指示取指目标地址对应的基本块需要进行二进制翻译;所述取指目标地址为所述宿主机发送的取指请求中携带的地址;所述基本块为所述二进制翻译器的基本处理单位;

翻译模块,用于对所述取指目标地址对应的基本块进行二进制翻译,得到翻译后的目标指令;所述目标指令属于所述宿主机支持的指令集;

覆盖模块,用于利用所述目标指令覆盖所述取指目标地址对应的基本块。

第六方面,本发明实施例公开了一种指令执行装置,应用于宿主机,所述宿主机与翻译控制器、二进制翻译器、内存均连接在总线上;所述装置包括:

取指请求发送模块,用于向所述内存发送取指请求,所述取指请求中携带取指目标地址;

第一接收模块,用于接收所述内存返回的取指结果并执行;或者,

第二接收模块,用于接收所述翻译控制器发送的目标指令并执行;

其中,所述目标指令为所述取指目标地址对应的基本块被翻译后得到的指令;所述取指结果与所述目标指令均属于所述宿主机支持的指令集。

第七方面,本发明实施例还公开了一种电子设备,所述电子设备包括处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行前述第一方面的翻译控制方法,或者,执行前述第二方面的二进制翻译方法,或者,执行前述第三方面的指令执行方法。

本发明实施例还公开了一种可读存储介质,当所述可读存储介质中的指令由电子设备的处理器执行时,使得电子设备能够执行前述第一方面的翻译控制方法,或者,执行前述第二方面的二进制翻译方法,或者,执行前述第三方面的指令执行方法。

本发明实施例包括以下优点:

在本发明实施例中,宿主机无需感知动态二进制翻译过程,也不需要在执行指令和翻译客户程序之间来回切换,从而节省了上下文切换开销,提升了宿主机的指令执行效率。并且,本发明实施例将指令执行和二进制翻译独立开来,二进制翻译过程由二进制翻译器执行,二进制翻译器仅需在接收到第一指示的情况下对取指结果进行二进制翻译,无需关注指令执行过程,从而提升了二进制翻译性能。

附图说明

为了更清楚地说明本发明实施例的技术方案,下面将对本发明实施例的描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

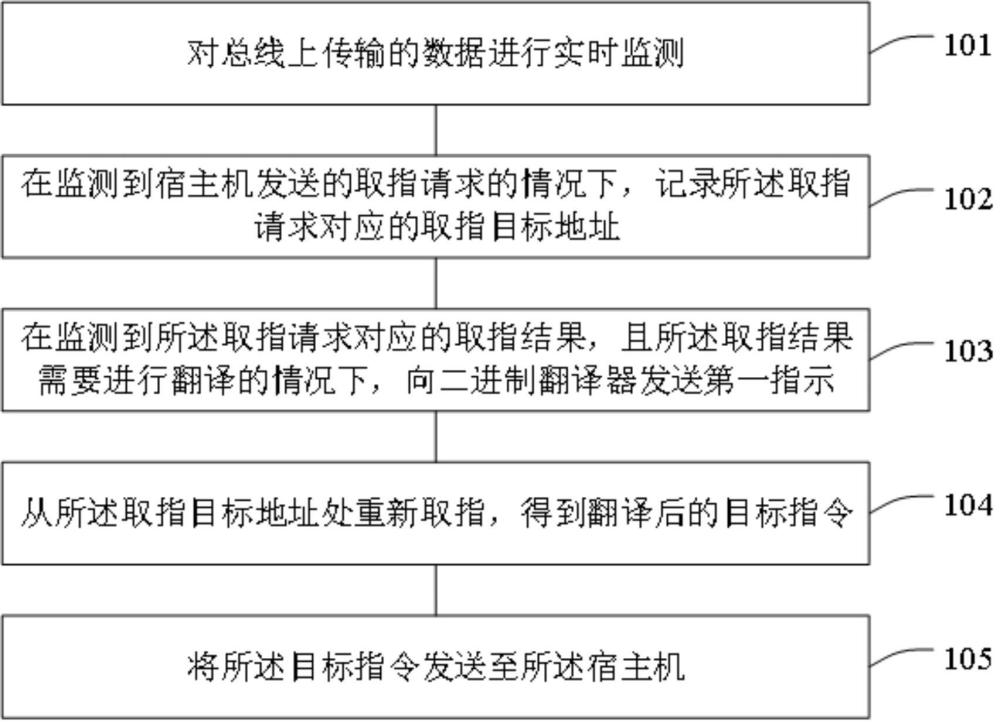

图1是本发明的一种翻译控制方法实施例的步骤流程图;

图2是本发明的一种二进制翻译系统的架构示意图;

图3是本发明的一种二进制翻译方法实施例的步骤流程图;

图4是本发明的一种指令执行方法实施例的步骤流程图;

图5是本发明的一种翻译控制装置的结构框图;

图6是本发明的一种二进制翻译装置的结构框图;

图7是本发明的一种指令执行装置的结构框图;

图8是本发明示例提供的一种电子设备的结构框图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明的说明书和权利要求书中的术语“第一”、“第二”等是用于区别类似的对象,而不用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便本发明的实施例能够以除了在这里图示或描述的那些以外的顺序实施,且“第一”、“第二”等所区分的对象通常为一类,并不限定对象的个数,例如第一对象可以是一个,也可以是多个。此外,说明书以及权利要求中的术语“和/或”用于描述关联对象的关联关系,表示可以存在三种关系,例如,A和/或B,可以表示:单独存在A,同时存在A和B,单独存在B这三种情况。字符“/”一般表示前后关联对象是一种“或”的关系。本发明实施例中术语“多个”是指两个或两个以上,其它量词与之类似。

方法实施例

动态二进制翻译技术通常用于在宿主机上执行不同指令集的客户程序,其基本工作过程是将一段客户指令序列翻译成语义等价的宿主指令序列并执行。在翻译过程中,客户程序被划分为一个或多个基本块,翻译程序以基本块为单位进行二进制翻译处理。对于当前将要执行的基本块,执行分发器会首先检查当前的基本块是否已经被翻译过。若当前的基本块没有被翻译过,执行分发器将会调用翻译程序,将该基本块中的客户程序片段翻译成行为等价的宿主代码;若该基本块已经被翻译过,执行分发器将会直接取出之前的翻译结果。接下来执行分发器将会跳转到翻译出的宿主代码,把控制权交给宿主代码直接执行。执行完这一基本块之后,将会返回到执行分发器,查看下一个基本块的翻译情况。动态二进制翻译技术的工作流程将会重复进行上述过程。

然而,在一些情况下,上述工作过程需要在宿主代码和翻译程序之间频繁跳转,如客户程序位于初始化阶段,客户程序一次只执行少量代码,或客户程序执行大量代码,但其热点不明显。此时,宿主代码和翻译过程之间的频繁切换将会给动态二进制翻译过程带来明显的性能下降。

为了解决上述问题,减少宿主机在执行宿主代码和翻译客户程序之间的频繁切换,本发明实施例提供了一种翻译控制方法、二进制翻译方法和指令执行方法。

第一方面,本发明实施例提供了一种翻译控制方法。参照图1,示出了本发明的一种翻译控制方法实施例的步骤流程图,所述方法具体可以包括如下步骤:

步骤101、对总线上传输的数据进行实时监测。

步骤102、在监测到宿主机发送的取指请求的情况下,记录所述取指请求对应的取指目标地址。

步骤103、在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,向二进制翻译器发送第一指示。

步骤104、从所述取指目标地址处重新取指,得到翻译后的目标指令;

步骤105、将所述目标指令发送至所述宿主机。

其中,所述第一指示用于指示所述取指目标地址对应的基本块需要进行二进制翻译;所述基本块为所述二进制翻译器的基本处理单位。

本发明实施例提供的翻译控制方法,可以应用于翻译控制器,该翻译控制器与宿主机、二进制翻译器均连接在总线上。其中,翻译控制器用于监控总线上传输的取指请求、取指结果等数据,判断取指结果是否需要进行翻译,并在取指结果需要进行翻译的情况下,向宿主机发送翻译后的目标指令。宿主机用于发送取指请求进行取指,并执行取指结果或目标指令。二进制翻译器用于对需要翻译的取指结果进行二进制翻译处理。需要说明的是,在本发明实施例中,宿主机执行的指令(包括取指结果或目标指令)属于宿主机支持的指令集中的指令。

参照图2,示出了本发明实施例提供的一种二进制翻译系统的架构示意图。如图2所示,翻译控制器、宿主机、内存、二进制翻译器均连接在总线上。宿主机发送的取指请求通过总线传输至内存。

翻译控制器可以对总线上传输的数据进行实时监测。当翻译控制器监测到取指请求的情况下,记录取指请求对应的取指目标地址,并等待该取指请求对应的取指结果。在监测到取指结果的情况下,进一步判断该取指结果是否需要进行翻译,如果该取指结果需要进行翻译,就向二进制翻译器发送第一指示,请求二进制翻译器对取指目标地址对应的基本块进行二进制翻译处理。可以理解的是,本发明实施例中的第一指示可以是中断信号,也可以是其他信令形式,例如第一指示为“1”或“0”,或者,第一指示也可以为低电平信号或者高电平信号,等等。

二进制翻译器在接收到第一指示之后,对取指目标地址对应的基本块进行翻译处理,得到目标指令,并利用目标指令覆盖取指目标地址处原本的基本块。

经过上述处理,取指目标地址处记录的指令为适配于宿主机的目标指令。

翻译控制器从取指目标地址处重新取指,就可以得到翻译后的目标指令。翻译控制器将获取到的目标指令发送至宿主机,以供宿主机执行。

在另一种可能的应用场景中,翻译控制器在监测到取指结果的情况下,如果确定该取指结果不需要进行翻译,就可以不对该取指结果做任何处理,也即不干涉该取指结果在总线上的正常传输。宿主机可以接收到内存返回的取指结果。

在本发明实施例中,无论内存提供的取指结果是否需要进行翻译,宿主机都无需感知动态二进制翻译过程,也不需要在执行指令和翻译客户程序之间来回切换,从而节省了上下文切换开销,提供了宿主机的指令执行效率。并且,本发明实施例将指令执行和二进制翻译独立开来,二进制翻译过程由二进制翻译器执行,二进制翻译器仅需在接收到第一指示的情况下对取指结果进行二进制翻译,无需关注指令执行过程,从而提升了二进制翻译性能。

在本发明的一种可选实施例中,在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,向所述二进制翻译器发送第一指示之前,所述方法还包括:

在满足预设条件的情况下,确定所述取指结果需要进行翻译。

其中,所述预设条件包括:所述取指结果中包括预先指定的非法指令,且所述取指目标地址为代码缓存中的地址;所述代码缓存用于存储预先指定的非法指令。

在本发明实施例中,可以在内存中指定一个存储区域作为代码缓存,用于存储预先指定的非法指令,非法指令用于指示相应基本块未翻译。

翻译控制器在监测到取指结果之后,如果该取指结果中包括预先指定的非法指令,且取指请求中携带的取指目标地址属于代码缓存中的地址,就可以确定该取指结果需要进行二进制翻译。此时翻译控制器可以向二进制翻译器发送第一指示,以触发二进制翻译器对取指目标地址对应的基本块进行翻译处理。

如果该取指结果中不包括非法指令,和/或,取指请求中携带的取指目标地址不属于代码缓存中的地址,就可以确定该取指结果不需要进行二进制翻译。此时翻译控制器就无需对该取指结果的传输过程进行干涉。可以理解的是,如果取指结果中包括非法指令,但取指请求中携带的取指目标地址不是代码缓存中的地址,此时翻译控制器不对该取指结果的传输过程进行干涉,宿主机收到非法指令后正常进行后续处理。

可选地,所述代码缓存为被所述宿主机初始化为用于存储预先指定的非法指令的缓存,且所述代码缓存的起始地址和结束地址被写入所述翻译控制器。

在本发明实施例中,可以由宿主机对代码缓存进行初始化处理,也即在内存中指定一个存储区域作为代码缓存,将非法指令存储至代码缓存中,并将代码缓存的起始地址和结束地址写入翻译控制器。翻译控制器在判断取指结果是否需要翻译时,就可以直接从本地读取代码缓存的起始地址和结束地址,以判断取指目标地址是否为代码缓存中的地址,无需再向宿主机请求代码缓存的起始地址和结束地址。

进一步地,在包含虚拟内存的宿主机中,可以由宿主机的操作系统在系统启动时预留部分物理内存用作代码缓存。

在本发明的一种可选实施例中,步骤103所述在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,向所述二进制翻译器发送第一指示,包括:

步骤S11、在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,拦截所述取指结果并丢弃;

步骤S12、向所述二进制翻译器发送第一指示。

翻译控制器在监测到取指请求对应的取指结果,且该取指结果需要进行翻译的情况下,可以拦截该取指结果并丢弃,使其不再被发送至宿主机。同时翻译控制器向二进制翻译器发送第一指示,请求二进制翻译器对该取指结果进行翻译。然后,翻译控制器在获取到翻译后的目标指令的情况下,通过总线向宿主机发送目标指令。

在本发明实施例中,如果取指结果不属于宿主机支持的指令集中的指令,取指结果就不会被发送至宿主机。换言之,宿主机不会接收到无法直接执行的指令,能够一直保持在宿主代码的执行状态中,无需检查指令是否被翻译过,也无需感知动态二进制翻译过程,从而提升了宿主机执行指令的性能。

在本发明的一种可选实施例中,步骤104所述从所述取指目标地址处重新取指,得到翻译后的目标指令,包括:

在接收到第二指示的情况下,从所述取指目标地址处重新取指,得到翻译后的目标指令。

其中,所述第二指示用于指示所述取指目标地址对应的基本块已被翻译为适配于所述宿主机的目标指令。

二进制翻译器在完成对取指目标地址对应的基本块的二进制翻译工作之后,可以向翻译控制器发送第二指示,以告知翻译控制器翻译工作已完成。翻译控制器在接收到第二指示的情况下,从取指目标地址处重新取指,就可以得到翻译后的目标指令。

可以理解的是,第二指示可以是中断信号,也可以是其他信令形式,例如第二指示为“1”或“0”,或者,第二指示也可以为低电平信号或者高电平信号,等等。示例性地,二进制翻译器在完成对取指目标地址对应的基本块的二进制翻译工作后,向翻译控制器中的预设寄存器中写入预设值,如“0”、“1”等,作为第二指示,以告知翻译控制器取指目标地址对应的基本块已被翻译为适配于宿主机的目标指令。

综上,本发明实施例提供了一种翻译控制方法,通过翻译控制器对总线上传输的数据进行实时监测,并在内存向宿主机返回的取指结果需要进行翻译的情况下,向二进制翻译控制器发送第一指示,触发二进制翻译控制器对取指目标地址对应的基本块进行翻译;翻译控制器将翻译后的目标指令传输给宿主机,以供宿主机直接执行。在本发明实施例中,无论内存提供的取指结果是否需要进行翻译,宿主机都无需感知动态二进制翻译过程,也不需要在执行指令和翻译客户程序之间来回切换,从而节省了上下文切换开销,提升了宿主机的指令执行效率。并且,本发明实施例将指令执行和二进制翻译独立开来,二进制翻译过程由二进制翻译器执行,二进制翻译器仅需在接收到第一指示的情况下对取指结果进行二进制翻译,无需关注指令执行过程,从而提升了二进制翻译性能。

第二方面,本发明实施例提供了一种二进制翻译方法。参照图3,示出了本发明的一种二进制翻译方法实施例的步骤流程图,所述方法具体可以包括如下步骤:

步骤301、接收翻译控制器发送的第一指示;所述第一指示用于指示取指目标地址对应的基本块需要进行二进制翻译;

步骤302、对所述取指目标地址对应的基本块进行二进制翻译,得到翻译后的目标指令;

步骤303、利用所述目标指令覆盖所述取指目标地址对应的基本块。

其中,所述取指目标地址为所述宿主机发送的取指请求中携带的地址;所述基本块为所述二进制翻译器的基本处理单位。所述目标指令属于所述宿主机支持的指令集。

本发明实施例提供的二进制翻译方法,可以应用于二进制翻译器,该二进制翻译器与翻译控制器、宿主机均连接在总线上。其中,翻译控制器用于监控总线上传输的取指请求、取指结果等数据,判断取指结果是否需要进行翻译,并在取指结果需要进行翻译的情况下,向宿主机发送翻译后的目标指令。宿主机用于发送取指请求进行取指,并执行取指结果或目标指令。二进制翻译器用于对需要翻译的取指结果进行二进制翻译处理。需要说明的是,在本发明实施例中,宿主机执行的指令(包括取指结果或目标指令)属于宿主机支持的指令集中的指令。

具体地,如图2所示,翻译控制器、宿主机、内存、二进制翻译器均连接在总线上。宿主机发送的取指请求通过总线传输至内存。

翻译控制器可以对总线上传输的数据进行实时监测。当翻译控制器监测到取指请求的情况下,记录取指请求对应的取指目标地址,并等待该取指请求对应的取指结果。在监测到取指结果的情况下,进一步判断该取指结果是否需要进行翻译,如果该取指结果需要进行翻译,就向二进制翻译器发送第一指示,请求二进制翻译器对取指目标地址对应的基本块进行二进制翻译处理。

二进制翻译器在接收到第一指示之后,对取指目标地址对应的基本块进行翻译处理,得到目标指令,并利用目标指令覆盖取指目标地址处原本的基本块。

经过上述处理,取指目标地址处记录的指令为适配于宿主机的目标指令。

翻译控制器从取指目标地址处重新取指,就可以得到翻译后的目标指令。翻译控制器将获取到的目标指令发送至宿主机,以供宿主机执行。

在本发明实施例中,宿主机无需感知动态二进制翻译过程,也不需要在执行指令和翻译客户程序之间来回切换,从而节省了上下文切换开销,提供了宿主机的指令执行效率。并且,本发明实施例将指令执行和二进制翻译独立开来,二进制翻译过程由二进制翻译器执行,二进制翻译器仅需在接收到第一指示的情况下对取指结果进行二进制翻译,无需关注指令执行过程,从而提升了二进制翻译性能。

可选地,所述方法还包括:向所述翻译控制器发送第二指示。其中,所述第二指示用于指示所述取指目标地址对应的基本块已被翻译为适配于所述宿主机的目标指令。

二进制翻译器在完成对取指目标地址对应的基本块的二进制翻译工作之后,可以向翻译控制器发送第二指示,以告知翻译控制器翻译工作已完成。翻译控制器在接收到第二指示的情况下,从取指目标地址处重新取指,就可以得到翻译后的目标指令。

可以理解的是,第二指示可以是中断信号,也可以是其他信令形式,例如第二指示为“1”或“0”,或者,第二指示也可以为低电平信号或者高电平信号,等等。示例性地,二进制翻译器在完成对取指目标地址对应的基本块的二进制翻译工作后,向翻译控制器中的预设寄存器中写入预设值,如“0”、“1”等,作为第二指示,以告知翻译控制器取指目标地址对应的基本块已被翻译为适配于宿主机的目标指令。

综上,本发明实施例提供了一种翻译控制方法,将指令执行和二进制翻译独立开来,二进制翻译过程由二进制翻译器执行,二进制翻译器仅需在接收到第一指示的情况下对取指结果进行二进制翻译,无需关注指令执行过程,从而提升了二进制翻译性能。

第三方面,本发明实施例提供了一种指令执行方法。参照图4,示出了本发明的一种指令执行方法实施例的步骤流程图,所述方法具体可以包括如下步骤:

步骤401、向所述内存发送取指请求,所述取指请求中携带取指目标地址;

步骤402、接收所述内存返回的取指结果并执行;或者,

步骤403、接收所述翻译控制器发送的目标指令并执行。

其中,所述取指结果与所述目标指令均属于所述宿主机支持的指令集,所述目标指令为所述取指目标地址对应的基本块被翻译后得到的指令。

本发明实施例提供的指令执行方法,可以应用于宿主机,该宿主机与翻译控制器、二进制翻译器均连接在总线上。其中,翻译控制器用于监控总线上传输的取指请求、取指结果等数据,判断取指结果是否需要进行翻译,并在取指结果需要进行翻译的情况下,向宿主机发送翻译后的目标指令。宿主机用于发送取指请求进行取指,并执行取指结果或目标指令。二进制翻译器用于对需要翻译的取指结果进行二进制翻译处理。需要说明的是,在本发明实施例中,宿主机执行的指令(包括取指结果或目标指令)属于宿主机支持的指令集中的指令。

具体地,如图2所示,翻译控制器、宿主机、内存、二进制翻译器均连接在总线上。宿主机发送的取指请求通过总线传输至内存。

翻译控制器可以对总线上传输的数据进行实时监测。当翻译控制器监测到取指请求的情况下,记录取指请求对应的取指目标地址,并等待该取指请求对应的取指结果。在监测到取指结果的情况下,进一步判断该取指结果是否需要进行翻译,如果该取指结果需要进行翻译,就向二进制翻译器发送第一指示,请求二进制翻译器对取指目标地址对应的基本块进行二进制翻译处理。

二进制翻译器在接收到第一指示之后,对取指目标地址对应的基本块进行翻译处理,得到目标指令,并利用目标指令覆盖取指目标地址处原本的基本块。

经过上述处理,取指目标地址处记录的指令为适配于宿主机的目标指令。

翻译控制器从取指目标地址处重新取指,就可以得到翻译后的目标指令。翻译控制器将获取到的目标指令发送至宿主机。宿主机接收目标指令并执行。

在另一种可能的应用场景中,翻译控制器在监测到取指结果的情况下,如果确定该取指结果不需要进行翻译,就可以不对该取指结果做任何处理,也即不干涉该取指结果在总线上的正常传输。宿主机在向内存发送取指请求之后,可以接收到内存返回的取指结果。

进一步地,在本发明实施例中,翻译控制器在监测到取指请求对应的取指结果,且该取指结果需要进行翻译的情况下,可以拦截该取指结果并丢弃,使其不再被发送至宿主机。宿主机不会接收到无法直接执行的指令,能够一直保持在宿主代码的执行状态中,无需检查指令是否被翻译过,也无需感知动态二进制翻译过程,从而提升了宿主机执行指令的性能。

综上,本发明实施例提供了一种指令执行方法,宿主机无需感知动态二进制翻译过程,也不需要在执行指令和翻译客户程序之间来回切换,可以一直保持在宿主代码的执行状态中,对接收到的取指结果或目标指令直接执行,从而节省了上下文切换开销,提升了宿主机的指令执行效率。

需要说明的是,对于方法实施例,为了简单描述,故将其都表述为一系列的动作组合,但是本领域技术人员应该知悉,本发明实施例并不受所描述的动作顺序的限制,因为依据本发明实施例,某些步骤可以采用其他顺序或者同时进行。其次,本领域技术人员也应该知悉,说明书中所描述的实施例均属于优选实施例,所涉及的动作并不一定是本发明实施例所必须的。

装置实施例

第四方面,本发明实施例提供了一种翻译控制装置。参照图5,示出了本发明的一种翻译控制装置的结构框图,所述翻译控制装置应用于翻译控制器,所述翻译控制器与宿主机、二进制翻译器均连接在总线上;所述装置具体可以包括:

监测模块501,用于对所述总线上传输的数据进行实时监测;

记录模块502,用于在监测到所述宿主机发送的取指请求的情况下,记录所述取指请求对应的取指目标地址;

第一指示发送模块503,用于在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,向所述二进制翻译器发送第一指示;所述第一指示用于指示所述取指目标地址对应的基本块需要进行二进制翻译;所述基本块为所述二进制翻译器的基本处理单位;

取指模块504,用于从所述取指目标地址处重新取指,得到翻译后的目标指令;

指令发送模块505,用于将所述目标指令发送至所述宿主机。

可选地,所述装置还包括:

确定模块,用于在满足预设条件的情况下,确定所述取指结果需要进行翻译;

其中,所述预设条件包括:所述取指结果中包括预先指定的非法指令,且所述取指目标地址为代码缓存中的地址;所述代码缓存用于存储预先指定的非法指令。

可选地,所述代码缓存为被所述宿主机初始化为用于存储预先指定的非法指令的缓存,且所述代码缓存的起始地址和结束地址被写入所述翻译控制器。

可选地,所述在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,向所述二进制翻译器发送第一指示,包括:

在监测到所述取指请求对应的取指结果,且所述取指结果需要进行翻译的情况下,拦截所述取指结果并丢弃;

向所述二进制翻译器发送第一指示。

可选地,所述从所述取指目标地址处重新取指,得到翻译后的目标指令,包括:

在接收到第二指示的情况下,从所述取指目标地址处重新取指,得到翻译后的目标指令;

其中,所述第二指示用于指示所述取指目标地址对应的基本块已被翻译为适配于所述宿主机的目标指令。

第五方面,本发明实施例提供了一种二进制翻译装置。参照图6,示出了本发明的一种二进制翻译装置的结构框图,所述二进制翻译装置应用于二进制翻译器,所述二进制翻译器与翻译控制器、宿主机均连接在总线上;所述装置具体可以包括:

第一指示接收模块601,用于接收所述翻译控制器发送的第一指示;所述第一指示用于指示取指目标地址对应的基本块需要进行二进制翻译;所述取指目标地址为所述宿主机发送的取指请求中携带的地址;所述基本块为所述二进制翻译器的基本处理单位;

翻译模块602,用于对所述取指目标地址对应的基本块进行二进制翻译,得到翻译后的目标指令;所述目标指令属于所述宿主机支持的指令集;

覆盖模块603,用于利用所述目标指令覆盖所述取指目标地址对应的基本块。

可选地,所述装置还包括:

第二指示发送模块,用于向所述翻译控制器发送第二指示;

其中,所述第二指示用于指示所述取指目标地址对应的基本块已被翻译为适配于所述宿主机的目标指令。

第六方面,本发明实施例提供了一种指令执行装置。参照图7,示出了本发明的一种指令执行装置的结构框图,所述指令执行装置应用于宿主机,所述宿主机与翻译控制器、二进制翻译器、内存均连接在总线上;所述装置具体可以包括:

取指请求发送模块701,用于向所述内存发送取指请求,所述取指请求中携带取指目标地址;

第一接收模块702,用于接收所述内存返回的取指结果并执行;或者,

第二接收模块703,用于接收所述翻译控制器发送的目标指令并执行;

其中,所述目标指令为所述取指目标地址对应的基本块被翻译后得到的指令;所述取指结果与所述目标指令均属于所述宿主机支持的指令集。

对于装置实施例而言,由于其与方法实施例基本相似,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

关于上述实施例中的处理器,其中各个模块执行操作的具体方式已经在有关该方法的实施例中进行了详细描述,此处将不做详细阐述说明。

参照图8,是本发明实施例提供的一种电子设备的结构框图。如图8所示,所述电子设备包括:处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行前述第一方面的翻译控制方法,或者,执行前述第二方面的二进制翻译方法,或者,执行前述第三方面的指令执行方法。

所述处理器可以是CPU(Central Processing Unit,中央处理器),通用处理器、DSP(Digital Signal Processor,数字信号处理器),ASIC(Application SpecificIntegrated Circuit,专用集成电路),FPGA(Field Programmble Gate Array,现场可编程门阵列)或者其他可编辑器件、晶体管逻辑器件、硬件部件或者其任意组合。所述处理器也可以是实现计算功能的组合,例如包含一个或多个微处理器组合,DSP和微处理器的组合等。

所述通信总线可包括一通路,在存储器和通信接口之间传送信息。通信总线可以是PCI(Peripheral Component Interconnect,外设部件互连标准)总线或EISA(ExtendedIndustry Standard Architecture,扩展工业标准结构)总线等。所述通信总线可以分为地址总线、数据总线、控制总线等。为便于表示,图8中仅用一条线表示,但并不表示仅有一根总线或一种类型的总线。

所述存储器可以是ROM(Read Only内存,只读内存)或可存储静态信息和指令的其他类型的静态存储设备、RAM(Random Access,随机存取存储器)或者可存储信息和指令的其他类型的动态存储设备,也可以是EEPROM(Electrically Erasable Programmable ReadOnly,电可擦可编程只读内存)、CD-ROM(Compact Disa Read Only,只读光盘)、磁带、软盘和光数据存储设备等。

本发明实施例还提供了一种非临时性计算机可读存储介质,当所述存储介质中的指令由电子设备(服务器或者终端)的处理器执行时,使得处理器能够执行第一方面的翻译控制方法,或者,执行前述第二方面的二进制翻译方法,或者,执行前述第三方面的指令执行方法。

本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

本领域内的技术人员应明白,本发明实施例的实施例可提供为方法、装置、或计算机程序产品。因此,本发明实施例可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本发明实施例可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、CD-ROM、光学存储器等)上实施的计算机程序产品的形式。

本发明实施例是参照根据本发明实施例的方法、终端设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理终端设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理终端设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理终端设备以预测方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

这些计算机程序指令也可装载到计算机或其他可编程数据处理终端设备上,使得在计算机或其他可编程终端设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程终端设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

尽管已描述了本发明实施例的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例做出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明实施例范围的所有变更和修改。

最后,还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者终端设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者终端设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者终端设备中还存在另外的相同要素。

以上对本发明所提供的一种翻译控制方法、二进制翻译方法、指令执行方法及装置,进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

- 指令执行方法、指令执行装置及存储介质

- 一种翻译模型的训练方法、翻译方法和装置

- 二进制指令翻译执行方法及装置

- 在动态二进制翻译系统中处理间接转移指令的方法和装置