信息存储

-

存储器故障处理方法和装置

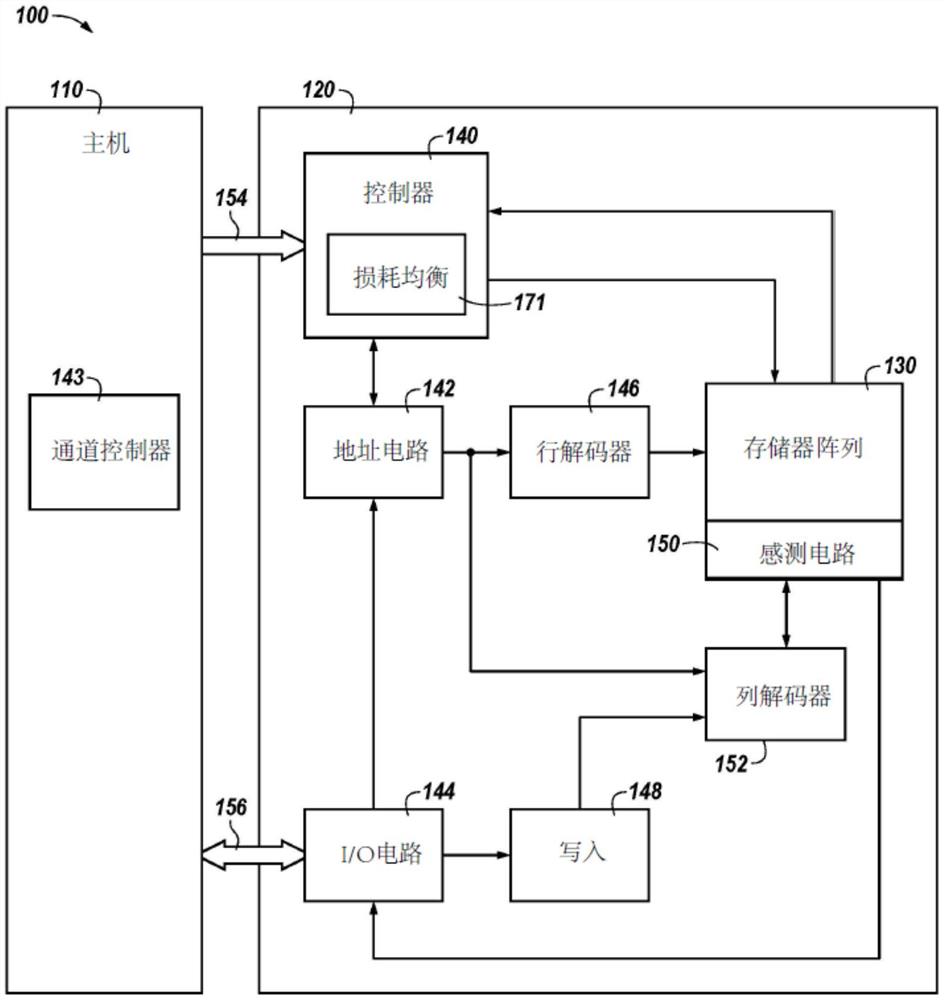

本公开涉及集成电路技术领域,具体涉及一种存储器故障处理方法和存储器故障处理装置。本公开中的存储器故障处理方法包括:确定所述存储器中出现存储故障的故障类型,所述故障类型包括软故障和硬故障;当所述故障类型为软故障时,获取用于调整所述存储器的工作参数的修复编码;将所述修复编码写入所述存储器的软故障修复控制器,以由所述软故障修复控制器生成软故障修复指令;根据所述软故障修复指令调整所述存储器的工作参数。本公开采用向软故障修复控制器写入修复编码的方式对存储器的工作参数做出调整,可以适应性地修复存储故障,降低修复成本,提高修复效率。

2023-08-21 -

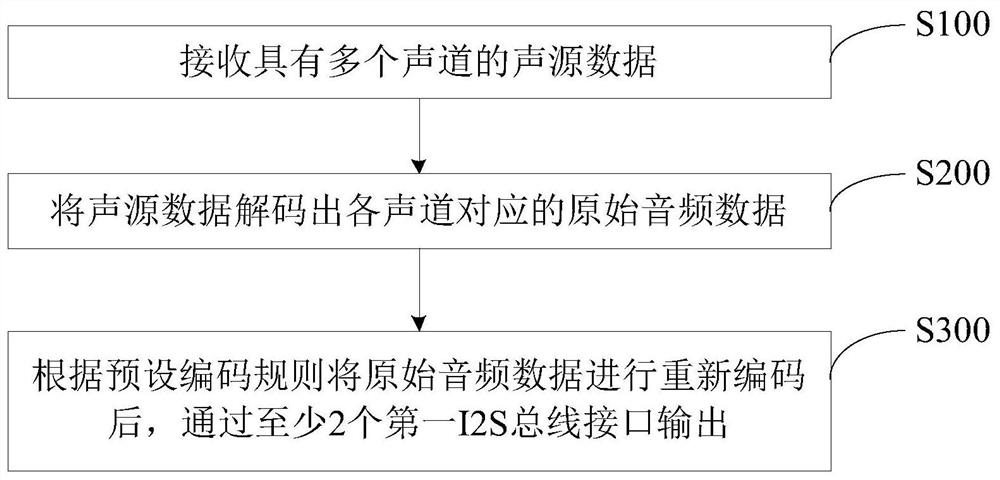

音频处理方法与装置、以及多声道系统

本发明公开了一种音频处理方法与装置、以及多声道系统,通过将声源数据解码出各声道对应的原始音频数据,由于声道的总数大于所有第一I2S总线接口的通道总数,从而根据预设编码规则将原始音频数据进行重新编码后,可以将所有声道的原始音频数据通过至少2个第一I2S总线接口进行输出。这样可以将声源文件中的所有声道对应的原始音频数据均传输到多声道设备中,进而提高多声道设备的播放效果。

2023-08-21 -

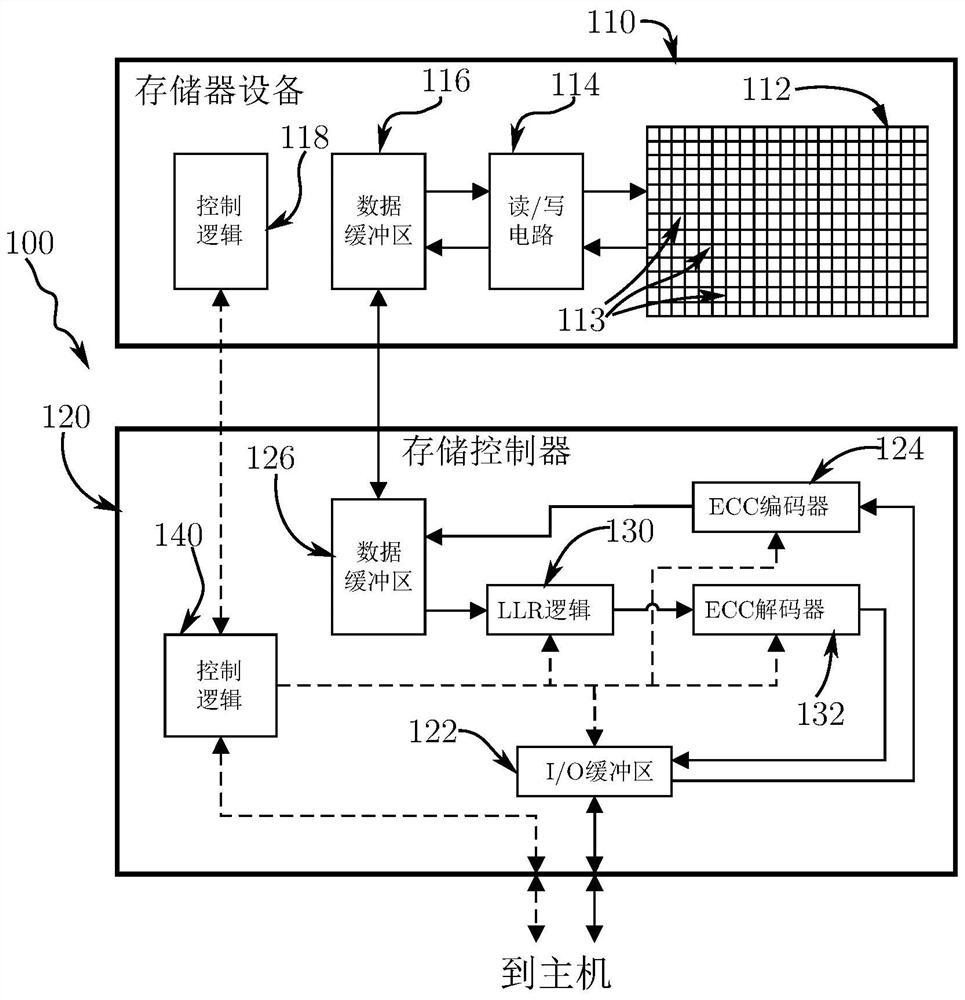

一种操作多状态存储器设备的方法和装置

多状态存储器设备包含一个模拟信号多状态存储单元阵列。每个存储单元可以被视为一个离散信道,包括一个输入符号集,一个输出符号集,和一个转移概率矩阵。数据比特的可靠度信息,如对数似然比,可以根据转移概率矩阵和从存储单元中读取的数据来计算,并用于软解码。在一个数据存储系统中,通常的硬解码和软解码可以通过多种方式结合使用依据转移概率矩阵来计算对数似然比的方法。

2023-08-21 -

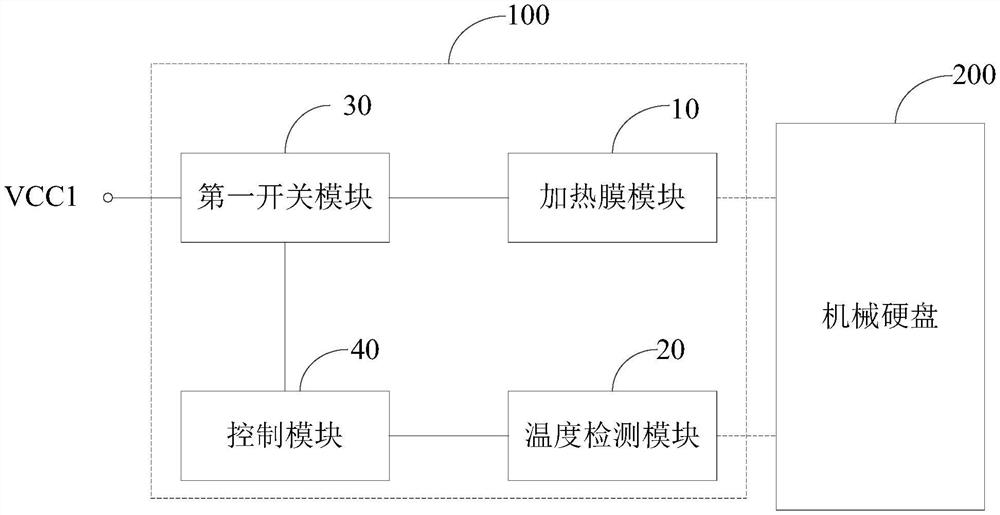

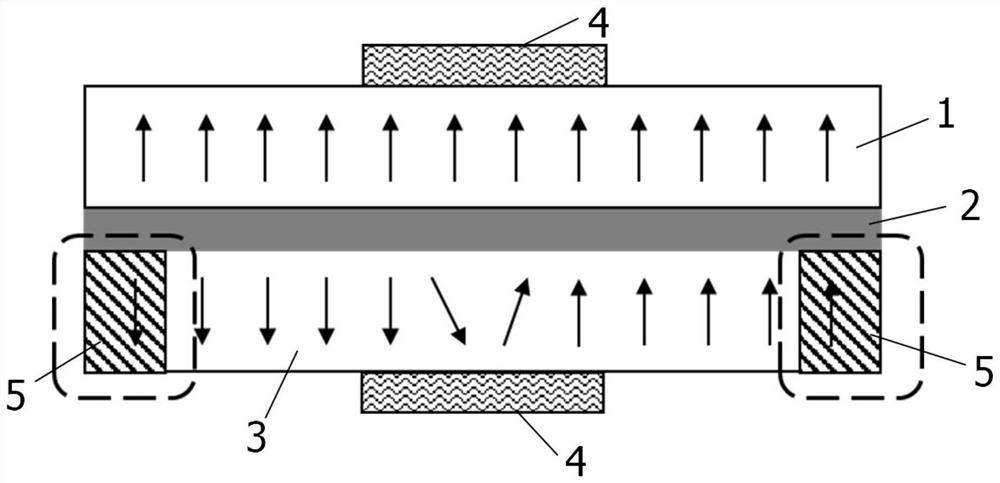

机械硬盘加热电路、机械硬盘加热装置和车辆

本申请公开一种机械硬盘加热电路,该机械硬盘加热电路(100)包括加热膜模块(10)、第一开关模块(30)、温度检测模块(20)和控制模块(40),控制模块(40)根据机械硬盘200的温度对应控制第一开关模块(30)切换至加热模式和停止加热模式,同时,在加热时根据机械硬盘(200)的升温速度对应调整第一开关模块(30)在每个周期内的导通时间,以使机械硬盘(200)的升温速度在预设速度阈值内,可兼容不同尺寸的机械硬盘(200),提高了机械硬盘(200)的加热可靠性和稳定性。

2023-08-21 -

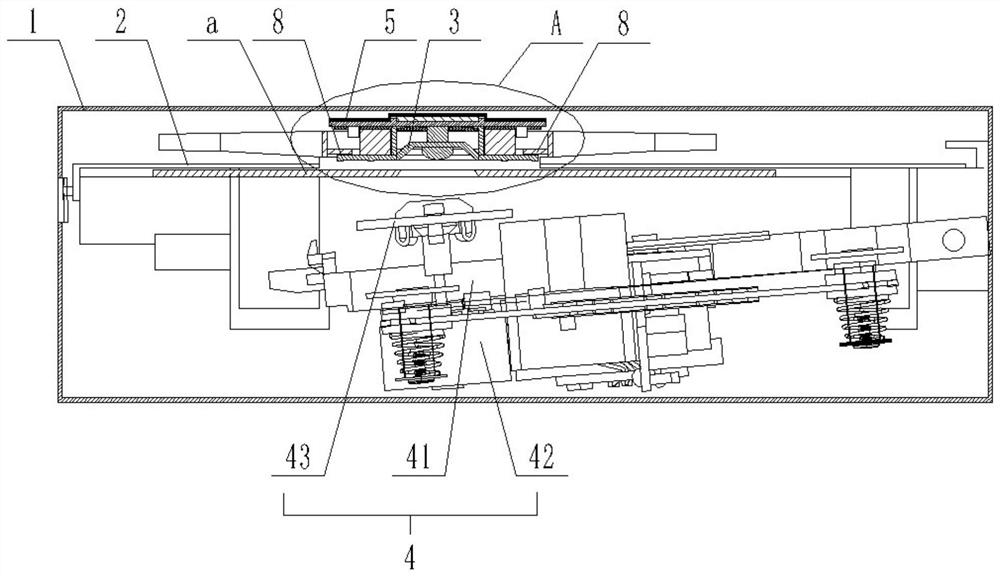

具有光碟进出仓保护功能的光碟机

本发明涉及光碟机技术领域,具体涉及具有光碟进出仓保护功能的光碟机,包括机体,设置于所述机体中的光碟托盘,光碟托盘用以承载一光碟片,光碟托盘上方设置有压碟装置,光碟托盘下方设置有转碟装置,压碟装置包括压碟安装架、压碟片、设置于压碟安装架的第一磁性部件、设置于压碟片的第二磁性部件,第二磁性部件分别与转碟装置或第一磁性部件相互吸引,使压碟片固定或脱离光碟片。与现有技术相比,本发明通过第二磁性部件体与第一磁性部件和转碟装置的磁力差异,在出仓取碟时,随着转碟装置往下滑落,压碟机构失去了第二磁性部件与转碟装置的强磁吸引后,被弱磁的第一磁性部件往上吸,从而方便碟片通过运载托盘取出和送入,避免光碟擦碰。

2023-08-21 -

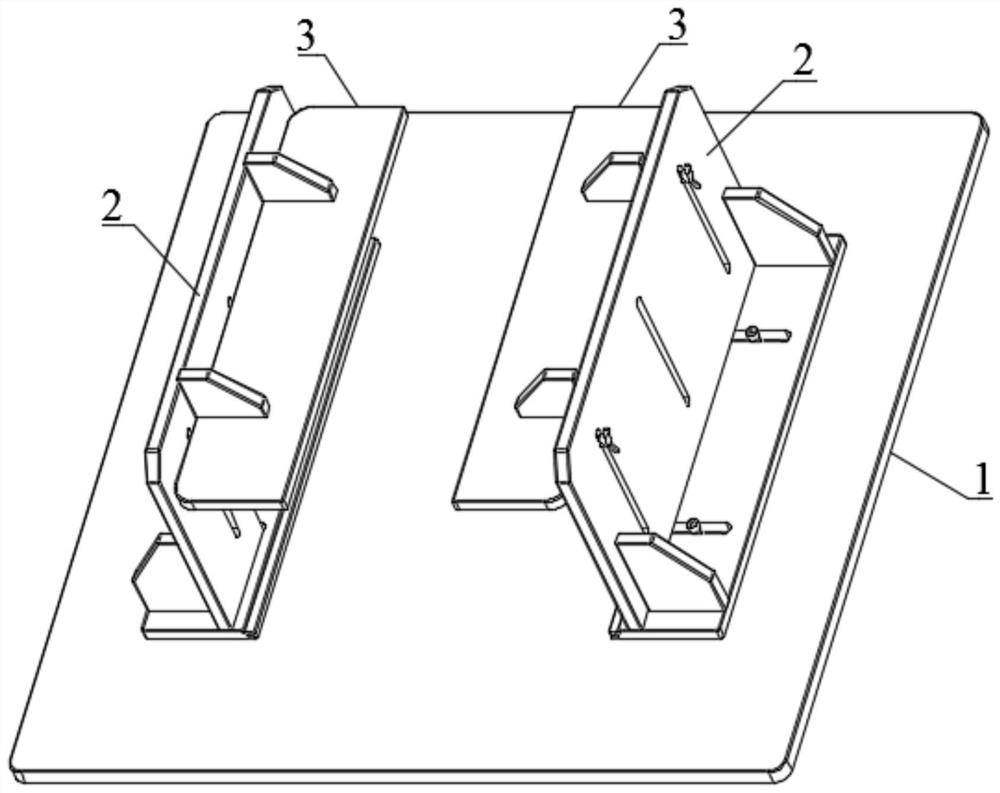

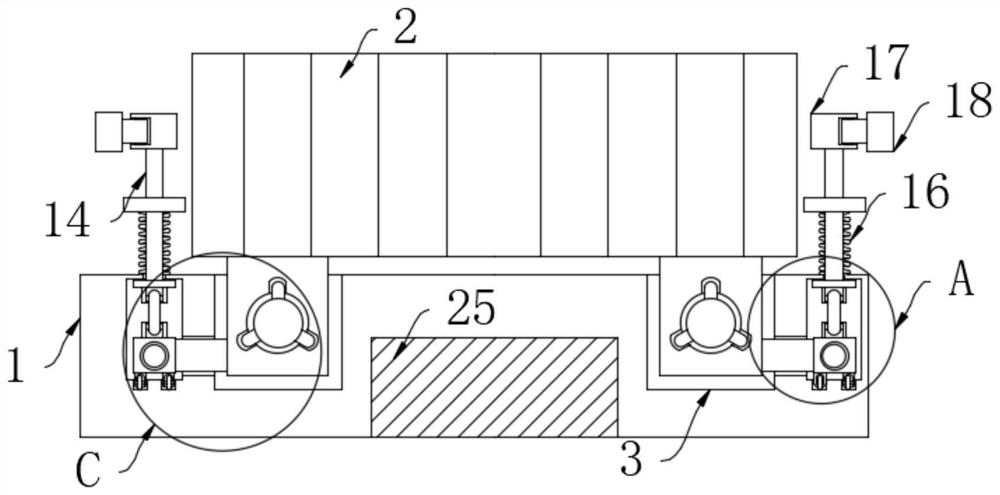

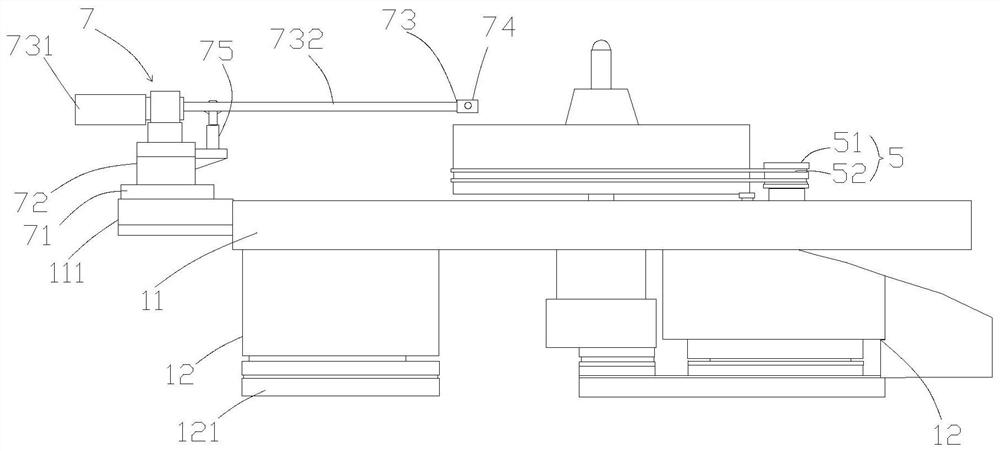

振动测试治具

本发明公开了一种振动测试治具,包括测试底板和两个相对设置于测试底板上的测试夹具,测试夹具在与另一测试夹具相对的一侧底部设置有远离另一测试夹具的方向凹陷的夹持滑槽,至少一个测试夹具在与另一测试夹具相对的一侧顶部设置有向着靠近另一测试夹具的方向延伸的上夹板;本发明通过两个测试夹具的夹持滑槽用于夹持存储器件载板的两端,由于待测存储器件是插接在存储器件载板上,则此时在待测存储器件远离存储器件载板的一端设置有上夹板来抵触待测存储器件,从而在振动测试中更好地对待测存储器件进行夹持固定,避免待测存储器件在振动测试中发生的脱落现象,提高测试效率。

2023-08-21 -

含氟醚化合物、磁记录介质用润滑剂及磁记录介质

本发明涉及下述式(1)表示的含氟醚化合物。R‑CH‑R‑CH‑R(1)(式(1)中,R为包含2个以上的极性基团、各极性基团分别键合于不同的碳原子、前述极性基团所键合的碳原子彼此介由包含未键合极性基团的碳原子的连接基团进行键合而形成的末端基团,R包含下述式(3)表示的全氟聚醚链,R为羟基或R。)‑(CF)‑O‑((CF)O)‑(CF)‑(3)(式(3)中,y表示2~4的整数,z表示1~30的整数。)。

2023-08-21 -

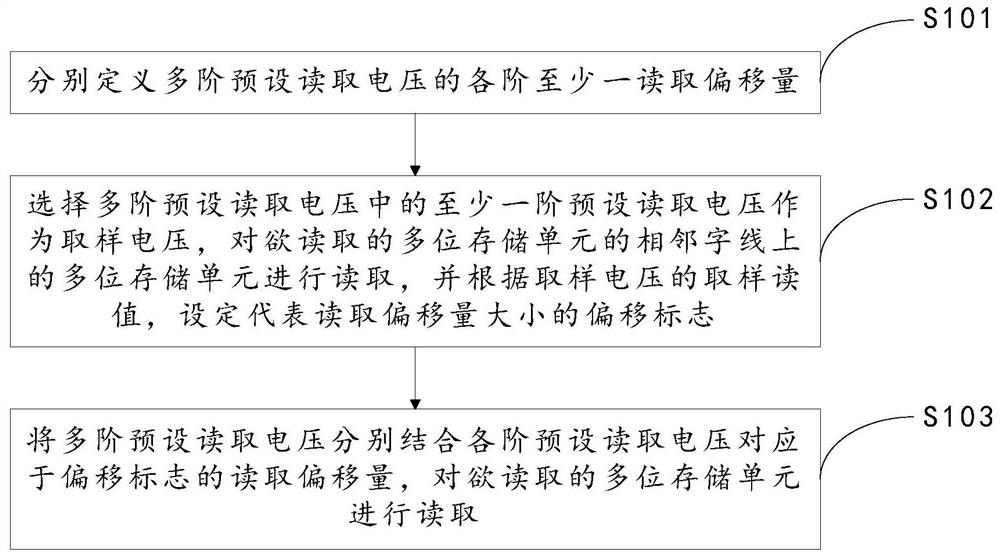

存储器的读取方法以及电压补偿装置

本发明提供了一种存储器的读取方法,存储器包括多条字线以及连接于多条字线上的多个多位存储单元,多位存储单元用以通过多阶预设读取电压,以读取多位存储单元的存储值,该读取方法包括:分别定义多阶预设读取电压的各阶至少一读取偏移量,选择多阶预设读取电压中的至少一阶预设读取电压作为取样电压,对欲读取的多位存储单元的相邻字线上的多位存储单元进行读取,并根据取样电压的取样读值,设定代表读取偏移量大小的偏移标志,之后,将多阶预设读取电压分别结合各阶预设读取电压对应于偏移标志的读取偏移量,对欲读取的多位存储单元进行读取,从而使得该欲读取的多位存储单元的预设读取电压得以补偿。

2023-08-21 -

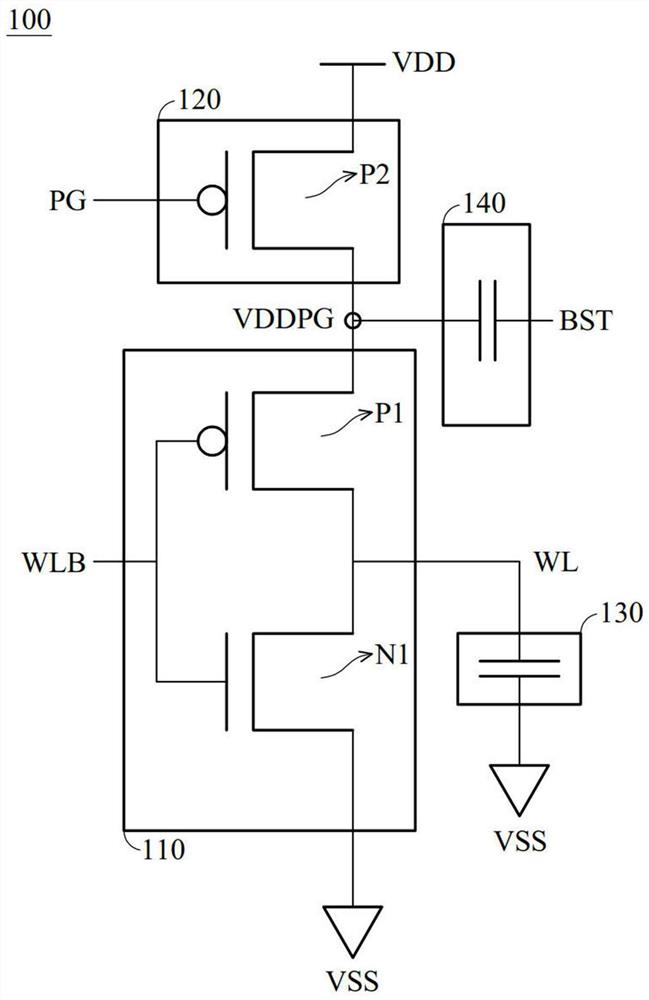

字线调制电路

本发明提供一种字线调制电路。上述字线调制电路包括至少一反相器、一电源开关电路、至少一第一电容器以及至少一第二电容器。上述反相器耦接一字线和一反相字线,以接收一反相字线信号和产生一字线信号,以及经由上述字线耦接一第一电容器。上述电源开关电路耦接上述反相器,以及用以接收一电源开关控制信号。上述第二电容器耦接上述反相器和上述电源开关电路于一内部节点,以及用以接收一升压信号。

2023-08-21 -

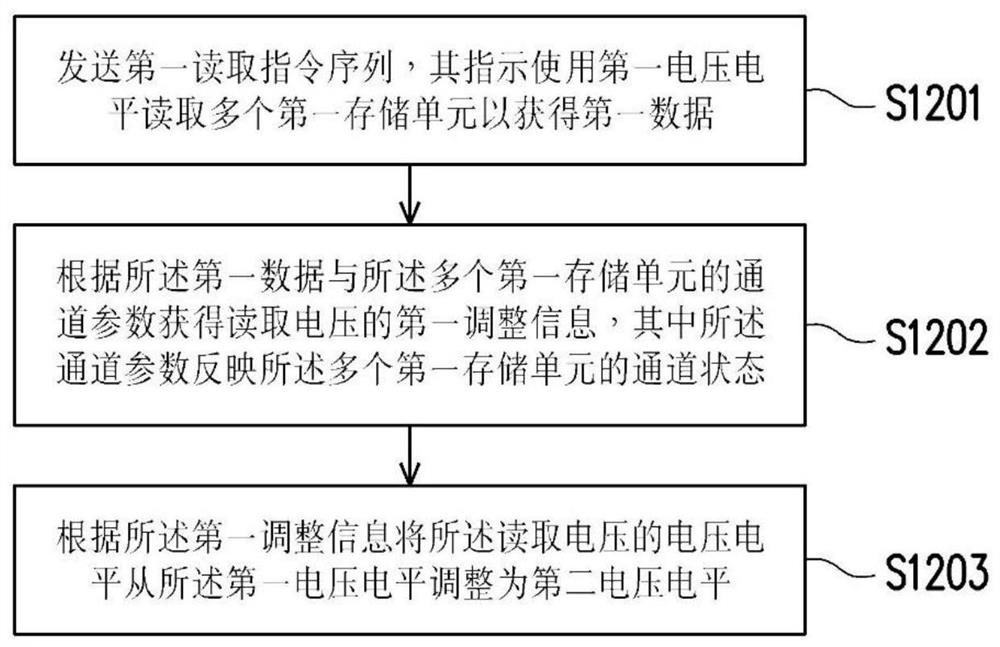

电压控制方法、存储器存储装置及存储器控制电路单元

本发明提供一种电压控制方法、存储器存储装置及存储器控制电路单元,所述读取电压控制方法用于可复写式非易失性存储器模块。所述方法包括:发送第一读取指令序列,其指示使用第一电压电平读取多个第一存储单元以获得第一数据;根据所述第一数据与所述多个第一存储单元的通道参数获得读取电压的第一调整信息,其中所述通道参数反映所述多个第一存储单元的通道状态;以及根据所述第一调整信息将所述读取电压的电压电平从所述第一电压电平调整为第二电压电平。借此,可提高读取电压的校正效率。

2023-08-21 -

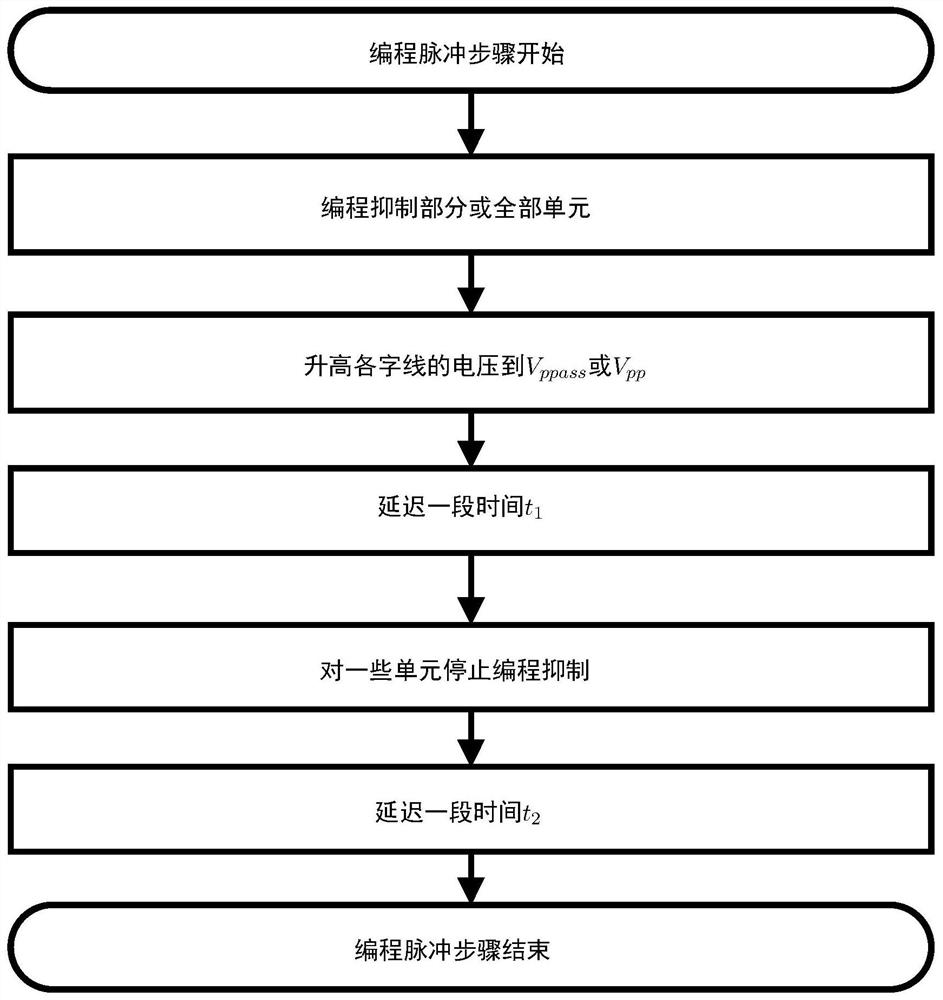

多层单元非易失性存储器的一种编程方法

本发明提供了多层单元存储器的一种编程方法。在编程脉冲步骤中,根据单元目标状态或目标状态和当前状态调整单元的有效编程脉冲的时间,以降低编程所需要的编程脉冲步骤的数量,提高编程效率。本发明还提供了一种适用于多层单元NAND闪存的通过改变位线电压进行部分编程抑制,进而调整单元的有效编程脉冲的时间的方法。

2023-08-21 -

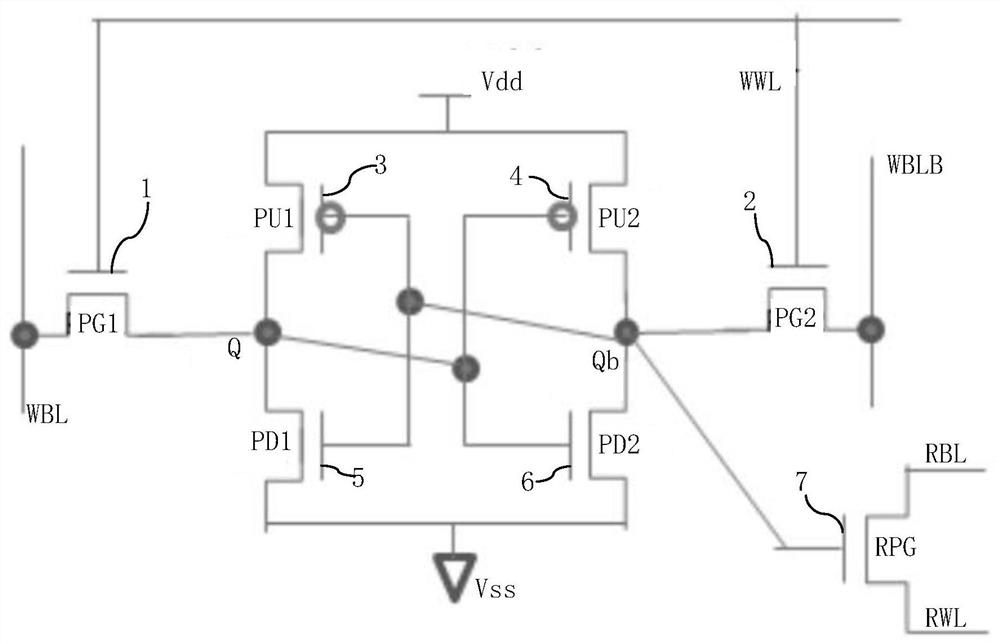

SRAM的存储单元结构及阵列结构

本发明公开了一种SRAM的存储单元结构,包括:主体电路,写端口电路和读端口电路;主体电路包括一对互为反相且互相锁存的第一存储节点和第二存储节点;读端口电路包括第一MOS晶体管,第一MOS晶体管的栅极连接第一和第二存储节点中的一个,第一MOS晶体管的两个源漏区分别连接读位线和读字线;在读操作过程中,读位线为低电平,读字线为高电平;在写操作和待机的过程中,读位线和读字线都保持为低电平。本发明还公开了一种SRAM的阵列结构。本发明能提高SRAM的静态噪声容限和写入余量,同时减少电路面积。

2023-08-21 -

一种准确度高的计算机硬件检测平台

本发明公开了一种准确度高的计算机硬件检测平台,包括台体以及两个检测板,所述台体上对称设有两个滑槽,两个所述检测板下端均固定安装有两个滑块,每两个位置相对应的所述滑块共同滑动连接在对应的滑槽内,所述台体上设有两个安装槽,且两个安装槽内均固定安装有固定杆,两个所述固定杆上均滑动连接有两个滑套,每个所述滑套上均固定安装有连接杆,两个所述安装槽的侧壁上均设有连接槽。优点在于:本发明内存条在检测平台上的拿取以及固定操作均较为简便,无需进行插拔操作,可避免插拔过程中内存条出现磨损的问题,且检测过程中可确保两个检测板与内存条连接紧密,避免因连接不牢导致检测结果不准确的问题。

2023-08-21 -

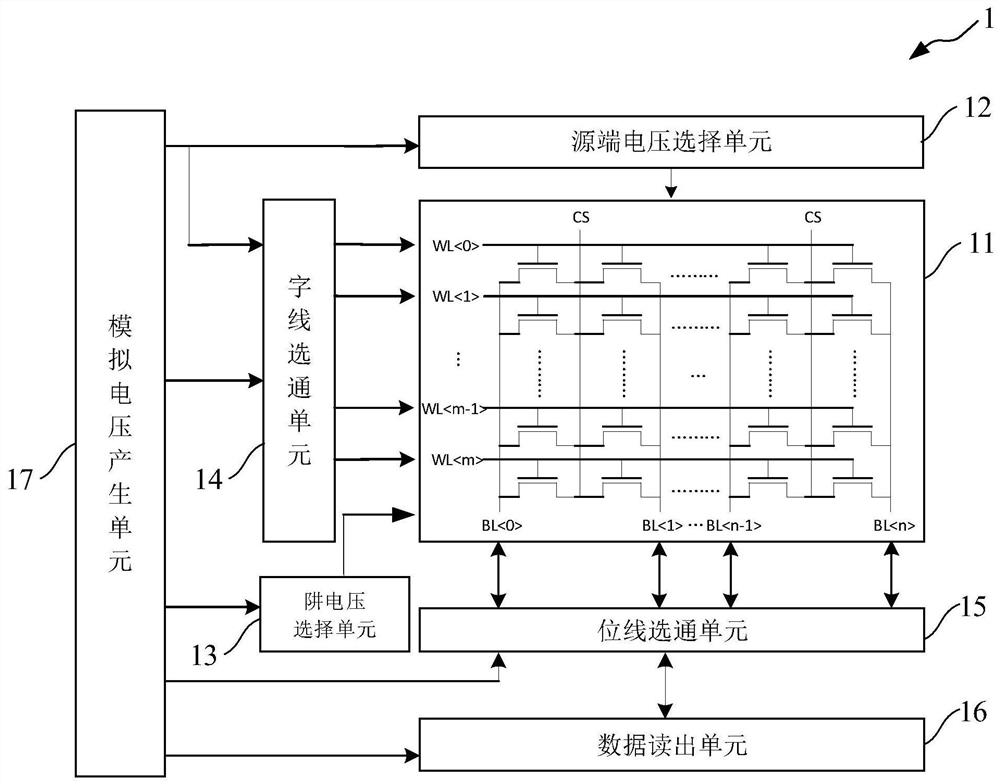

NOR闪存电路及数据写入、读取、擦除方法

本发明提供一种NOR闪存电路及数据写入、读取、擦除方法,包括:NOR存储阵列,源端电压选择单元,阱电压选择单元,字线选通单元,位线选通单元,数据读出单元及模拟电压产生单元。数据写入时将源极浮空,阱电极接地;待写入数据的存储单元所在位线施加第一正向电压、字线施加第二正向电压。数据读取时将源极接地,阱电极接地;待读取数据的存储单元的字线施加第三正向电压、位线选通并输出数据。数据擦除时源极及阱电极接第五正向电压;待擦除数据的存储单元所在位线浮空、字线施加负向电压。本发明通过操作步骤的改进优化,可降低存储单元的有效沟道长度,进而缩减存储器面积,同时提高效率、降低功耗。

2023-08-21 -

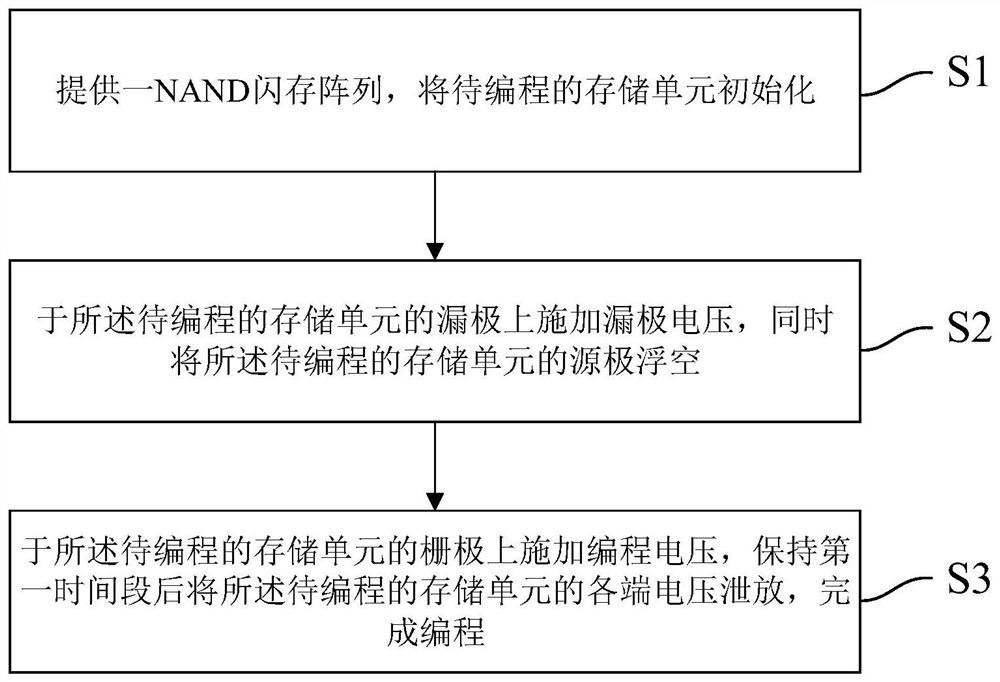

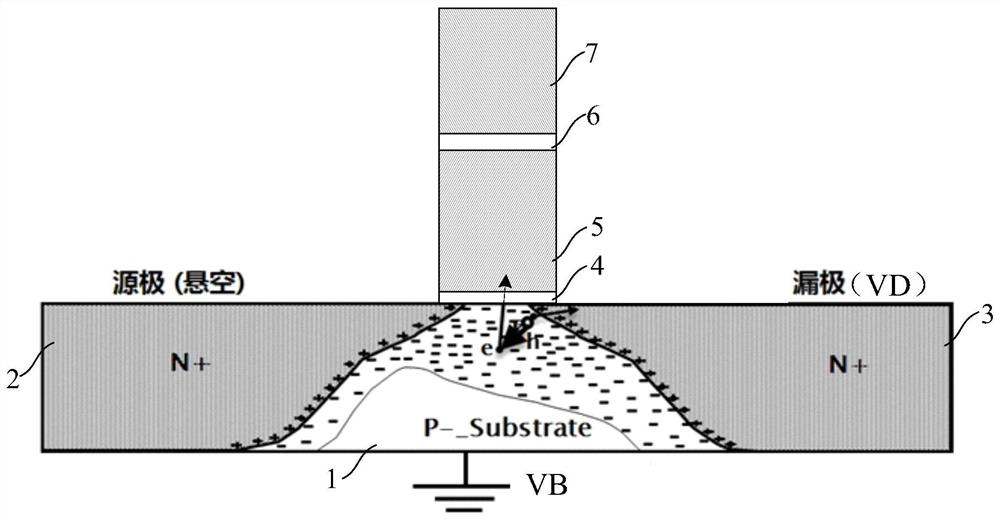

NAND闪存编程方法

本发明提供一种NAND闪存编程方法,包括:提供一NAND闪存阵列,将待编程的存储单元初始化;于待编程的存储单元的漏极上施加漏极电压,将待编程的存储单元的源极浮空;于待编程的存储单元的栅极上施加编程电压,保持第一时间段后将待编程的存储单元的各端电压泄放,完成编程;其中,待编程的存储单元的漏极及衬底的电压差不小于4V,第一时间段不大于100μs,编程电压不大于10V。本发明的NAND闪存编程方法初始化后,施加漏极电压并对源极做浮空处理,然后施加编程电压完成编程,编程时的栅极电压远小于现有的隧穿(F‑N)编程方式的栅极电压,且编程时间短,可有效提高存储单元的使用寿命及编程效率,同时降低功耗。

2023-08-21 -

快闪存储器的编程方法

本发明提供一种快闪存储器的编程方法,包括:提供一具有浮栅的闪存结构,将闪存结构的源极浮空;在漏极及衬底分别施加电压,形成电场,产生电子空穴对,形成一次电子,其中,施加于衬底的电压小于施加于漏极的电压;在预设时间内,空穴在电场作用下向下做加速度运动并撞击闪存结构中的衬底,产生二次电子;在栅极及衬底分别施加电压,施加于衬底的电压小于施加于栅极的电压,使二次电子在垂直方向电场作用下形成三次电子注入浮栅中,完成编程操作。本发明通过编程电压操作方式的改进优化,形成三次电子激发进行编程,可以提高编程效率,降低功耗,编程读取电流大,对隧穿氧化层损伤小;同时能避免本体贯通效应,为闪存进一步微缩创造条件。

2023-08-21 -

音频播放方法及装置

本公开是关于一种多音频文件播放方法及装置。其中,多音频文件播放方法包括:接收对于第一音频的播放开始指令;在当前正在播放N个第二音频的情况下,将当前待播放音频的总数更新为N+1;确定播放切换时长;以播放切换时长为单位,分别将当前待播放音频中的每一音频的未播放部分划分为多个音频片段;根据时间线,依序轮流播放各个当前待播放音频的一个音频片段,当前待播放音频的每一音频的前一音频片段的播放结束时刻与后一音频片段的播放开始时刻在时间线上的时间间隔不超过预定最大阈值。在需要播放多个音频的情况下,通过在根据播放切换时长轮流播放多个音频,避免了混音带来的音质下降,同时也保证了用户收听效果,从而提高了播放质量。

2023-08-21 -

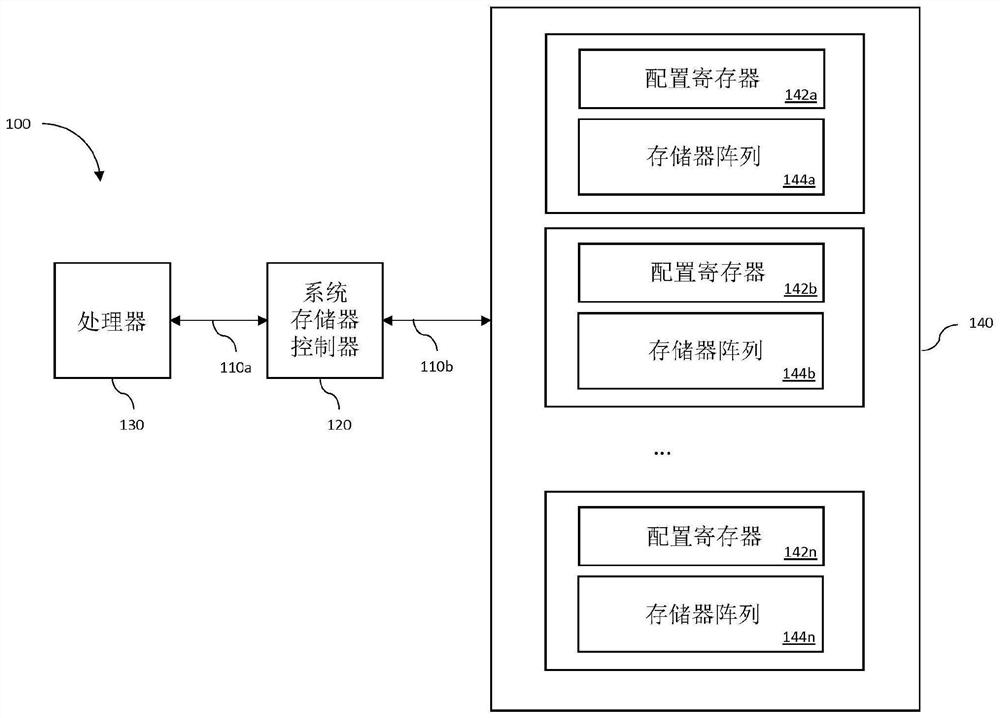

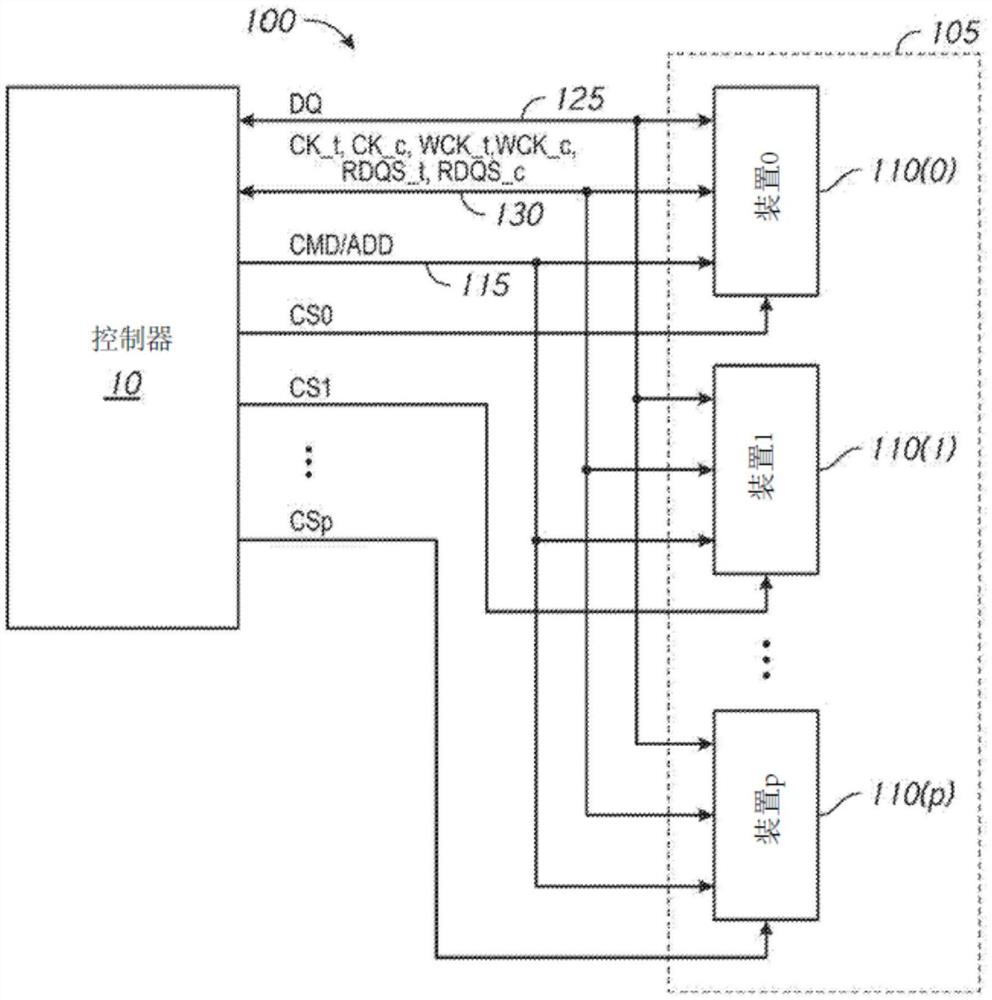

用于动态地调整分区存储器的性能的方法和设备

本发明揭示用于动态地调整分区存储器的性能的方法和设备。在一个实施例中,所述方法包含:接收对存储器装置的一或多个配置请求;确定是否准予对所述存储器装置的所述一或多个配置请求;响应于所述确定,在所述存储器装置内实施所述一或多个配置请求;及根据所述实施操作所述存储器装置。对所述分区存储器的所述性能的所述调整包含以下操作中的一或多个:启用/禁用刷新操作,变更所述分区存储器的刷新速率,对所述分区存储器启用/禁用纠错码ECC电路系统,和/或变更所述分区存储器的存储器单元架构。本发明还揭示可从所述动态性能调整受益的系统和应用程序。

2023-08-21 -

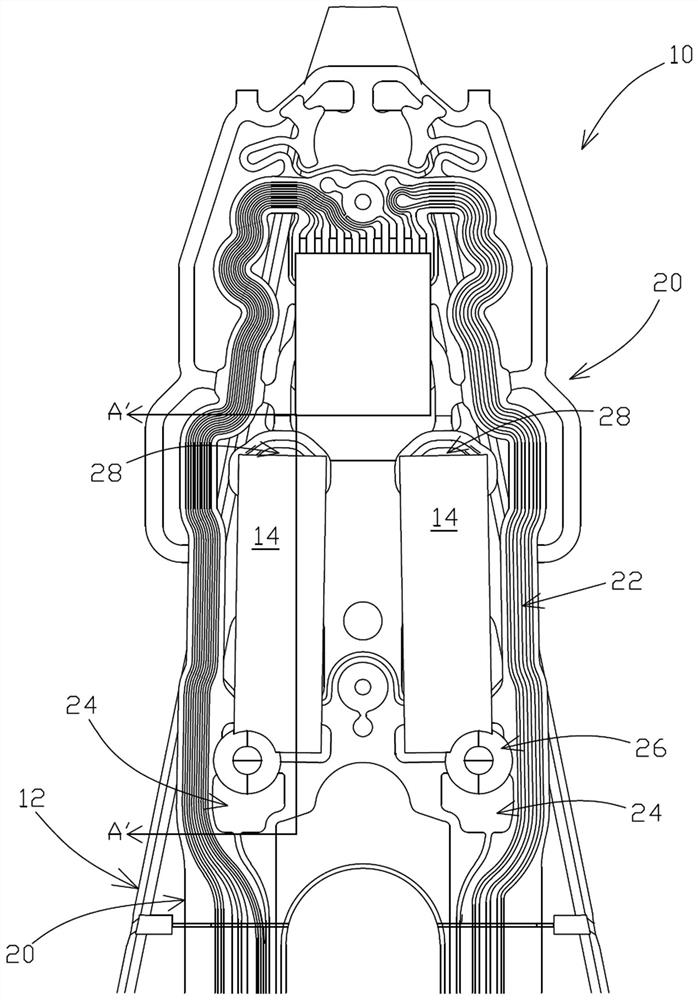

用于谐振改善的多层执行器电极构型

描述了压电致动器组件。该压电致动器组件包括第一有源压电层、第二有源压电层和第三有源压电层。第一层包括顶表面和底表面。第二层包括顶表面以及在第一层的顶表面上的底表面。第三层包括顶表面以及在第二层的顶表面上的底表面。第一层和第二层可限定第一有效电极长度。类似地,第二层和第三层可限定第二有效电极长度,该第二有效电极长度被构造成比该第一有效电极长度长。

2023-08-21 -

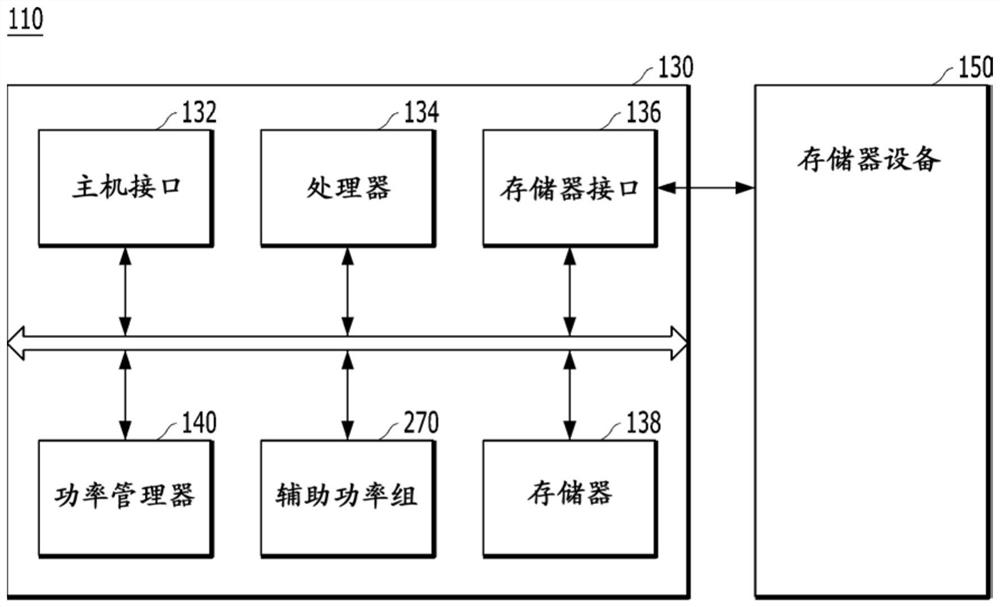

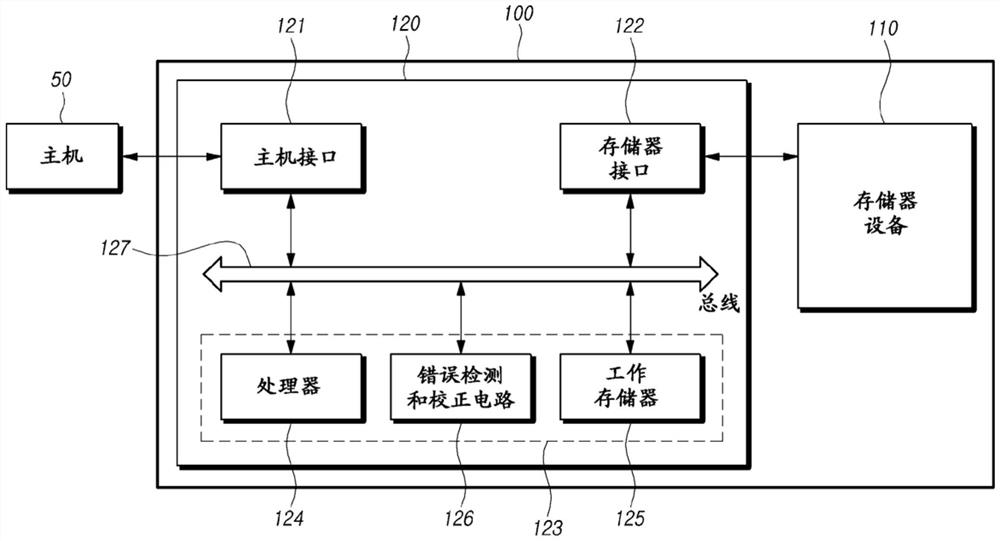

存储器系统及其操作方法

本文描述了存储器系统及其操作方法。一种存储器系统可以包括:适于存储数据的存储器设备;适于控制存储器设备的控制器;适于接收外部功率并且向存储器设备和控制器供应操作功率的功率管理器;以及适于从功率管理器接收操作功率、存储所接收的功率以及在外部功率被移除时向功率管理器供应辅助功率的多个辅助功率电路。功率管理器可以将多个辅助功率电路之中所选择的辅助功率电路进行分组和管理为测试组,并且对所选择的辅助功率电路执行完全放电测试。

2023-08-21 -

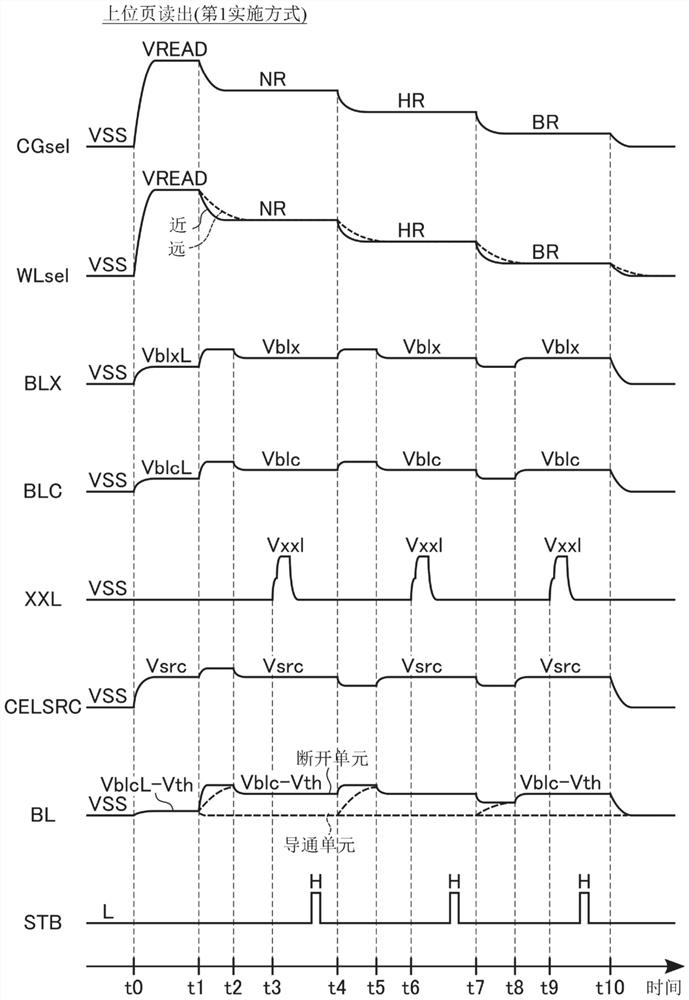

半导体存储装置

实施方式提供一种能够使读出动作高速化的半导体存储装置。实施方式的半导体存储装置包含连接于位线与源极线之间的存储单元、连接于存储单元的栅极的字线、以及执行读出动作的控制器。在读出动作中,控制器对字线(WLsel)施加第1读出电压(NR)与第2读出电压(BR),在施加第1读出电压的第1时刻与施加第2读出电压的第2时刻分别读出数据。控制器在第1时刻与第2时刻,分别对源极线施加第1电压(Vsrc),在对字线施加第1读出电压期间且在第1时刻之前对源极线施加高于第1电压的第2电压,在对字线施加第2读出电压期间且在第2时刻之前对源极线施加低于第1电压的第3电压。

2023-08-21 -

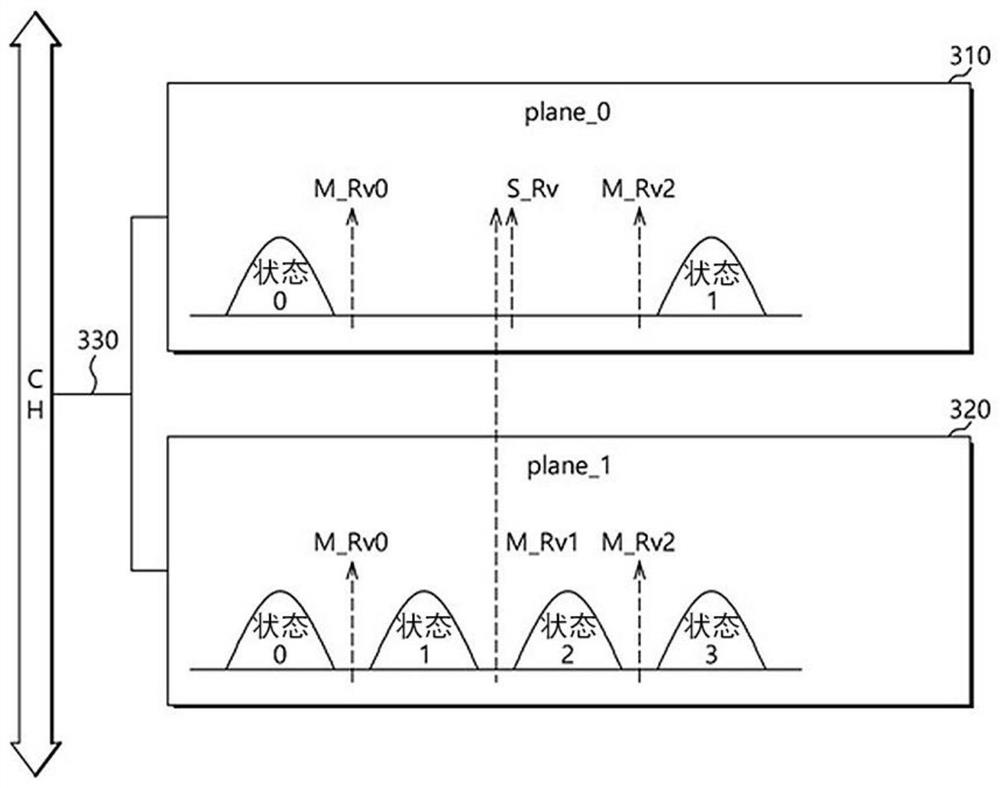

控制器、存储器系统及其操作方法

一种存储器系统包括:非易失性存储器装置;以及控制器,控制非易失性存储器装置。非易失性存储器装置包括存储器单元以第一模式存储一位数据的第一数据存储区域和存储器单元以第二模式存储两位或更多位数据的第二数据存储区域。控制器控制非易失性存储器装置以第二模式对第一数据存储区域和第二数据存储区域执行读取操作。控制器将通过读取操作从第一数据存储区域读取的第一数据解码为第一模式的数据,并将通过读取操作从第二数据存储区域读取的第二数据解码为第二模式的数据。控制器控制非易失性存储器装置通过将读取第二模式的数据的多个读取电压中的任意一个改变为读取第一模式的数据的读取电压值来以第二模式对第一数据存储区域执行读取操作。

2023-08-21 -

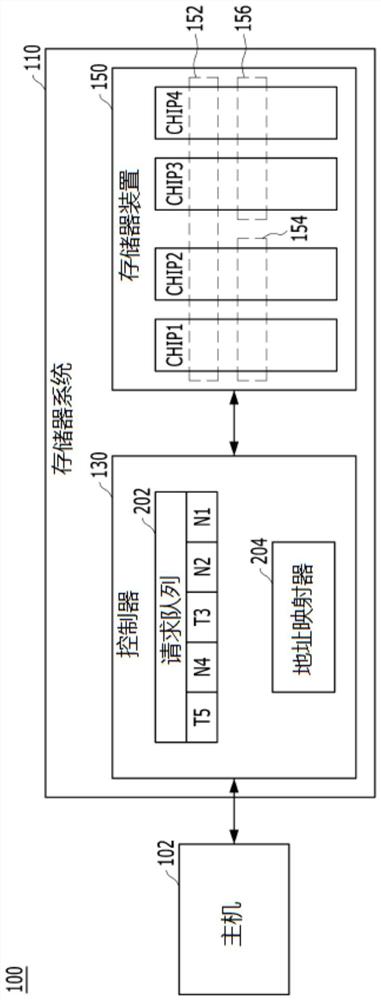

控制器及其操作方法

本申请涉及一种控制器。该控制器控制存储器芯片,每个存储器芯片包括由多个存储块组成的至少一个平面,该控制器包括:主机接口,从主机接收请求;地址映射器,在接收到加速写入请求和正常写入请求时,将存储器芯片中的每一个的至少一个平面之中的第一平面分配到第一平面组,以响应加速写入请求,并且将第二平面分配到第二平面组,以响应正常写入请求;以及存储器接口,控制存储器芯片,使得第一平面组执行与加速写入请求相对应的操作,并且第二平面组执行与正常写入请求相对应的操作。

2023-08-21 -

存储器中的感测操作

本公开包含与存储器中的感测操作有关的设备及方法。例示性设备可包含:存储器单元阵列;及控制器,其耦合到所述阵列,所述控制器经配置以基于与第一存储器单元相关联的第一输入以及与第二存储器单元相关联的第二输入及第三输入来感测所述第一存储器单元。

2023-08-21 -

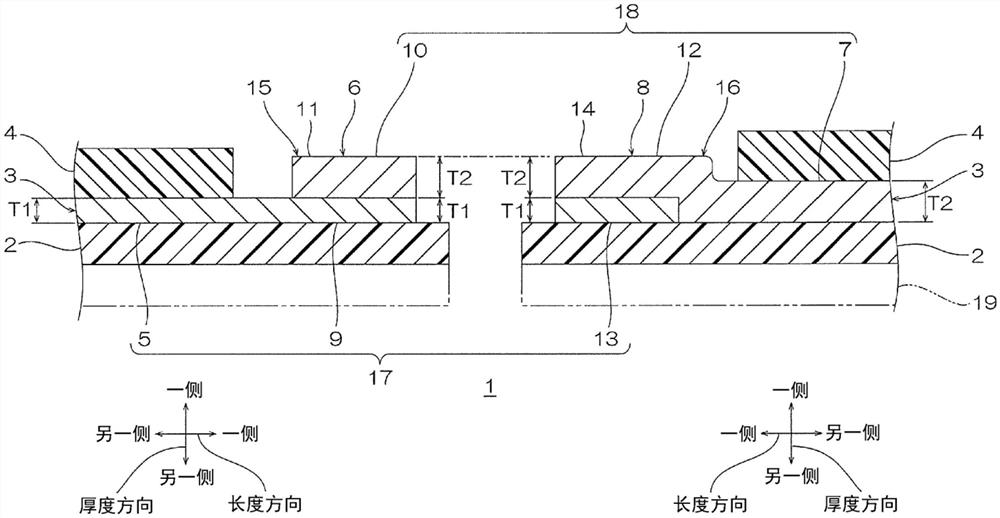

布线电路基板

布线电路基板具有绝缘层和配置于绝缘层的表面的导体层。导体层具有第1布线、与第1布线电连接的第1端子、与第1布线彼此独立并且具有相对于第1布线的厚度T1而言较厚的厚度T2的第2布线以及与第2布线电连接的第2端子。第1端子的表面和第2端子的表面在厚度方向上配置于大致同一位置。

2023-08-21 -

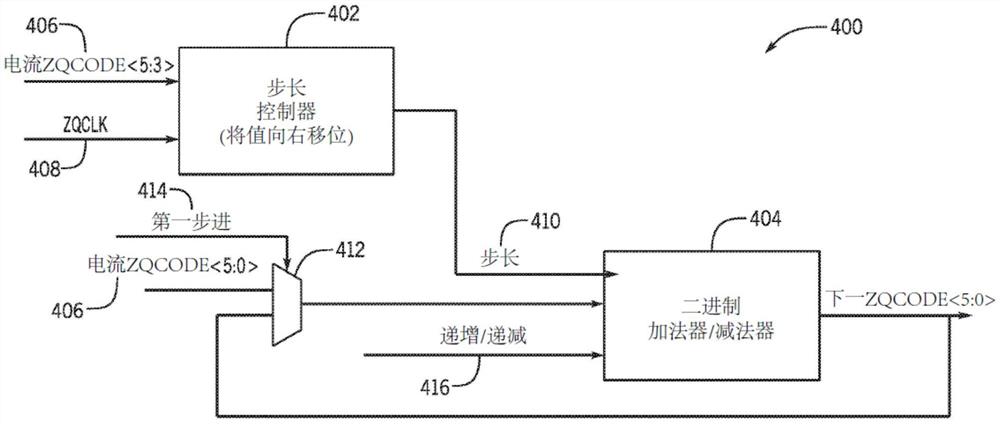

用于半导体装置的阻抗校准的系统及方法

本发明提供用于执行有效ZQ校准的系统及方法。所描述的技术使用非线性补偿电路,其经配置以通过调整校准步进的调整量值、将ZQCODE调整到替代ZQCODE或调整校准步进的所述调整量值且将所述ZQCODE调整到所述替代ZQCODE来补偿多个ZQ校准码的变动与对应电阻变动之间的非线性关系。

2023-08-21 -

用于设置用于改进时钟工作循环的工作循环调整器的设备及

方法

本发明揭示用于设置工作循环器调整器以改进时钟工作循环的设备及方法。所述工作循环调整器可按不同量进行调整,至少一者小于另一者。确定何时使用较小调整可基于工作循环结果。工作循环监测器可具有偏移。可将用于到期工作循环调整器的小循环代码设置到工作循环监测偏移的中间值。可通过识别用于所述工作循环监测偏移的上边界及下边界的工作循环代码确定所述工作循环监测偏移。

2023-08-21 -

控制器、存储器系统及其操作方法

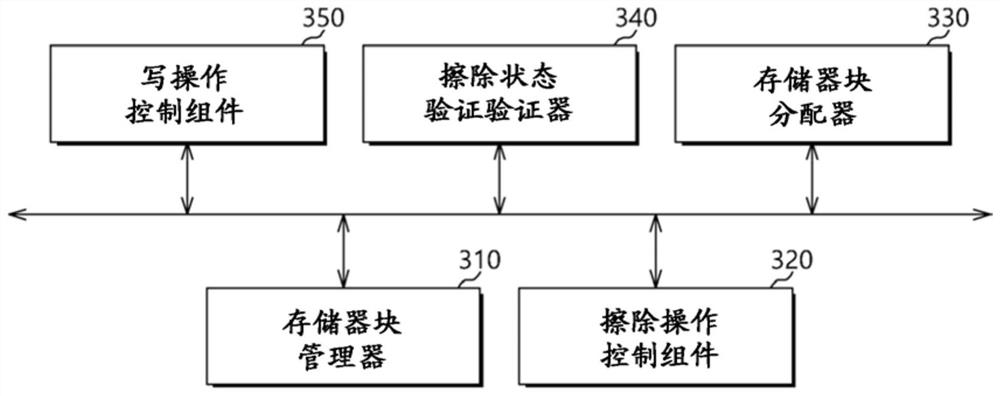

公开了一种控制器、存储器系统及其操作方法。控制器的操作方法包括:控制非易失性存储器设备以对无效存储器块执行第一擦除操作;在对其执行了第一擦除操作的存储器块之中分配用于写操作的目标存储器块;控制非易失性存储器设备以对目标存储器块执行擦除状态验证操作;以及当擦除状态验证操作指示目标存储器块的擦除状态满足设定条件时,控制非易失性存储器设备以对目标存储器块执行写操作。

2023-08-21 -

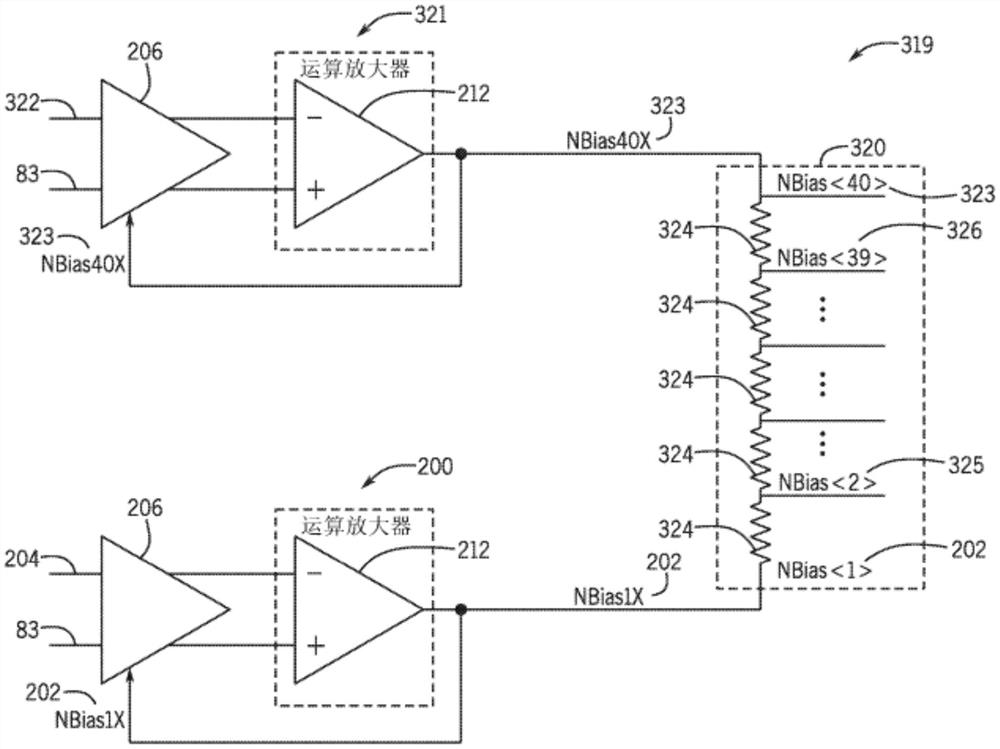

多偏置电平生成和内插

一种装置(10)包含:第一偏置电平生成器(200),其用以生成多个偏置电平中的第一偏置电平(202)且发射具有第一电压值的偏置电平(202);第二偏置电平生成器(321),其用以生成所述多个偏置电平中的第二偏置电平(323)且发射具有第二电压值的第二偏置电平(321)。所述装置(10)还包含分压器(320),所述分压器在所述第一偏置电平(202)与所述第二偏置电平(323)之间内插所述多个偏置电平的偏置电平子组,且将所述多个偏置电平中的选定偏置电平控制信号供应到决策反馈均衡器(70)的调整电路,以补偿由于位流的先前接收位带来的位的符号间干扰。

2023-08-21 -

一种利用光敏电阻的软件硬盘偏转自动校正的辅助设备

本发明涉及软件硬盘维护技术领域,且公开了一种利用光敏电阻的软件硬盘偏转自动校正的辅助设备,包括保护层,所述保护层内部活动连接有固定壳,所述固定壳内部活动连接有读取接口,所述固定壳顶部活动连接有紧固板,所述紧固板顶部活动连接有安装座,所述安装座顶部活动连接有传动柱,所述传动柱顶部活动连接有施压磁铁,通过当硬盘发生倾斜时,则此时发光灯泡产生的光照射至硬盘表面时会有一定的角度从而发生折射,折射后的光照射在光敏电阻的表面,使得通电线圈对复位弹簧产生的吸引力增大,从而使得紧固板对硬盘施加的紧固力降低,使得硬盘起翘端向下运动,从而达到了硬盘发生倾斜时自动调整使其平整的效果。

2023-08-21 -

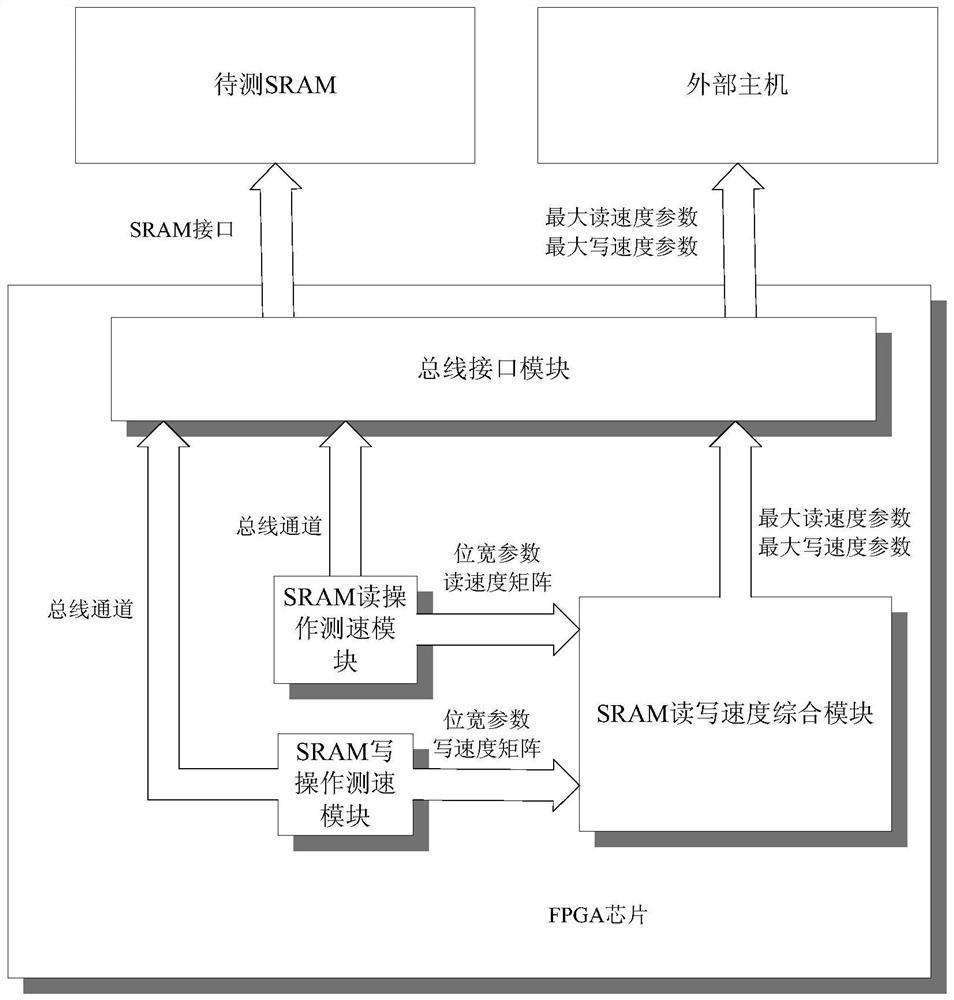

SRAM通用测速电路

本发明属于SRAM存储硬件系统技术领域,具体涉及一种SRAM通用测速电路。所述SRAM通用测速电路包括:SRAM读操作测速模块、SRAM写操作测速模块、SRAM读写速度综合模块和总线接口模块;为了解决硬件系统在适配不同型号的SRAM时无法自动识别SRAM的最大读写速度而导致的无法发挥SRAM最佳性能的问题。该电路通过对SRAM读写速度采用特定算法进行多次试探性采样确定SRAM的读写速度。该电路可以通过硬件实现模块化并嵌入到硬件电路系统中,使系统具备自动识别SRAM读写速度的功能,在系统更换SRAM后不用更改系统代码和状态,提高了系统的兼容性、易用性和可维护性,具有十分重要的应用意义。

2023-08-21 -

缓震唱片机

本发明公开了一种缓震唱片机,涉及放音装置技术领域;其包括底座、第一转盘、第二转盘、第一驱动部件和传动部件;所述第一转盘可转动的安装在所述底座上方,所述第一驱动部件安装在所述底座内;所述传动部件分别与所述第一驱动部件和所述第一转盘传动连接;所述第二转盘用于安装唱盘,所述第二转盘安装在所述第一转盘上,并与所述第一转盘同步转动。本发明通过在第二转盘下部设置第一转盘,第一转盘通过皮带与电机连接,以第一转盘转动带动上层第二转盘转动,提升了仅由皮带带动第二转盘转动所带来的震动。

2023-08-21 -

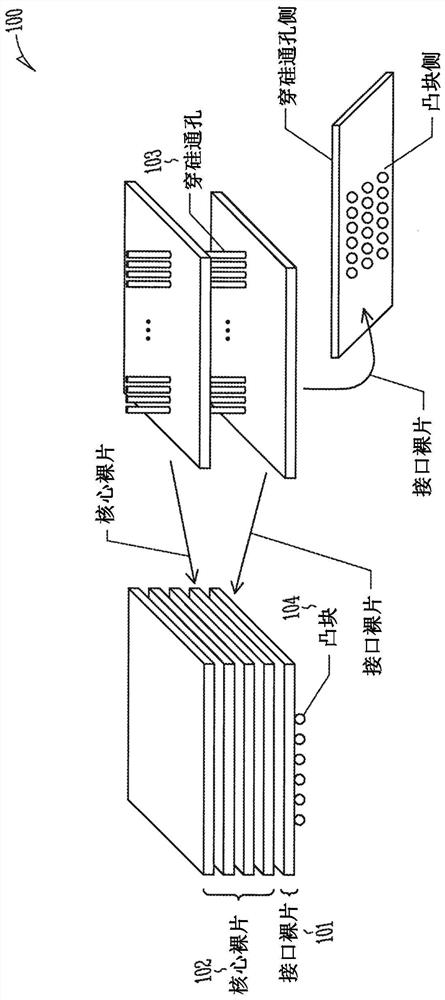

具有裸片以执行刷新操作的设备

本申请涉及具有裸片以执行刷新操作的设备。一些实施例包含一种设备,其包括:接口芯片,其具有振荡器以产生原始时钟信号;第一存储器芯片,其具有第一存储器单元;及第二存储器芯片,其具有第二存储器单元。可响应于基于所述原始时钟信号的第一时钟信号而刷新所述第一存储器单元。可响应于基于所述原始时钟信号的第二时钟信号而刷新所述第二存储器单元。

2023-08-21 -

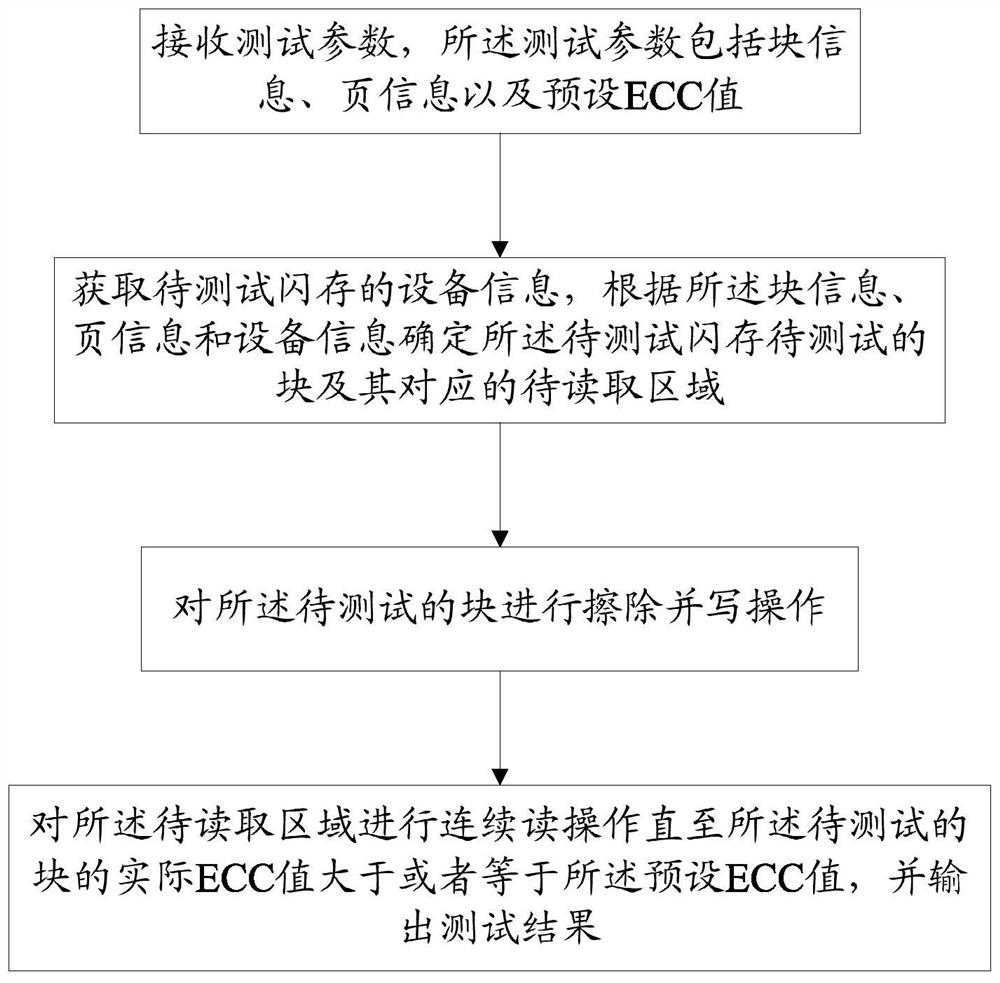

读干扰测试方法、装置、计算机可读存储介质及电子设备

本发明公开一种读干扰测试方法、装置、计算机可读存储介质及电子设备,根据输入的测试数据确定待测试闪存待测试的块及其对应的待读取区域,对待读取区域进行连续读操作直至所述待测试的块的实际ECC值大于预设ECC值,并输出测试结果,通过自动化测试方式,有效检测待测试闪存持续读操作下,不同读次数所对应的块的稳定程度,从而在对闪存的数据安全处理上,获取到一个可以明确需要数据搬移或刷新的读次数的阈值,通过自动化的方式实现了测试对比动作,实现对读干扰的自动化测试,提高了测试效率,并且能够输出直观的测试结果,方便对闪存进行特性分析和之后的算法调试。

2023-08-21 -

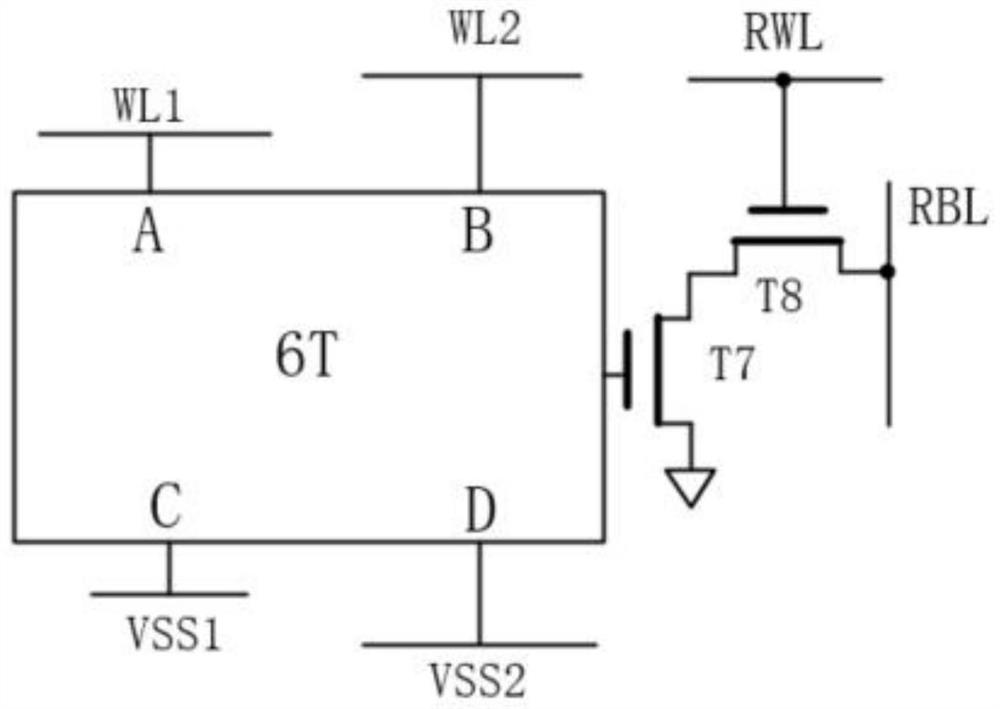

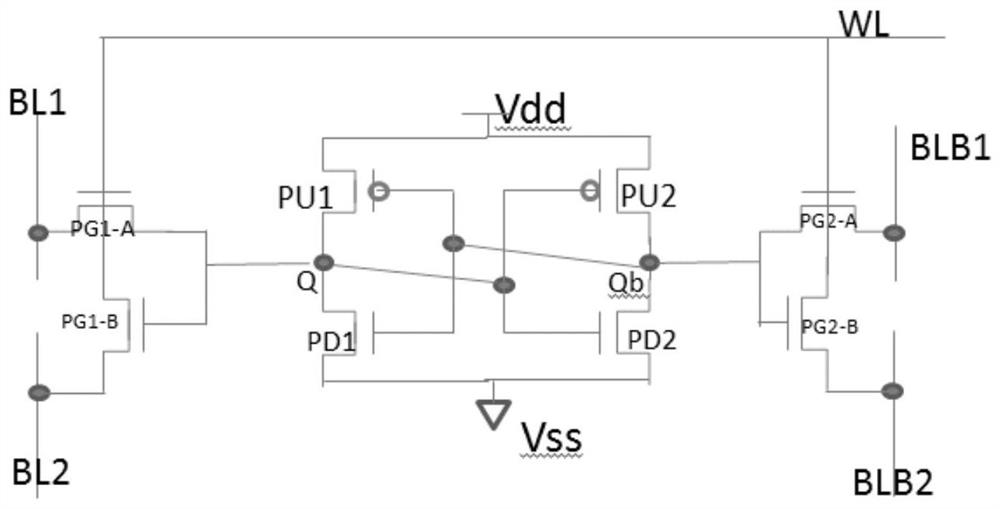

一种8管双分裂控制存储单元、存储阵列及存内计算装置

本发明涉及一种8管双分裂控制存储单元、存储阵列及存内计算装置,包括PMOS管T1、PMOS管T2、NMOS管T3、NMOS管T4、NMOS管T5、NMOS管T6、NMOS管T7、NMOS管T8、位线BL、位线BLB、读字线RWL、读位线RBL、字线WL1、字线WL2、公共接地线VSS1和公共接地线VSS2,采用两个T7管、T8管的NMOS串联实现权重和输入乘积的计算方式,将模拟计算结果在读位线上进行模拟累计,最后将模拟电压通过ADC数字化输出,简化了计算方式,节省了计算面积。

2023-08-21 -

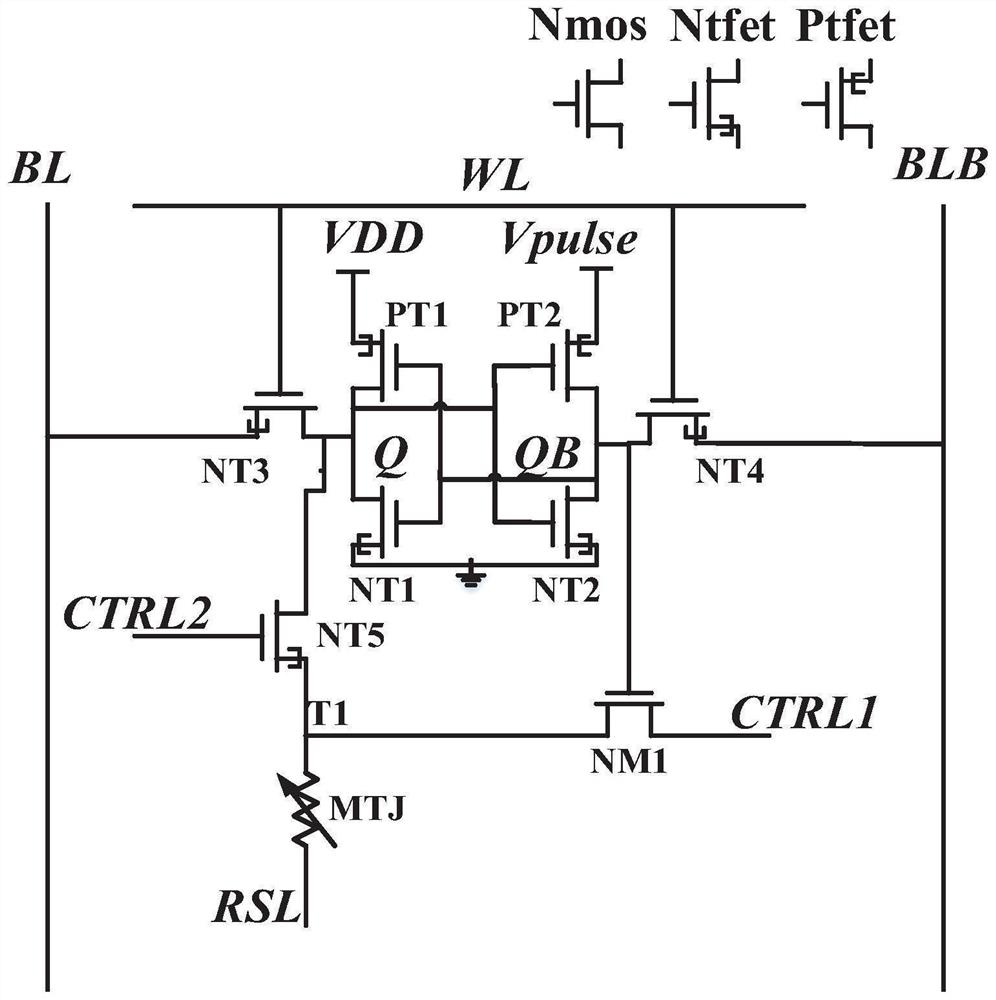

利用隧道场效应管抑制漏电的混合非易失性随机存储器

本发明公开了利用隧道场效应管抑制漏电的混合非易失性随机存储器,该随机存储器SRAM包括上电后存储数据的SRAM存储模块、断电前保存数据的磁隧道结(MTJ)写入路径、电源恢复后SRAM数据恢复路径、磁隧道结(MTJ)数据恢复路径,SRAM存储模块包含六个隧穿场效晶体应管(TFET)晶体管,即两个上拉集体管、两个下拉晶体管、两个数据传输晶体管;本发明利用了TFET的超低漏电和在超低电压下工作的的特性,能够实现非易失存储功能,达到整体电路漏电和SRAM唤醒功耗降低的目的。该结构利用了TFET的超低漏电和在超低电压下工作的的特性,使得整体电路漏电和SRAM唤醒功耗降低。此外,在MTJ写入速度以及电路唤醒功耗上也有一定的改善。

2023-08-21 -

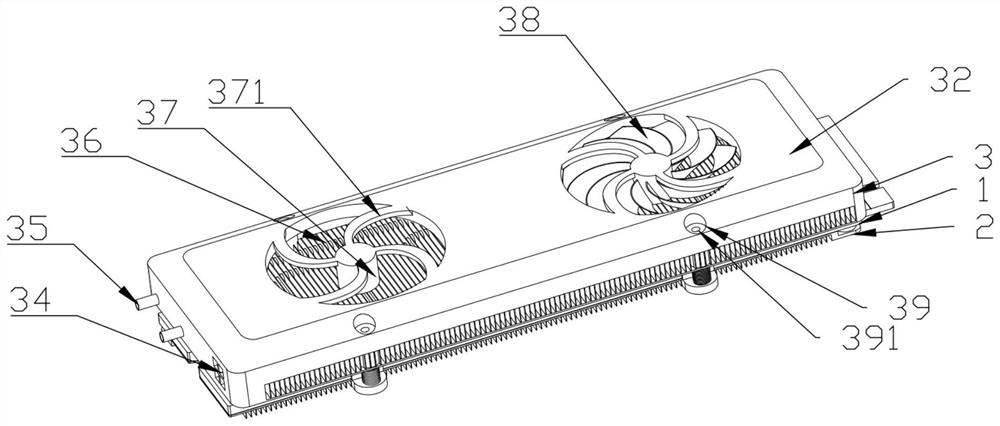

一种复合式M.2硬盘散热装置

本发明公开了一种复合式M.2硬盘散热装置,包括散热底座和散热顶,所述散热底座的顶部与M.2硬盘的底部贴合,所述散热底座的底部设有均匀分布的下散热片,所述散热顶与M.2硬盘顶部存储单元的顶部贴合设置;本发明通过散热底座与散热顶的设置,为M.2硬盘提供了一种高效的复合式散热方案,能够有效的控制M.2硬盘的高负载运行温度,减少热量堆积对M.2硬盘寿命和工作速度的影响,降低数据丢失的可能性;同时上下双层式的散热设置,使得M.2硬盘产生的热量能够双向流动散热,减少了热量在导热性较差的硬盘材料中的传递距离,提升了导热效率,双向的导热也大大减少了热量经由存储单元向上传递的部分,能够有效的控制存储单元温度,进一步降低了数据丢失的风险。

2023-08-21 -

一种EEPROM芯片上的高效自检测电路

本发明提出一种EEPROM芯片上的高效自检测电路,其特征在于,包括:移位寄存器1、计数器1、计数器2、比较器1、触发器、比较器2、计数器3、比较器3、选择器和移位寄存器2。当数字逻辑电路接收到0x86命令后,自主发送写和读请求至EEPROM。上位机发送0x87命令轮询芯片检测状态,当收到ack为1时,表示芯片正在处于自检测状态,当收到ack为0时,芯片将紧接着发送8位有效数据0xaa或0x55,表征自检测结果。

2023-08-21 -

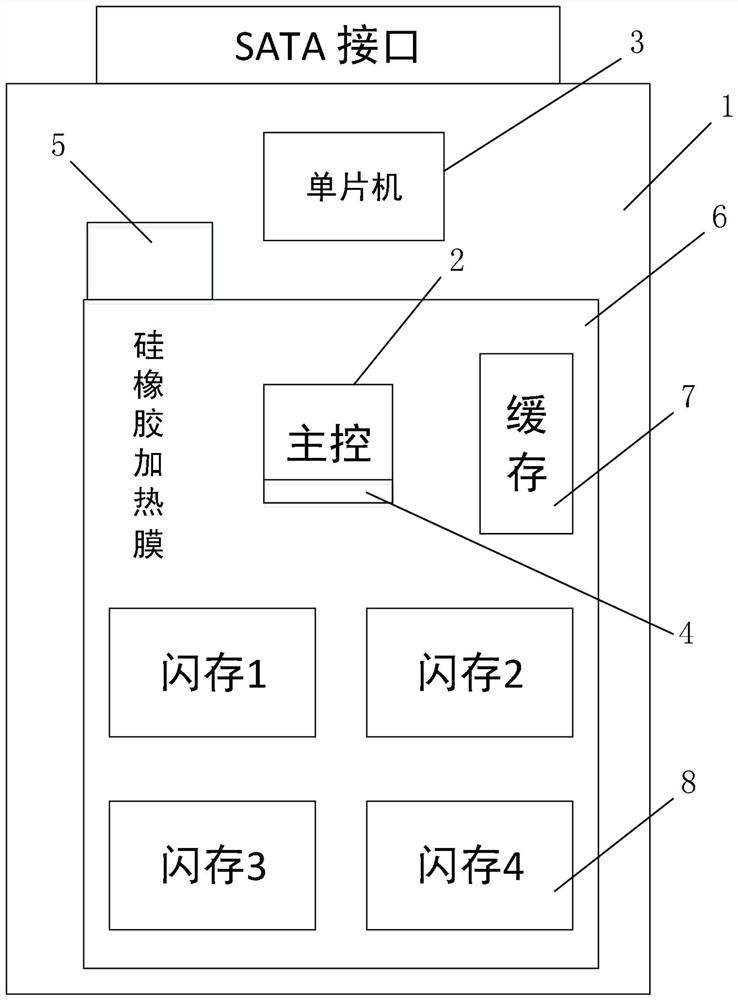

一种应用于低温环境的温控式固态硬盘及温控方法

本发明公开了一种应用于低温环境的温控式固态硬盘,其包括有壳体,壳体内设有主板,主板上设有主控单元、单片机和加热控制电路,主控单元内置有温度传感器,主控单元的表面贴合有电热器件,主控单元通过温度传感器采集环境温度,并且当环境温度低于预设温度值时,向单片机发送一上电信号,单片机根据上电信号向加热控制电路发送加热指令,借由加热控制电路控制电热器件上电加热,直至温度传感器采集的环境温度高于预设温度值时,主控单元向单片机发送一掉电信号,单片机根据掉电信号向加热控制电路发送停止指令,借由加热控制电路控制电热器件停止加热。本发明能自动实现温度控制、加热效率高、能够在低温环境下稳定运行。

2023-08-21 -

一种双端口SRAM存储单元及其版图结构

一种双端口SRAM存储单元,包括第一至第四NMOS;第一、第二NMOS的栅极与第三、第四NMOS的漏极共同连接字线;第一NMOS的源极连接第一位线;第三NMOS的源极连接第四位线;第二NMOS的源极连接第三位线;第四NMOS的源极连接第二位线;设有输入节点Q和输出节点Qb的锁存器;第一NMOS的漏极、第三NMOS的栅极共同连接至锁存器的输入节点Q;第二NMOS的漏极、第四NMOS的栅极共同连接至锁存器的输出节点Qb。本发明在不改变传统SRAM单元长宽尺寸的情况下,通过八颗晶体管的再排布,显著改善双端口SRAM存储单元的对称性,有效提高读写速度以及读干扰窗口,而且与传统工艺兼容。由于双端口SRAM广泛应用于CPU一级高速缓冲器,对于其速度要求更高,所以本发明具有其现实意义。

2023-08-21 -

一种利用磁畴壁钉扎的自旋转移力矩存储器

本发明属于半导体的技术领域,公开了一种利用磁畴壁钉扎的自旋转移力矩存储器,自上而下包括钉扎层、势垒层和自由层,在所述钉扎层的顶面、自由层的底面分别设置有读操作电极,在所述自由层的左右两端均设置有写操作连接区域,所述写操作连接区域具有钉扎效应,用于存储器写操作时的电连接,所述自由层的磁畴壁左右两侧的磁畴方向相反,且位于左端的写操作连接区域与磁畴壁左侧的磁畴方向一致,位于右端的写操作连接区域与磁畴壁右侧的磁畴方向一致。整体结构简单,效率高,适应性强,极具应用前景。

2023-08-21 -

一种数据盒载具

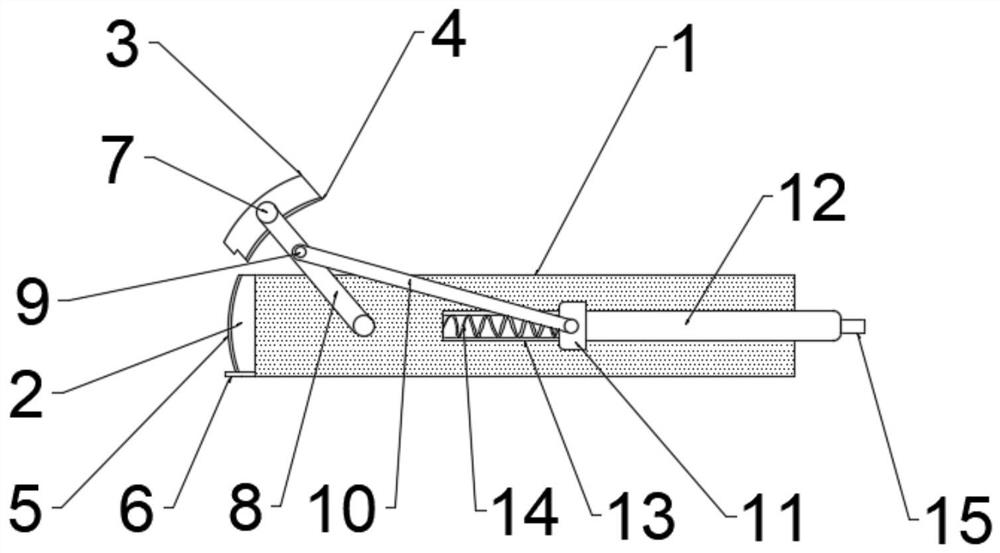

本发明公开了一种数据盒载具,属于数据盒技术领域,本发明包括载具盒、接头挡板、滑盖、摆臂、连接杆和U型滑块,其中用于保护数据线接头的接头挡板安装在载具盒的左侧,接头挡板与载具盒固定连接,载具盒侧壁上设置有摆臂,摆臂上方安装有用于密封接头挡板的滑盖,滑盖通过摆臂与载具盒活动连接,摆臂右侧设置有连接杆,连接杆与摆臂活动连接,连接杆右侧设置有U型滑块,摆臂通过连接杆与U型滑块间接连接。本发明通过可绕轴旋转的滑盖和其运动连接组件,拉动拉环即可打开载具盒的接头保护盖,松手后复位弹簧就会自动将滑盖卡进接头挡板的滑槽中,完成对载具盒的密封,有效防止水汽和灰尘对载具盒的接头造成腐蚀污染,影响载具盒的使用寿命。

2023-08-21 -

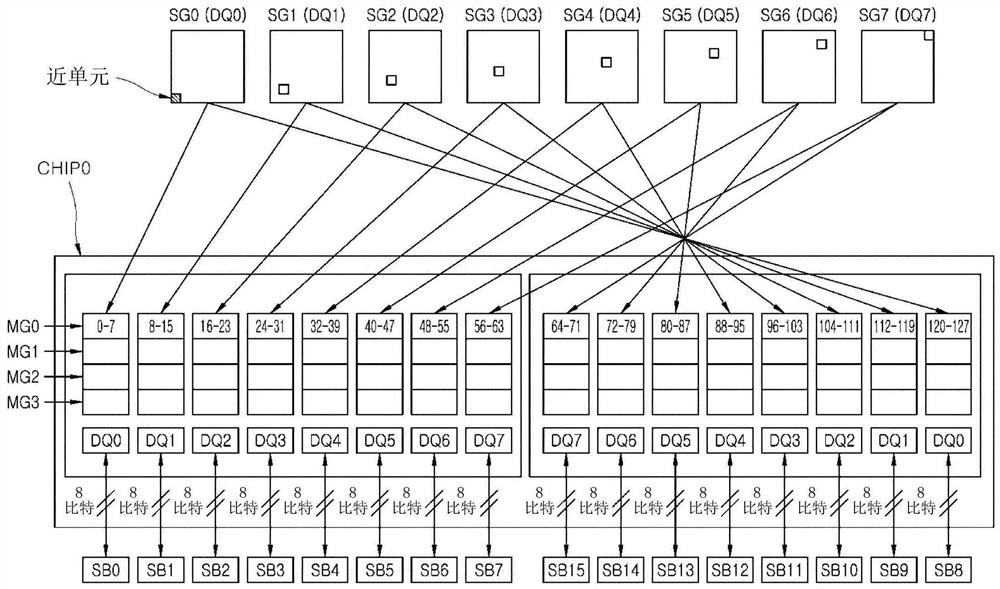

具有可配置裸片加电延迟的存储器

本文中揭示具有可配置裸片加电延迟的存储器装置及系统及相关联方法。在一个实施例中,存储器系统包含两个或两个以上存储器裸片。至少一个存储器裸片具有加电群组端子及加电群组检测电路系统。所述加电群组检测电路系统经配置以检测指派到所述至少一个存储器裸片的加电群组。所述至少一个存储器裸片经配置以使其加电操作延迟对应于其被指派到的所述加电群组的时间延迟。以此方式,所述两个或两个以上存储器裸片的加电操作可经错开以减少所述存储器系统的峰值电流需求。

2023-08-21 -

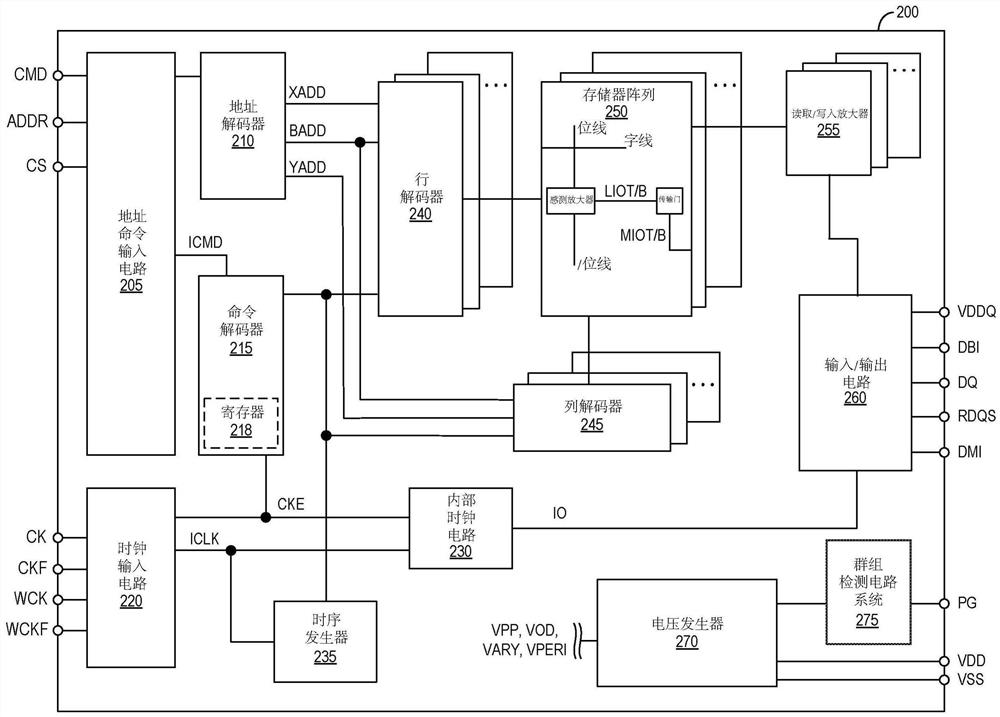

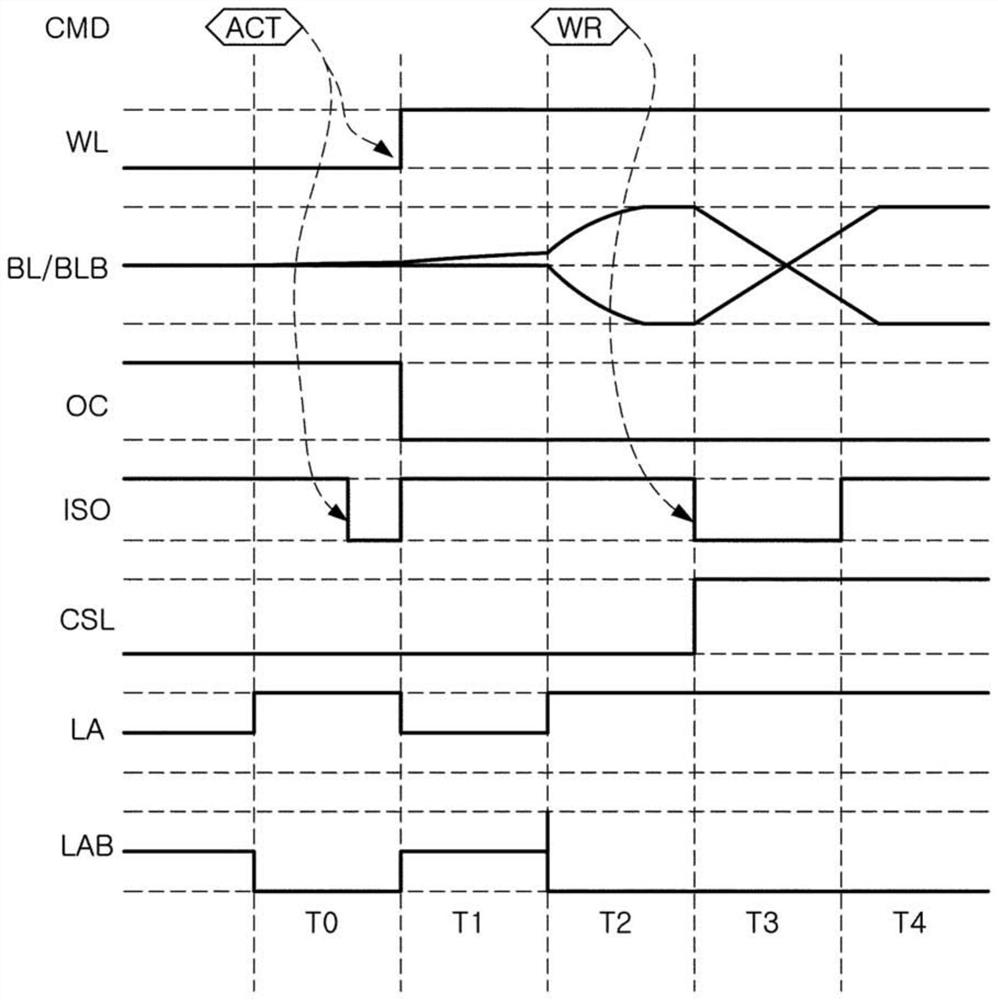

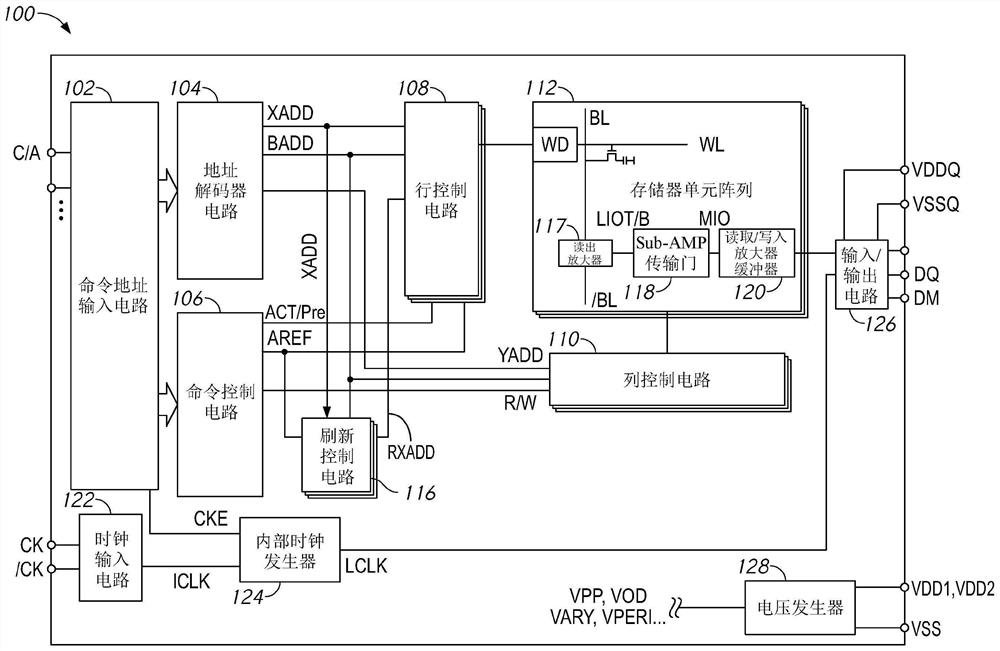

半导体存储器设备及其操作方法

提供了一种半导体存储器设备及其操作方法。半导体存储器设备包括连接一对位线的多个存储器单元、列选择电路和读出放大器。当半导体存储器设备处于数据写入操作时,列选择电路在相继布置的第一时间间隔和第二时间间隔期间将一对数据输入输出线电连接到一对位线,并且读出放大器在第一时间间隔期间与一对位线电断开,并且在第二时间间隔期间感测并放大一对位线之间的电压差。

2023-08-21 -

用于调整受害者数据的设备和方法

本申请涉及用于调节受害者数据的设备和方法。存储被存取字线的地址。还存储与和所述被存取字线相关联的受害者字线有关的数据。所述受害者字线可以具有关于多条被存取字线存储的数据。在目标刷新操作或自动刷新操作期间刷新所述受害者字线时,对与所述受害者字线有关的所述数据进行调整。在存储器存取操作期间对所述受害者字线进行存取时,对与所述受害者字线有关的所述数据进行调整。

2023-08-21 -

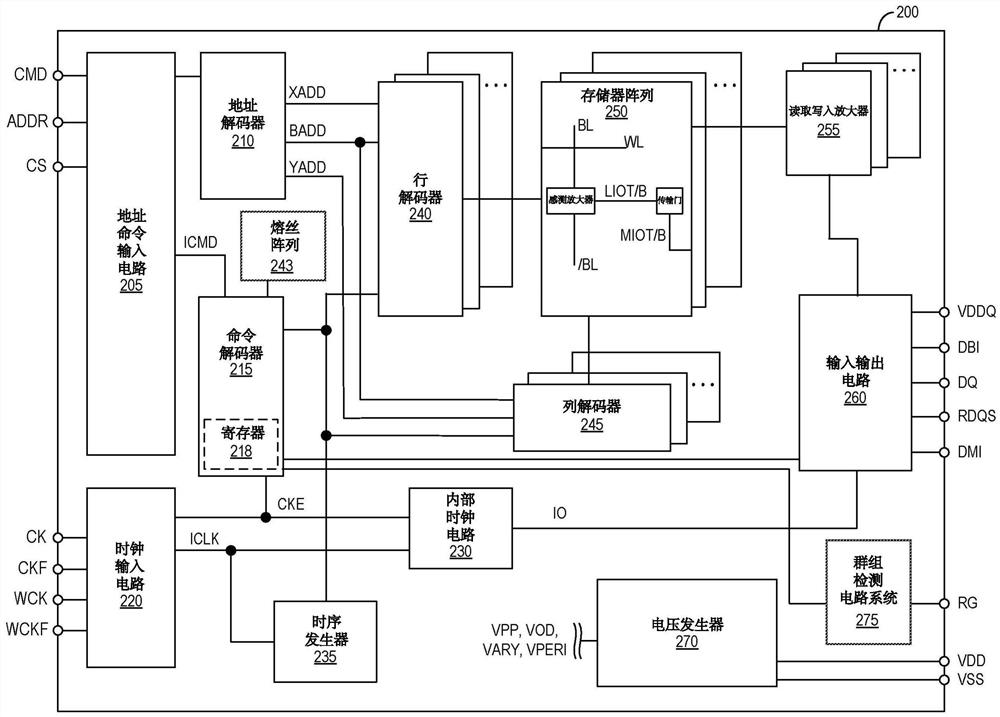

具有可编程裸片刷新错开的存储器

本申请案涉及具有可编程裸片刷新错开的存储器。本文中揭示具有可配置裸片刷新错开的存储器装置及系统及相关联方法。在一个实施例中,存储器系统包含两个或两个以上存储器裸片。至少一个存储器裸片包含熔丝阵列,其存储指定所述存储器裸片的刷新群组的刷新信息。在这些及其它实施例中,至少一个存储器裸片包含刷新群组端子及电连接到所述刷新群组端子的刷新群组检测电路系统。所述至少一个存储器裸片经配置以检测所述存储器裸片的刷新群组且使其刷新操作延迟对应于所述刷新群组的时间延迟。以此方式,所述两个或两个以上存储器裸片的刷新操作可经错开以减少所述存储器系统的峰值电流需求。

2023-08-21 -

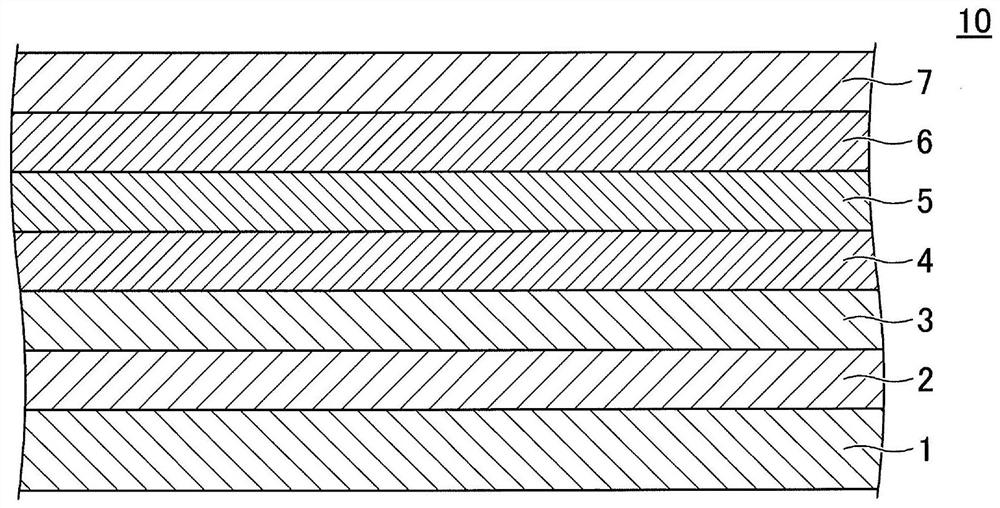

磁记录介质及其制造方法、以及磁记录再生装置

提供一种基底层和垂直磁记录层的晶体取向性较高的磁记录介质。磁记录介质(10)在非磁性衬底(1)上依次具有软磁性层(2)、第一种子层(3)、第二种子层(4)、基底层(5)、以及垂直磁记录层(6)。第一种子层(3)包含MoS、六方BN、WS、WSe或石墨。第二种子层(4)包含具有六方纤锌矿型晶体结构的AlN。基底层(5)包含Ru。

2023-08-21 -

存储器系统、存储器控制器和用于操作存储器系统的方法

本公开的各实施例涉及存储器系统、存储器控制器和用于操作存储器系统的方法。公开了存储器系统、存储器控制器和用于操作存储器系统的方法。具体地,通过基于一个或多个最佳读取电压中的第一最佳读取电压、基于一个或多个第一阈值电压区段和一个或多个第二阈值电压区段的可靠性值,以及基于第一阈值电压区段和第二阈值电压区段,针对从多个存储器单元中的一些存储器单元读取的数据执行软判决解码,从而可以提供甚至在存储数据的存储器单元的阈值电压分布退化的情况下,能够通过软判决解码来提高错误校正效果的存储器系统、存储器控制器和用于操作存储器系统的方法。

2023-08-21 -

存储系统

本发明提供一种存储系统,包括:存储介质,其包括多个矩阵和多个数据输入/输出(I/O)端子;行地址加法电路,被配置为将行地址添加值与用于访问多个矩阵的存储单元的输入行地址相加;以及列地址加法电路,被配置为将列地址添加值与用于访问多个矩阵的存储单元的输入列地址相加。多个矩阵被配置成为多个矩阵子组,其中每个矩阵子组由通过相同的数据I/O端子访问的矩阵组成。行地址添加值根据矩阵子组而彼此不同,并且列地址添加值根据矩阵子组而彼此不同。

2023-08-21 -

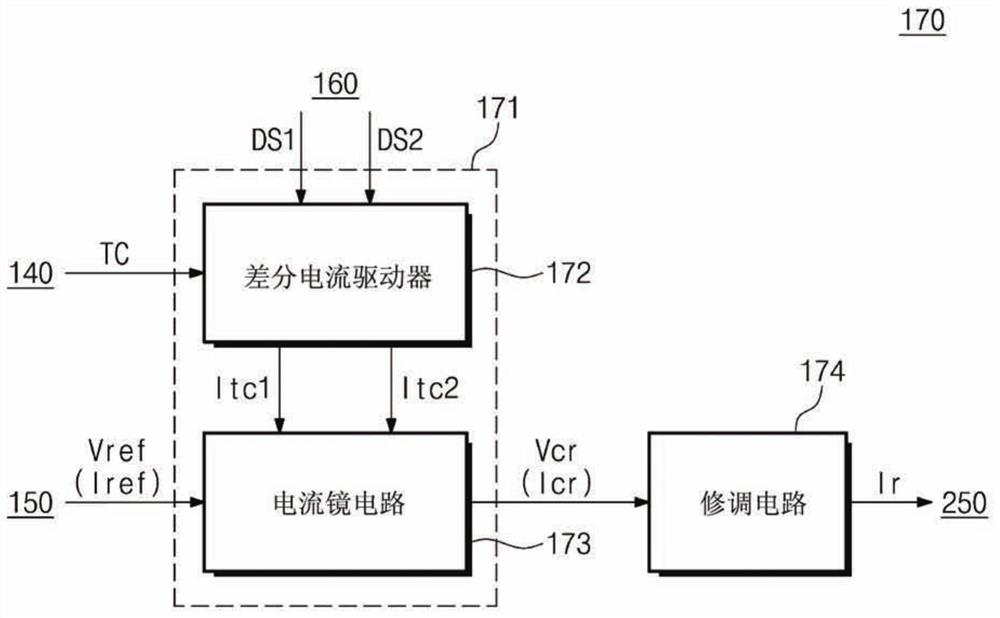

包括温度补偿电路的非易失性存储器装置

提供了一种包括温度补偿电路的非易失性存储器装置。所述非易失性存储器装置包括:差分电流驱动器,接收基于温度的第一差分信号和第二差分信号,并且生成与第一差分信号和第二差分信号之间的差值对应的第一补偿电流和第二补偿电流;电流镜电路,复制作为参考电流与第一补偿电流之和的第一电流,以生成具有与第一电流的值相同的值的第二电流,并且根据第二电流与第二补偿电流的差值来调节参考电流;修调电路,基于调节的参考电流来生成编程电流或读取电流。

2023-08-21