信息存储

-

一种存储芯片测试座及测试装置

本发明公开了一种存储芯片测试座,包含芯片座与芯片压件,所述的芯片压件与所述的芯片座分离设置,所述的芯片座用于容置存储芯片,所述的芯片压件用于压紧容置于所述的芯片座中的存储芯片,所述的芯片压件为多层结构,包含第一压件层、设置在所述第一压件层下部的凸出部与设置在所述第一压件层上部的第二压件层,本发明公开一种与现有技术不一样的芯片压件结构,所述的芯片压件结构可以应用在自动化存储芯片测试机台中,实现存储芯片的自动化装载与压合,本发明还包含高温测试模块,所述的高温测试环境可被自动化精准控温,解决了半导体芯片高温测试困难的问题,本发明还公开一种包含上述的存储芯片测试座的测试装置。

2023-11-16 -

一种基于电路控制的人工智能设备的唤醒自动化测试装置

本发明提供一种基于电路控制的人工智能设备的唤醒自动化测试装置,包括:耳机插头、遥控器与继电器;所述耳机插头具有第一音频线;所述遥控器具有语音按钮,用于操控人工智能设备;所述继电器的输入端与所述第一音频线连接,所述继电器的输出端与所述语音按钮的引脚连接。本发明的优点在于:耳机插头将音频输出电压发给继电器,通过继电器的触点闭合与断开,实现了遥控器的语音按钮的按下与抬起的效果,能自动触发语音按钮从而唤醒录音测试,模拟了人工操作按钮的动作,可以在无人值守的情况下完成人工智能设备的录音自动测试。

2023-11-16 -

非易失性存储器装置

提供一种非易失性存储器装置。所述非易失性存储器装置包括:存储器单元阵列,在第一半导体层中并且包括连接到第一字线和第一位线的第一存储器单元和连接到第一字线和第二位线的第二存储器单元;页缓冲器电路,在第二半导体层中并且包括连接到第一位线的第一页缓冲器和连接到第二位线的第二页缓冲器;以及页缓冲器控制器,在第二半导体层中。页缓冲器控制器控制第一页缓冲器和第二页缓冲器,使得第一页缓冲器的第一感测节点的发展时序与第二页缓冲器的第二感测节点的发展时序不同。第一页缓冲器比第二页缓冲器靠近贯穿电极区域。

2023-11-15 -

一种MLC存储器的存储单元的读取方法和读取电路

本发明公开了一种MLC存储器的存储单元的读取方法和读取电路,其中,读取方法包括:判断MLC存储器所接入的电源电压是否大于电压阈值;当电源电压大于或等于电压阈值,则执行第一读取操作以确定存储单元的数据状态;当电源电压小于电压阈值,则执行第二读取操作以确定存储单元的数据状态;根据本发明实施例可以在在现有的MLC存储器所接入的电源电压过低时,保证存储单元存储的重要数据的读取的可靠性和将存储单元存储的数据读出,因此本发明实施例较之现有技术,具有更高的灵活性。

2023-11-15 -

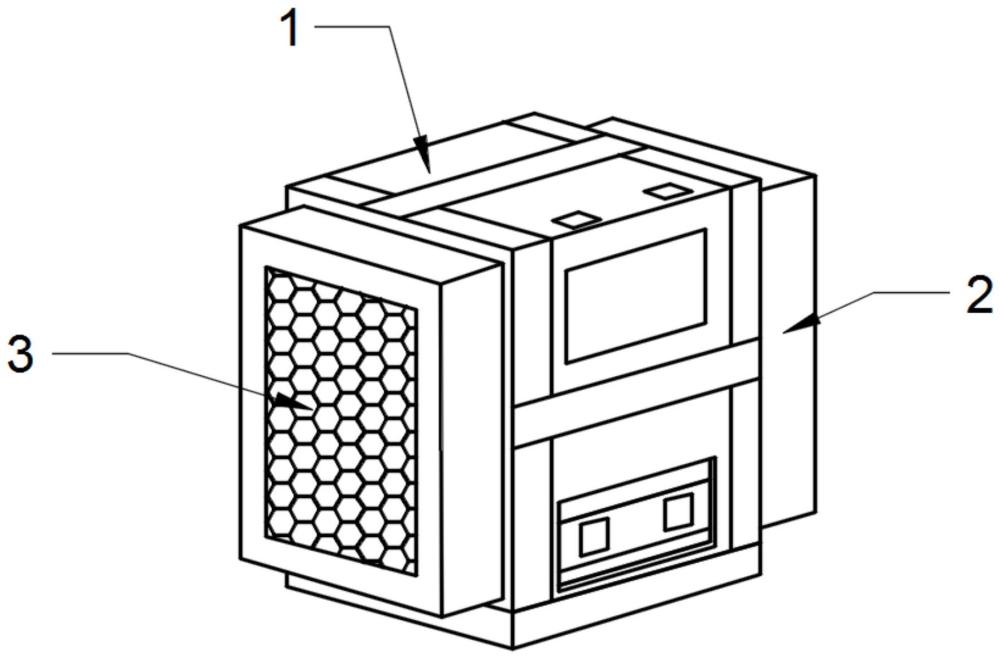

一种车载电子设备机芯的防尘罩

本发明公开了一种车载电子设备机芯的防尘罩,其结构包括防尘罩、接线板、连接块,防尘罩右侧与接线板外侧焊接连接,连接块左侧与接线板右侧焊接连接,防尘罩包括侧板、底板、过滤器、排风机,侧板外侧与底板外侧焊接连接,在空气进入时会吹动清理器进行旋转,在旋转时保护框对清理器进行保护,韧性块推动下通过固定板固定滚轮在过滤网外侧进行滚动,同时清理块会对毛发进行清理,防止毛发对过滤网造成堵塞,提高了过滤网的使用寿命,在切割过程中接触片触碰到毛发,当毛发难以切割向上滑动时弹簧收缩接触片受压向上偏转,同时摆动片跟随偏转,使得接触片与摆动片形成剪切力对毛发进行剪切,提高了清理器对毛发的清理效果。

2023-11-15 -

非易失性存储器装置及其操作方法和存储器系统

公开了非易失性存储器装置及其操作方法和存储器系统。所述非易失性存储器装置包括:存储器单元阵列,包括存储芯片级信息的元数据区域;控制逻辑,响应于命令识别目标单元;机器学习(ML)逻辑,基于作为输入被施加到人工神经网络模型的芯片级信息和与目标单元相关联的物理信息来推断最佳参数;以及缓冲存储器,被配置为存储人工神经网络模型的权重参数。

2023-11-15 -

半导体存储装置

本发明的一实施方式提供一种能够使动作高速化的半导体存储装置。一实施方式的半导体存储装置具备存储单元、位线、以及包含第1电路及锁存电路的感测放大器。第1电路包含:第1节点,能够电连接于位线,且在存储单元的读出动作中,根据存储单元的数据将电荷传输到位线;第1晶体管,栅极连接于第1节点,且该第1晶体管能够与连接于锁存电路的第2节点连接;第2晶体管,能够将第2节点与第3节点连接;及第3晶体管,栅极连接于第3节点,且该第3晶体管能够连接于第1节点。感测放大器在读出动作中,感测向位线传输电荷时的第1节点的第1电压,对第3节点施加将第1电压放大所得的第2电压,并对第1节点施加将第2电压放大所得的第3电压。

2023-11-15 -

具有页缓冲器的存储器设备

本文中提供的可以是一种具有页缓冲器的存储器设备。存储器设备可以包括被配置成存储数据的存储器单元,并且可以包括页缓冲器,页缓冲器通过位线耦合到存储器单元,并且被配置成:存储要在编程操作中被使用的数据;并且在编程操作中执行的编程验证操作期间,依赖于该数据,将位线预充电到第一预充电电压或第二预充电电压,第二预充电电压低于第一预充电电压。

2023-11-15 -

分栅存储器阵列及其操作方法

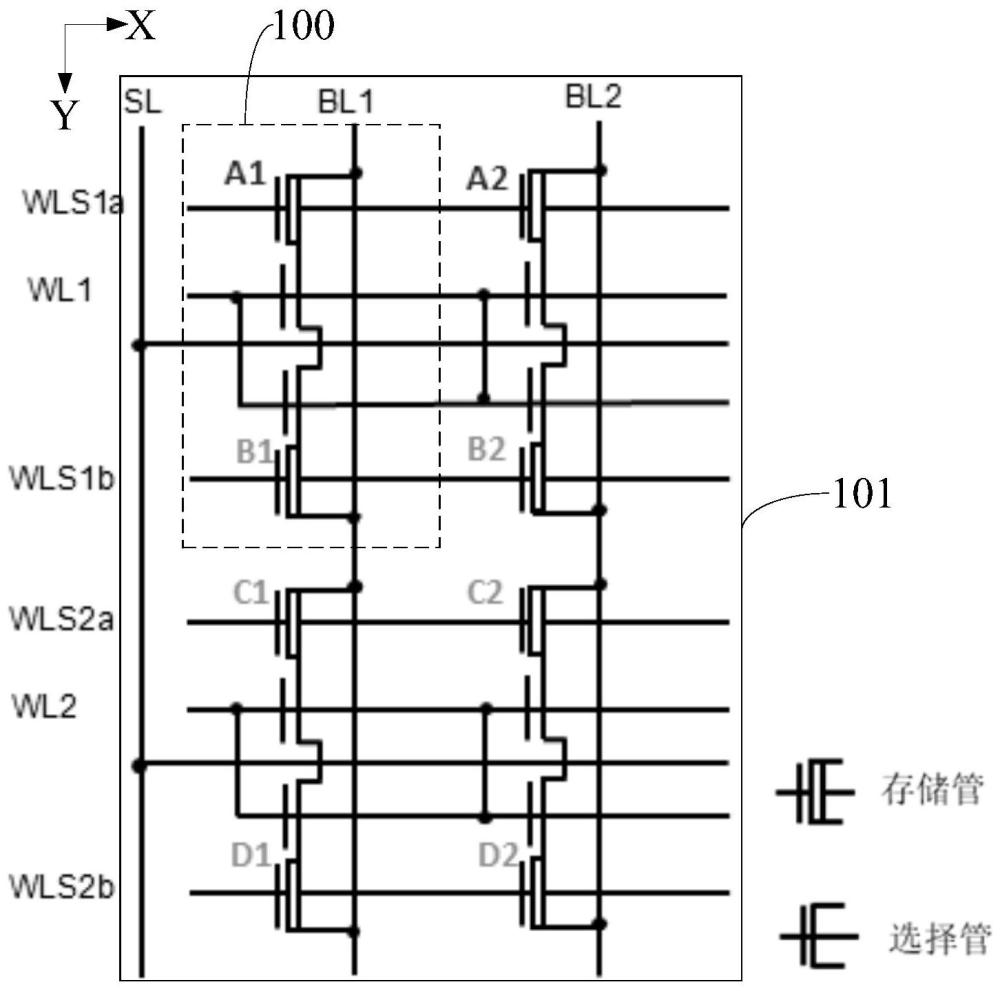

一种分栅存储器阵列及其操作方法,其中阵列包括:若干存储单元组构成的存储阵列,存储单元组包括第一存储单元和第二存储单元,第一存储单元包括分栅结构的第一存储管和第一选择管,第二存储单元包括分栅结构的第二存储管和第二选择管;位于同一行的第一存储管的栅极相连;位于同一行的第二存储管的栅极相连;位于同一行的第一选择管的栅极相连,位于同一行的第二选择管的栅极相连,共接的第一选择管和第二选择管栅极相连;位于同一列的第一存储管和第二存储管的漏极相连。由于选择管与存储管之间为分栅结构,相邻的选择管栅极共接,减少了外接孔的数量;且位于同一列的第一存储管和第二存储管的漏极相以一条位线接出,有效缩减了存储单元的面积。

2023-11-14 -

一种按压式硬盘盒

本发明提供了一种按压式硬盘盒,其特征在于,包括相对两端开口且由分隔板分成第一容腔和第二容腔的外壳,和放置于所述第一容腔内的中框,及放置于所述第二容腔内的收线壳,所述收线壳与外壳卡扣固定,所述第一容腔的内侧壁设有第一凹槽,所述中框上设有与第一凹槽卡合的弹性机构,弹性机构包括按压板、固定板、滑板,按压弹性机构可使中框从外壳中滑出。本发明设计的硬盘盒拾取硬盘方便,结构稳定。

2023-11-14 -

一种基于单Die读重试的纠错调度方法

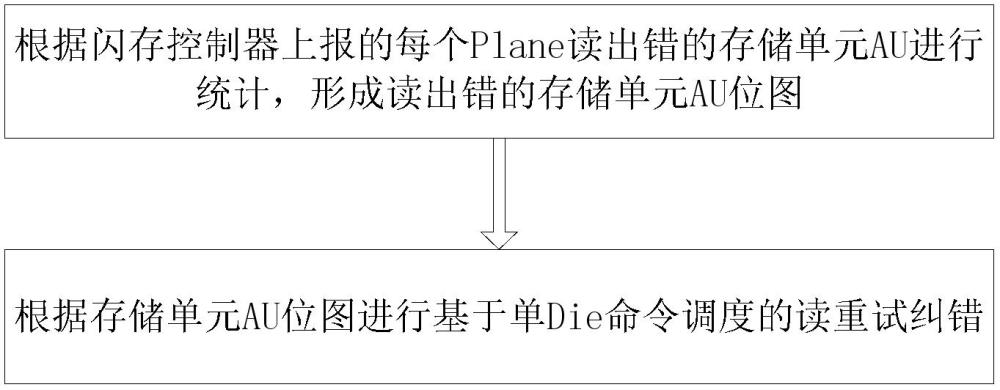

本发明公开了一种基于单Die读重试的纠错调度方法,该方法包括以下步骤:1)主机多Plane读出错后,对闪存控制器上报的每个Plane读出错的存储单元AU进行统计,形成读出错的存储单元AU位图;其中,存储单元AU位图是同一个Die中每个Plane所在的page页上4个存储单元AU的分布图,读出错的存储单元AU位图通过将读出错的存储单元AU在存储单元AU位图进行标记形成;2)根据存储单元AU位图进行基于单Die命令调度的读重试纠错。本发明方法通过设置读出错的存储单元AU位图,可以有效缩短读重试纠错方法时间,提升纠错效率。

2023-11-13 -

用于字线开关晶体管的具有多个阱的非易失性存储器

非易失性存储器包括非易失性存储器阵列,该非易失性存储器阵列包括非易失性存储器单元的块、连接到该存储器单元的位线和连接到该存储器单元的字线。字线开关晶体管将该字线连接到电压源。该字线开关晶体管位于三阱中。利用多个三阱,并且基于在编程过程期间使用的字线电压范围将该字线开关晶体管分组到三阱中。在一个实施方案中,对于给定块,连接到数据字线的字线开关晶体管位于第一三阱中,并且连接到选择及虚设字线的字线开关晶体管位于第二三阱中。这种结构允许这些三阱被不同地偏置。

2023-11-10 -

flash芯片的擦除方法、装置及flash芯片

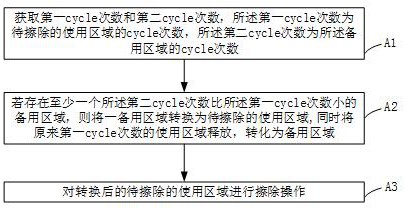

本申请公开了一种flash芯片的擦除方法、装置及flash芯片,属于半导体集成电路技术领域,其中所述擦除方法包括以下步骤:获取第一cycle次数和第二cycle次数,所述第一cycle次数为待擦除的使用区域的cycle次数,所述第二cycle次数为所述备用区域的cycle次数;若存在一所述第二cycle次数比所述第一cycle次数小的备用区域,则将该备用区域转换为待擦除的使用区域;对待擦除的使用区域进行擦除操作。本申请的擦除方法,能解决芯片中边角容量被浪费的问题,从而能有效利用边角容量以延长芯片的使用寿命。

2023-11-10 -

非挥发性锁存器

本发明提供一种非挥发性锁存器,该非挥发性锁存器包括:控制电路,所述控制电路的第一端用于接入工作电源,且包括串联的第一开关和第二开关;忆阻器,所述忆阻器的第一极与位于所述第一开关与所述第二开关之间的接入节点相连;反相器,所述反相器的输入端与所述接入节点相连,所述反相器的输出端与所述忆阻器的第二极相连。本发明的非挥发性锁存器,不依赖稳定的外接电源,可以同时实现锁存和非挥发性存储,并可适用于部分供电不稳定的场合。

2023-11-09 -

用于动态分配的侵害者检测的设备和方法

用于动态分配的侵害者检测的设备、系统和方法。存储器可包含跟踪对行地址及其相关联排组地址的存取模式的侵害者地址存储结构。这些可用以确定作为存取操作的部分所接收的行和排组地址是否为侵害者行和排组地址。所述侵害者行地址可用以产生用于由所述侵害者排组地址识别的排组的刷新地址。由于所述侵害者存储结构跟踪行地址和排组地址,因此其存储空间可基于对那些排组的存取模式而在排组之间动态分配。

2023-11-09 -

双轨式电源切断系统及方法

提供用于控制集成双轨式存储电路电源切断的系统及方法。电源切断系统被配置成在维持对存储胞元(VDDM)的电源轨通电的同时使输入及逻辑组件(VDD)的电源轨断电。所述断电系统包括两个电压轨、时钟产生器及用于检测VDD上的功率的功率检测器。当VDD上的电压低于电压阈值时,功率检测器产生隔离功率信号。隔离功率信号被配置成禁用时钟产生器,且因此在断电期间不触发读取/写入循环,降低了动态功率。

2023-11-09 -

半导体器件的深阱电压的控制方法

本发明提供一种半导体器件的深阱电压的控制方法,所述半导体器件包括第一衬底、设置在第一衬底上的第一阱及设置在所述第一阱上的第二阱,所述控制方法包括:当对所述第二阱施加负电压时,降低所述第一阱的电压。本发明的优点是,通过降低第一阱电压的方式减小半导体器件的第二阱和第一阱之间的寄生电容,进而减小寄生电容消耗的电流,提高电路性能。

2023-11-08 -

一种降低IR Drop的存算阵列折叠布局方法

本发明公开了一种降低IR Drop的存算阵列折叠布局方法,存算阵列包括m行存算单元与n列存算单元;字线端WL至WL分别连接至1至m行的存算单元,位线BL端BL至BL分别连接至1至n列的存算单元,源线端SL至SL分别连接至1至n列存算单元的源端,所述方法包括:步骤一:将m×n的存算阵列在字线端WL处沿字线WL方向切断;步骤二:将相同的位线BL与相同的源线SL进行跨线连接;步骤三:将跨线连接的两个m/2×n的存算阵列交叉合并;步骤四:将字线WL端的WL至WL由阵列一侧引出,字线WL端WL至WL由阵列另一侧引出。

2023-11-08 -

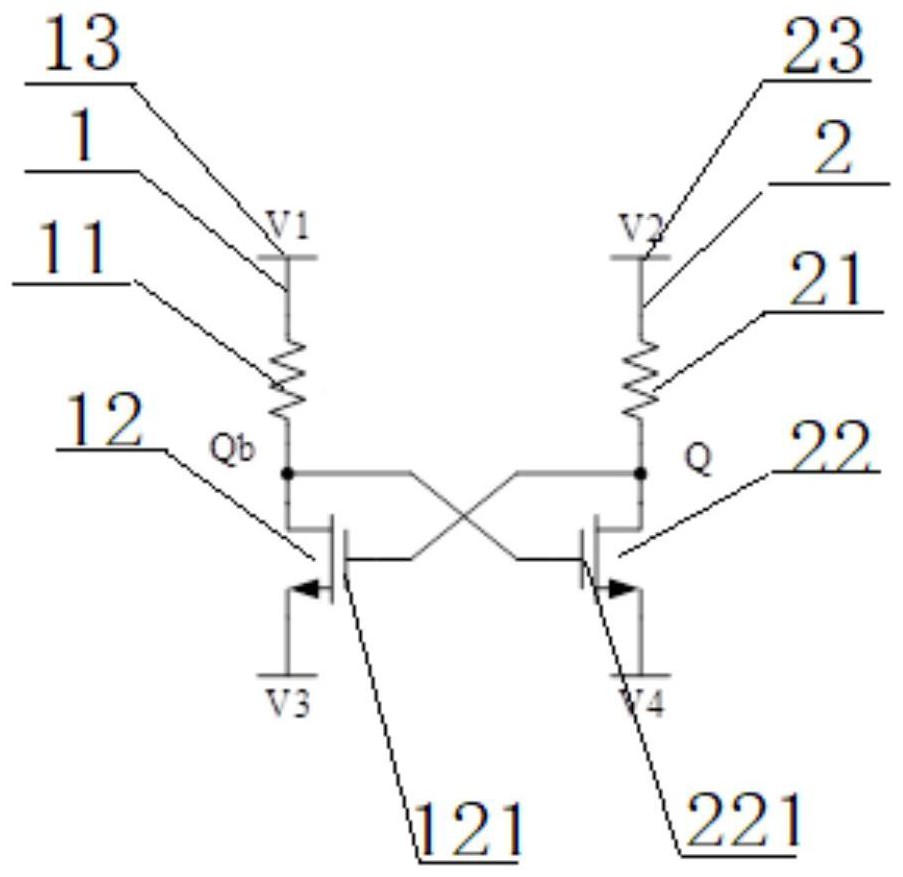

一种基于阈值型忆阻器的锁存器

本发明涉及一种基于阈值型忆阻器的锁存器,包括:输入端口、第一输出端口、第二输出端口和锁存电路;锁存电路,包括阈值型忆阻器,用于在时钟控制信号有效的情况下,控制第一输出端口和第二输出端口的接入信号随着输入信号的电平信息变动,并将输入信号的电平信息存储到阈值型忆阻器上;还用于在时钟控制信号无效的情况下,基于阈值型忆阻器存储的输入信号的电平信息,控制第一输出端口和第二输出端口的接入信号与最近一次接入信号一致。本发明锁存器的设计结合了阈值型忆阻器的阻变特性和非挥发性特性,功耗小、具备存算一体的能力,在外接偏置电源关闭的情况下不会丢失电平信息。

2023-11-07 -

自动拷贝机

本公开涉及拷贝设备领域,尤其涉及一种用于固态硬盘的自动拷贝机,该自动拷贝机包括供料及收料模组、机械手臂模组和制造执行系统;供料及收料模组包括传输带,传输带上沿传输方向依次设置取料区、缓冲区和合格品收料区,且取料区、缓冲区和合格品收料区分别设有托盘;机械手臂模组包括机械手臂和第一扫描组件,第一扫描组件设于机械手臂的抓取端,并用于扫描固态硬盘的工单/批次信息;制造执行系统用于接收固态硬盘的工单/批次信息,并匹配测试软体图像。本公开实施例提供的一种自动拷贝机,固态硬盘的拷贝操作自动完成,可避免因人工操作而导致的静电、损伤、工单/批次匹配错误、拷贝后产品不易区分、以及拷贝效率低等问题。

2023-11-07 -

非易失性三维存储器、存储系统及其读取方法

本申请提供一种非易失性三维存储器、存储系统及其读取方法,非易失性三维存储器包括多个存储单元串,每个存储单元串包括多个存储单元和漏极选择栅极晶体管,读取方法包括:在所述非易失性三维存储器的空闲阶段之后,根据接收的n次读取命令,对选定存储单元串包括的选定存储单元执行n次读取操作,n≥2且为正整数,其中,在执行n次读取操作期间,控制未选定存储单元串的漏极选择栅极晶体管在第一次读取操作的预脉冲恢复阶段从导通到关断的时间比在其余n‑1次读取操作的任一预脉冲恢复阶段从导通到关断的时间长,从而能够改善存储单元阈值电压的偏移,降低第一次读取的失败比特币数。

2023-11-02 -

存储器电路及其操作方法

本公开涉及存储器电路及其操作方法。一种存储器电路,包括:NAND逻辑门、第一N型晶体管、第二N型晶体管、第一反相器和第一锁存器。NAND逻辑门被配置为接收第一位线信号和第二位线信号,并且生成第一信号。第一N型晶体管耦合至NAND逻辑门,并且被配置为接收第一预充电信号。第二N型晶体管耦合至第一N型晶体管和参考电压源,并且被配置为接收第一时钟信号。第一反相器耦合至NAND逻辑门,并且被配置为输出从第一信号反相的数据信号。第一锁存器耦合至NAND逻辑门,并且被配置为响应于至少第一时钟信号或第一预充电信号而锁存第一信号。

2023-11-02 -

基于声波驱动的多种香薰切换释放的音频播放器

本发明公开了基于声波驱动的多种香薰切换释放的音频播放器,包括外壳、固定设置于外壳内的喇叭及香薰组件;香薰组件包括风扇、震动片及驱动机构,风扇固定安装于风扇支板上,风扇支板与外壳的内壁固定连接;震动片固定设置于喇叭上,驱动机构设置于震动片上侧;风扇的出风方向设有中空腔体的出风筒,出风筒贯穿于外壳的上端面。上述的音频播放器,驱动机构吸附固定多个香薰盒,可使任一香薰盒脱离驱动机构并沿震动片滑入中空腔体内,通过喇叭的声波驱动香薰盒释放香薰,风扇吹风以将香薰由出风筒排出,在通过喇叭播放音频的同时可切换释放各种不同香薰,提升了音频播放器的实用性及使用功能。

2023-10-20 -

一种数据接收器、芯片以及数据处理方法

本申请公开了一种数据接收器、芯片以及数据处理方法,该数据接收器包括:第一接收电路接收输入信号与参考信号,对输入信号与参考信号的差值信号进行放大及转换处理,以输出第一输出信号;第二接收电路接收输入信号与参考信号,对输入信号与参考信号的差值信号进行放大及转换处理,以输出第二输出信号;源极跟随器电路连接第一接收电路,用于调整第一输出信号以使第一输出信号匹配第二输出信号;或者连接第二接收电路,用于调整第二输出信号以使第二输出信号匹配第一输出信号。本申请通过设置与第一接收电路或第二接收电路连接的源极跟随器电路,以使第一接收电路和第二接收电路复用同一功能性电路,简化电路结构,减小数据接收器面积,降低成本。

2023-10-17 -

DRAM数据存储拓扑的探测方法及探测装置

本申请公开了一种DRAM数据存储拓扑的探测方法及探测装置。该DRAM数据存储拓扑的探测方法包括:在DRAM中的存储单元中写入外部逻辑数据;基于存储单元的内部物理数据与外部逻辑数据确定存储单元的数据存储拓扑类型,内部物理数据是外部逻辑数据写入存储单元后得到的。通过这种方式,能够准确且快速的探测DRAM存储阵列的各个存储单元的数据存储拓扑。

2023-10-17 -

具有用于支撑带卷轴对的可移除安装件的多卷轴带记录装置

一种装置包括被配置为接收多个安装件的接收区域,每个安装件被配置为在其上支撑至少一个带卷轴对。磁头被配置为对带卷轴对的磁记录带执行数据操作。定位机构被配置为选择性地将磁头对准带卷轴对中的选择的一个带卷轴对。根据另一方法的产品装置包括其上具有带卷轴对的安装件。安装件被配置为插入到被配置为接收多个安装件的装置的接收区域中。

2023-10-15 -

存储器装置的块族的基于时间的组合

本申请涉及存储器装置的块族的基于时间的组合。一种实例存储器子系统包含:存储器装置;以及处理装置,其可操作地耦合到所述存储器装置。所述处理装置配置成确定所述存储器装置的多个块族中的第一块族和所述多个块族中的第二块族符合接近度条件;确定所述第一块族和所述第二块族是否满足与所述接近度条件相对应的基于时间的组合准则;以及响应于确定所述第一块族和所述第二块族满足所述基于时间的组合准则,合并所述第一块族和所述第二块族。

2023-10-14 -

非易失性存储设备和对非易失性存储设备进行编程的方法

一种用于对非易失性存储设备中包括的多个存储单元中的至少一个存储单元进行编程的方法,至少一个存储单元包括字线和位线,该方法包括:分别基于第一条件和第二条件执行第一编程和验证操作以及第二编程和验证操作,其中,每个编程和验证操作包括:由非易失性存储设备中包括的电压生成器生成编程电压和位线电压;以及分别向字线和位线提供编程电压和位线电压,其中,编程电压和位线电压各自的电压电平和电压施加时间分别与第一条件或第二条件相对应,其中,第一条件不同于第二条件。

2023-10-14 -

用于存储器地址区的激活和去激活的增强

本申请涉及一种用于存储器地址区的激活和去激活的增强。在一些实例中,一种存储器装置可包含:第一高速缓存,其用于存储所述存储器装置的逻辑地址与物理地址之间的映射;以及第二高速缓存,其用于存储与从所述第一高速缓存移除的条目相关联的索引。所述存储器装置可包含被配置成在接收到读取命令后将映射加载到所述第一高速缓存的控制器。当所述第一高速缓存满了时,并且当所述存储器装置接收到读取命令时,所述控制器可从所述第一高速缓存移除条目并且可将与所移除条目相关联的索引存储到所述第二高速缓存。所述控制器接着可将与所述索引相关联的映射传输到主机装置以供在HPB操作中使用。

2023-10-14 -

半导体芯片及其预烧测试方法

本公开提供一种半导体芯片及其预烧测试方法。另本公开执行一种预测试,预测试在预烧测试之前的预测试阶段期间检查插口的每一电接触件与半导体芯片的对应引脚之间的电连接。每一个电接触件与每一个引脚之间的电连接通过多个信号通道来检查。即使在信号通道中的一个失效时,只要信号通道中的另一个通过预测试,就仍可执行预测试和预烧测试。另外,通过多个信号通道的预测试阶段还提供信息,以用于确定半导体芯片的失效是否由预烧板的插口之间的电连接或由半导体芯片自身所导致。

2023-10-14 -

易失性存储器装置及其操作方法以及存储装置

本发明提供了一种易失性存储器装置以及操作方法。该易失性存储器装置包括:多个存储器单元,按行和列布置并且结构设计成存储数据;字线;位线;行解码器;列解码器;以及控制逻辑,联接成与行解码器和列解码器通信,并且被配置成在激活时段中,向行解码器提供第一命令并且向列解码器提供第二命令,其中行解码器进一步被配置成:从提供第一命令时起,将高于接地电压的第一字线电压施加到选择的字线;并且在行解码器被激活的持续时间内,将低于第一字线电压的第二字线电压施加到选择的字线或不对选择的字线施加电压。

2023-10-14 -

用于确定读取阈值电压的变化的系统和方法

本申请涉及一种存储器系统,该存储器系统包括存储器装置和控制器。控制器基于与读取操作相关联的失败位计数、解码器的错误校正能力和解码器中队列的利用率,确定除了作为先前成功的读取操作中使用的读取阈值电压的历史读取阈值电压之外的读取阈值电压是否将用于下一次读取操作。当确定历史读取阈值电压不用于下一次读取操作时,控制器确定与使用读取阈值电压对存储器装置的存储器单元的读取操作相关联的失败位计数;控制器基于失败位计数确定最佳读取阈值电压。控制器将包括与设置最佳读取阈值电压相关联的参数的第一命令传输到存储器装置。

2023-10-14 -

存储器系统及其操作方法

本公开的实施例提供了一种存储器系统及其操作方法。存储器系统包括存储器装置和存储器控制器。存储器控制器被配置成:创建坏存储器区域替换表,该坏存储器区域替换表包括多个存储器区域之中的坏存储器区域的状态信息;当出现一个或多个运行时间坏存储器区域时,将一个或多个运行时间坏存储器区域的状态信息添加到坏存储器区域替换表中;以及基于坏存储器区域替换表,将目标坏存储器区域中包括的坏子区域重新映射到被添加到坏存储器区域替换表中的坏存储器区域之中除了目标坏存储器区域之外的剩余坏存储器区域的一个中包括的正常子区域。

2023-10-14 -

采用放大器反馈进行阻抗匹配的数据存储设备

本发明公开了一种数据存储设备,该数据存储设备包括在磁介质上致动的磁头,其中磁头包括被配置成在从磁介质读取数据时生成读取信号的读取元件。共源共栅(CS‑CG)差分放大器通过具有传输线阻抗Z0的传输线耦接到读取元件。反馈电路耦接在CS‑CG差分放大器的输出与CS‑CG差分放大器的输入之间,其中反馈电路被配置成使得CS‑CG差分放大器的输入阻抗基本上匹配传输线阻抗Z0。

2023-10-14 -

一种用于闪存芯片的自动化测试设备及其测试方法

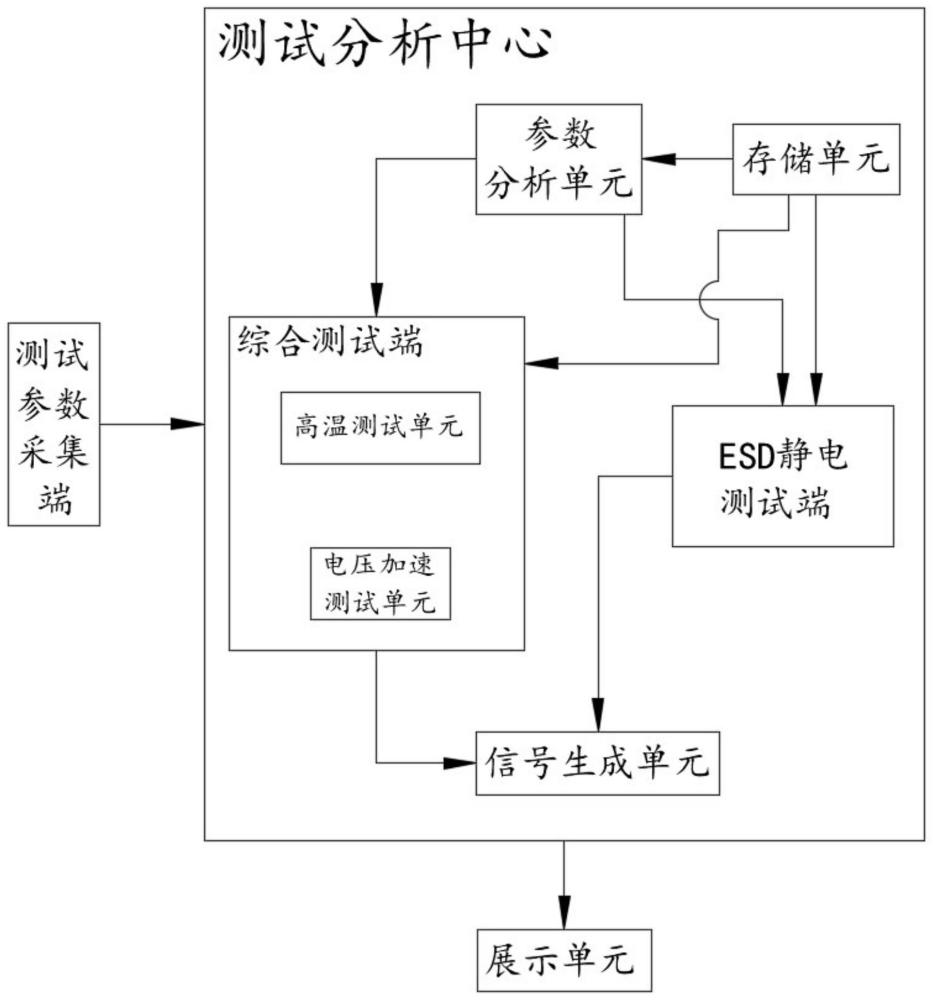

本发明公开了一种用于闪存芯片的自动化测试设备及其测试方法,涉及芯片测试技术领域,解决了对于处于正常状态下的闪存芯片,并未进行多方面分析,并不清楚此闪存芯片的可靠度,其整体测试并不全面的技术问题,根据具体的参数,将闪存芯片划分为正常芯片或异常芯片,针对于正常芯片,对其进行高温以及电压加速测试,并根据测试数值,判定正常芯片在使用过程中,是否存在不可靠情况,并进行展示,采用此种行驶,将正常芯片进行多方面测试,提升芯片测试的全面性以及准确度,对异常芯片进行极限测试,确定异常芯片的输出参数,并分析此参数是否符合规定,根据测试结果,判定异常芯片是否处于故障状态,提升异常芯片的全面度。

2023-10-08 -

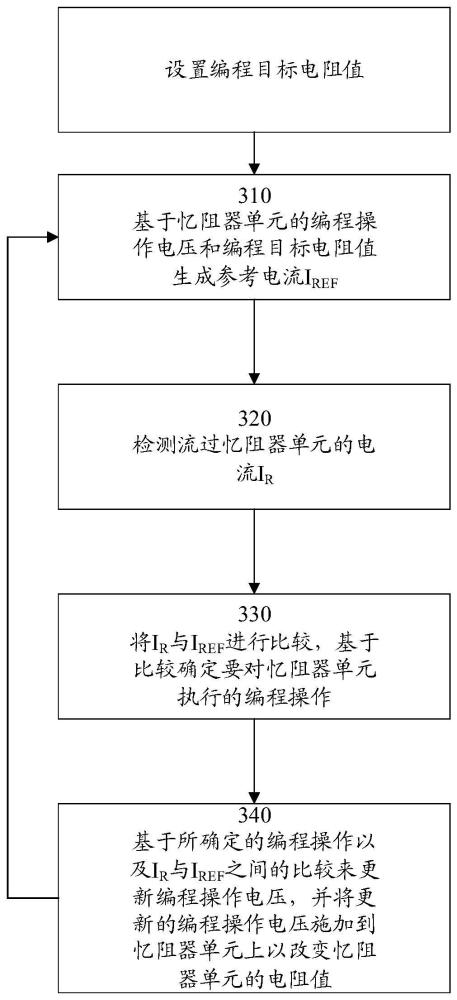

用于忆阻器单元编程的方法和装置

本公开提供用于忆阻器单元编程的方法,方法包括执行至少一个编程循环,其中,每个编程循环包括:基于用于忆阻器单元的编程操作电压和编程目标电阻值生成参考电流,其中,编程操作电压是要用于置位或复位忆阻器单元的操作电压;检测被施加编程操作电压的忆阻器单元的第一电流;基于要对忆阻器单元执行的编程操作以及第一电流与参考电流之间的比较,更新编程操作电压,并对忆阻器单元施加更新的编程操作电压以对忆阻器单元进行编程以改变忆阻器单元的阻值。本公开还提供了对应于上述编程方法的装置。本公开所提供的用于忆阻器单元编程的方法和装置避免了忆阻器单元在编程状态和校验状态之间的切换和过操作现象的发生,提升了编程的效率。

2023-10-07 -

半导体设备

本公开涉及一种半导体设备,该半导体设备包括第一数据线、第二数据线以及连接到第一数据线和第二数据线的存储器单元。存储器单元包括多个开关、第一数据保持电路、第二数据保持电路、第三数据保持电路、第四数据保持电路和输入线。通过基于由第三数据保持电路保持的值来控制多个开关之中的连接到第一数据线的开关,以及通过基于由第四数据保持电路保持的值来控制多个开关之中的连接到第二数据线的开关,存储器单元的特性值可改变。

2023-10-06 -

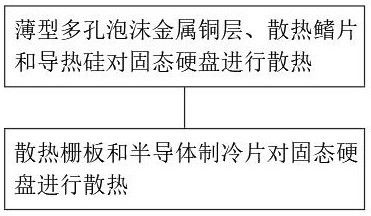

固态硬盘的读写接口及接口散热方法

本发明公开了固态硬盘的读写接口及接口散热方法,固态硬盘通过读写接口与目标主板连接,读写接口为M.2接口,M.2接口具有信号输出端,用于输出信号,并基于所输出的信号,进行对应的通信协议的切换,使得切换后的通信协议与当前接入的M.2接口的硬盘相匹配,M.2接口通过模拟开关连接至中央处理器,M.2接口还包括用于对其进行散热的散热组件,散热组件包括:薄型多孔泡沫金属铜层、散热鳍片、导热硅脂、散热栅板和半导体制冷片,散热方法包括:薄型多孔泡沫金属铜层、散热鳍片和导热硅脂为一组散热组件,其通过导热胶水粘合在固态硬盘的一面上;散热栅板和半导体制冷片为第二组散热组件,其通过导热胶水固定粘合在固态硬盘的另一面上。

2023-10-04 -

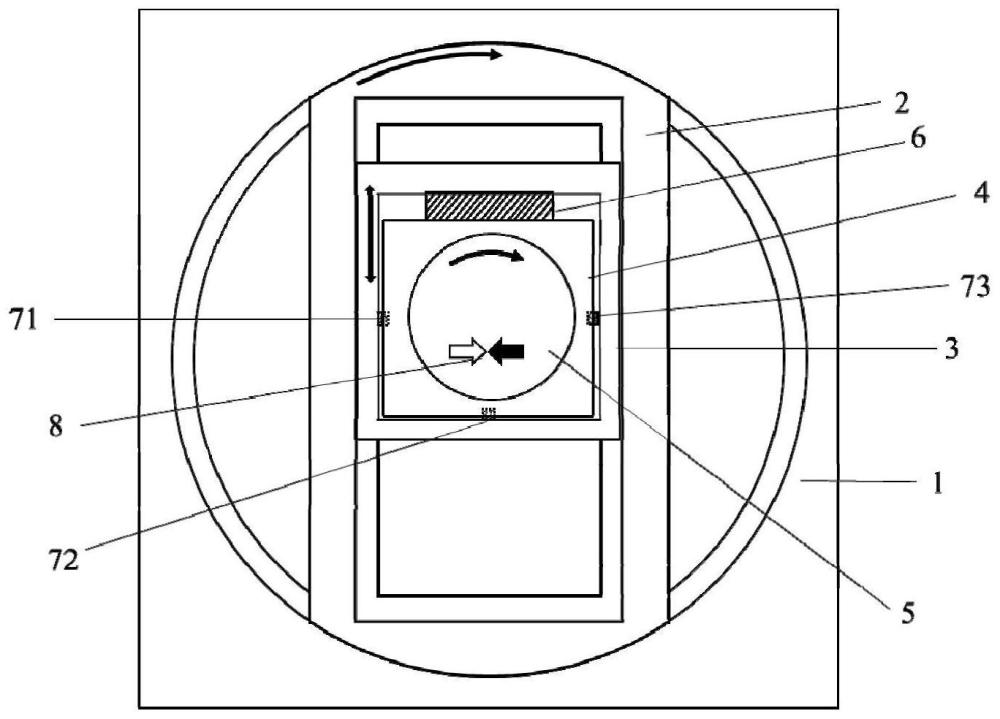

一种全息光存储系统中的伺服平台、复用方法及校准方法

本发明公开了一种全息光存储系统中的伺服平台、复用方法及校准方法,其中伺服平台,包括光头、传感器、公转平台、线性平移台、自转平台以及姿态调整平台;光头用于输出读写光和伺服光;传感器用于检测存储介质相对光头的姿态误差,并生成控制信号;公转平台、线性平移台以及自转平台相互连接,用于放置存储介质以及带动存储介质与光头发生位置变换;姿态调整平台用于支撑放置存储介质的平台,以及根据控制信号,对存储介质相对光头的姿态进行调整。本发明通过存储介质的位置移动,实现移位复用以及交叉复用,提高全息光存储的存储容量,以及通过径向微动平台和竖向微动平台,精准矫正存储介质相对光头的位置和姿态,保证全息图的准确刻录和读取。

2023-10-03 -

用于三维NAND闪存中的擦除和复位的方法

提出了用于擦除三维(3D)存储器件的存储数据的方法。3D存储器件包括多个存储块,每个存储块具有多个存储串,所述多个存储串具有垂直地堆叠的存储单元。每个存储单元可通过字线和位线来寻址。可以通过在阵列公共源上施加擦除电压并在选定的存储块的字线上施加第一电压来擦除选定的存储块中的存储数据。在擦除操作期间,未选定的存储块的字线是浮动的,即没有外部偏置。在擦除操作之后,在整个存储器平面的字线上施加第二电压来复位存储单元以改进数据保持。

2023-10-03 -

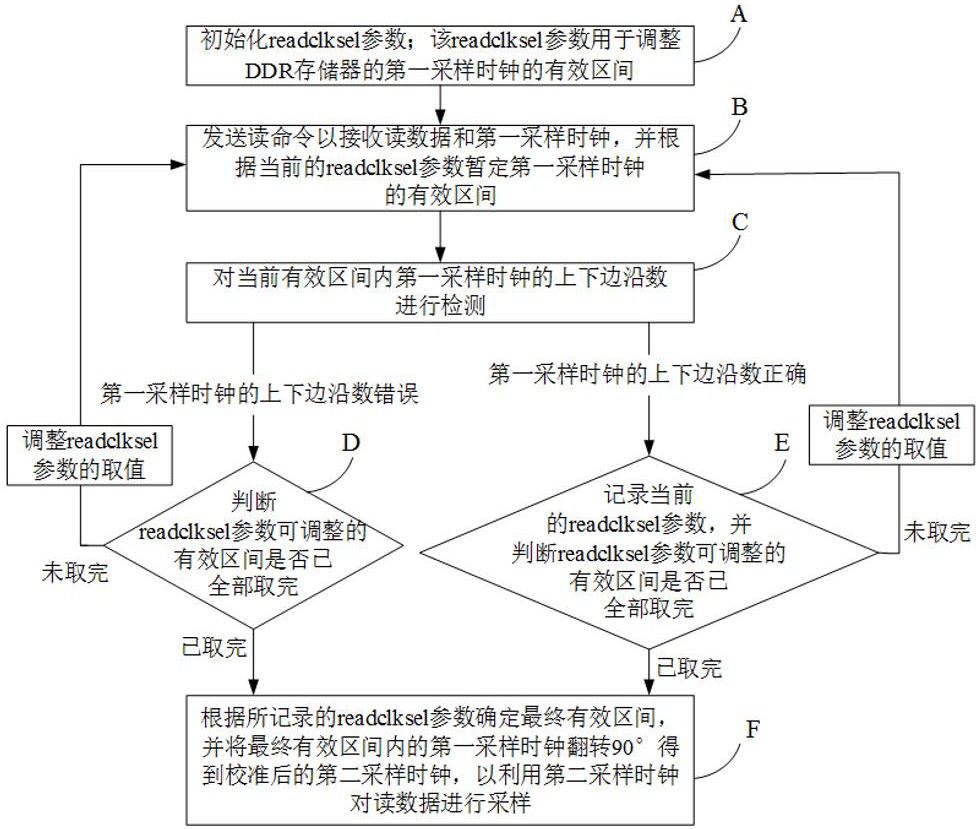

一种DDR存储器采样校准方法及DDR存储器

本发明公开了一种DDR存储器采样校准方法及DDR存储器,该方法包括:初始化readclksel;B、接收读数据和第一采样时钟,根据readclksel暂定第一采样时钟的有效区间;对该区间内第一采样时钟的上下边沿数进行检测;若上下边沿数错误,判断readclksel是否已遍历完;若未完,调整readclksel后返回B;否则执行F;E、若上下边沿数正确,记录readclksel并判断readclksel是否已遍历完;若未完,调整readclksel后返回B,否则执行F;F、根据所记录的readclksel确定最终有效区间,并依此生成第二采样时钟进行采样。本发明可提高DDR存储器的采样精度。

2023-10-03 -

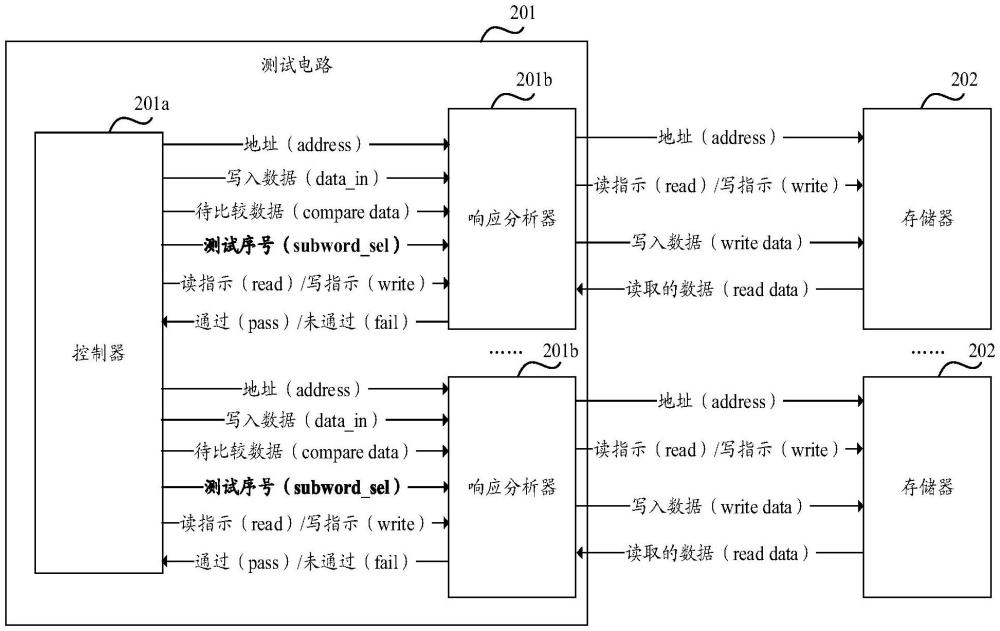

一种测试电路、集成芯片及测试方法

一种测试电路、集成芯片及测试方法,用以减小测试电路的面积。测试电路用于对存储器进行测试,包括控制器和响应分析器。控制器用于向响应分析器发送第一读取指令,以读取第一地址对应的第一数据,第一读取指令中携带第一地址、第二数据和第一测试序号,第一测试序号用于指示响应分析器对第一部分比特位进行测试,第一数据包括M比特,第一部分比特位对应M比特中的第n比特至第n+P比特,M>0,P<M,n≥0;响应分析器用于向存储器发送第二读取指令,然后接收存储器发送的第一数据,并根据第一测试信号将第一数据中位于第一部分比特位的子数据,与第二数据中位于第一部分比特位的子数据进行比较,将第一测试结果输出至控制器。

2023-10-03 -

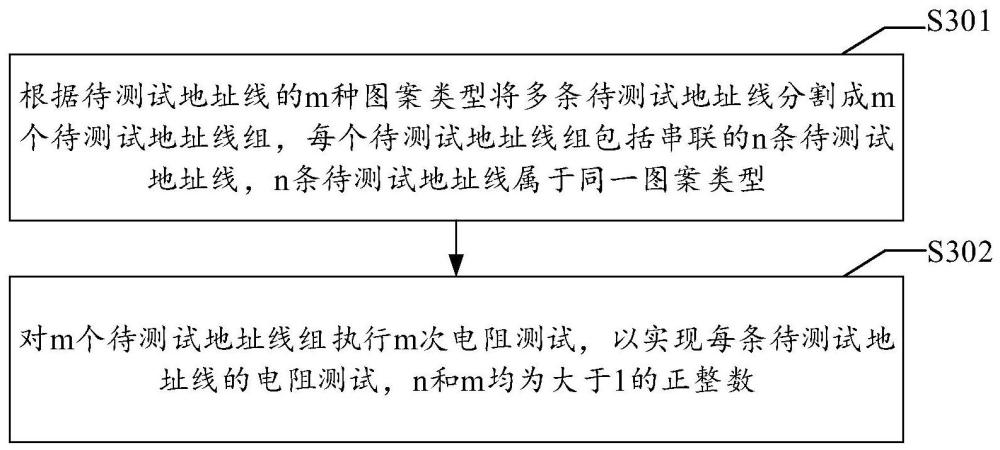

存储器电阻测试方法、半导体结构及其制备方法

本公开提供一种存储器电阻测试方法、半导体结构及其制备方法,属于半导体制造技术领域。该电阻测试方法包括:根据待测试地址线的m种图案类型将多条待测试地址线分割成m个待测试地址线组,每个待测试地址线组包括串联的n条待测试地址线,n条待测试地址线属于同一图案类型;对m个待测试地址线组执行m次电阻测试,以实现每条待测试地址线的电阻测试,n和m均为大于1的正整数。本公开能够测试全部的WL和BL,且可以判断出WL和BL中间是否有断裂。

2023-10-02 -

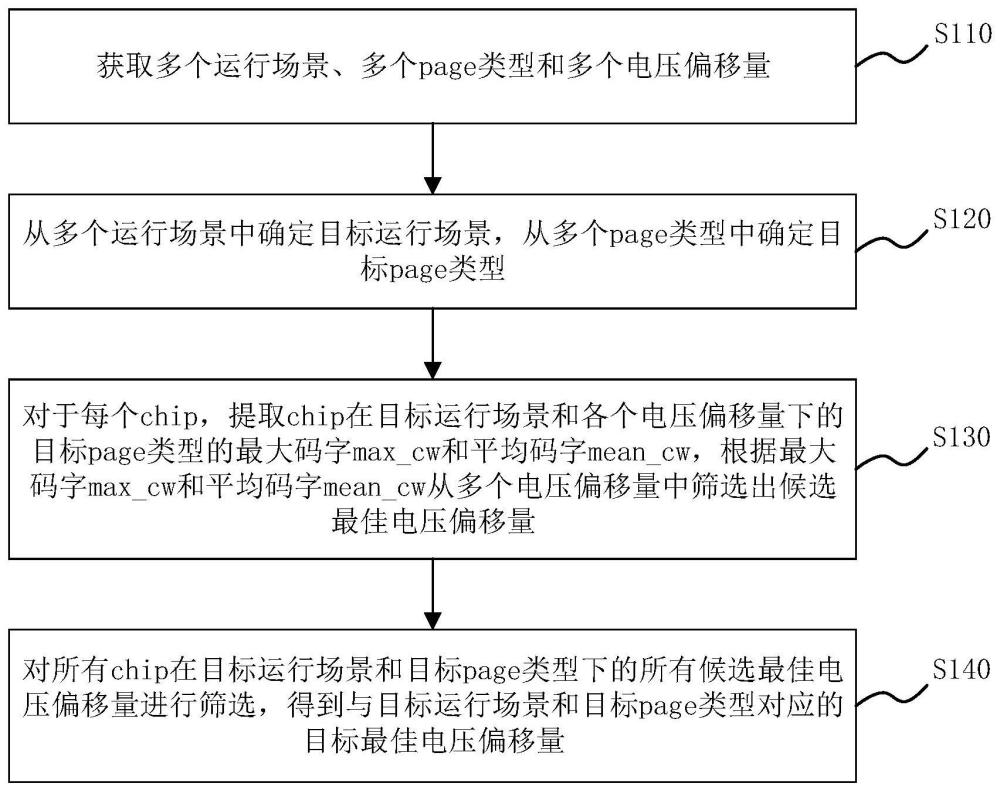

电压偏移量确定方法、电压偏移量调整方法和存储介质

本申请提出了一种电压偏移量确定方法、电压偏移量调整方法和存储介质,包括:获取多个运行场景、多个page类型和多个电压偏移量;从多个运行场景中确定目标运行场景,从多个page类型中确定目标page类型;对于每个chip,提取chip在目标运行场景和各个电压偏移量下的目标page类型的最大码字max_cw和平均码字mean_cw,根据最大码字max_cw和平均码字mean_cw从多个电压偏移量中筛选出候选最佳电压偏移量;对所有chip在目标运行场景和目标page类型下的所有候选最佳电压偏移量进行筛选,得到与目标运行场景和目标page类型对应的目标最佳电压偏移量。本申请能够根据运行场景和page类型快速调整得到多个chip的最佳电压偏移量,能够同时保证多个chip的纠正成功率和纠正速度,使得芯片性能得到极大提升。

2023-10-01 -

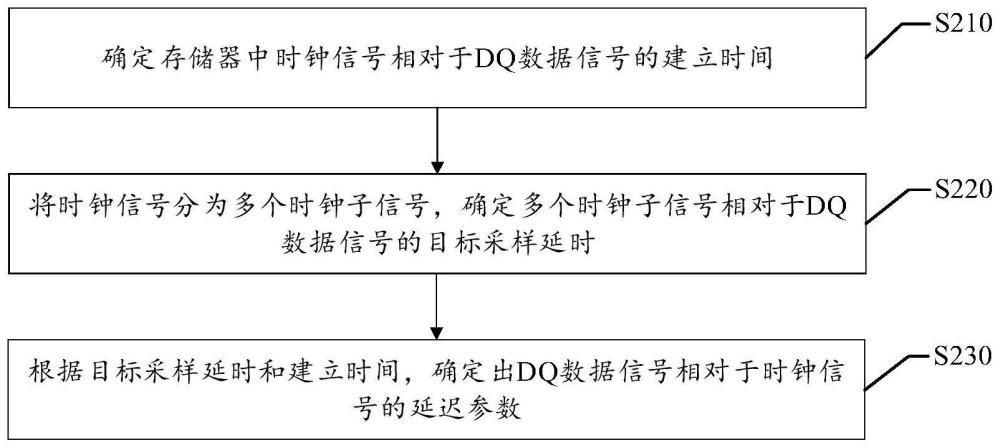

延迟参数确定方法及装置、存储介质及电子设备

本公开是关于一种延迟参数确定方法、延迟参数确定装置、计算机可读存储介质及电子设备,涉及集成电路技术领域。该延迟参数确定方法包括:确定存储器中时钟信号相对于DQ数据信号的建立时间;将时钟信号分为多个时钟子信号,确定多个时钟子信号相对于DQ数据信号的目标采样延时;根据目标采样延时和建立时间,确定出DQ数据信号相对于时钟信号的延迟参数。本公开提供了一种时钟子信号有效采样DQ数据的方法。

2023-10-01 -

一种智慧社区建设考核评价及存储装置

本发明涉及一种智慧社区建设考核评价及存储装置。该装置通过对基础设施、综合信息服务平台、社区管理、社区服务和特色创新等方面的评价等级划分,将各个区、县智慧社区数据汇总至该装置中,并分析社区的覆盖率、一标三实的覆盖率、每天的进出量等数据,输出一个综合的评价。评价结果可以判断建设的智慧社区是否符合智慧社区建设标准,并提出改进建议。该装置可以提供一种有效的智慧社区建设监管工具,可以实现对各个区、县智慧社区的全面监管,从而提高智慧社区建设的质量和效率。本发明具有广泛的应用前景,可应用于各种智慧社区建设场合,为智慧社区建设提供了一种便捷、高效的考核评价工具。

2023-10-01 -

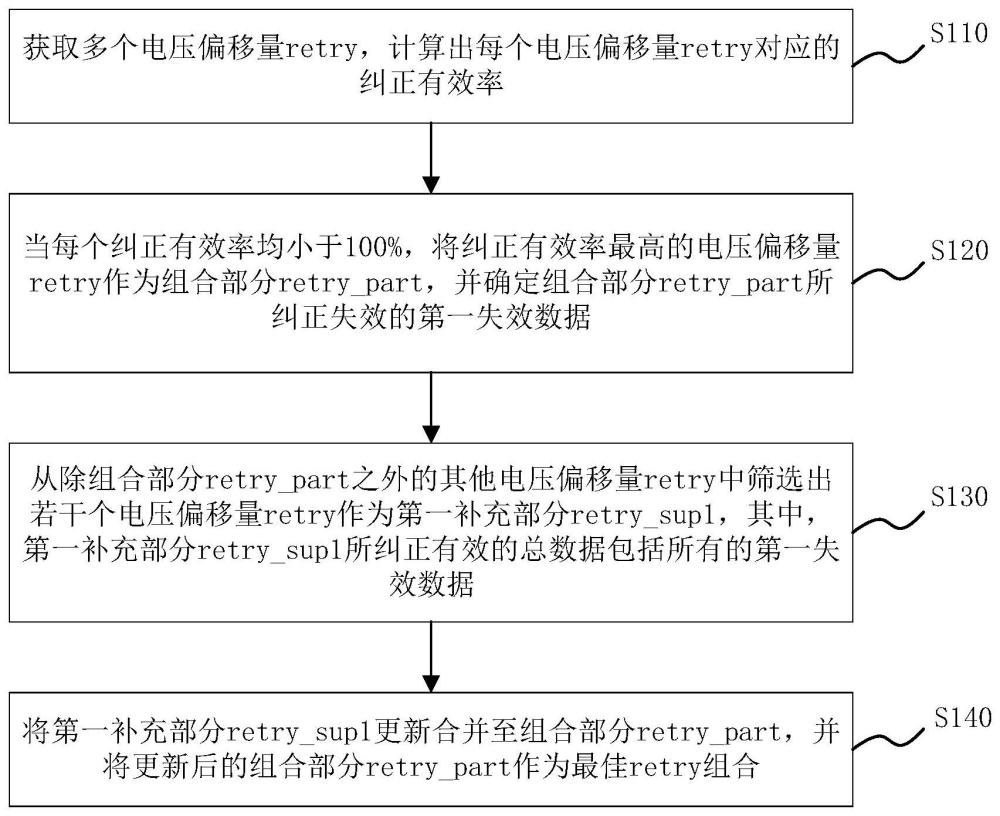

基于数据可靠性的最佳retry组合确定方法、装置和存储介质

本申请提出了一种基于数据可靠性的最佳retry组合确定方法、装置和存储介质,包括:获取多个电压偏移量retry,计算出每个电压偏移量retry对应的纠正有效率;当每个纠正有效率均小于100%,将纠正有效率最高的电压偏移量retry作为组合部分retry_part,并确定组合部分retry_part所纠正失效的第一失效数据;从除组合部分retry_part之外的其他电压偏移量retry中筛选出若干个电压偏移量retry作为第一补充部分retry_sup1;将第一补充部分retry_sup1更新合并至组合部分retry_part,并将更新后的组合部分retry_part作为最佳retry组合。当芯片产品不具备一个能够实现100%纠正能力的最佳retry时,可以通过本申请查找出能够实现100&数据纠错能力的最佳retry组合,从而使得芯片产品能够有效地纠错所有异常数据,从而极大地提升了芯片产品的质量性能。

2023-09-30 -

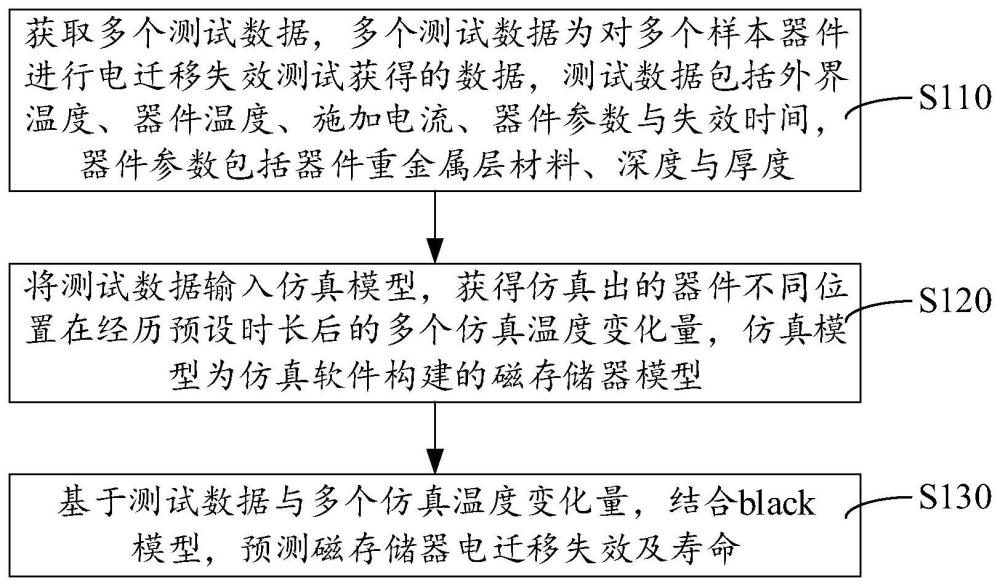

磁存储器电迁移失效及寿命预测方法、装置及电子设备

本发明涉及一种磁存储器电迁移失效及寿命预测方法、装置及电子设备,该方法包括:获取多个测试数据,多个测试数据为对多个样本器件进行电迁移失效测试获得的数据,测试数据包括外界温度、器件温度、施加电流、器件参数与失效时间,器件参数包括器件重金属层材料、深度与厚度;将测试数据输入仿真模型,获得仿真出的器件不同位置在经历预设时长后的多个仿真温度变化量;基于测试数据与多个仿真温度变化量,结合black模型,预测磁存储器电迁移失效及寿命。本发明可实现对磁存储器器件温度的再量化,特别是器件重金属层温度的再量化,使再量化后的器件重金属层的温度更贴近于实际温度,进而结合black模型,更准确的预测出磁存储器电迁移失效及寿命。

2023-09-28 -

基于ReRAM的电路耦合单元及电路耦合方法

本发明提供一种基于ReRAM的电路耦合单元及电路耦合方法,包括:第一ReRAM电路和第二ReRAM电路;第一ReRAM电路包括第一ReRAM结构和第一晶体管;第一ReRAM结构的一端连接有第一供电电压,另一端与第一晶体管的输入端连接,第一晶体管的输出端接地;第二ReRAM电路包括第二ReRAM结构和第二晶体管;第二ReRAM结构的一端连接有第二供电电压,另一端与第二晶体管的输入端连接,第二晶体管的输出端接地。利用本发明能够解决现有技术中,1T1R结构在ReRAM为LRS时,流经ReRAM的电流非常大,增加电流消耗,从而导致1T1R的电路结构不适合长时间开启的场景的技术问题。

2023-09-28 -

一种在一个PAGE内使用不同LDPC译码率的数据保护管理方法

本发明提供了一种在一个PAGE内使用不同LDPC译码率的数据保护管理方法,其通过根据CodeWord不同的error bits分配对应的spare bytes和LDPC译码能力,延缓使用了Read retry和LDPC soft bit,提升了数据纠错能力和系统稳定性,延长了系统寿命,并且本方法只需要修改FW,便于实现,其特征在于:所述方法包括以下步骤:步骤1、检测同一个PAGE内每个CodeWord的error bits数;步骤2、根据CodeWord的error bits数的差异将每个CodeWord分级;步骤3、根据CodeWord的级数,分配对应的spare bytes。

2023-09-27